**University of Southampton**

Power Conscious Scan-Based Test

of

Digital VLSI Circuits

*by*

*Paul Rosinger*

A thesis submitted for the degree of

Doctor of Philosophy

in the

Faculty of Engineering and Applied Science

Department of Electronics and Computer Science

February 2003

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF ENGINEERING AND APPLIED SCIENCE

ELECTRONICS AND COMPUTER SCIENCE

Doctor of Philosophy

POWER CONSCIOUS SCAN TESTING

OF

DIGITAL VLSI CIRCUITS

by Paul Rosinger

Significant research has been devoted over the past decade to solving power-related challenges in digital integrated circuit design. While power optimisation become almost a push-button design step, the gap between the design and test camps left the power issues associated with the integrated circuit test process unsolved. Ignoring power during test may have serious consequences on product reliability and manufacturing yield. This thesis addresses the problem of power dissipation in scan-based test with the goal of developing and validating a set of power conscious design-for-test methodologies and structures. Four different test development and integration scenarios are investigated and an appropriate solution is proposed in each case.

The first part of this thesis addresses the problem of power dissipation during test in the system integration step. A test power profile manipulation technique, easy to integrate into any existing power constrained test scheduling algorithm, was developed in order to reduce the overall testing time by increasing test concurrency. Extensive experimental results using benchmark circuits, show that the proposed power profile manipulation approach enables testing time reductions up to 41% when compared to existing power constrained test scheduling approaches.

Mixed-mode BIST offers complete fault coverage with short test application times and small test data storage requirements. The second part of this thesis addresses the problem of reducing power dissipation in mixed-mode BIST. A new mixed-mode test pattern generator combining the masking properties of AND/OR composition with LFSR reseeding is proposed. Experimental data shows reductions up to 20% in average power dissipation during test when compared with traditional test pattern generators.

Test data compression/decompression represents an efficient solution to the increasing test data storage requirements on external test equipment. A new test data encoding scheme combined with a new weighted scan latch reordering algorithm are proposed for reducing the test data storage requirements for low power test sets. Experimental results show reductions up to nearly 50% in test data storage requirements and up to 75% in power dissipation when compared with other existing approaches.

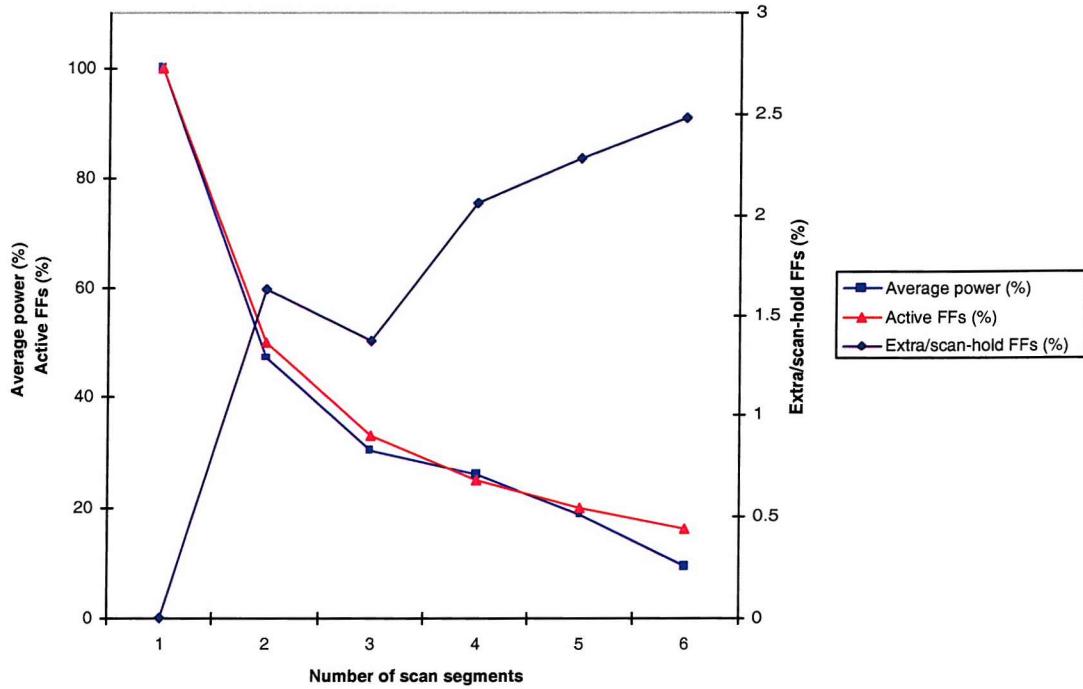

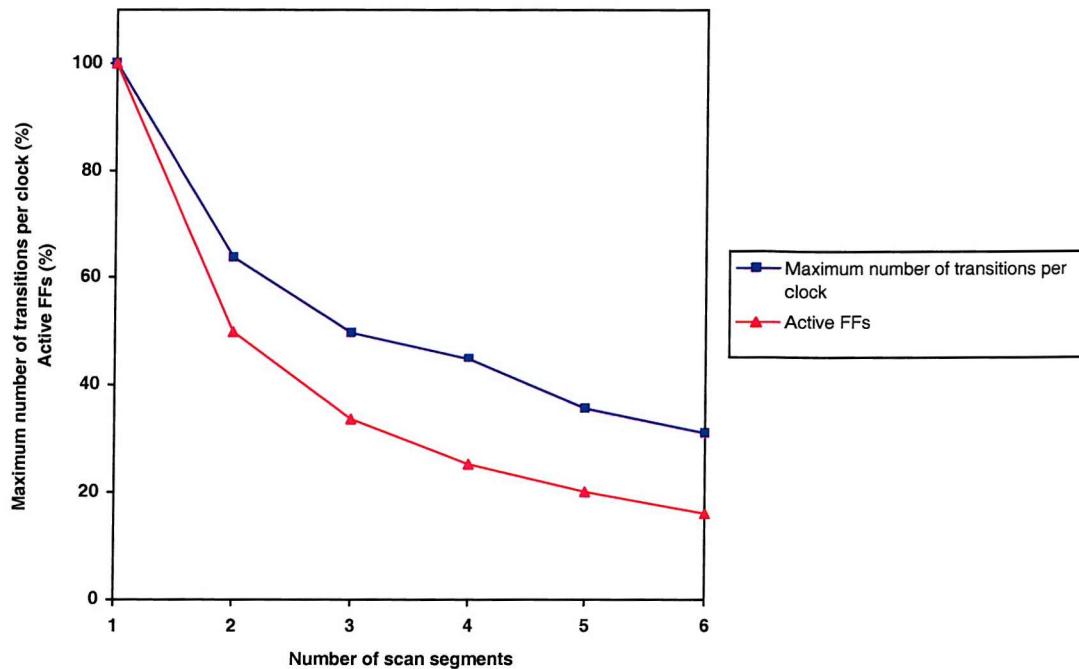

The last part of this thesis presents a scan architecture with mutually exclusive scan segment activation which reduces both average and peak power dissipation during test, hence eliminating not only the risks of reliability problems but also the risks of noise-induced test failures. Experimental results show reductions up to 50% in both peak and average power when compared to standard scan architectures.

# Contents

|          |                                                               |           |

|----------|---------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                                           | <b>2</b>  |

| 1.1      | Test process and design for test . . . . .                    | 3         |

| 1.1.1    | Fault Models . . . . .                                        | 4         |

| 1.1.2    | Fault Simulation . . . . .                                    | 6         |

| 1.1.3    | Automatic Test Pattern Generation . . . . .                   | 7         |

| 1.1.4    | Internal Scan . . . . .                                       | 8         |

| 1.1.5    | Full-Scan Design vs. Partial-Scan Design . . . . .            | 10        |

| 1.1.6    | Automatic Test Equipment . . . . .                            | 12        |

| 1.1.7    | Built-in Self-Test . . . . .                                  | 13        |

| 1.2      | Power Dissipation in Digital VLSI Circuits . . . . .          | 15        |

| 1.2.1    | Sources of Power Dissipation in Digital VLSI Circuits . . . . | 16        |

| 1.2.2    | Effects of Excessive Power Dissipation . . . . .              | 18        |

| 1.2.3    | Low Power Design . . . . .                                    | 19        |

| 1.3      | Power Issues Affecting the Test Process . . . . .             | 22        |

| 1.4      | Thesis Overview and Contributions . . . . .                   | 26        |

| <b>2</b> | <b>Power Profile Manipulation</b>                             | <b>29</b> |

---

|          |                                                           |           |

|----------|-----------------------------------------------------------|-----------|

| 2.1      | Background Information . . . . .                          | 32        |

| 2.1.1    | Test Scheduling . . . . .                                 | 32        |

| 2.1.2    | Approximation Model for Power Dissipation During Test . . | 33        |

| 2.1.3    | Global Peak Power Approximation Model . . . . .           | 33        |

| 2.2      | Power Profile Manipulation Technique . . . . .            | 34        |

| 2.2.1    | Test Vector Reordering . . . . .                          | 35        |

| 2.2.2    | Test Sequence Expansion . . . . .                         | 40        |

| 2.2.3    | Improved Power Approximation Model . . . . .              | 41        |

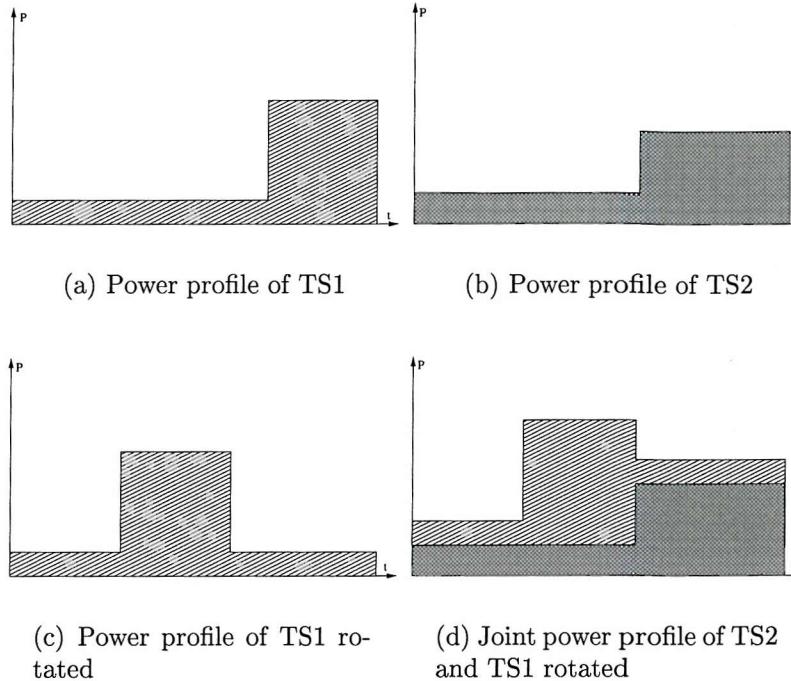

| 2.2.4    | Test Sequence Rotation . . . . .                          | 42        |

| 2.3      | Using power profile manipulation . . . . .                | 43        |

| 2.4      | Experimental Results . . . . .                            | 48        |

| 2.5      | Concluding Remarks . . . . .                              | 51        |

| <b>3</b> | <b>Low Power Mixed-Mode BIST</b>                          | <b>52</b> |

| 3.1      | LFSR Re-Seeding . . . . .                                 | 55        |

| 3.2      | AND/OR Masking . . . . .                                  | 58        |

| 3.3      | AND/OR Masking in Mixed-Mode BIST . . . . .               | 60        |

| 3.4      | Dual MP-LFSR Test Pattern Generator . . . . .             | 63        |

| 3.5      | Test Set Pre-processing . . . . .                         | 64        |

| 3.6      | Experimental Results . . . . .                            | 69        |

| 3.7      | Concluding Remarks . . . . .                              | 76        |

| <b>4</b> | <b>Low Power Test Data Compression</b>                    | <b>80</b> |

| 4.1      | Background Information . . . . .                          | 84        |

---

|          |                                                                |            |

|----------|----------------------------------------------------------------|------------|

| 4.1.1    | Golomb Codes . . . . .                                         | 84         |

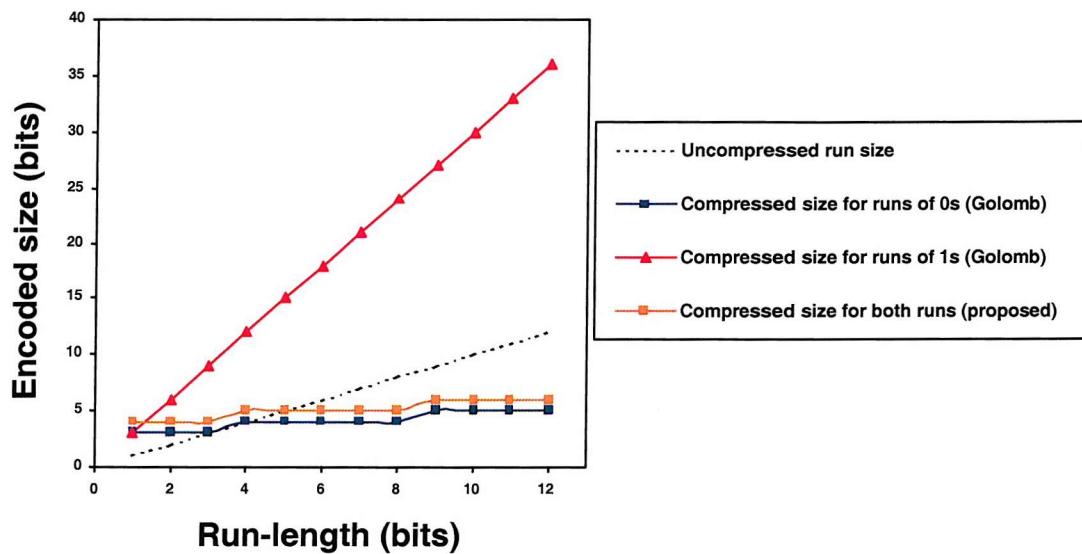

| 4.2      | Compression Efficiency of Standard Golomb Codes . . . . .      | 86         |

| 4.3      | Symmetric Golomb Coding Scheme . . . . .                       | 87         |

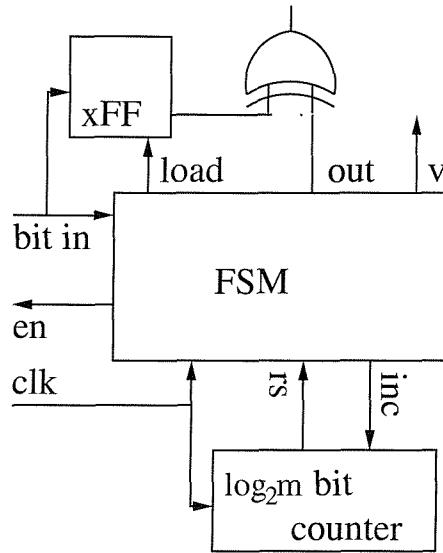

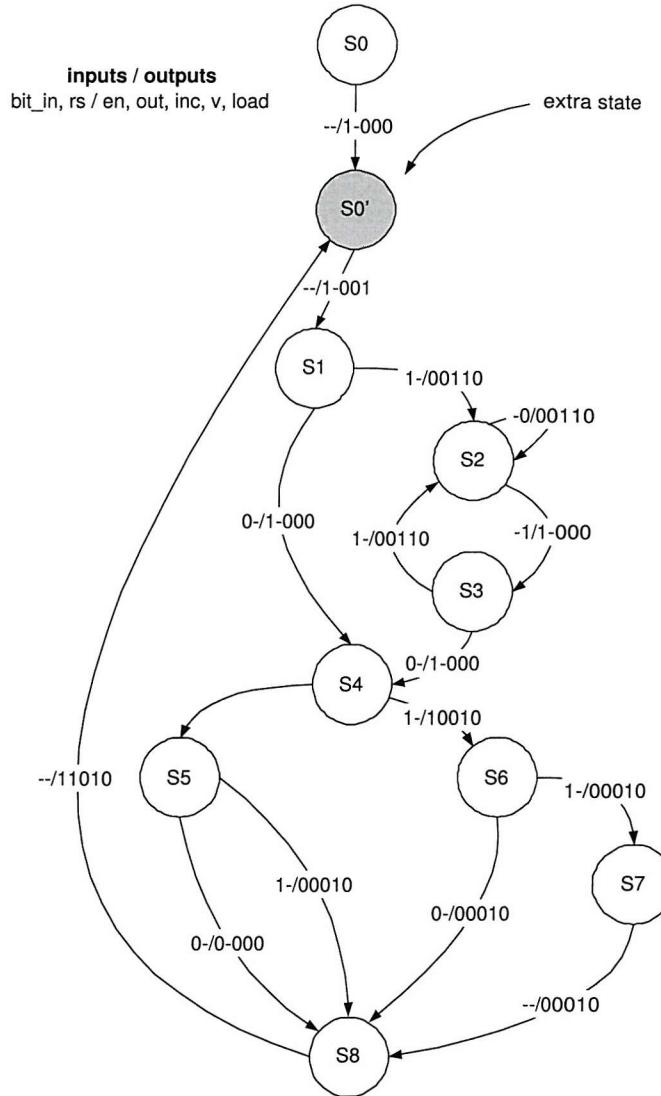

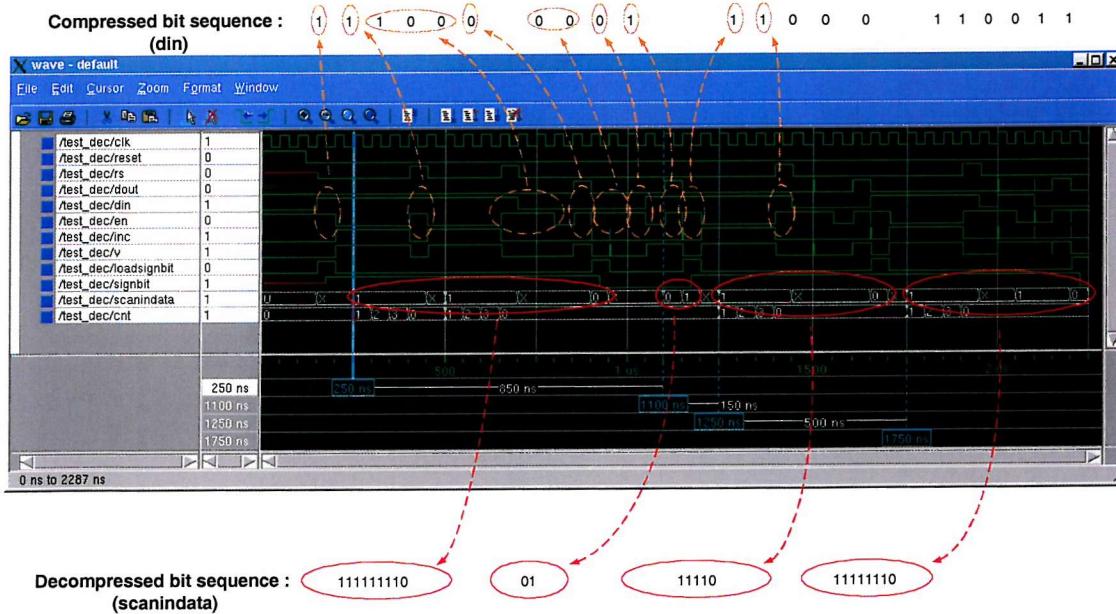

| 4.4      | Decompression Unit for Symmetric Golomb Codes . . . . .        | 90         |

| 4.5      | Weighted Scan Latch Reordering (W-SLR) . . . . .               | 93         |

| 4.6      | Experimental Results . . . . .                                 | 96         |

| 4.7      | Concluding Remarks . . . . .                                   | 101        |

| <b>5</b> | <b>Low Power Scan Architecture</b>                             | <b>102</b> |

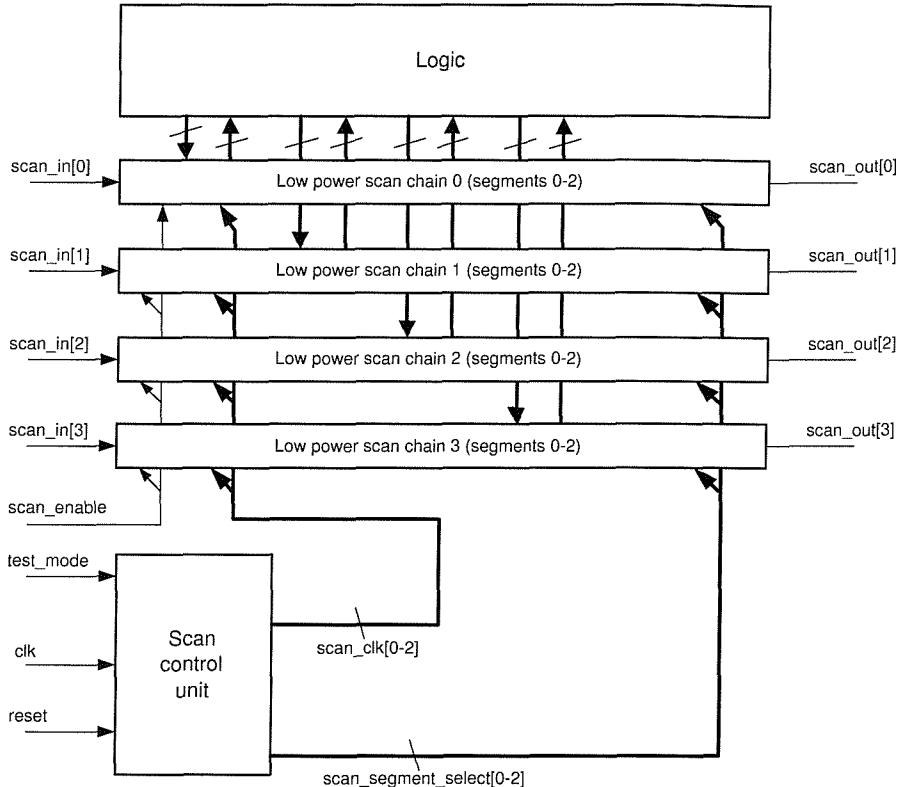

| 5.1      | New Low Power Scan Architecture . . . . .                      | 106        |

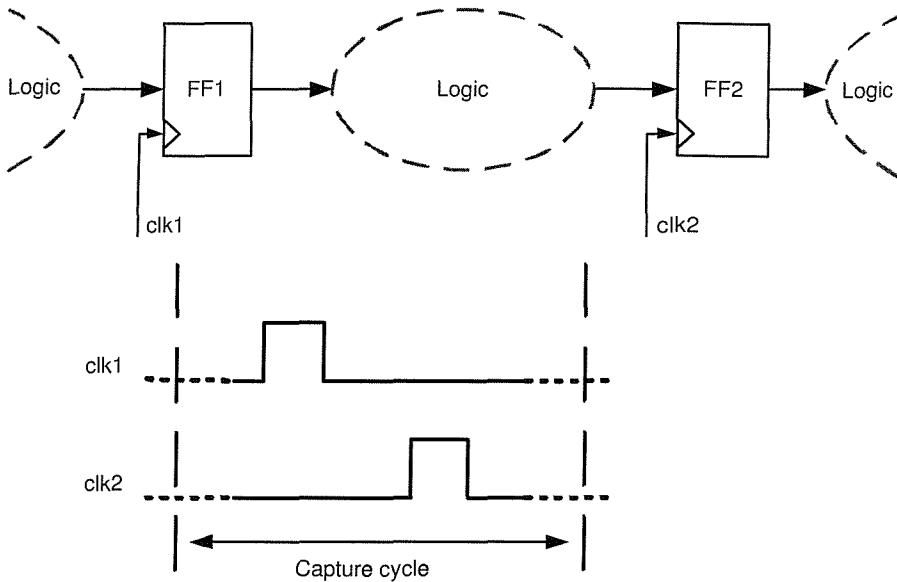

| 5.1.1    | Structural Dependencies and Capture Violations . . . . .       | 110        |

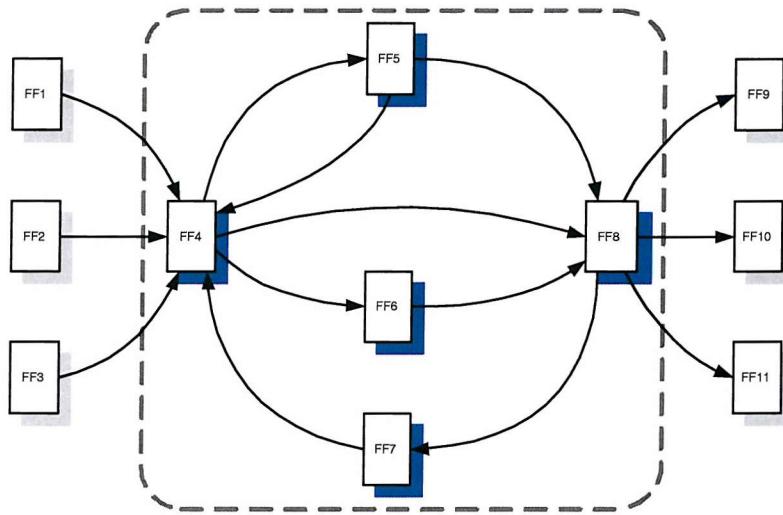

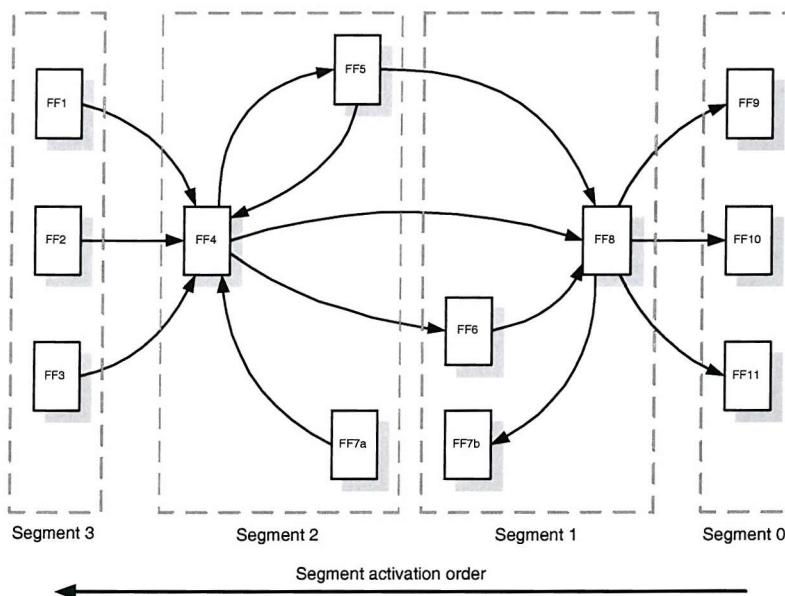

| 5.1.2    | Scan Chain Partitioning . . . . .                              | 112        |

| 5.2      | Low Power Multiple Scan Chain Architecture . . . . .           | 118        |

| 5.3      | Experimental Results . . . . .                                 | 120        |

| 5.4      | Concluding Remarks . . . . .                                   | 125        |

| <b>6</b> | <b>Conclusions and Further Work</b>                            | <b>127</b> |

| 6.1      | Further Work . . . . .                                         | 131        |

| 6.1.1    | Low Power Delay Test . . . . .                                 | 131        |

| 6.1.2    | Low Power Test Response Compression . . . . .                  | 132        |

| <b>A</b> | <b>Experimental Setup for Low Power Mixed-Mode BIST</b>        | <b>133</b> |

| <b>B</b> | <b>Decoding Unit Implementation for Symmetric Golomb Codes</b> | <b>142</b> |

|                                                                      |            |

|----------------------------------------------------------------------|------------|

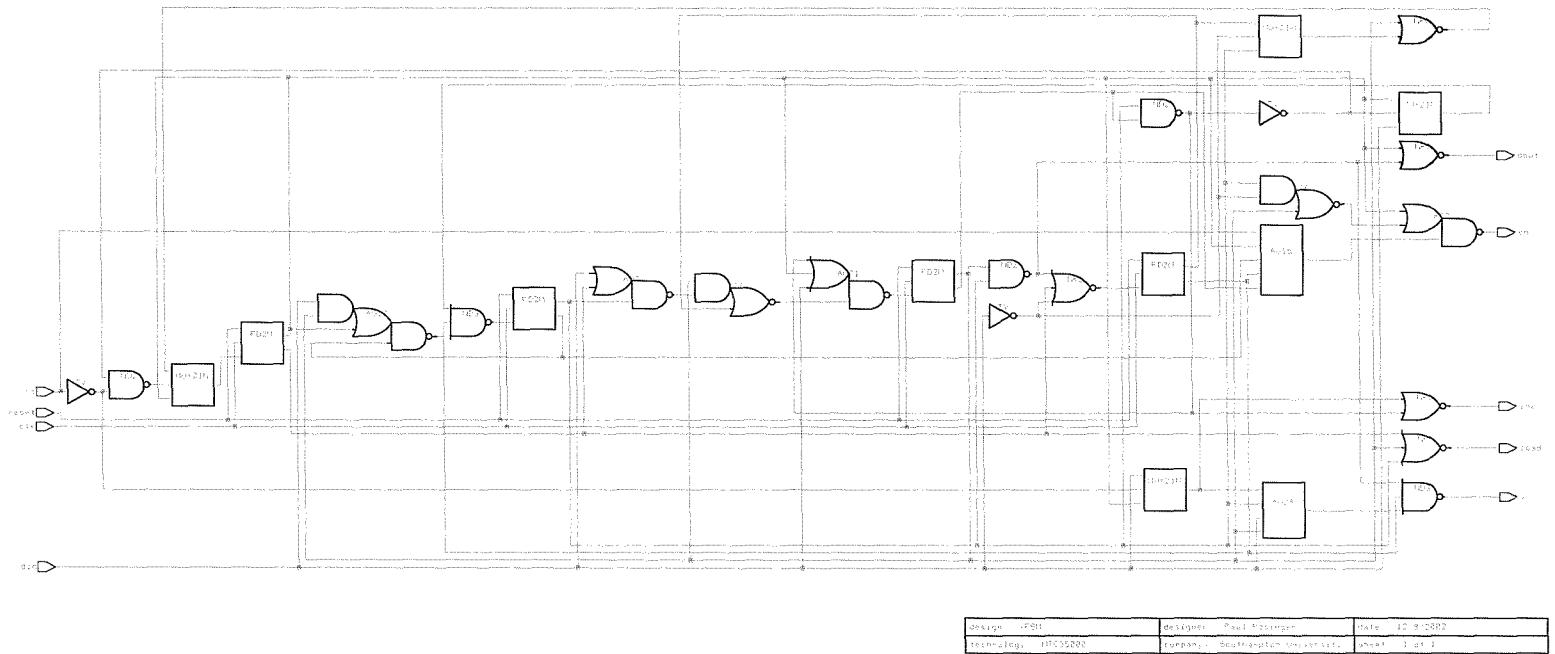

| <b>C Control Unit and Experimental Setup for Low Power Scan Test</b> | <b>148</b> |

| <b>D Tools and Benchmark Circuits</b>                                | <b>159</b> |

| D.1 Academic and Commercial Software Tools . . . . .                 | 159        |

| D.2 Benchmark Circuits . . . . .                                     | 160        |

# List of Figures

|      |                                                            |    |

|------|------------------------------------------------------------|----|

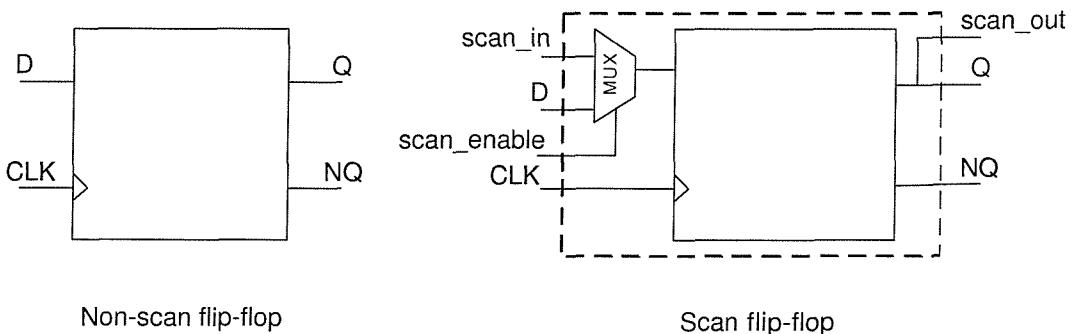

| 1.1  | D flip-flop with scan capability                           | 8  |

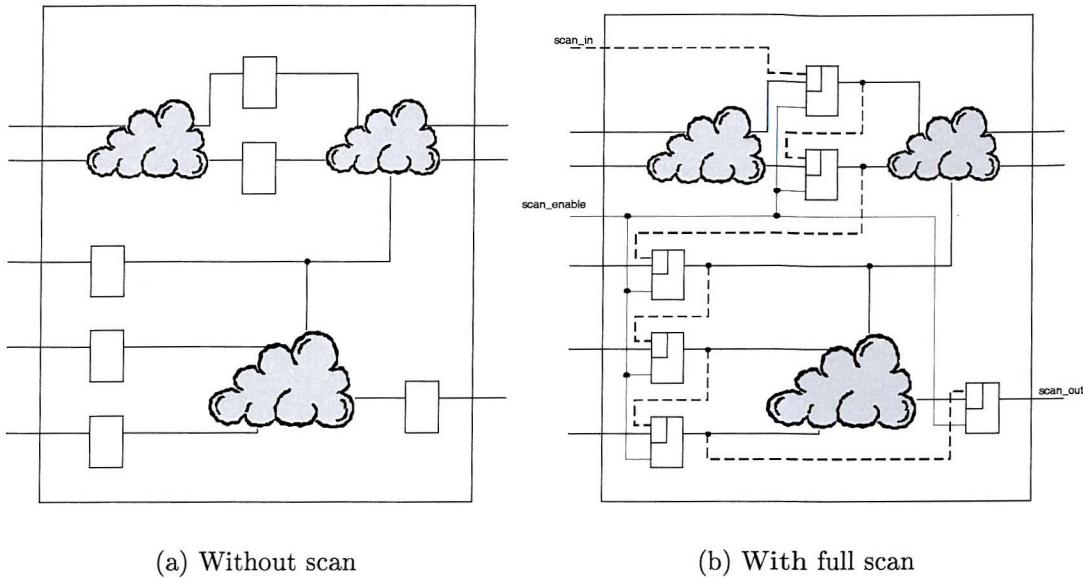

| 1.2  | Scan path through a full-scan design                       | 11 |

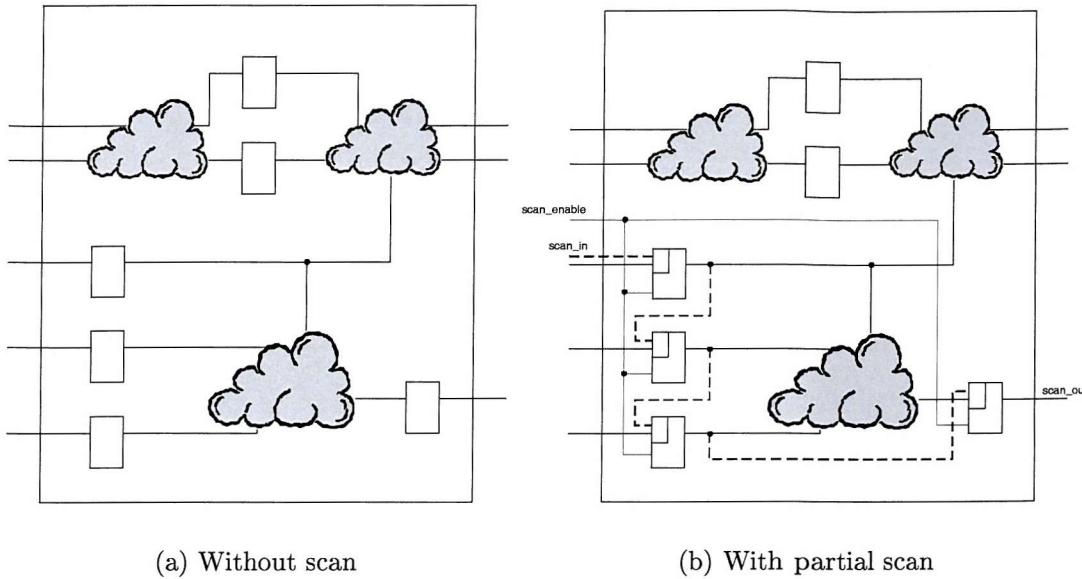

| 1.3  | Scan path through a partial-scan design                    | 12 |

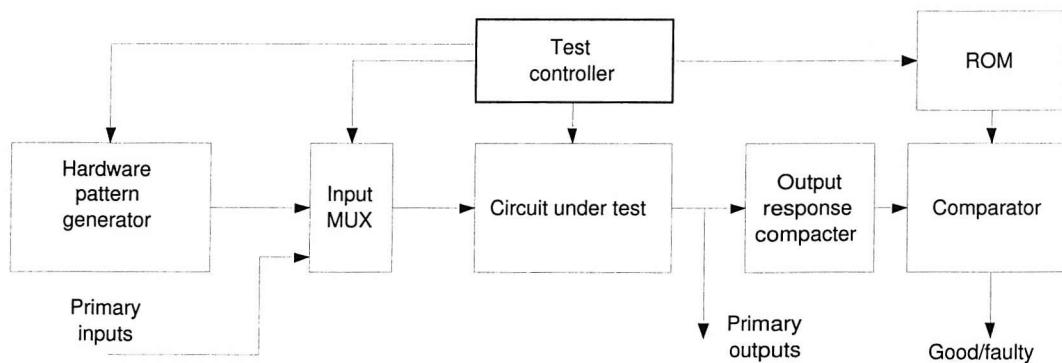

| 1.4  | Typical BIST scheme                                        | 13 |

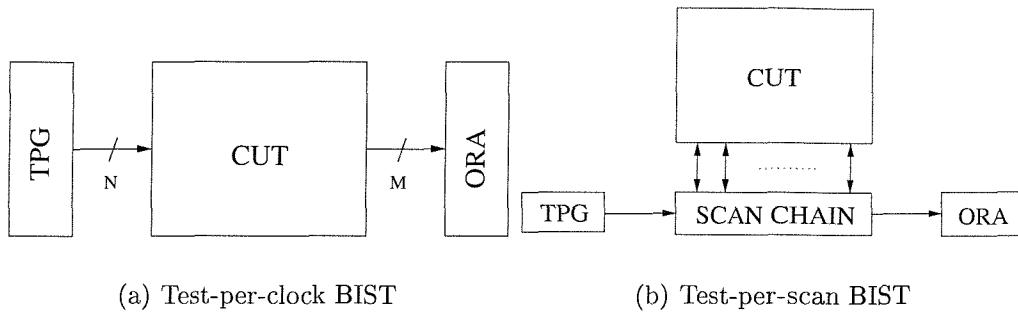

| 1.5  | BIST schemes                                               | 15 |

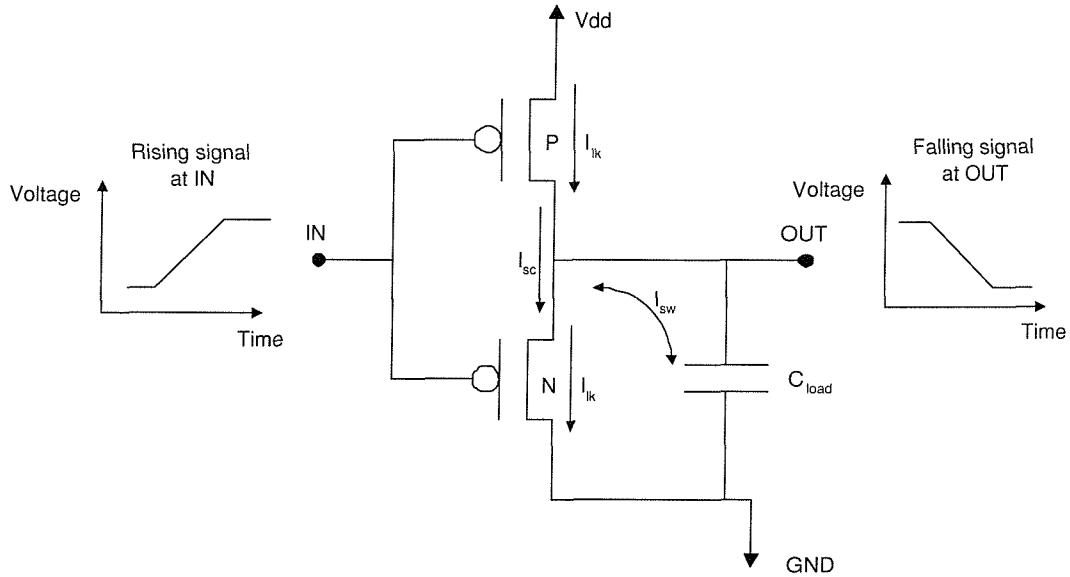

| 1.6  | Components of power dissipation                            | 16 |

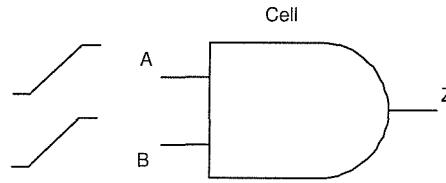

| 1.7  | Simple cell                                                | 18 |

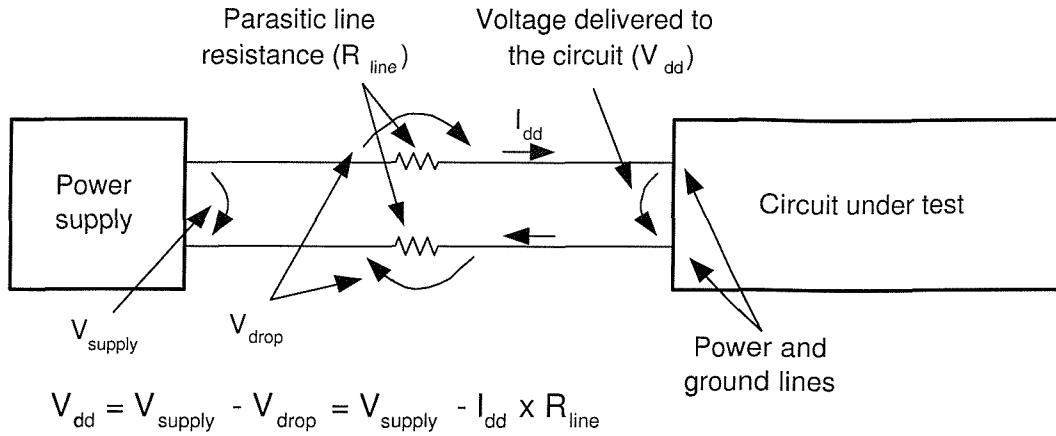

| 1.8  | Voltage (IR) drop                                          | 19 |

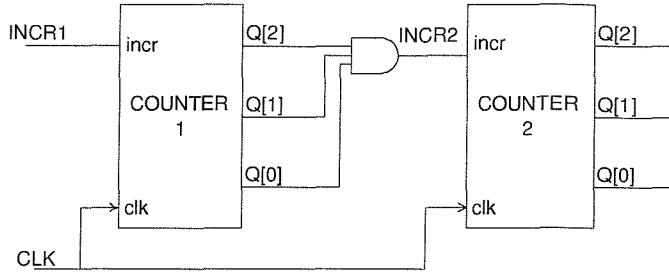

| 1.9  | Two-counter sample design                                  | 21 |

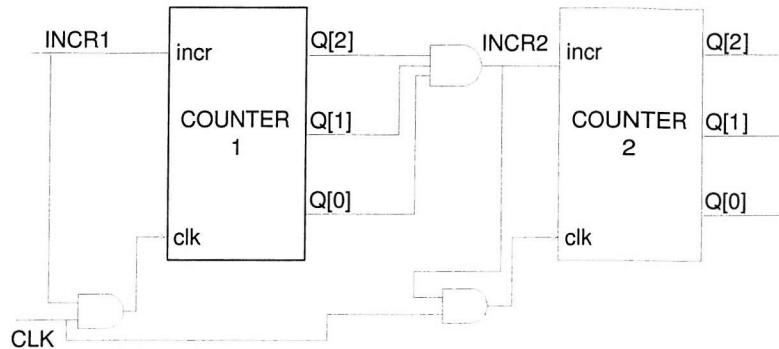

| 1.10 | Implementation of the two-counter design with clock gating | 22 |

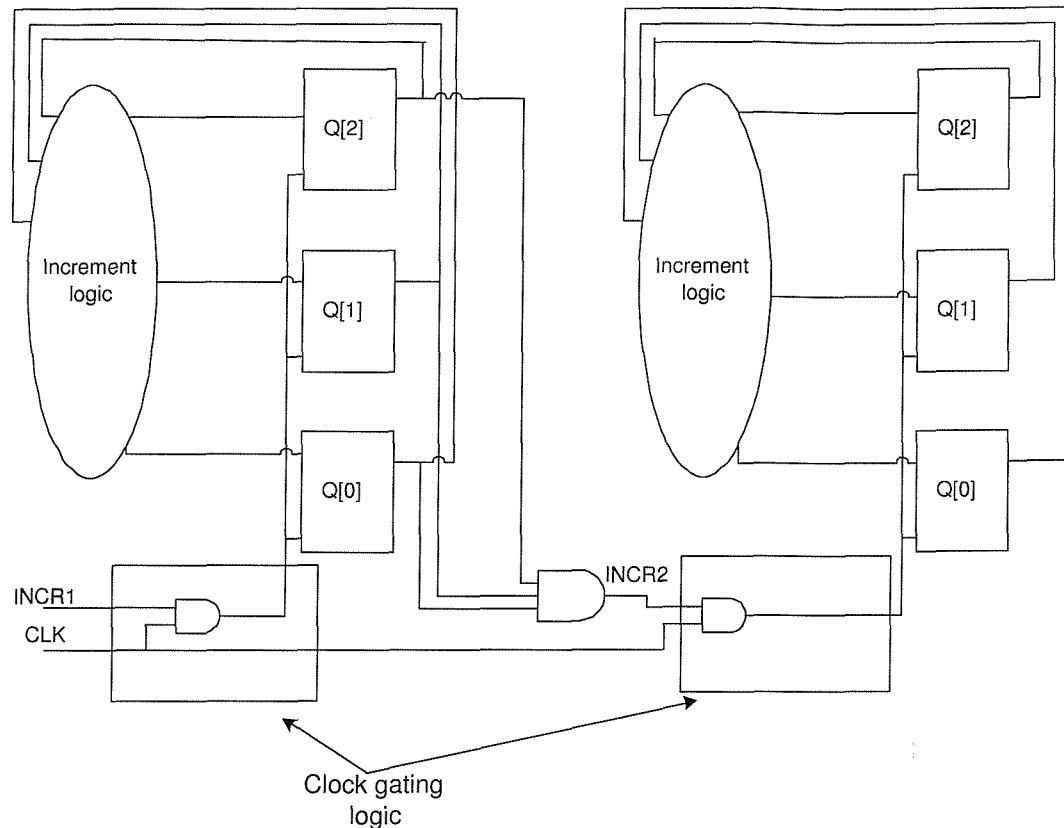

| 1.11 | Implementation of the two-counter design with clock gating | 24 |

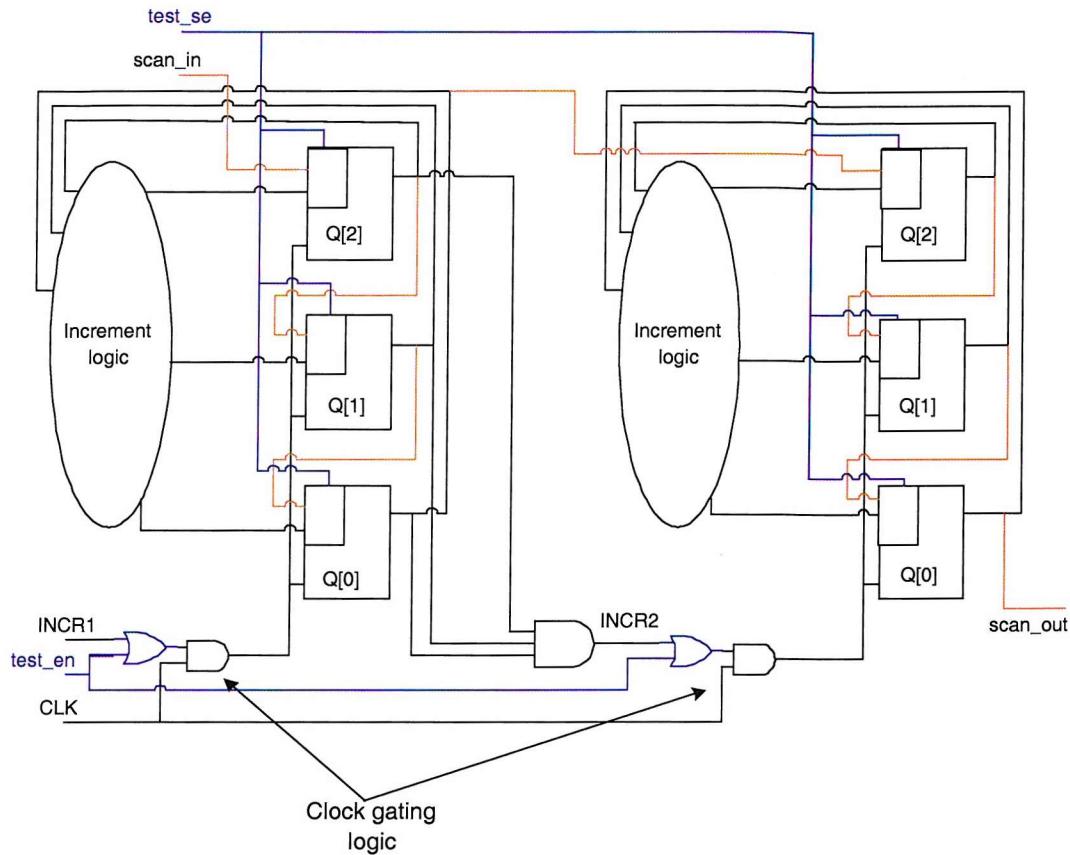

| 1.12 | Implementation of sample design with clock gating          | 25 |

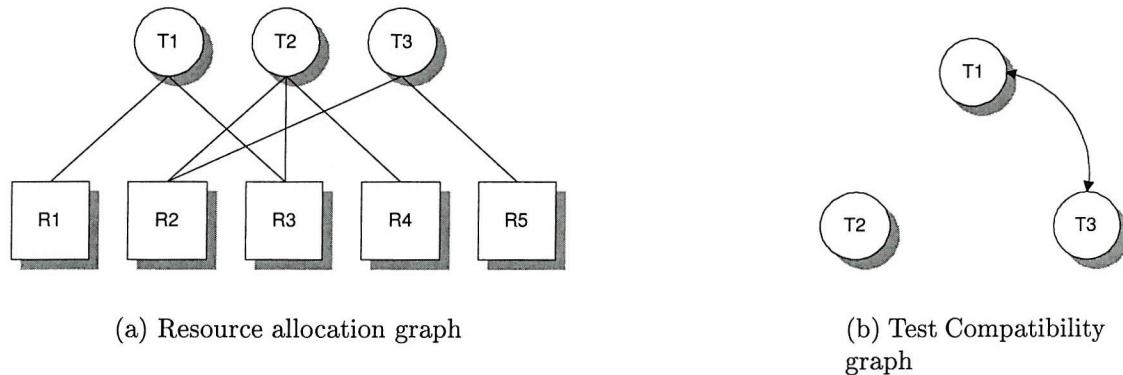

| 2.1  | Resource allocation graph and test compatibility graph     | 32 |

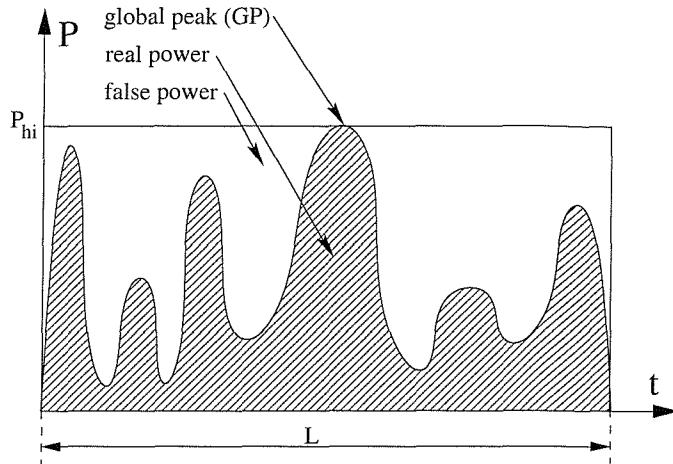

| 2.2  | Global peak power approximation model                      | 34 |

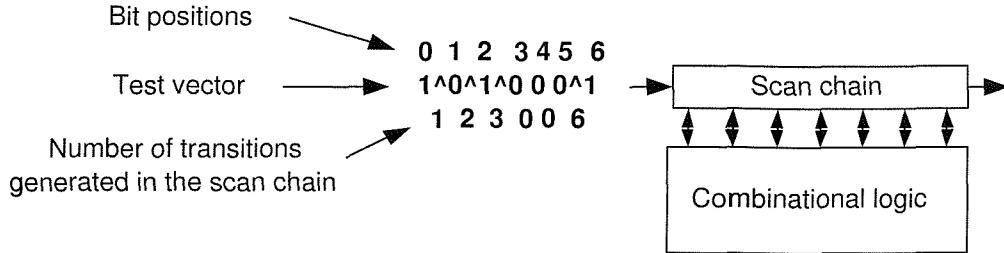

| 2.3  | Weighted transition metric explained                       | 38 |

---

|     |                                                                                                                                                                                                                      |    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

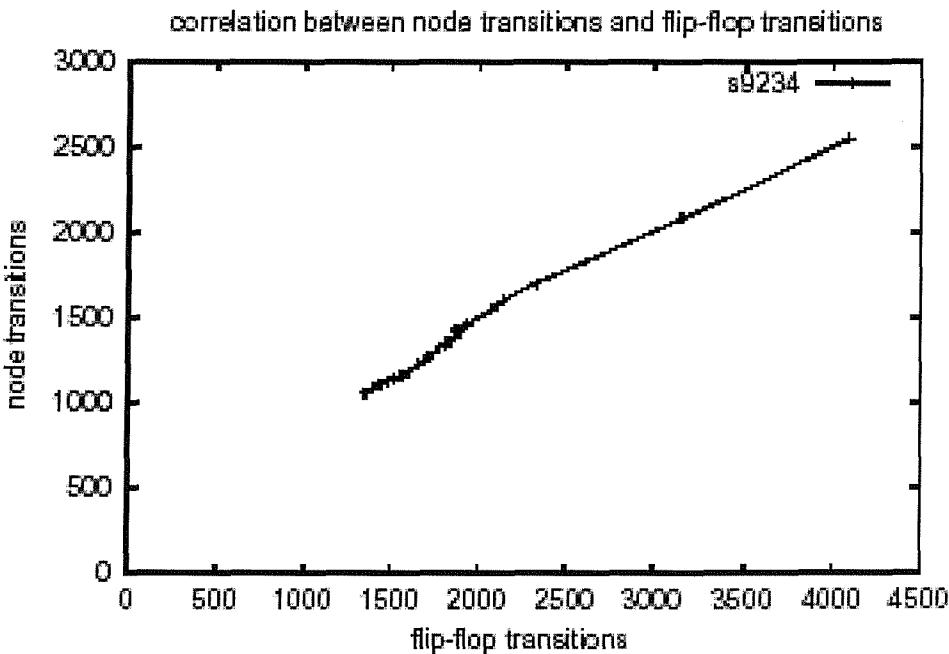

| 2.4 | Correlation between internal node transition count and WTC(flip-flop transitions) [SOT00] . . . . .                                                                                                                  | 38 |

| 2.5 | Two local peak power approximation model . . . . .                                                                                                                                                                   | 41 |

| 2.6 | Test sequence rotation . . . . .                                                                                                                                                                                     | 44 |

| 2.7 | Example: Test Compatibility Graph . . . . .                                                                                                                                                                          | 46 |

| 2.8 | Example: Power compatible lists under the 2LP-PAM and GP-PAM                                                                                                                                                         | 46 |

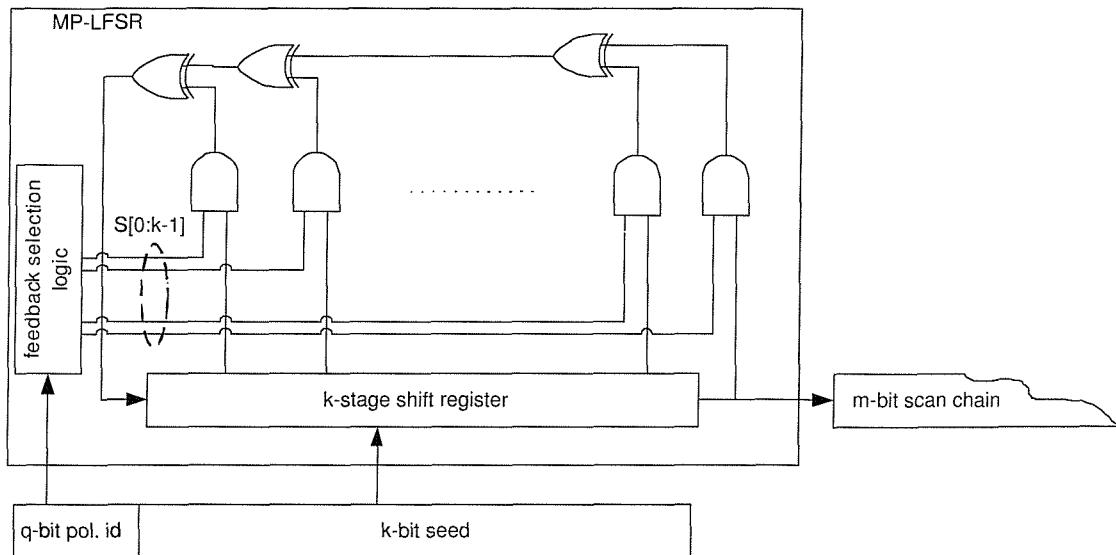

| 3.1 | Multiple-polynomial LFSR architecture [HRT <sup>+</sup> 95] . . . . .                                                                                                                                                | 58 |

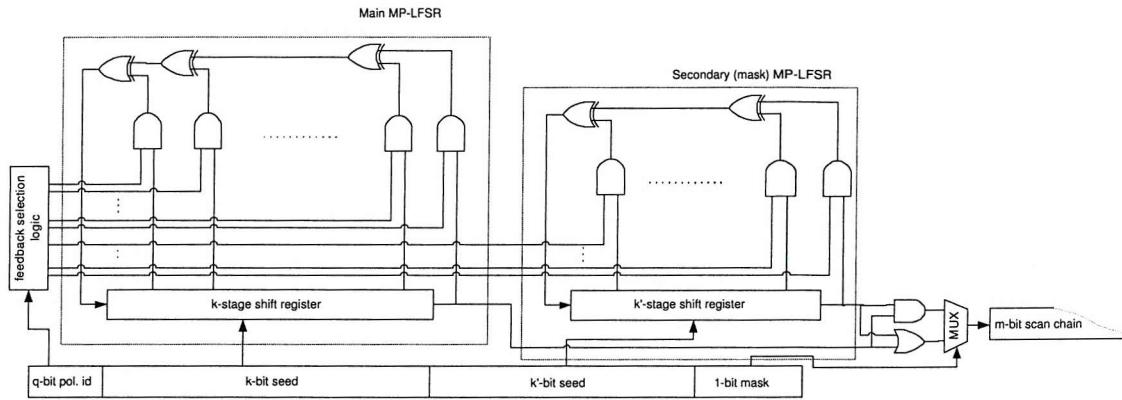

| 3.2 | Proposed dual MP-LFSR for low power mixed-mode BIST . . . . .                                                                                                                                                        | 64 |

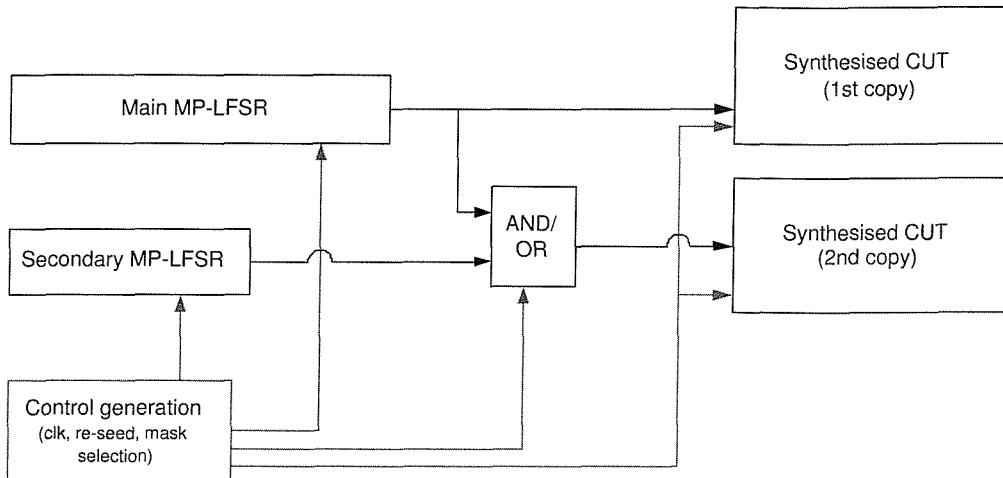

| 3.3 | Circuit configuration for simulation . . . . .                                                                                                                                                                       | 70 |

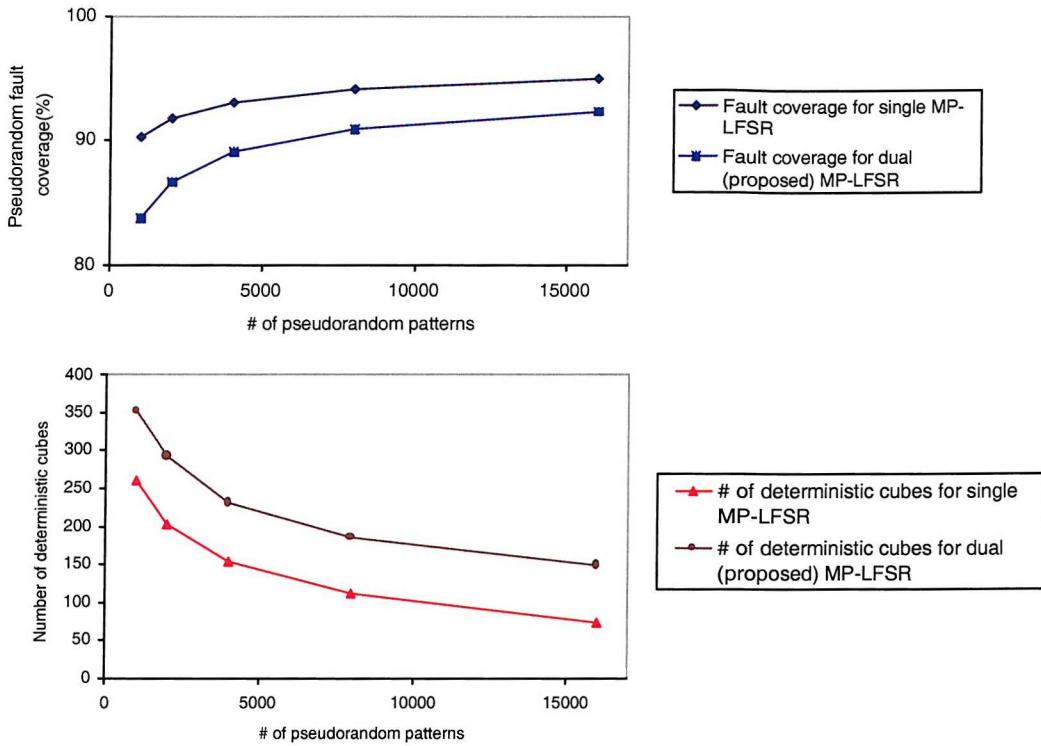

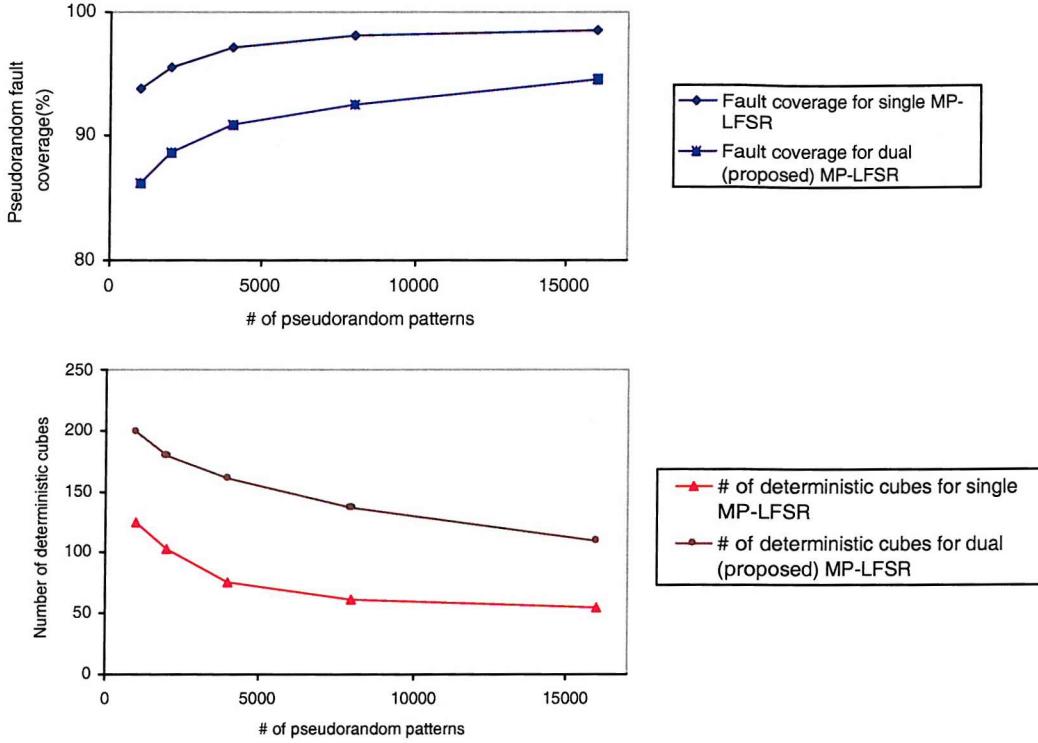

| 3.4 | Comparison between the proposed dual MP-LFSR TPG and the traditional single MP-LFSR TPG [HRT <sup>+</sup> 95] in terms of pseudo-random fault coverage and test data storage requirements (circuit s38584) . . . . . | 73 |

| 3.5 | Comparison between the proposed dual MP-LFSR TPG and the traditional single MP-LFSR TPG [HRT <sup>+</sup> 95] in terms of pseudo-random fault coverage and test data storage requirements (circuit s5378) . . . . .  | 74 |

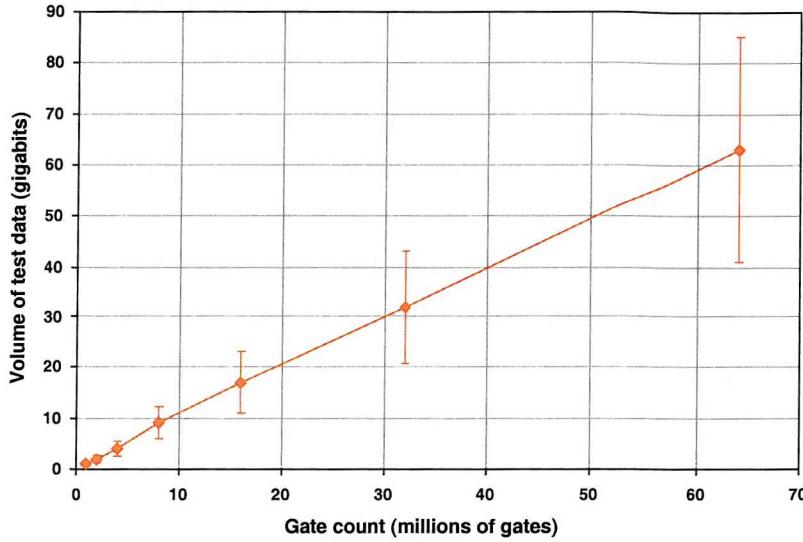

| 4.1 | Volume of test data vs. gate count . . . . .                                                                                                                                                                         | 81 |

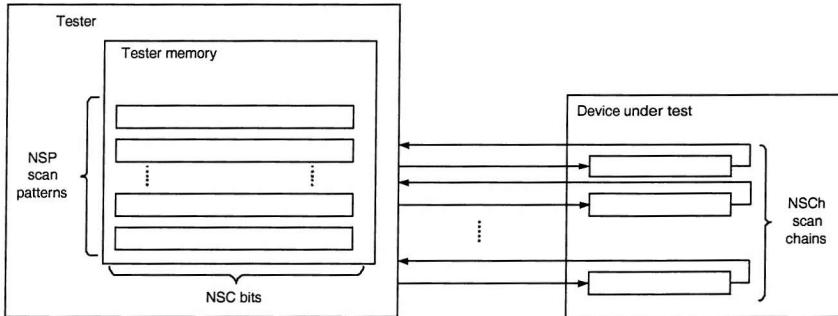

| 4.2 | Tester and device under test . . . . .                                                                                                                                                                               | 81 |

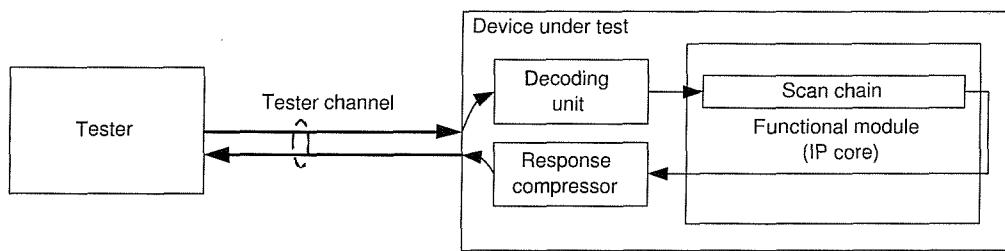

| 4.3 | Scan-based test using a test data compression scheme . . . . .                                                                                                                                                       | 82 |

| 4.4 | Code size comparison for the asymmetric and symmetric Golomb coding schemes for a group size of 4 . . . . .                                                                                                          | 89 |

| 4.5 | Decoding unit for the symmetric Golomb coding scheme . . . . .                                                                                                                                                       | 90 |

| 4.6 | FSM for the symmetric Golomb code decoder (group size 4) . . . . .                                                                                                                                                   | 91 |

---

|      |                                                                                     |     |

|------|-------------------------------------------------------------------------------------|-----|

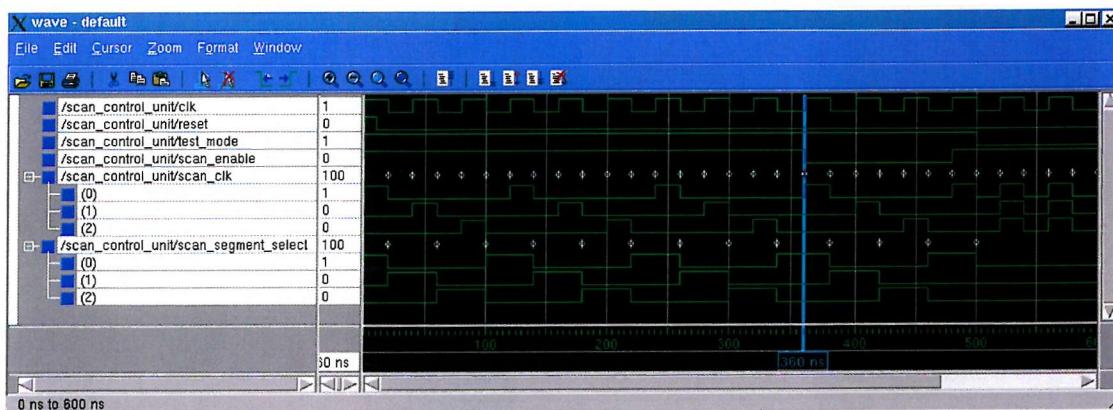

| 4.7  | Simulation waveforms for the symmetric Golomb decompression unit                    | 92  |

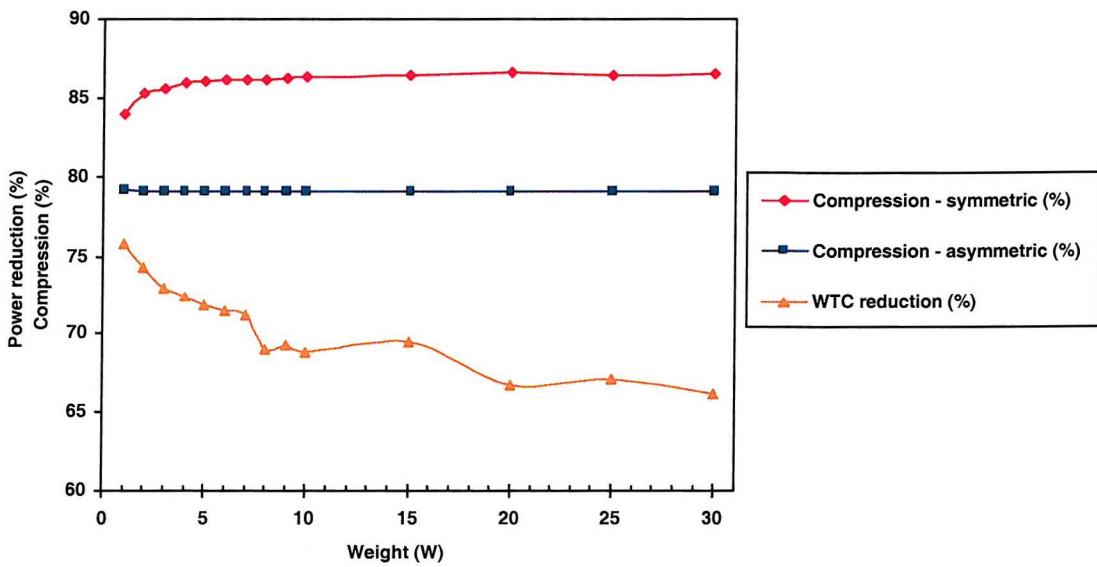

| 4.8  | Experimental results for circuit s13207                                             | 100 |

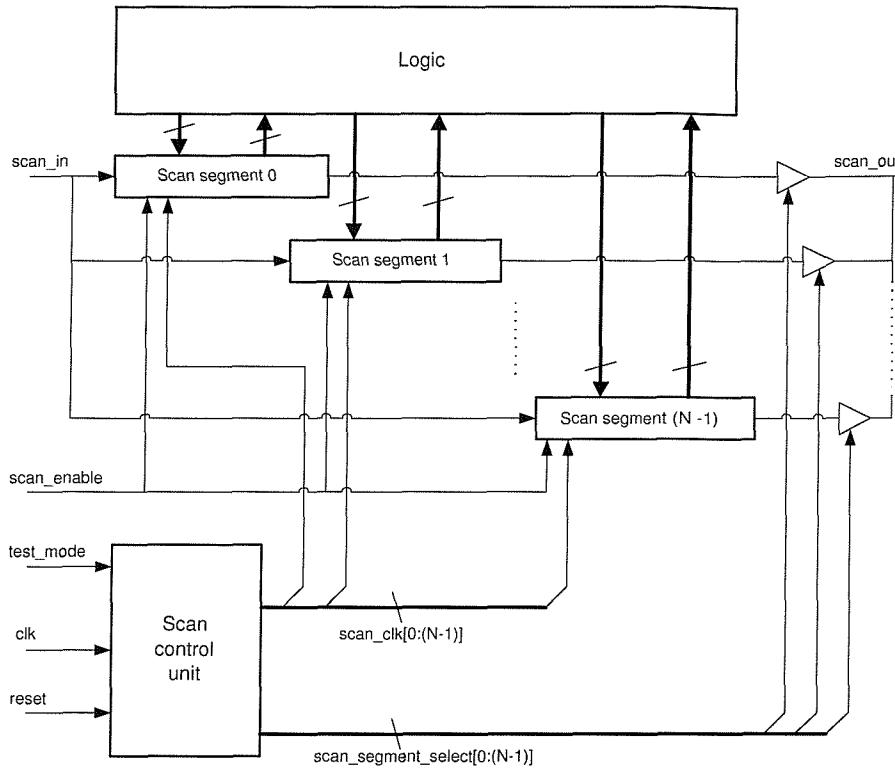

| 5.1  | Scan architecture with mutually exclusive scan segment activation                   | 107 |

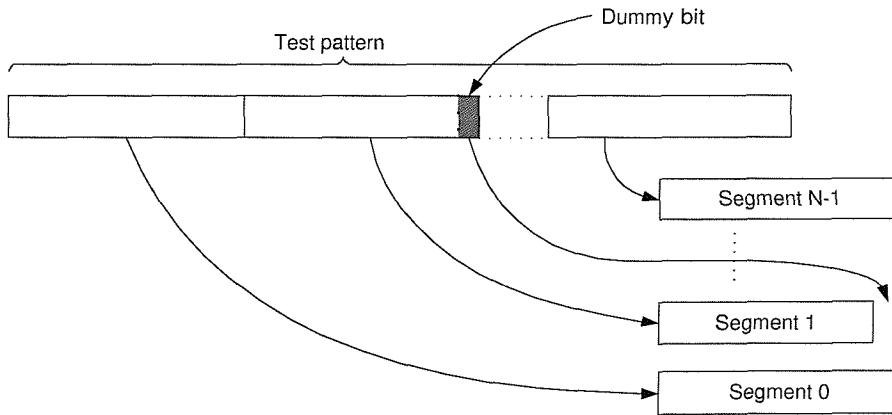

| 5.2  | Compensating length differences among scan segments                                 | 107 |

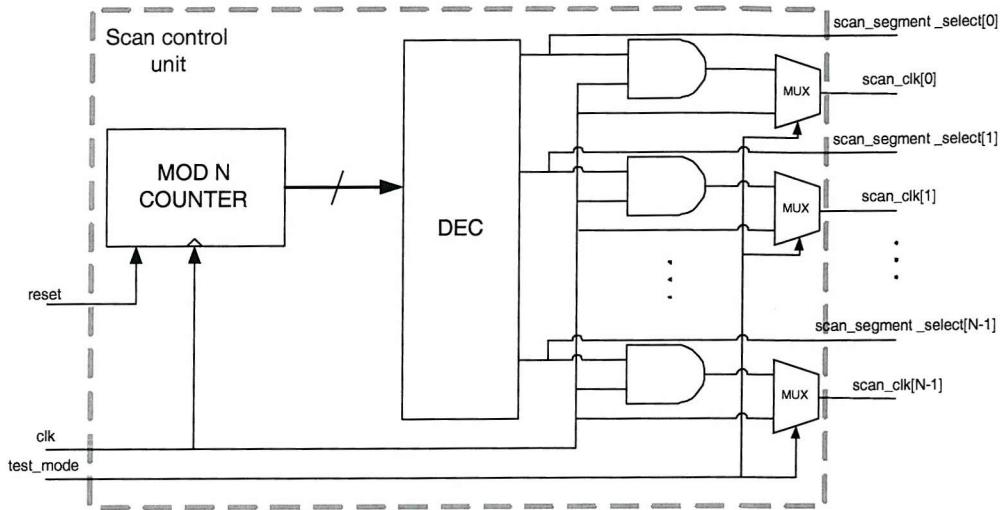

| 5.3  | Control unit for low power scan chain architectures                                 | 109 |

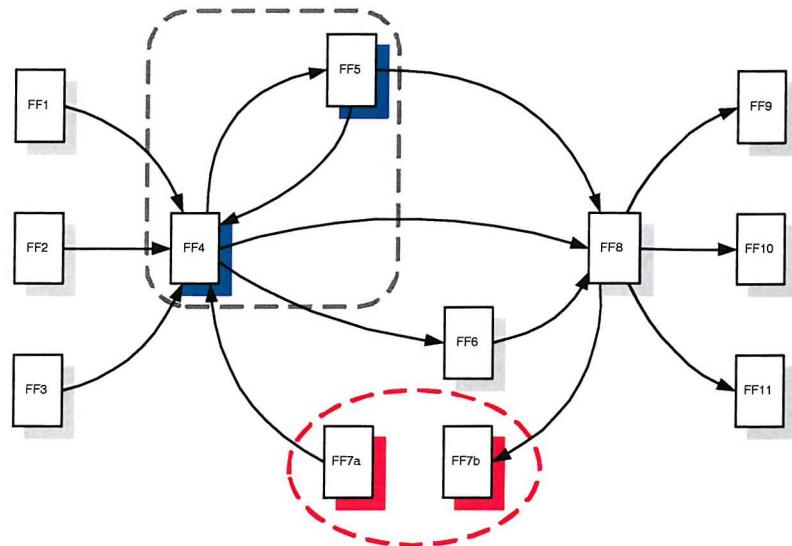

| 5.4  | Capture violation example                                                           | 111 |

| 5.5  | Structural dependency graph                                                         | 112 |

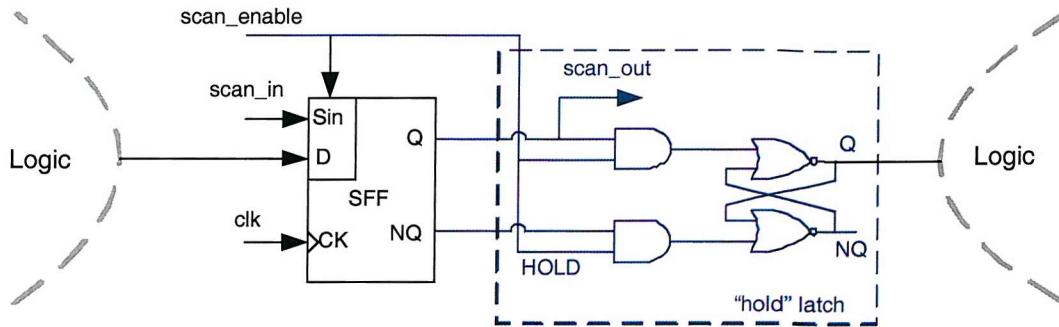

| 5.6  | Implementing an extended node using an extra scan flip-flop                         | 114 |

| 5.7  | Implementing an extended node using a scan-hold flip-flop                           | 115 |

| 5.8  | Breaking the largest strong component                                               | 117 |

| 5.9  | Scan segments                                                                       | 117 |

| 5.10 | Low power multiple scan chain architecture                                          | 119 |

| 5.11 | Average trends for average power and number of extended nodes                       | 123 |

| 5.12 | Average trends for maximum number of transitions per clock                          | 125 |

| B.1  | Schematic of the synthesised FSM for symmetric Golomb codes and Golomb group size 4 | 147 |

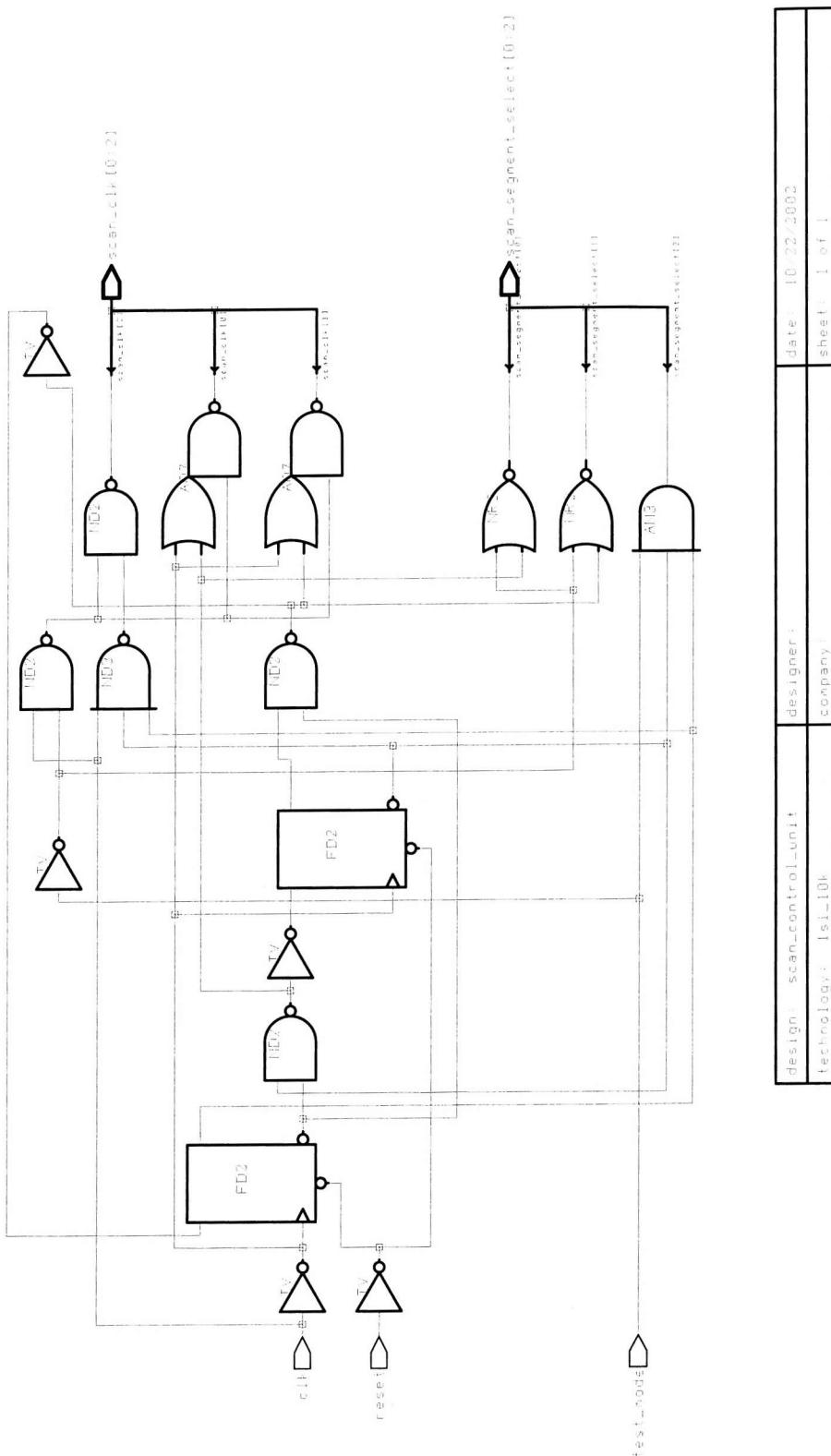

| C.1  | Schematic of the synthesised scan control unit for three scan segments              | 158 |

# List of Tables

|     |                                                                                                                                                                                            |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Approximation accuracy improvement for test-per-clock and test-per-scan testing schemes . . . . .                                                                                          | 49 |

| 2.2 | Experimental results for the test-per-clock testing scheme (ISCAS85 benchmarks) . . . . .                                                                                                  | 50 |

| 2.3 | Experimental results for the test-per-scan testing scheme (ISCAS89 benchmarks) . . . . .                                                                                                   | 50 |

| 3.1 | Comparison between the proposed dual MP-LFSR TPG and the traditional single MP-LFSR TPG [HRT <sup>+</sup> 95] in terms of scan-in transition count and average power dissipation . . . . . | 71 |

| 3.2 | Comparison between the proposed dual MP-LFSR TPG and the traditional single MP-LFSR TPG [HRT <sup>+</sup> 95] in terms of area overhead                                                    | 72 |

| 3.3 | Comparison between the proposed dual MP-LFSR TPG and the traditional single MP-LFSR TPG [HRT <sup>+</sup> 95] . . . . .                                                                    | 77 |

| 3.4 | Comparison between the proposed dual MP-LFSR TPG and the traditional single MP-LFSR TPG [HRT <sup>+</sup> 95] . . . . .                                                                    | 78 |

| 3.5 | Comparison between the proposed dual MP-LFSR TPG and the traditional single MP-LFSR TPG [HRT <sup>+</sup> 95] . . . . .                                                                    | 79 |

| 4.1 | Golomb codes for group size $g = 4$ . . . . .                                                                                                                                              | 85 |

|     |                                                                                   |     |

|-----|-----------------------------------------------------------------------------------|-----|

| 4.2 | Asymmetric and symmetric Golomb codes for group size 4 . . . . .                  | 88  |

| 4.3 | Experimental results . . . . .                                                    | 100 |

| 5.1 | Average power dissipation vs. the number of scan segments . . . . .               | 121 |

| 5.2 | Number of extended nodes vs. the number of scan segments . . . . .                | 121 |

| 5.3 | Maximum number of transitions per clock vs. the number of scan segments . . . . . | 124 |

| D.1 | The ISCAS85 benchmark suite . . . . .                                             | 160 |

| D.2 | The ISCAS89 benchmark suite . . . . .                                             | 161 |

# Acknowledgements

This PhD project would have not been possible without the support, encouragement and guidance of my supervisor Dr. Bashir Al-Hashimi. I would also like to thank him for his help during the preparation of this thesis and all my publications. I am grateful for the funding and research facilities provided by the Electronics and Computer Science Department of Southampton University, which made possible the work presented in this thesis. Dr. Mark Zwolinski also deserves thanks for his constructive comments during my nine-month and MPhil transfer examinations.

My friend and colleague Dr. Nicola Nicolici deserves thanks for his guidance, feedback and supervision throughout my PhD. I would also like to thank the Department of Electrical and Computer Engineering of McMaster University for providing the necessary research facilities for the three month period I have spent as a visiting researcher at McMaster University.

The encouragements and tolerance of my friends have helped me greatly through this PhD programme. This people include: Marcus, Mauricio, Matheos, Neil, Mircea and others. Special mention deserves Theo Gonciari for his substantial feedback on technical and non-technical matters.

Finally, I would like to thank my mother Ileana, my father Peter and my grandfather Pista for their love and continuous support over the past three years. Pista should be also thanked for persuading me to engage into this PhD.

# Chapter 1

## Introduction

The rapid advancements in process technologies have enabled the fabrication of chips with tens of millions of transistors operating at frequencies in the gigahertz range. While these advances brought unprecedented performance to electronic products, they also turn effects until recently ignored, such as power dissipation and resistive voltage drop, into critical issues which have to be addressed by integrated circuit design methodologies [Bis02, Gre99].

Significant research has been devoted to the power-related challenges in integrated circuit (IC) design. As a result, several industry leading design tools provide power optimisation, analysis and characterisation capabilities [Syn01c, Gra00a, Cad02]. While power optimisation has become almost a push-button design step, the gap between the design and test camps left unsolved the power issues associated with the IC test process. In most cases, the behaviour of the circuit under test is significantly different than during its normal operation mode due to the different scopes of the two modes. On one hand, low power design techniques [CB95, RP96, Yea98, Ped96] try to shut down all unnecessary blocks during the normal operation of the circuit in order to extend battery life, cut down cooling costs, etc. On the other hand, test scheduling algorithms increase the number of blocks which are tested in parallel in order to reduce test time. The conflicting perspectives of design for testability (DFT) and low power design methodologies make test power

a critical design issue. Ignoring power during test may have serious consequences on reliability and yield [BA00, Zor93, SBW01, Whe00].

This thesis addresses the problem of testing digital ICs under power constraints. Various scenarios at system and gate level are investigated with the ultimate goal of developing power conscious DFT methodologies.

This chapter begins with an overview of the test process and of the main DFT techniques. It continues with a section on power dissipation in VLSI circuits outlining the sources of power dissipation and the mostly used power optimisation design techniques. The motivation of the work presented in this thesis is built by explaining the power issues associated with the test process. The chapter concludes with an outline of the thesis and its contributions.

## 1.1 The Test Process and Design for Testability

The main purpose of the IC test process is to provide a measure of the quality and reliability of a semiconductor stand-alone die or packaged part. *Functional testing* verifies that the circuit performs correctly the intended function it was designed for, over a range of input values. However, the time for exhaustively testing all possible input combinations grows exponentially with the number of inputs. To maintain a reasonable test time, the functional test must focus on the general function and corner cases. *Manufacturing testing* verifies the circuit for manufacturing defects by focusing on circuit structure rather than functional behaviour. Manufacturing defects include problems such as power and ground shorts, open interconnect on the die caused by dust particles, short-circuited source or drain of the transistor caused by metal spike-through, etc. Manufacturing defects might remain undetected by functional testing yet cause undesirable behaviour during circuit operation. Manufacturing test enables the screening out of devices with such structural defects.

### 1.1.1 Fault Models

When a manufacturing defect occurs, the physical defect has a logical effect on the behaviour of the circuit. For example, a signal shorted to power appears to be permanently high, while a signal shorted to ground appears to be permanently low. *Fault models* increase test generation efficiency by mapping controllable and observable physical defects to mathematical constructs that can be operated upon algorithmically and understood by a software simulator in order to provide a metric for quality measurement.

A fault model is a description of the behaviour and assumptions of how elements in a defective circuit behave. The goal of fault modelling is to model a high percentage of the physical defects that occur in the device at the highest possible level of abstraction. The high level of abstraction reduces the number of individual defects that must be considered and lowers the complexity of the algorithms used in generating the test. The result is that test generation can occur earlier in the design cycle in less time with less expensive computing resources [Gar01].

The gate-level model is widely accepted as the best compromise between abstraction level and the ability to represent most of the defects in the circuit under test (CUT). Register-transfer level (RTL) modelling is too abstract to accurately represent many of the fault types, and switch-level modelling is too computation-intensive [Gar01].

A commonly used metric for quality assessment of digital circuits is the *fault coverage*, given by the ratio:

$$F_{cov} = \frac{N_{DF}}{N_F - N_{UDF}},$$

where  $N_{DF}$  is the number of detected faults,  $N_F$  is the total number of faults, and  $N_{UDF}$  is the number of undetectable faults.

The *single stuck-at fault model* (SSAF) is the most popular fault model, first pub-

lished in 1961 [Rot61]. It makes the assumption that only one line in the circuit is faulty at one time and that the fault is permanent. The effect of the fault is the same as if the faulty node is tied to  $V_{dd}$  (logical 1) or  $Gnd$  (logical 0), while the other gates in the circuit are not affected by the fault. The SSAF model covers many of the possible manufacturing defects in CMOS circuits, such as missing features, source-drain shorts, diffusion contaminants and metallisation shorts. The International Technology Roadmap for Semiconductors 1999 (ITRS) [Gro99] indicates that SSAF covers about 70% of the possible manufacturing defects in CMOS circuits. However, recent research [SM00] has shown that N-detect test sets for SSAF are very effective for both timing and hard failures. Algorithms for automatic test pattern generation (ATPG) and fault simulation on combinational networks with SSAF are well developed and efficient [BA00, ABF90].

The *multiple stuck-at fault model* (MSAF) [Gar01] makes the same basic assumptions as SSAF, except that it allows two or more lines in the circuit to be faulty at the same time. Although MSAF covers a greater number of defects, it also increases the number of faults which must be analysed under this approach:  $3^n - 1$  for  $n$  circuit nodes. Furthermore, algorithms for ATPG and fault simulation are much more complex and not as well developed, and commercial simulators do not support MSAF well. Therefore, MSAF fault simulation is rarely used.

The *stuck-open fault model* (SOF) [Gar01] assumes that a single physical line in the circuit is broken and that the resulting open node is not tied to either  $V_{dd}$  or  $Gnd$ . The advantage of this approach is that it covers defects that can not be detected by SSAF and MSAF models but that can be tested with pairs of SAF test vectors.

Even if the circuit does not have a logical defect, it may have some physical defect, such as a process variation, that creates a large enough gate delay to cause problems. The *transition-delay fault model* [Gar01] assumes that the logic function of the circuit under test is error free but that a gate output may be slow to rise or slow to fall and that this time is longer than a required value. If this delay is large enough, the transition-delay fault behaves as a SAF and can be modelled using

that method. The primary weaknesses of the transition-fault delay are that two pattern sequences are needed for initialisation and transition detection, and the minimum delay fault size is difficult to determine because of timing hazards.

The *path-delay fault model* [Gar01] is similar to the transition-delay model in assuming that the logic of the circuit under test is error-free. However, instead of modelling the fault as if a single gate delay in the circuit is faulty, this model assumes that the total delay in a path from input to output exceeds some maximum value. The path-delay fault model overcomes a possible problem with the transition-delay model, in which other faster gates in the circuit may compensate for the delay of a faulty gate. A problem with this fault model is that the number of possible paths grows exponentially with the number of nets.

From the above discussion on fault models it may be concluded that there is no universal fault model to cover all possible physical defects. This conclusion is also supported by the results of the experimental work presented in [SM00]. Each of the fault models presented is valuable in certain situations yet also has limitations. For each application, designers have to determine the fault model or, more likely, the combination of fault models which will provide a satisfactory level of defect coverage. The DFT techniques proposed in this thesis, unless otherwise specified, are targeting testing for stuck-at faults, due to the efficiency and wide industrial acceptance of this fault model.

### 1.1.2 Fault Simulation

Fault simulation determines the fault coverage of a set of test vectors. It can be thought of as performing several logic simulations concurrently - one that represents the fault-free circuit, and the rest that represent the circuits containing faults. A fault is detected each time the output response of the faulty machine differs from the output response of the good machine for a given vector. Fault simulation produces a list of detected faults for each test vector. Fault simulation is useful for determining the fault coverage when the manufacturing test vectors

are generated manually or using existing hardware test pattern generators such as linear feedback shift registers (LFSR), etc. For large or complex designs, fault simulation can be very time consuming and often the test sets do not give good fault coverage.

### 1.1.3 Automatic Test Pattern Generation

Automatic test pattern generation (ATPG) generates test patterns and provides fault coverage statistics for the generated pattern set. ATPG for combinational circuits is well understood, and consequently, in most cases, it is possible to generate test sets with high fault coverage.

Combinational ATPG tools use both random and deterministic techniques to generate test patterns for faults on cell pins [BA00, ABF90]. During random pattern generation, the tool assigns input stimulus in a pseudo-random manner, then it performs fault simulation on the generated vector to determine which faults are detected. As the number of faults detected by successive random patterns decreases, ATPG shifts to a deterministic phase. During the deterministic pattern generation phase, the tool uses a pattern generation algorithm based on path sensitivity concepts to generate a test vector that detects a specific fault in the design. After generating a vector, the tool fault-simulates the vector to determine the complete set of faults detected by the vector. Test pattern generation continues until all faults have either been detected or have been identified as undetectable by this algorithm.

Due to the effects of memory and timing, ATPG for sequential circuits is much more difficult than for combinational circuits. Often, it is not possible to generate high fault coverage test sets for complex sequential designs, even when using sequential ATPG. Sequential ATPG tools use deterministic pattern generation algorithms based on extended applications of the path-sensitivity concepts [BA00, ABF90].

Structural DFT techniques, such as internal scan, simplify the test-pattern gen-

eration task for complex sequential designs, resulting in higher fault coverage and reduced testing costs.

### 1.1.4 Internal Scan

Internal scan design is the most popular DFT technique and has the greatest potential for achieving high fault coverage [BA00]. This technique simplifies the pattern generation problem by dividing complex sequential designs into fully isolated (full-scan design) or semi-isolated combinational blocks (partial-scan design). Internal scan modifies existing sequential elements in the design to support a serial shift capability in addition to their normal functions. This serial shift capability enhances internal node controllability and observability with a minimum of additional I/O pins.

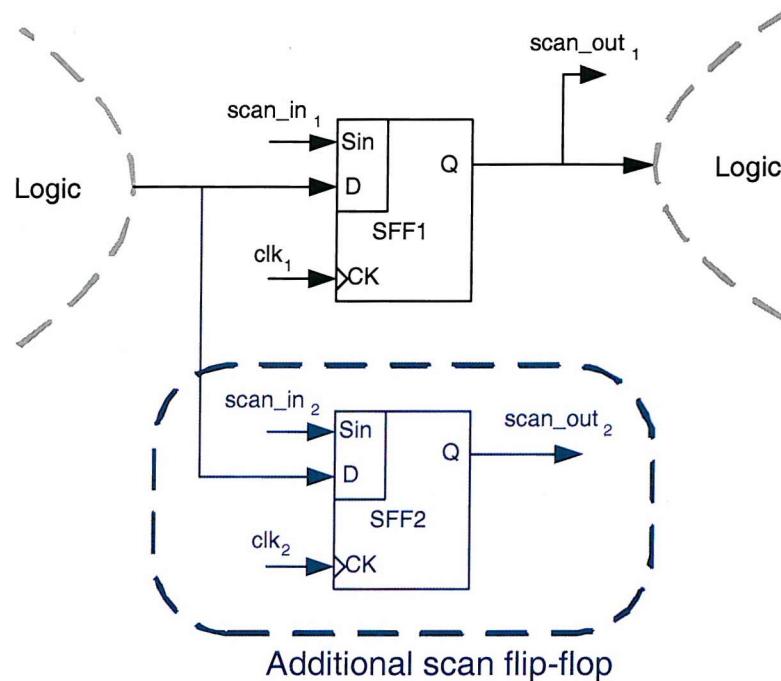

Figure 1.1 shows a D flip-flop modified to support internal scan. Inputs to the multiplexer are the data input of the flip-flop (D) and the scan input signal (scan\_in). The active input of the multiplexer is controlled by the scan-enable signal (scan\_enable). Input pins are added to the cell for the scan\_in and scan\_enable signals. One of the data outputs of the flip-flop is used as the scan output signal (scan\_out). The scan\_out signal is connected to the scan\_in signal of another scan cell to form a serial scan (shift) capability.

Figure 1.1: D flip-flop with scan capability

The modified sequential cells are chained together to form one or more large shift

registers. These shift registers are called scan chains or scan paths. The sequential cells connected in a scan chain are scan controllable and scan observable. A sequential cell is scan controllable when it can be set to a known state by serially shifting in specific logic values. ATPG tools consider scan controllable cells as pseudo-primary inputs of the combinational part of the design. A sequential cell is scan observable when its state can be observed by serially shifting out data. ATPG tools consider scan observable cells as pseudo-primary outputs of the combinational part of the design.

Adding scan circuitry to a design usually has the following effects:

- Design size and power increase slightly because scan cells are usually larger than the non-scan cells they replace, and the nets used for the scan signals use additional area.

- Design performance (speed) decreases marginally because of changes in the electrical characteristics of the scan cells that replace the non-scan cells.

- Global test signals that drive many sequential elements might require buffering to prevent electrical design-rule violations.

Test patterns are applied to a scan-based design through the scan chains. The process is the same for full-scan and partial-scan designs. Scan cells operate in one of two modes: parallel mode (or capture mode) or shift mode. For the multiplexed flip-flop scan style shown in Figure 1.1, the mode is controlled by the `scan_enable` pin. In parallel mode, the input to each scan element comes from the combinational logic block. In shift mode, the input comes from the output of the previous scan cell or a scan input port. Other scan styles work in a similar fashion.

To apply a scan pattern, the target tester performs the following steps:

1. Selects shift mode by setting the `scan_enable` port. This test signal is connected to all scan cells.

2. Shifts in the input stimulus for the scan cells (pseudo-primary inputs) at the scan input ports.

3. Selects parallel mode by inverting the scan-enable port.

4. Applies the input stimulus to the primary inputs.

5. Checks the output response at the primary outputs after the circuit has settled and compares it to the expected fault-free response. This process is called parallel measure.

6. Pulses one or more clocks to capture the steady-state output response of the non-scan logic blocks into the scan cells. This process is called parallel capture.

7. Selects shift mode by resetting the scan-enable port.

8. Shifts out the output response of the scan cells (pseudo-primary outputs) at the scan output ports and compares the scan cell contents to the expected fault-free response.

### 1.1.5 Full-Scan Design vs. Partial-Scan Design

In the full-scan design technique, all sequential cells in the design are modified to perform a serial shift function. Sequential elements that are not scanned are treated as black box cells (cells with unknown function).

Full-scan divides a sequential design into combinational blocks as shown in Figure 1.2. Clouds represent combinational logic; rectangles represent sequential logic. The full-scan diagram shows the scan path through the design.

Through pseudo-primary inputs, the scan path enables direct control of inputs to all combinational blocks. Through pseudo-primary outputs, the scan path enables direct observation of outputs from all combinational blocks. Efficient combinational ATPG algorithms can be used to generate test sets with high fault coverage for the full-scan design.

In the partial-scan design technique, the scan chains contain only a fraction of the sequential cells in the design. The partial-scan technique offers a trade-off

Figure 1.2: Scan path through a full-scan design

between the maximum achievable fault coverage and the effect on design size and performance [ABF90, Syn01b]. For example, flip-flops on the critical paths of designs with limited timing budget cannot be replaced with scan cells as the cell multiplexer would increase the overall delay of the design. Partial-scan divides a complex sequential design into simpler sequential blocks, as shown in Figure 1.3. The partial-scan diagram shows the scan path through the design.

Sequential ATPG algorithms are needed for partial-scan designs to allow fault propagation through non-scan sequential elements. In general, a partial-scan design can not achieve the fault coverage of the full-scan version of the design. The level of fault coverage for a partial-scan design is related to the location and fraction of scan registers in that design. Moreover, sequential ATPG algorithms are much more complex than combinational ATPG algorithms [BA00, ABF90].

Figure 1.3: Scan path through a partial-scan design

### 1.1.6 Automatic Test Equipment

Automatic test equipment (ATE) is an instrument used to apply test patterns to a device under test (DUT) (also referred to as circuit under test (CUT)), analyse the responses from the DUT, and mark the DUT as good or bad [BA00]. The ATE is controlled by a central computer, and one or more CPUs are built into it to ease control and to enable test data compression. The tester has one or more test heads, which contain buffering electronics local to the DUT, but one mainframe with common instrumentation, power supplies, etc. The ATE is connected to external equipment that mechanically handles the wafers or IC packages being tested. The ATE, unlike a simulator, can operate only at the edge of the design through the package pins, and has real signal and clock delays and signal degradations, chip output loads and thermal considerations. The tester also has edge placement precision, accuracy, and edge-rate (rise and fall time) limitations.

The main component of the cost-of-test is the time a chip spends “in-socket” on the ATE. There is a minimum cost based on the time it takes an automated handler to insert and remove a chip from the tester socket (production throughput). For

a typical ATE, the test cost per second is about \$0.11 [BRCA01]. Cost reductions to bring the tester time below the handler threshold require testing multiple dies in parallel with the same tester. If the test programs applied on the tester are excessively complex or contain an excessive amount of vector data, then a vector reload may be required. A reload adds a large time overhead to the overall testing process, which increases the “in-socket” time, and consequently the cost of test.

### 1.1.7 Built-in Self-Test

There is an increasing number of testability problems posed by the increasing complexity of modern chips. The rising logic-to-pin ratio makes it harder to accurately observe signals on the device. VLSI devices are increasingly dense and faster with the emerging deep submicron feature sizes. The time needed to generate and apply test patterns to these chips, as well as the volume of test data which has to be stored on the tester are also increasing. The growing gap between chip internal frequencies and the I/O frequencies makes it very difficult, if not impossible, to perform at-speed testing using external ATE [BA00]. Built-in self-test (BIST) represents a viable solution to most of these problems. BIST moves test pattern generation and test response analysis from the tester to the chip under test. Thus, at the expense of one to three percent area overhead, BIST eliminates the problems associated with the limited pin count and I/O bandwidth.

Figure 1.4: Typical BIST scheme

Figure 1.4 shows typical BIST hardware. In test mode, the test controller connects the inputs of the circuit under test to the hardware pattern generator through the input multiplexer. The hardware pattern generators are also referred to as test pattern generators (TPG). The output response compactor transforms the output of the circuit under test into signatures which are compared with reference signatures stored in a ROM.

The most commonly used hardware pattern generators [BA00] include:

1. **ROM.** A precomputed test set is stored in a ROM on the chip. This approach is prohibitively expensive in terms of chip area.

2. **LFSR.** Linear feedback shift registers are used to generate pseudo-random tests. The advantage of this approach is the very low area requirements, however very long test sequences (1 million or more test vectors) are required in order to obtain good fault coverage.

3. **Binary counters.** Binary counters are used to generate pseudo-exhaustive test sequences (the pattern generator is built of several smaller binary counters, each producing an exhaustive sequence at its outputs). The binary counter approach requires more hardware than the LFSR pattern generator.

4. **Modified counters.** Modified counters have also been successful as test pattern generators, but they also require long test sequences for good fault coverage.

5. **LFSR and ROM.** This is one of the most effective approaches, which uses an LFSR to generate a limited number of pseudo-random test vectors to cover the easy-to-detect faults, and generates deterministic test patterns using an ATPG tool for the few remaining random-pattern-resistant faults. The deterministic patterns are embedded in the output of the LFSR, by reseeding the LFSR with values stored in the ROM, in order to augment the fault coverage. This approach is also known as *mixed-mode BIST* because it uses both pseudo-random and deterministic test vectors [HWH96].

6. **Cellular automaton.** In this approach, each pattern generator cell has a few logic gates, a flip-flop, and connections only to neighbouring cells. The cell is replicated to produce the cellular automaton.

Figure 1.5: BIST schemes

BIST schemes can be classified into *test-per-clock* (Figure 1.5(a)) and *test-per-scan* schemes (Figure 1.5(b)) according to the method used to apply the test patterns to the CUT. In test per-clock BIST, the outputs of the TPG are connected directly to the CUT inputs and a new test pattern is applied to the CUT with every test clock. In a test-per-scan BIST scheme, the test patterns generated by the TPG are applied to the CUT via one or more internal scan chains, and hence a test pattern is applied to the CUT every  $m+1$  test clocks cycles, where  $m$  is the number of flip-flops in the scan chain. The test response of the CUT is captured in the scan chain and scanned-out during the next  $m$  clock cycles simultaneously with scanning-in of the next test vector. Usually test-per-clock schemes are preferred for memory test, due to their regular structure which makes them easily controllable from the primary input pins, while test-per-scan schemes are commonly used for testing random logic blocks.

## 1.2 Power Dissipation in Digital VLSI Circuits

Battery life, packaging and cooling costs, reliability are all factors which justify the need for low power design [Ped96]. This section will provide background information on the main sources of power dissipation in digital VLSI circuits, as well as

an overview of existing power optimisation techniques. The information provided in this section will be used later in this chapter to explain the conflict between the current DFT techniques and low power design.

### 1.2.1 Sources of Power Dissipation in Digital VLSI Circuits

The power dissipated in a circuit falls into two broad categories: *static power* and *dynamic power* [Ped96].

Figure 1.6: Components of power dissipation

*Static power* is the power dissipated by a gate when it is not switching, that is, when it is inactive or static. The largest fraction of static power results from source-to-drain subthreshold leakage, which is caused by reduced threshold voltages that prevent the gate from completely turning off. Static power is also dissipated when current leaks between the substrate and the diffusion layers.

*Dynamic power* is the power dissipated when the circuit is active. A circuit is active anytime the voltage on a net changes due to some stimulus applied to the circuit. Because voltage on an input of a cell can change without necessarily

resulting in a logic transition on the output, dynamic power is dissipated by the internal transistors of the cell which are switching even when an output net does not change its logic state. The dynamic power of a circuit is composed of two kinds of power: *switching power* and *internal power* [Syn01c].

The switching power of a driving cell is the power dissipated by the charging and discharging of the load capacitance at the output of the cell. The total load capacitance at the output of a driving cell is the sum of the net and gate capacitances on the driving output. Because such charging and discharging are the result of the logic transitions at the output of the cell, switching power increases as logic transitions increase. Therefore, the switching power of a cell is a function of both the total load capacitance at the cell output and the rate of logic transitions. Switching power comprises a large percentage of the power dissipation of an active CMOS circuit. The switching power ( $P_c$ ) is given by:

$$P_c = \frac{V_{dd}^2}{2} \sum_{\forall_{nets(i)}} C_{loadi} \times TR_i \quad (1.1)$$

where  $C_{loadi}$  is the capacitive load of net  $i$ ,  $TR_i$  is the toggle rate of net  $i$  as number of transitions per second, and  $V_{dd}$  is the supply voltage.

Internal power is any power dissipated within the boundary of a cell. During switching, a circuit dissipates internal power by the charging or discharging of any existing capacitances internal to the cell. Internal power includes power dissipated by a momentary short circuit between the P and N transistors of a gate, called short-circuit power. To illustrate the cause of the short-circuit, consider the simple gate shown in Figure 1.6. As the IN signal transitions from low to high, the N type transistor turns on and the P type transistor turns off. However, for a short time, both the P and N transistors can be on simultaneously. During this time, current  $I_{sc}$  flows from  $V_{dd}$  to  $GND$ , causing the dissipation of short-circuit power. For circuits with fast transition times, short-circuit power can be small. However, for circuits with slow transition times, short-circuit power can account for 30 percent

of the total power dissipated by the gate [Syn01c]. Short-circuit power is affected by the dimensions of the transistors and the load capacitance at the output of the cell [Syn01c]. The internal power of a cell is the sum of the internal power of all of the cell's inputs and outputs as modelled in the technology library.

Figure 1.7: Simple cell

For the simple cell shown in Figure 1.7, internal power can be estimated as follows:

$$\begin{aligned}

P_{int} &= E_Z \times TR_Z & (1.2) \\

E_Z &= f(C_{load}, \text{WeightAvg}(\text{Trans})) \\

\text{WeightAvg}(\text{Trans}) &= \frac{\sum_{i=A,B} TR_i \times \text{Trans}_i}{\sum_{i=A,B} TR_i}

\end{aligned}$$

where  $E_Z$  is the internal energy for output  $Z$  as a function of input transitions and output load (usually defined in the technology library),  $TR_Z$  is the toggle rate of output pin  $Z$ ,  $TR_i$  is the toggle rate of input pin  $i$ ,  $\text{Trans}_i$  is the transition time of input  $i$ , and  $\text{WeightAvg}(\text{Trans})$  is the weighted average transition time for output  $Z$ .

### 1.2.2 Effects of Excessive Power Dissipation

Power dissipation in a VLSI circuit is usually described in terms of its average and peak values. High average power means a high power consumption sustained for a long period of time. This has the following negative effects on the VLSI device: shortens battery life for mobile applications, increases chip temperature with the risk of exceeding the maximum value tolerated by the package, speeds-up

electro-migration, hence leading to reliability problems. High peak power can lead

Figure 1.8: Voltage (IR) drop

to a drop in power supply voltage, called voltage drop or IR drop. As shown in Figure 1.8, IR drop occurs because of the high instantaneous current  $I_{\text{dd}}$  flowing through the resistive power network. Its value depends on the resistance  $R_{\text{line}}$  of the power net, the power grid architecture, the power pad locations and the current drawn by standard cells connected to power net [Bis02]. Thus, for a circuit with a given power grid, the value of the instantaneous current is given by the number of cells which are switching simultaneously. Power net voltage drop affects the performance of a design by increasing cell and interconnect delay. IR drop also reduces noise margins of cells and increases the probability of failures due to crosstalk noise.

### 1.2.3 Low Power Design

In order to address the challenges posed by the increasing power requirements, various power optimisation methods have been developed [Ped96]:

- **Scaling the supply voltage:** This approach can be very effective in reducing the power dissipation, but often requires new IC fabrication processing.

Supply voltage scaling also requires support circuitry for low-voltage operation including level-converters and DC/DC converters as well as detailed consideration of issues such as signal-to-noise margins.

- **Employing better design techniques:** This approach promises to be very successful because the investment to reduce power by design is relatively small in comparison to other approaches. The most popular solution, adopted by most major synthesis tools is RTL clock gating, which basically ensures that each sequential part of the design is clocked only when it is necessary [Syn01c].

- **Using power management strategies:** The power savings that can be achieved by various static and dynamic power management techniques are very application dependent, but can be significant [BBM00].

### RTL Clock Gating

One of most efficient design technique for reducing dynamic power, already provided by most popular commercial synthesis tools, is *RTL clock gating*. RTL clock gating works by identifying groups of flip-flops which share a common enable term (a term which determines that new values will be clocked into the flip-flops). Traditional methodologies use this enable term to control the select on a multiplexer connected to the D port of the flip-flop or to control the clock enable pin on a flip-flop with clock enable capabilities. RTL clock gating uses this enable term to control a clock gating circuit which is connected to the clock ports of all of the flip-flops with the common enable term. Therefore, if a bank of flip-flops which share a common enable term have RTL clock gating implemented, the flip-flops will consume zero dynamic power as long as this enable term is false. The following example shows how RTL clock gating works.

**Example 1** Consider the two pipelined 3-bit counters shown in Figure 1.9. The two counters share the same clock signal (CLK). The overflow pre-condition for COUNTER 1 (all three bits high) is used to trigger the increment of COUNTER 2.

Figure 1.9: Two-counter sample design

*Each of the two counters increments on every clock cycle when its corresponding increment signal, INCR1 and INCR2 respectively, is asserted high. As the clock signal is routed directly to both counters, which means that they will be clocked continuously, with the old data recirculated into their flip-flops when the INCR1 and INCR2 signals are low. It should be noted that flip-flops consume power even if their inputs, and therefore, their internal state, do not change. Assuming that INCR1 is held permanently high, COUNTER 1 will increment with every clock while COUNTER 2 will increment only once every 8 clocks, although it will consume power during each clock cycle.*

*In Figure 1.10, the same circuit is implemented using clock gating. This implementation is similar to the previous one except that two clock gating elements have been inserted into the clock network, which cause the counters to be clocked only when their corresponding increment signals are high. As the increment conditions for the two counters are now used to enable their clocks, when the increment signals are asserted low, the counters are not clocked and hence, they retain their content just like the implementation without clock gating. The difference is that instead of having the two counters clocked every clock cycle and hence, consuming power even if their content does not change, in the optimised implementation, the counters are clocked only when they have to be incremented. Therefore the situation when the two counters are clocked simultaneously occurs only once every 8 clocks, assuming INCR1 is held permanently high.*

Figure 1.10: Implementation of the two-counter design with clock gating

As illustrated in the previous example, clock gating is a very efficient design technique for reducing the useless switching activity on-chip. Industrial experiences report dynamic power reductions ranging from 50% to 70% achieved through clock gating [EB00].

### 1.3 Power Issues Affecting the Test Process

As reported in [Zor93], power dissipation during test can be up to three times higher than during normal operation. This section will explain why power consumption tends to be significantly higher during test than during normal operation and what are the problems deriving from that.

The behaviour of a device in test mode is substantially different than its behaviour during normal operation. This is due the different scopes of the two modes. There are two major problems which will be discussed in the following.

- The first problem originates from the contradiction between the goals of system-level power reduction techniques and test scheduling algorithms. Consider, for example, high-performance memory systems. Memories are organised into several blocks of fixed sizes. Under normal system operation, only one memory block is active during each memory access while other blocks are in power down mode to minimise power consumption. During test however,

in order to test the memory in the shortest possible time, it is desirable to activate as many memory blocks as possible. Another example is testing of multi-chip modules (MCM) [CSA97]. An attractive approach is to use BIST blocks executing in parallel. This approach reduces significantly the overall testing time but also increases power dissipation during test, while during normal operation not all blocks are activated simultaneously and hence, the inactive blocks do not contribute to power dissipation. There are several reasons why the overall testing time should be kept as short as possible. One is to ensure that the ATE does not de-calibrate before the end of the test session. Another reason is to increase the testing throughput in the case of mass production [BA00]. Based on the facts mentioned above, aggressive test scheduling algorithms which ignore power, may lead to chip overheating. This is extremely undesirable, especially during early production tests performed on the unpackaged dies.

- The second problem arises from the conflict between RTL clock gating and scan testing. This will be explained through the following example.

**Example 2** Consider the implementation using clock gating of the two-counter design from example 1 in section 1.2.3 (Figure 1.11). The design after scan insertion is shown in Figure 1.12, assuming a full-scan configuration and multiplexed scan style for the scan cells [Syn01b]. Scan insertion has chained all flip-flops in the design into a long shift register. During test, the test enable signal (`test_en`) is asserted high, hence the clock is enabled simultaneously for all flip-flops, by disabling the effect of the clock gating logic. The scan enable signal (`test_se`) puts the scan chain into the "shift" (`test_se = 1`) or "capture" mode (`test_se = 1`). As the clock is globally enabled during the test mode, all six flip-flops in the design will be clocked every test clock, and hence the design will consume much more power than during normal operation. As stated in Example 1 in section 1.2.3, during normal operation all flip-flops are clocked simultaneously only once every 8 clocks, assuming `INCR1` is held permanently high.

Figure 1.11: Implementation of the two-counter design with clock gating

As shown in the previous example, during testing, a much larger part of the circuit is switching during each clock compared to normal operation. The high current drawn from the power lines by the increased number of simultaneously switching circuit nodes may produce high voltage drops, which would not occur during the normal operation mode. If the amplitude of the voltage drop exceeds the noise margins tolerated by the circuit, one of the following situations can occur:

1. the test stimulus and/or circuit response is corrupted, if the high voltage drop occurs during the shift cycles.

2. the scan chain will capture an erroneous circuit response, if the high voltage drop occurs during the capture cycle.

Moreover, having an increased level of switching activity over a longer period

Figure 1.12: Implementation of sample design with clock gating

of time will overheat the circuit which can affect circuit's reliability or even lead to permanent damage of the chip under test.

From the previous discussion it can be concluded that traditional DFT cancels the effect of power conscious design strategies, a fact which can have serious impact on product yield and reliability. Hence, as the fabrication technologies advance and the chips are becoming more and more complex, it is becoming increasingly important to embed power-awareness into existing DFT methodologies.

## 1.4 Thesis Overview and Contributions

The aim of this thesis is to investigate power-conscious scan-based DFT techniques. As explained in the previous section, power dissipation during test represents a critical issue for the semiconductor industry, which will become even more acute as the gate densities increase. The roots of this problem are the short time-to-market windows and the existing gap between the design and test development flows, which did not allow the advances in the low power design methodology to propagate into the DFT methodology. The work presented in this thesis addresses the problem of reducing power during testing of digital VLSI circuits. Various scenarios are analysed with the goal of developing suitable power conscious DFT techniques. An outline of this thesis is given in the following. Chapters 2, 3, 4 and 5 present the original contributions of this thesis. The relevant background and an outline of the related work is provided in each of these chapters.

Chapter 2 addresses the conflict between test scheduling algorithms and system-level solutions for reducing power during normal operation such as activity-driven block shutdown. As mentioned earlier in this chapter activity driven shutdown powers-down all idle blocks of a system until they become needed again. Test scheduling, on the other hand is trying to increase the number of blocks tested simultaneously in order to reduce test time, which has as a side-effect an undesirably high level of switching activity. Over the past decade, several power constrained test scheduling approaches have been proposed. Chapter 2 presents a power profile manipulation technique which can be used to enhance existing power constrained test scheduling algorithms. The proposed technique performs a set of transformations on the test sequence corresponding to each system block such that their corresponding power profile during testing is lowered and reshaped in order to increase test concurrency without exceeding a given power constraint.

Chapter 3 tackles the problem of power reduction in a BIST environment from the test pattern generation point of view. The proposed test pattern generator (TPG), designed for mixed-mode BIST, produces test sequences leading to less switching activity in the circuit under test, compared to traditional TPGs, while

achieving high fault coverage in short test application time.

Present ATE is facing the problem of storing the increasing amounts of test data required for testing complex chips. An attractive solution is to employ test data compression methods in order to reduce the volume of data stored on the tester. Chapter 4 proposes a run-length coding scheme suitable for compressing low power test sets. The efficiency of the proposed scheme is evaluated in conjunction with a recently proposed method for test data compression.

Chapter 5 proposes a low power scan chain architecture. The automated scan chain design technique is based on a scan chain partitioning algorithm which aims to translate clock gating into the testing domain. By enabling exactly one scan chain partition during each test clock, the proposed technique reduces significantly the both peak and average power dissipation during test, hence eliminating problems related to chip overheating, as well as the risk of noise-generated failures.

As it can be concluded from the outline of the thesis presented above, there are several ways to approach the problem of power reduction during test. The methods proposed in chapters 2 and 3 are based on transformations of the test set. Test set transformations do not require any structural changes to the circuit under test, and therefore they are suitable for system integration using intellectual property (IP) cores. Chapter 4 combines test sequence transformations with more power-efficient structural transformations of the circuit. The solution proposed in chapter 5 takes a purely structural, and thus test set independent, approach for test power reduction.

The contributions of the work presented in this thesis have been already published or are under consideration as follows:

1. *Power constrained test scheduling using power profile manipulation* **Rosinger, P.;** Al-Hashimi, B.M.; Nicolici, N. - The IEEE International Symposium on Circuits and Systems (ISCAS) 2001, Volume: 5, Page(s): 251-254, vol. 5

2. *Simultaneous reduction in volume of test data and power dissipation for systems-on-a-chip* **Rosinger, P.;** Gonciari, P.T.; Al-Hashimi, B.M.; Nicolici, N. - IEE

Electronics Letters , Volume: 37, Issue: 24, 22 Nov. 2001 Page(s): 1434-1436

3. *Power profile manipulation: a new approach for reducing test application time under power constraints* **Rosinger, P.**; Al-Hashimi, B.M.; Nicolici, N. - IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Volume: 21 Issue: 10 , Oct. 2002 Page(s): 1217-1225

4. *Analysing trade-offs in scan power and test data compression for systems-on-a-chip* **Rosinger, P.**; Gonciari, P.T.; Al-Hashimi, B.M.; Nicolici, N. - IEE Proceedings-Computers and Digital Techniques, Volume: 149 Issue: 4 , July 2002 Page(s): 188-196

5. *Low power mixed-mode BIST based on mask pattern generation using dual MP-LFSR reseeding* **Rosinger, P.**; Al-Hashimi, B.M.; Nicolici, N. - Proc of the IEEE International Conference on Computer Design (ICCD) 2002, Page(s): 474-479

6. *Scan architecture for shift and capture power reduction* **Rosinger, P.**; Al-Hashimi, B.M.; Nicolici, N. Proc of the IEEE Symposium on Defect and Fault Tolerance (DFT) 2002, Page(s): 129-137

7. *Scan architecture with mutually exclusive scan segment activation for shift and capture power reduction* **Rosinger, P.**; Al-Hashimi, B.M.; Nicolici, N. - Submitted (2nd revision) to the IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Nov. 2002.

8. *Dual multiple-polynomial LFSR for low power mixed-mode BIST* **Rosinger, P.**; Al-Hashimi, B.M.; Nicolici, N. - Accepted for publication in the IEE Proceedings-Computers and Digital Techniques, Dec. 2002

## Chapter 2

# Power Profile Manipulation

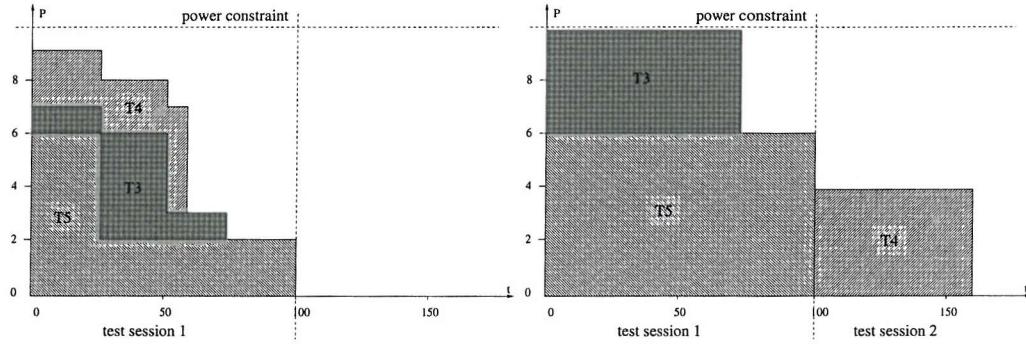

Chapter 1 has outlined that a major issue in testing modern systems is the long testing time. With the growing complexity of modern systems, testing time increases rapidly, producing a serious impact on the final cost of the design [BA00]. Test scheduling algorithms are system-level strategies for increasing test concurrency in order to reduce the overall test time. The high power consumption caused by the intense switching activity in the circuit may exceed the specified limits, hence it can damage the system under test or affect its reliability. Consequently, several solutions to the problem of power dissipation during test have been recently proposed [Nic00, Zor93, Gir00, DCPR98, GLPS97, NAHW00, FCN<sup>+</sup>99, WG98, CSA97, MWMV00, NAH00, LP01, IC01, Cha00, RCV00]. Within these solutions, two main directions can be identified: one considering power dissipation during test an optimisation objective, while the other considers power a design constraint under which other parameters, such as testing time, are improved.

- Test set transformations are examples of techniques which fall into the first category. Test set transformations include test vector reordering [DCPR98, GLPS97, FCN<sup>+</sup>99, CRRV99], test vector altering and test sequence expansion. Test set transformations methods aim to increase the correlation between successive test patterns and/or between successive bits in the test patterns, and hence decreasing power dissipation during test by reducing

the switching activity at the circuit inputs. Test vector reordering and test sequence expansion will be explained later in this chapter. Test vector altering techniques will be discussed in chapters 3 and 4. Usually embedded cores are delivered as IP blocks accompanied with test data, thus the system integrator cannot change their internal structure. Therefore, unless the cores are pre-designed with special scan architectures, the system integrator can control the power dissipation during test *only* by means of test data transformations.

- With the goal of reducing the test time while considering test power dissipation, several power constrained test scheduling (PCTS) algorithms, belonging to the second research direction, were proposed recently. PCTS algorithms [CSA97, MWMV00, NAH00, LP01, IC01, Cha00, RCV00] aim to minimise testing time under a given power constraint imposed by the package type and energy limitations. The basic idea of PCTS algorithms is to maximise the test concurrency, without exceeding the power constraint. Power constrained test scheduling will be discussed later in this chapter.

This chapter proposes a new approach for reducing test time under power constraints by manipulating the test power profiles of the system blocks. The proposed technique aims to reduce power dissipation at block level, and to maximise, with respect to the given power constraint, test concurrency at system level. The proposed technique is addressed to the system integrator without putting any constraints on the scan architectures of the cores. The power profile manipulation technique described in this chapter has the following advantages over existing PCTS algorithms:

1. It allows not only the average and/or peak values of power dissipation to be considered, *but also the shape* of the power profile. The possibility of controlling the size and position within the power profile of the higher and lower power parts would allow existing PCTS algorithms [CSA97, MWMV00, NAH00, LP01, IC01, Cha00, RCV00], to increase test concurrency under specified power constraints.

---

2. It exploits the *slack time* of short test sequences in order to obtain lower power profiles. A test session from a test schedule usually consists in a number of unequal length tests. The test length differences, referred earlier as "test sequence slack time", can be used to extend shorter test sets in the test session with additional vectors. Careful selection of the additional test vectors can lower the peak power during testing which enables increased test concurrency under a given power constraint.

By manipulating the power profile during test scheduling, the proposed solution is a fusion between the two research directions in low power testing mentioned earlier: techniques for minimising test power dissipation [DCPR98, GLPS97, FCN<sup>+</sup>99, CRRV99, WG98] and techniques for minimising test time under power constraints [CSA97, MWMV00, NAH00, LP01, IC01, Cha00, RCV00]. In this chapter it will be shown how complementary techniques can be easily combined to achieve high test concurrency under given power constraints. *The proposed power profile manipulation approach is not a test scheduling algorithm, rather it represents a complementary technique meant to enhance the performance of existing power constrained test scheduling algorithms.* The distinctive feature of power profile manipulation is that it is independent of the test scheduling policy. Consequently, it can be *equally* embedded into *any* existing PCTS algorithm to leverage its performance. It should be noted that this methodology targets testing scenarios where test data transformations are possible, such as stuck-at fault testing or skewed-load delay-testing using ATPG generated test sets.

The rest of the chapter is organised as follows. Section 2.1 provides background on test scheduling and a commonly used approximation model for power dissipation during test. The proposed power profile manipulation technique, including a new test power approximation model, is detailed in Section 2.2. Section 2.3 shows through an example how the proposed methodology can be integrated into existing power constrained test scheduling algorithms. Section 2.4 discusses the experiments performed in order to validate the efficiency of the proposed method.

## 2.1 Background Information

This section provides the terminology and concepts which will be used in the rest of the chapter.

### 2.1.1 Test Scheduling

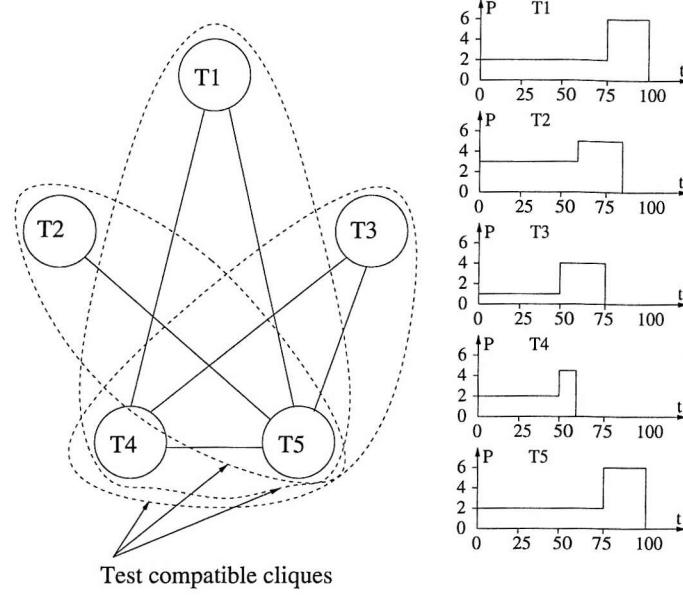

Test scheduling algorithms aim to reduce test application time by increasing the concurrency of the testing activities in the system. When ignoring power, maximum test concurrency is limited only by system's resource sharing configuration. The resource sharing configuration of a system can be represented using the *resource allocation graph*. An example of resource allocation graph is shown in Figure 2.1(a). T1, T2 and T3 represent the tests corresponding to the system's blocks, while R1 to R5 represent hardware resources required by the tests. Internal buses, dedicated test I/O pins, BIST test pattern generators and response analysers all constitute examples of hardware resources which might be shared during test. An arc between a test and a resource means that the resource is required by the test. For example, resources R1 and R3 are required in order to perform test T1.

Figure 2.1: Resource allocation graph and test compatibility graph

The blocks of a system which can be tested simultaneously without generating any resource conflicts are said to be *test compatible*. The tests which are executed

at the same time form a *test session*. The tests corresponding to test compatible blocks are said to be *resource compatible tests*. The test compatibility relations among the blocks of a system are represented using the *test compatibility graph* (TCG). Each block and its corresponding test are associated to a node in the TCG. An edge between two tests in the TCG signifies that the two corresponding tests are resource-compatible. Figure 2.1(b) shows the test compatibility graph for the resource allocation graph shown in Figure 2.1(a). Only tests T1 and T3 are compatible as they do not share any hardware resource. T1 is incompatible with T2 as they share resource R3, T2 and T3 are incompatible as they share R2. Thus, from the resource sharing perspective, T1 and T3 could be scheduled into the same test session.

### 2.1.2 Approximation Model for Power Dissipation During Test

In order to be considered by test scheduling algorithms, the power dissipation during test of a system block needs to be described using mathematical constructs which can be operated upon algorithmically. A *power profile* captures the power dissipation of a circuit over time when a sequence of test vectors is applied to the circuit. Power profiles represent cycle-accurate descriptions of power dissipation which makes them too complex to be considered by the test scheduling algorithms. Therefore simpler yet reliable approximate power models are needed. The following section analyses a commonly used power approximation model and justifies the need for a new power approximation model for power constrained test scheduling.

### 2.1.3 Global Peak Power Approximation Model

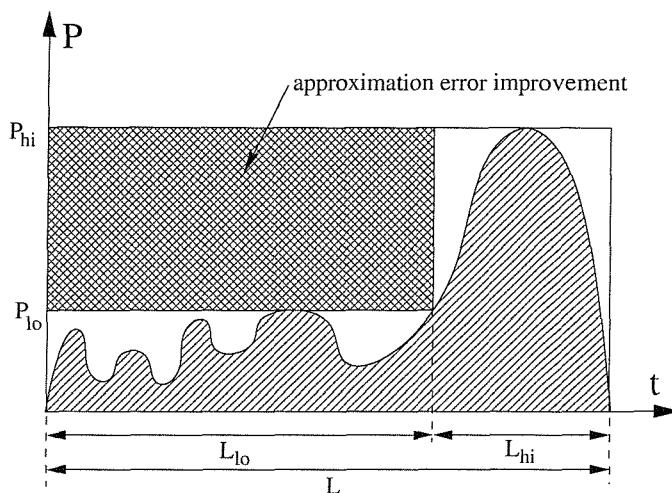

The power approximation model used by existing PCTS algorithms [CSA97, IC01, MWMV00, NAH00, LP01, Cha00, RCV00] will be referred in the rest of this chapter as the global peak power approximation model (GP-PAM). As shown in Figure 2.2, the GP-PAM basically flattens the power profile of a circuit to the

Figure 2.2: Global peak power approximation model

worst-case power dissipation value, i.e. its peak value. According to this model, the power profile of a block under test is described by the pair  $(P_{hi}, L)$ , where  $P_{hi}$  is the global peak value of the power profile, and  $L$  is the length of the test sequence. This simple approximation model, although it guarantees that power dissipation is not under-estimated at any time, it introduces a high approximation error, indicated by the *false power* from Figure 2.2. The false power component introduced by the power approximation model leads to sub-optimal test concurrency, and hence to longer testing times.

The false power can be minimised by modifying the test power profiles and using a more accurate power approximation model to describe them. Section 2.2 will show how test concurrency can be increased by reducing the false power component of the power profile.

## 2.2 Power Profile Manipulation Technique

The previous section has shown that, regardless of its simplicity and reliability, global peak power approximation model leads to large approximation errors and consequently to low test concurrency. This can be avoided if the shape of the

power profile can be changed such that it can be described using a more accurate yet simpler model. This section presents a power profile manipulation technique which enables increased test concurrency under power constraints. This technique consists of the following steps:

- **Test vector reordering (Section 2.2.1)** - initially, power profiles for the block tests are lowered by increasing the correlation between successive vectors; test vector reordering is used for peak power reduction, as well as for power profile reshaping;

- **Test sequence expansion (Section 2.2.2)** - additional test vectors are added to test sequences in order to lower further their power profiles. Only the test sequences which do not influence the test session length are extended, in order to preserve the total test time;

- **New power approximation model (Section 2.2.3)** - a power approximation model which is capable of exploiting the shape of power profiles corresponding to reordered test sequences is used to reduce the false power;

- **test sequence rotation (Section 2.2.4)** - finally, the low power profiles are rotated and piled up together such that the high power parts do not overlap with each other in order to obtain improved usage of the power constraint;