# SYNTHESIS AND STRUCTURES of TRANSCONDUCTAN CE AMPLIFIER AND CURRENT CONVEYOR-BASED FILTERS

Chun-Ming Chang

UNIVERSITY OF SOUTHAMPTON

## Synthesis and Structures of Transconductance Amplifier and Current Conveyor-Based Filters

## Chun-Ming Chang

A THESIS SUBMITTED for the DEGREE of PH.D.

ELECTRONIC SYSTEMS DESIGN RESEARCH GROUP SCHOOL OF ELECTRONICS AND COMPUTER SCIENCE FACULTY OF ENGINEERING AND APPLIED SCIENCE UNIVERSITY OF SOUTHAMPTON

UNITED KINGDOM

FEBRUARY 2004

### UNIVERSITY OF SOUTHAMPTON <u>ABSTRACT</u> FACULTY OF ENGINEERING AND APPLIED SCIENCE SCHOOL OF ELECTRONICS AND COMPUTER SCIENCE <u>Doctor of Philosophy</u> Synthesis and Structures of Transconductance Amplifier and Current Conveyor Based Filters

by Chun-Ming Chang

This thesis investigates the development of new synthesis methods and structures of analogue filters considering two types of active elements: operational transconductance amplifiers and current conveyors. Starting from an nth-order generic transfer function, it is shown how an analytical synthesis approach can be used to generate systematically filters that have less component count than previously known filters whilst maintaining the desirable features of grounded passive components and the employment of single-input active devices. Two new synthesis methods for current-mode filters and two new synthesis methods for voltage-mode filters have been developed including their associate structures to provide nth-order filtering functions. Equal transconductance and equal capacitance appear in the voltage-mode synthesized filter structures particularly suitable for VLSI implementation. Simulation results of various filter circuits obtained from the proposed synthesis methods are given based on CMOS design of the active elements.

Despite the numerous publications reporting filter biquads based on transconductance amplifiers and current conveyors, it is shown how such biquads normally make trade-offs with respect to some key performance parameters including excessive number of passive and active elements and the need to impose component choice conditions in order to provide universal filtering. This includes low-pass, high-pass, band-pass, notch and all-pass functions. This thesis proposes the concept and design of *unified* filter model based on nullators, norators, current mirrors, resistors and capacitors, from which two new biquad implementations based on two different active elements have been developed. It is shown that such biquads can achieve five key performance parameters simultaneously and without trade-offs.

Finally, a comparative analysis between the various synthesis methods and filter structures reported throughout the thesis has been carried out with the general aim of assisting the designer to develop the appropriate filter circuit given a filtering problem and an implementation style.

## **Table of Contents**

| A | CKN    | OWLEDGEMENTS5                                          |

|---|--------|--------------------------------------------------------|

| L | ist of | viations                                               |

| 1 | Intr   | oduction12                                             |

| 2 | Bac    | kground and Literature Review25                        |

|   | 2.1    | OTA Symbol and Biquad25                                |

|   | 2.2    | CCII Symbol and Biquad31                               |

|   | 2.3    | Active Current-Mode and Voltage-Mode Filters           |

|   | 2.4    | Biquad Classification                                  |

|   | 2.5    | Literature Review                                      |

|   |        | 2.5.1 Review of OTA- and CCII-Based Biquads            |

|   |        | 2.5.2 Review of OTA- and CCII-Based High-Order Filters |

|   | 2.6    | Concluding Remarks                                     |

| 3 | Cur    | rent-Mode High-Order OTA-C Filters Synthesis51         |

|   | 3.1    | Preliminaries                                          |

|   | 3.2    | Criteria and Design Notes of the Synthesis Methods53   |

|   | 3.3    | Analytical Synthesis Method I: MISOC Method55          |

|   | 3.4    | Analytical Synthesis Method II: DIMOC Method63         |

|   | 3.5    | Sensitivity Analysis                                   |

|   | 3.6    | Comparison with Previous Work71                        |

|   | 3.7    | Simulation Results77                                   |

|   | 3.8    | Concluding Remarks                                     |

| 4 | Vol    | tage-Mode High-Order OTA-C Filters Synthesis           |

|   | 4.1    | Extension Approach                                     |

|     | 4.2   | Analytical Synthesis Method I91                                  |

|-----|-------|------------------------------------------------------------------|

|     | 4.3   | Analytical Synthesis Method II100                                |

|     | 4.4   | Sensitivity Analysis107                                          |

|     | 4.5   | Comparison with Previous Work109                                 |

|     | 4.6   | Simulation Results119                                            |

|     | 4.7   | Concluding Remarks125                                            |

| 5   | Uni   | fied Biquadratic Filters127                                      |

|     | 5.1   | Literature Review and Motivation                                 |

|     | 5.2   | Biquad Filter Model                                              |

|     | 5.3   | CCCII-Based Implementation145                                    |

|     | 5.4   | OTA-Based Implementation147                                      |

|     | 5.5   | Simulation Results152                                            |

|     | 5.6   | Concluding Remarks158                                            |

| 6   | Con   | nparative Analysis of Filter Structures and Synthesis Methods159 |

|     | 6.1   | Analytical Synthesis Methods Comparison159                       |

|     |       | 6,1,1 Comarison between Current-mode Synthesis Methods160        |

|     |       | 6.1.2 Comarison between Voltage-mode Synthesis Methods162        |

|     |       | 6.1.3 Comarison between Filters Operating Mode163                |

|     | 6.2   | Comparison between Unified Biquad Filters165                     |

|     | 6.3   | Concluding Remarks171                                            |

| 7   | Con   | clusion173                                                       |

| Re  | feren | ces179                                                           |

| Ар  | pend  | ix 1 Example of New Voltage-Mode Analytical Synthesis Method186  |

| Ар  | pend  | ix 2 Theory of Cascadability190                                  |

| Ар  | pend  | ix 3 H-SPICE Netlists                                            |

| Ар  | pend  | ix 4 Non-ideal Comparison between Unified OTA and CCCII-based    |

| Big | luad  | Filters                                                          |

| Ар  | pend  | ix 5 PSpice Sensitivity Analysis and Simulations206              |

## ACKNOWLEDGEMENTS

I would like to express my sincere gratitude to Dr. Bashir M. Al-Hashimi, my project supervisor for his good guidance, advice and encouragement throughout the course of the research. In the meantime, I am deeply grateful to Dr. Neil Ross for his kind help with the structure and presentation of the thesis. Also, I would like to acknowledge Professor Yichuang Sun, University of Hertfordshire, for many valuable discussions and excellent comments particularly on the work described in Chapter 4.

I wish to thank the Faculty of Engineering and Applied Science and the School of Electronics and Computer Science, University of Southampton, for their partial financial support of my work through a Taiwan Postgraduate Scholarship. Also, I wish to acknowledge Chung Yuan Christian University, Chung-Li, Taiwan, R. O. China, who gave me a fully paid sabbatical year from 1 February 2002 to 31 January 2003.

I owe much thanks to my family for the help and the encouragement that they have given me over the years it has taken to complete this thesis. Finally, all my other thanks will be given to the God.

### Abbreviations

| CCII                | Second-Generation Current Conveyor                          |

|---------------------|-------------------------------------------------------------|

| CCII+               | Plus-Type Second-Generation Current Conveyor                |

| CCII-               | Minus-Type Second-Generation Current Conveyor               |

| CCII±               | Plus-/Minus-Type Second-Generation Current Conveyor         |

| CCCII               | Second-Generation Current-Controlled Conveyor               |

| CCCII-C             | Second-Generation Current-Controlled Conveyor and Capacitor |

| CFA                 | Current Feedback Amplifier                                  |

| CFCCII <sub>p</sub> | Four Terminal P-Type Active Current Conveyor                |

| DIMOC               | Double Input and Multiple Output Currents                   |

| DVCCS               | Differential Voltage-Controlled Current Source              |

| IC                  | Integrated Circuit                                          |

| MISOC               | Multiple Input Currents and a Single Output                 |

| OA                  | Operational Amplifier                                       |

| OTA                 | Operational Transconductance Amplifier                      |

| OTA-C               | Operational Transconductance Amplifier and Capacitor        |

|                     |                                                             |

### List of Tables

| Table 2-1 | Comparison of recently reported high-order OTA-C filters4                | 16 |

|-----------|--------------------------------------------------------------------------|----|

| Table 2-2 | Comparison of recently reported high-order CCII-based filters4           | 8  |

| Table 4-1 | Comparison with recently reported nth-order OTA-based filters1           | 12 |

| Table 4-2 | Comparison with recently reported nth-order OTA-based filters1           | 15 |

| Table 5-1 | Performance parameters of recently reported CCCII based filters1         | 32 |

| Table 5-2 | Performance parameters of recently reported OTA-based filters            | 35 |

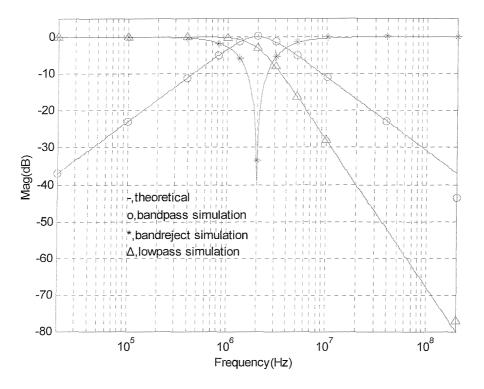

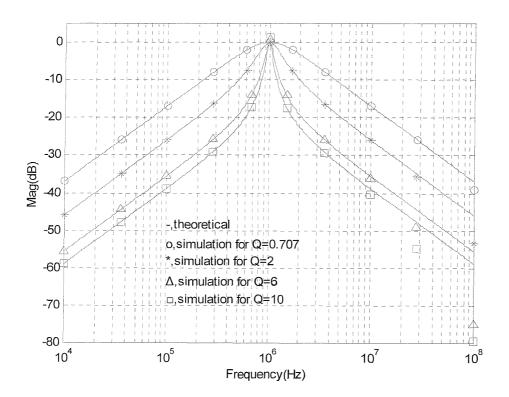

| Table 5-3 | Component values for simulating the BP and BR filter with different $Q1$ | 52 |

| Table 6-1 | Comparison between two current-mode synthesis methods1                   | 60 |

| Table 6-2 | Relationship between filtering functions and switches16                  | 52 |

| Table 6-3 | Comparison between two voltage-mode synthesis methods16                  | 52 |

## List of Figures

| Fig. 1-1 Implementation of the differential-analyzer technique [1-2]14                        |

|-----------------------------------------------------------------------------------------------|

| Fig. 1-2 Three circuits provided for the three parts in Eq. (1-9)16                           |

| Fig. 1-3 Tow-Thomas biquad [3-5]17                                                            |

| Fig. 1-4 20 <sup>th</sup> -order band-pass ladder prototype18                                 |

| Fig. 1-5 Left-LUD SC ladder simulation with broken loops                                      |

| Fig. 2-1 (a) OTA functional block25                                                           |

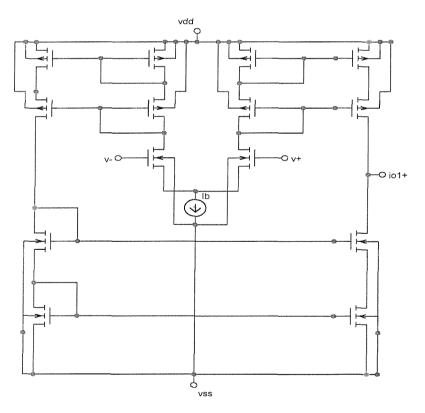

| Fig. 2-1 (b) CMOS implementation of a plus-type OTA [80]26                                    |

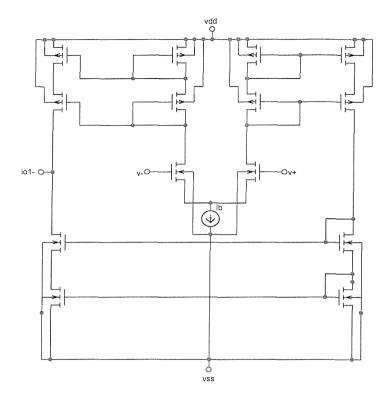

| Fig. 2-1 (c) CMOS implementation of a minus-type OTA [80]27                                   |

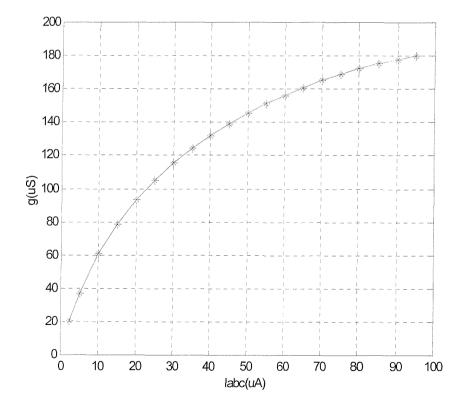

| Fig. 2-1 (d) Relationship between g and I <sub>abc</sub> for the CMOS OTA [80]27              |

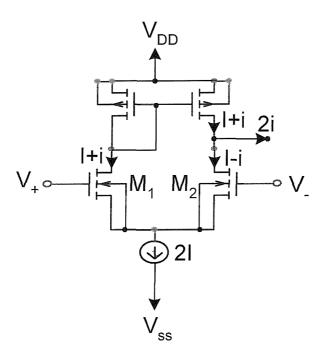

| Fig. 2-2 Matched differential pair in the CMOS implementation of an OTA28                     |

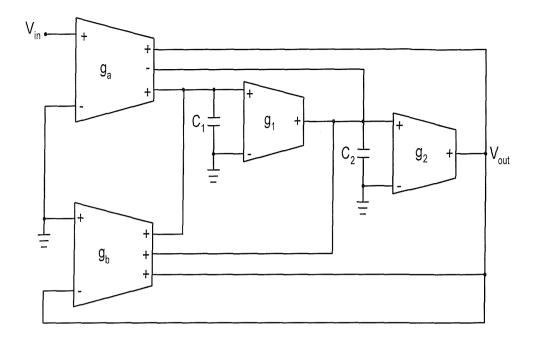

| Fig. 2-3 Block diagram of voltage-mode OTA-C universal biquad [21]30                          |

| Fig. 2-4 CCII functional block32                                                              |

| Fig. 2-5 Block diagram of voltage-mode CCII-based universal biquad [28]                       |

| Fig. 2-6 Active filter classification                                                         |

| Fig. 2-7 Current-mode OTA-C universal biquad [26]35                                           |

| Fig. 2-8 Current-mode CCII-based universal biquad [31]36                                      |

| Fig. 2-9 (a) and (b) Block diagrams of single-input, three-output multifunction biquads I and |

| II                                                                                            |

| Fig. 2-10 (a) and (b) Block diagrams of three-input, single-output multifunction biquads III  |

| and IV                                                                                        |

| <b>Fig. 3-1</b> Example 3.1 circuit51                                                         |

| Fig. 3-2 Floating capacitor                                                                   |

| Fig. 3-3 Double-input OTA54                                                                   |

| Fig. 3-4 Series of components55                                                               |

| Fig. 3-5 Shunt of components                                                                  |

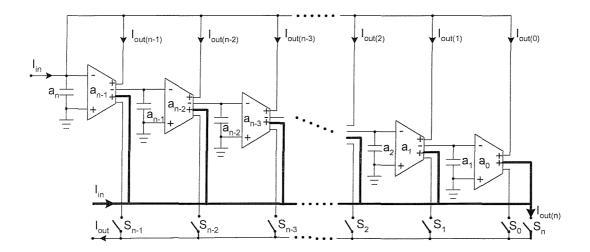

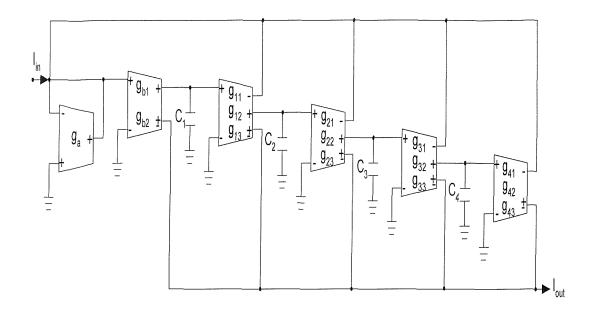

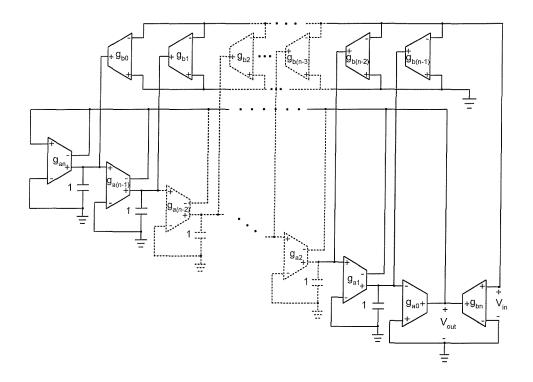

| Fig. 3-6 Nth-order OTA-C generic filter structure of the MISOC synthesis method56             |

| Fig. 3-7. OTA-C realization of the integrator given by Eq. (3-7a)59                           |

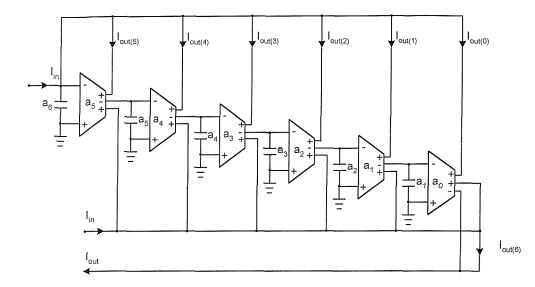

| Fig.3-8 7 <sup>th</sup> -order low-pass OTA-C filter using the MISOC synthesis method62       |

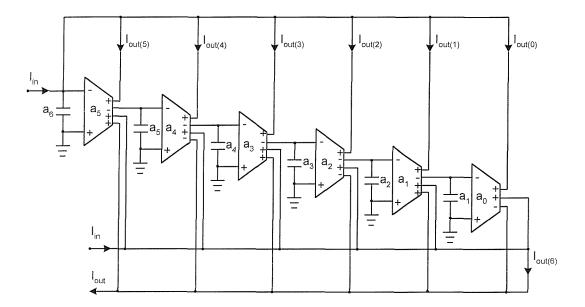

| Fig.3-9 6 <sup>th</sup> -order band-pass OTA-C filter using the MISOC synthesis method62      |

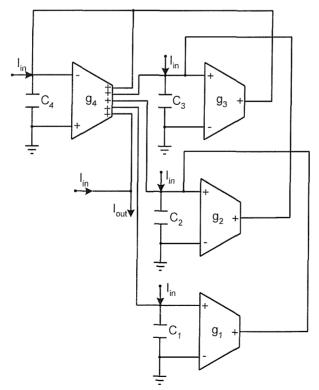

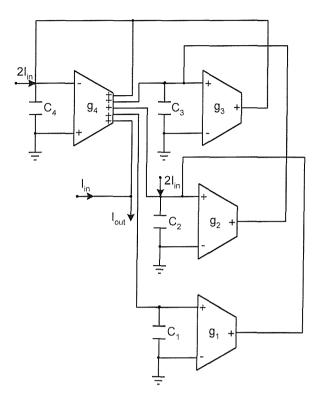

| Fig. 3-10 Nth-order OTA-C generic filter structure of the DIMOC synthesis method63            |

| Fig. 3-11 6 <sup>th</sup> -order band-reject OTA-C filter obtained using the DIMOC synthesis  |

| method                                                                                        |

| Fig.3-12 6 <sup>th</sup> -order all-pass OTA-C filter obtained using the DIMOC synthesis                                               |

|----------------------------------------------------------------------------------------------------------------------------------------|

| method68                                                                                                                               |

| Fig. 3-13 5 <sup>th</sup> -order all-pole low-pass ladder filter [17]71                                                                |

| Fig. 3-14 6 <sup>th</sup> -order all-pole band-pass ladder filter [17]72                                                               |

| <b>Fig. 3-15 (a)</b> 2nd-order high-pass filter [15]72                                                                                 |

| <b>Fig. 3-15 (b)</b> 2nd-order notch filter [15]73                                                                                     |

| <b>Fig. 3-16</b> 4 <sup>th</sup> -order high-pass filter [14]73                                                                        |

| <b>Fig. 3-17</b> 4th-order high-pass filter [12]74                                                                                     |

| Fig. 3-18 Fourth-order OTA-C high-pass filter using MISOC synthesis method78                                                           |

| Fig. 3-19 Fourth-order OTA-C all-pass filter using MISOC synthesis method                                                              |

| Fig. 3-20 Fourth-order OTA-C high-pass filter using DIMOC synthesis method79                                                           |

| Fig. 3-21 Fourth-order OTA-C all-pass filter using DIMOC synthesis method80                                                            |

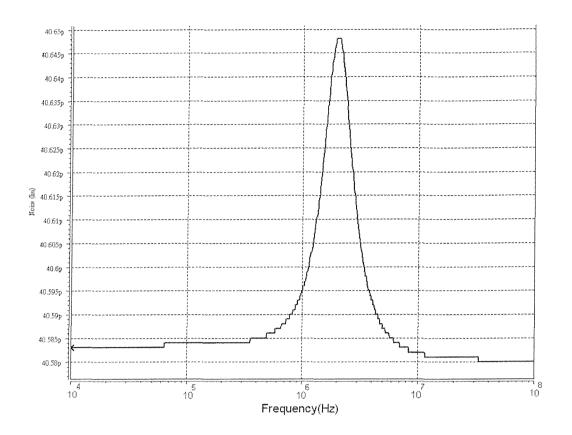

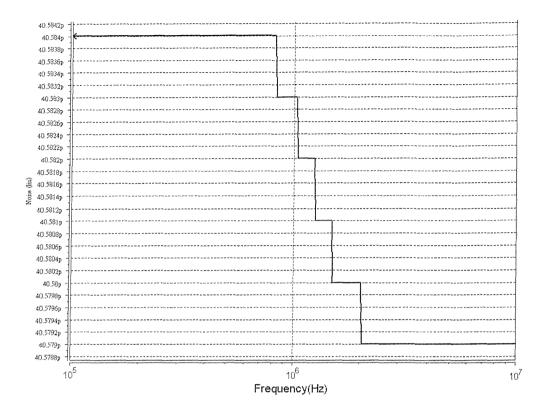

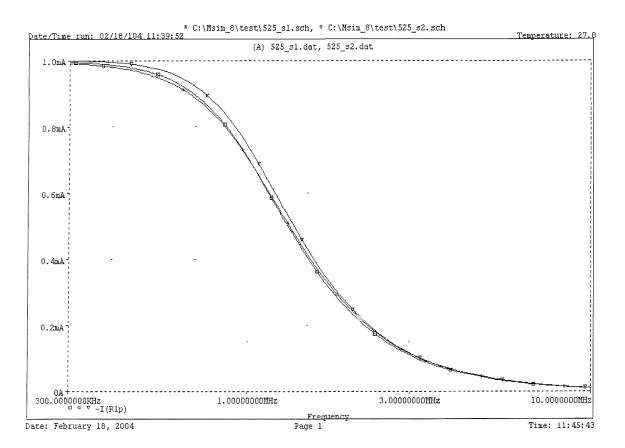

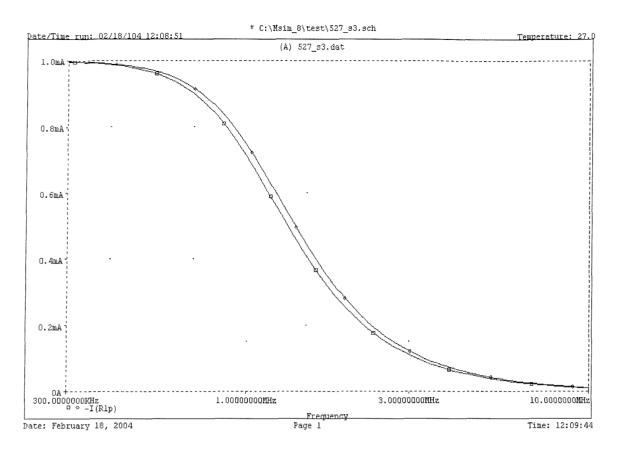

| Fig. 3-22 Amplitude-frequency response of Fig. 3-1880                                                                                  |

| Fig. 3-23 Amplitude-frequency response of Fig. 3-1981                                                                                  |

| Fig. 3-24 Superposed diagram of Figs. 3-22 and 3-2381                                                                                  |

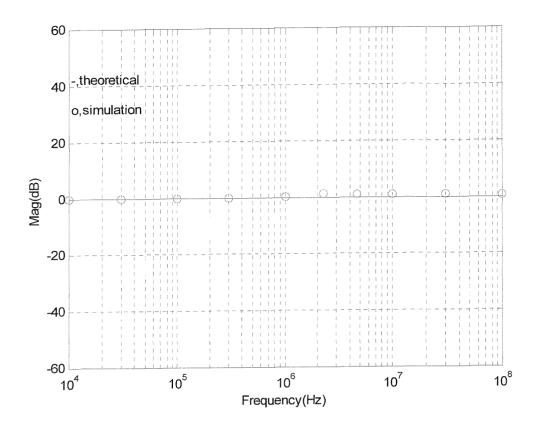

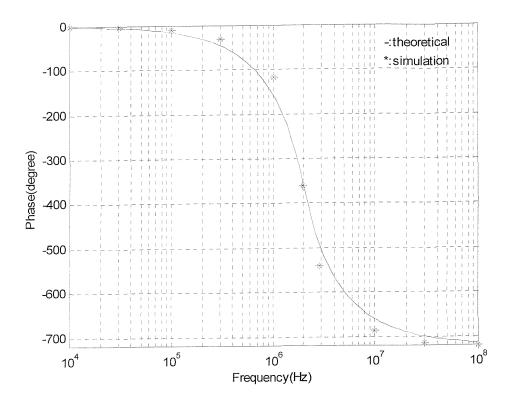

| Fig. 3-25 (a) Amplitude-frequency response of Fig. 3-19                                                                                |

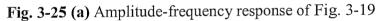

| Fig. 3-25 (b) Phase-frequency response of Fig. 3-19                                                                                    |

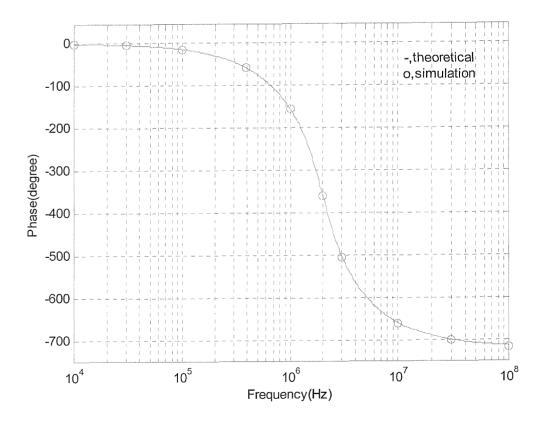

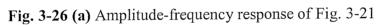

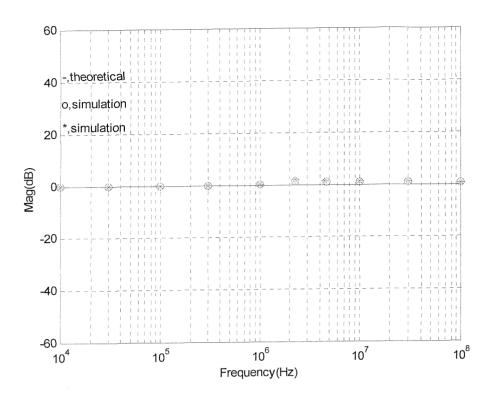

| Fig. 3-26 (a) Amplitude-frequency response of Fig. 3-21                                                                                |

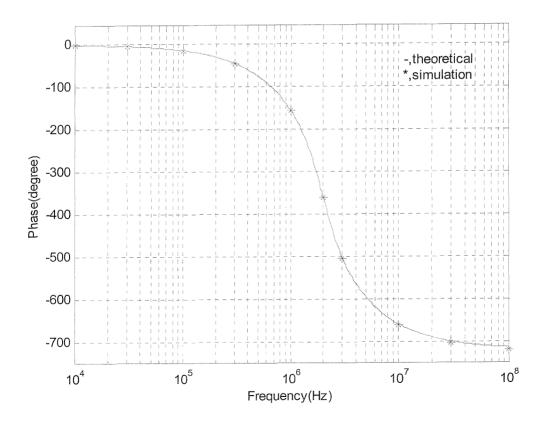

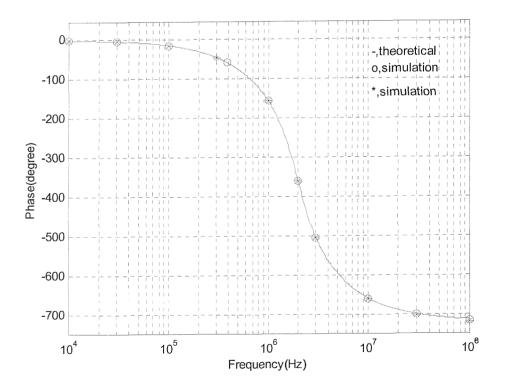

| Fig. 3-26 (b) Phase-frequency response of Fig. 3-21                                                                                    |

| Fig. 3-27 (a) Superposed diagram of Figs. 3-25 (a) and 3-26 (a)84                                                                      |

| Fig. 3-27 (b) Superposed diagram of Figs. 3-25 (b) and 3-26 (b)                                                                        |

| Fig. 3-28 Noise simulation result: amplitude-frequency response of Fig. 3-1885                                                         |

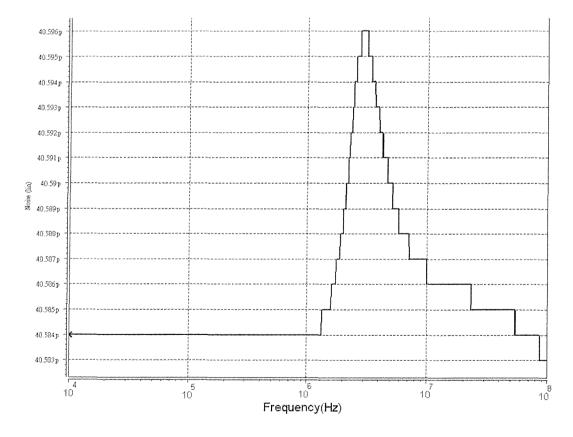

| Fig. 3-29 Noise simulation result: amplitude-frequency response of Fig. 3-2085                                                         |

| Fig. 3-30. 3 <sup>rd</sup> -order current-mode OTA-C filter using the MISOC synthesis method86                                         |

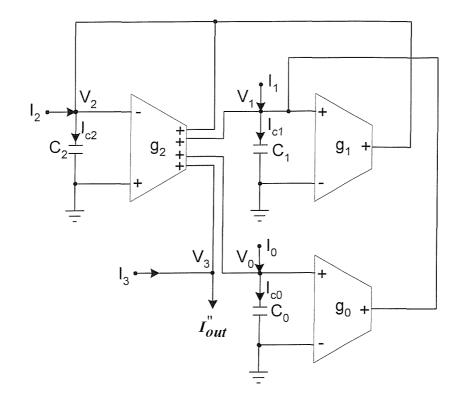

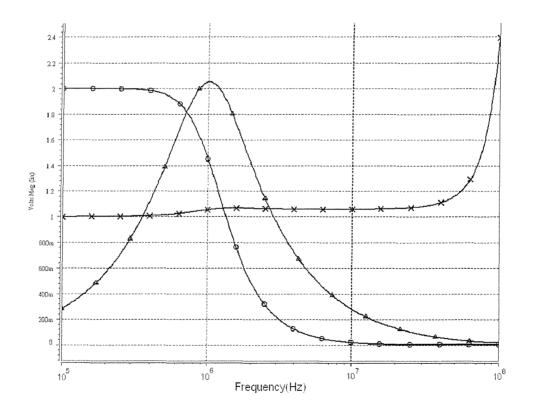

| <b>Fig. 3-31(a)</b> Amplitude-frequency responses of node voltages, $V_0$ (o), $V_1$ (*), $V_2$ ( $\Delta$ ), and $V_3$ ( $\Box$ )     |

| in Fig. 3-26 with $I_0 = I_1 = I_2 = I_3 = I_{in}$                                                                                     |

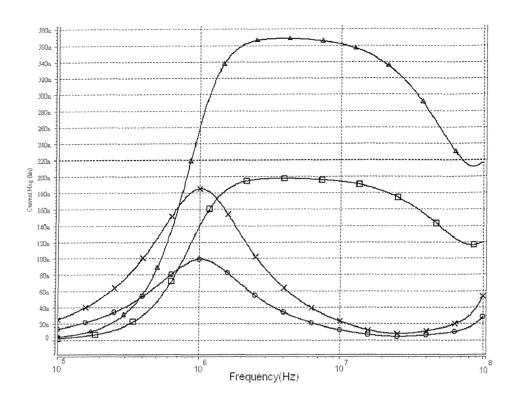

| <b>Fig. 3-31(b)</b> Amplitude-frequency responses of branch currents, $I_{out}$ (o), $I_{co}$ (*), $I_{cl}$ ( $\Delta$ ), and $I_{c2}$ |

| ( $\Box$ ) in Fig. 3-26 with $I_0 = I_{in}$ and $I_1 = I_2 = I_3 = 0$                                                                  |

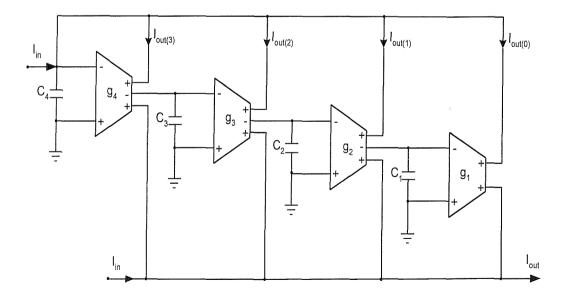

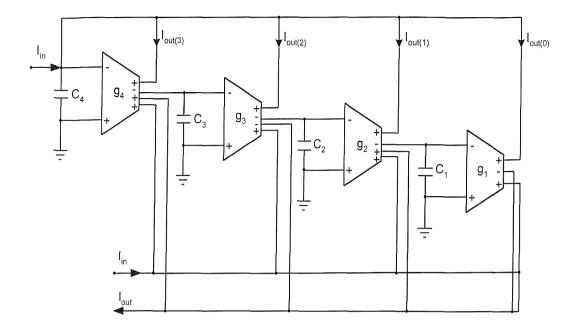

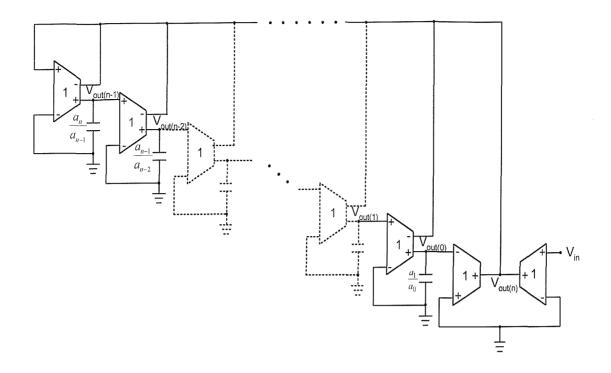

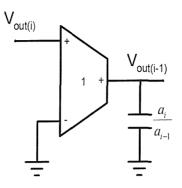

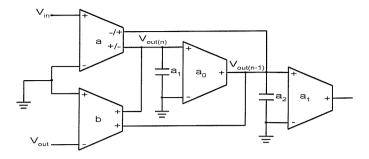

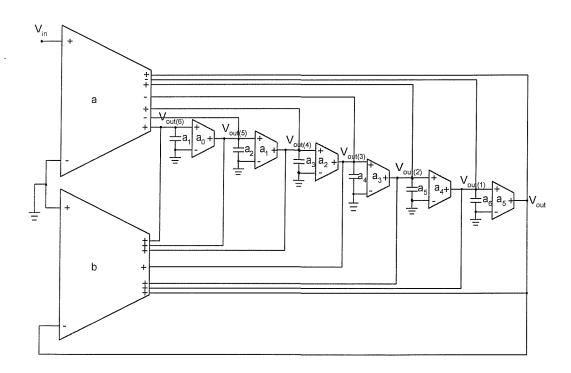

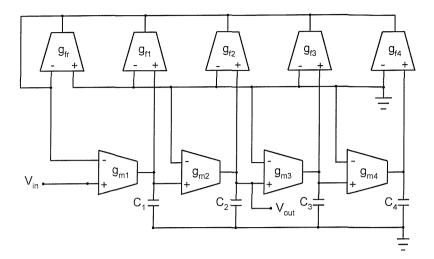

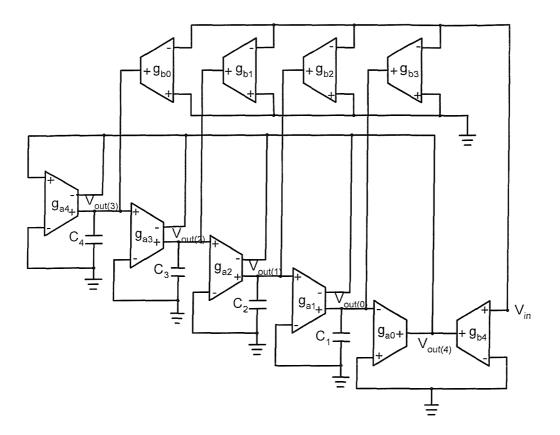

| Fig.4-1. Nth-order OTA-C filter structure of the proposed analytical synthesis                                                         |

| method                                                                                                                                 |

| Fig.4-2. OTA-grounded C realization of the integrator given by Eq. (4-13)95                                                            |

| Fig.4-3. 4 <sup>th</sup> -order OTA-C LP, BP, and HP filters derived from Fig.4-1                                                      |

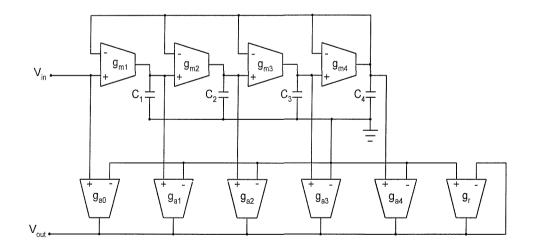

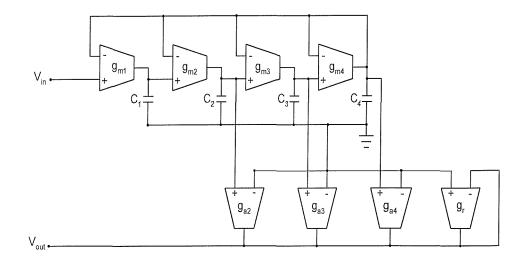

| Fig.4-4. OTA-C filter structure II for realizing general nth-order transfer functions                                                  |

| Fig.4-5. OTA-C filter structure I for realizing general nth-order transfer functions                                                   |

| Fig.4-6. Nth-order OTA-C all-pass filter structure101                                                                                  |

| Fig.4-7. OTA-C implementation of Eq. (4-31a)104                                                                                        |

| <b>Fig.4-8.</b> OTA-C implementation of Eqs. (4-31a) and (4-31b)                                                                       |

| Fig.4-9. 6th-order OTA-C all-pass filter derived from Fig.4-6                                                           | 106             |

|-------------------------------------------------------------------------------------------------------------------------|-----------------|

| Fig.4-10 (a) 4 <sup>th</sup> -order voltage-mode OTA-C high-pass filter [16]                                            | 110             |

| Fig.4-10 (b) 4 <sup>th</sup> -order voltage-mode OTA-C band-pass filter [16]                                            | 111             |

| Fig.4-11 (a) 4 <sup>th</sup> -order voltage-mode OTA-C high-pass filter [20]                                            | 111             |

| Fig.4-11 (b) 4 <sup>th</sup> -order voltage-mode OTA-C band-pass filter [20]                                            | 112             |

| Fig. 4-12 Third-order OTA-C all-pass filter derived from Fig. 4-6                                                       | 117             |

| Fig. 4-13 Third-order OTA-C all-pass filter [16]                                                                        | 118             |

| Fig. 4-14 Third-order OTA-C all-pass filter [20]                                                                        | 118             |

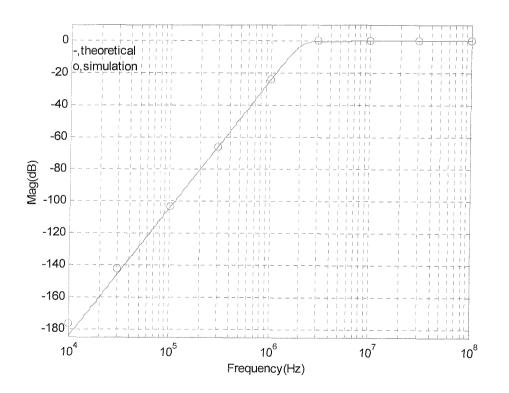

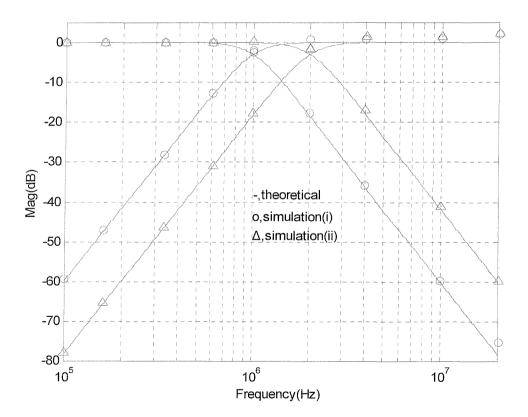

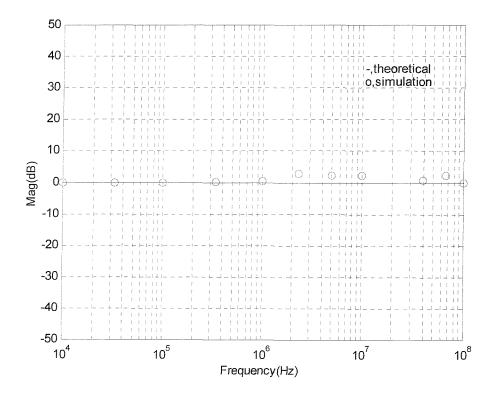

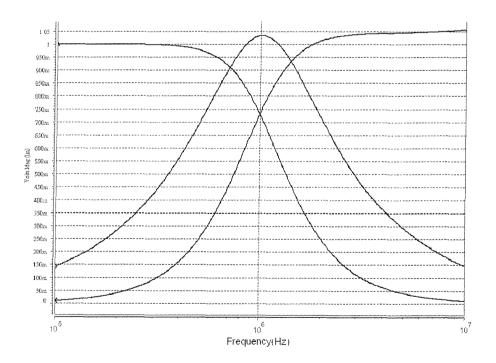

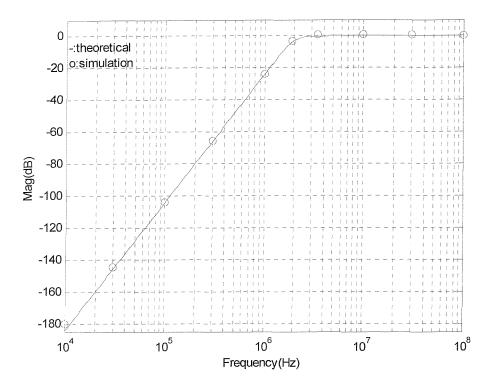

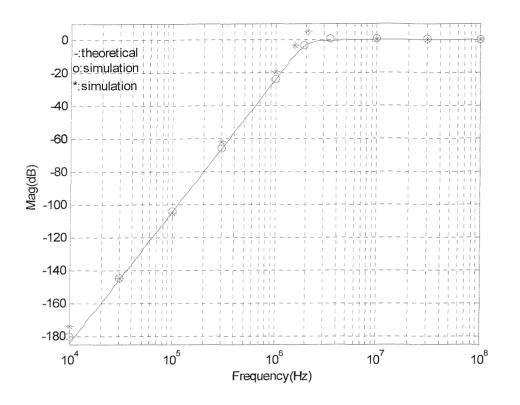

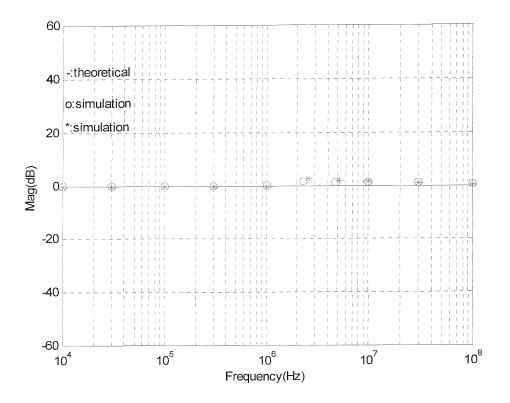

| Fig.4-15 LP and HP amplitude-frequency responses of the third-order filter                                              | 119             |

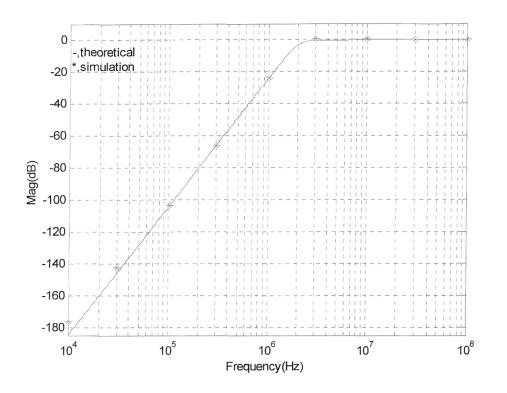

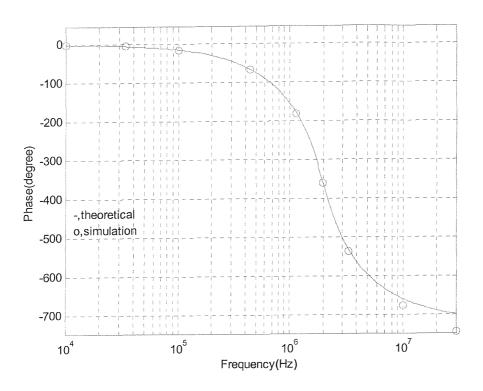

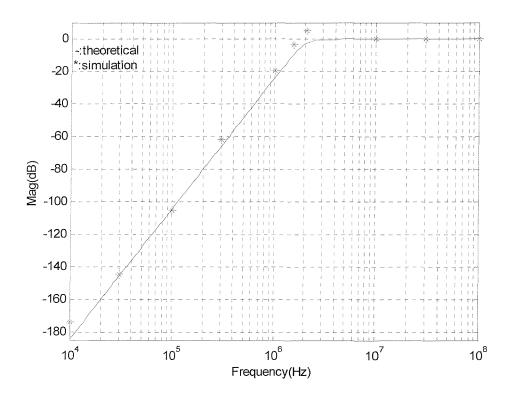

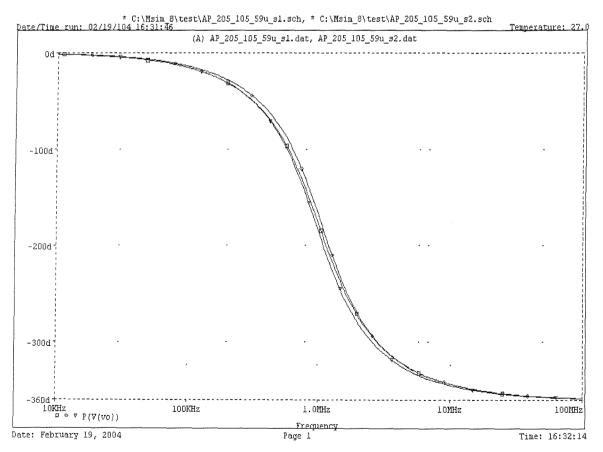

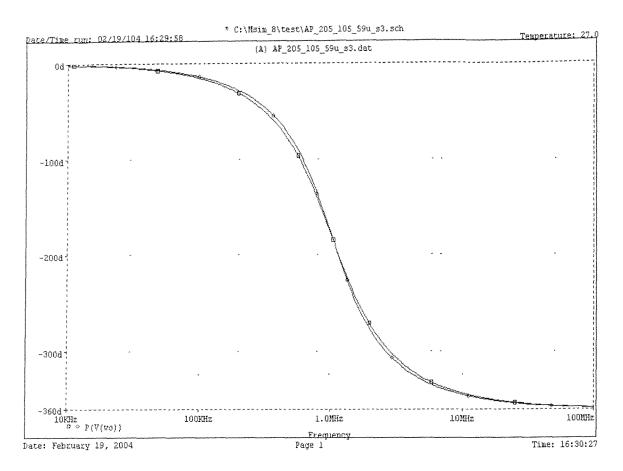

| Fig. 4-16 (a) Amplitude-frequency response of the 3 <sup>rd</sup> -order all-pass filter                                | 120             |

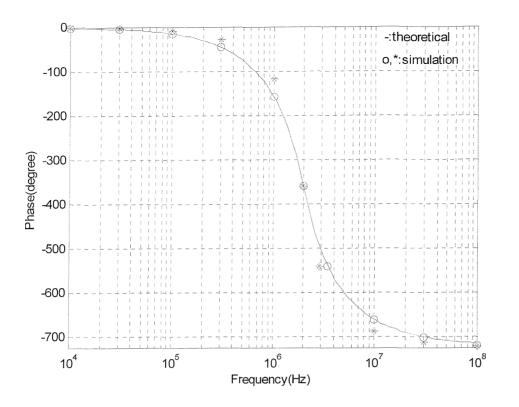

| <b>Fig. 4-16 (b)</b> Phase-frequency response of the 3 <sup>rd</sup> -order all-pass filter                             | 121             |

| Fig. 4-17 2nd-order OTA-C high-pass filter derived from Fig.4-1                                                         | 121             |

| Fig. 4-18 2nd-order OTA-C all-pass filter derived from Fig.4-6                                                          | 122             |

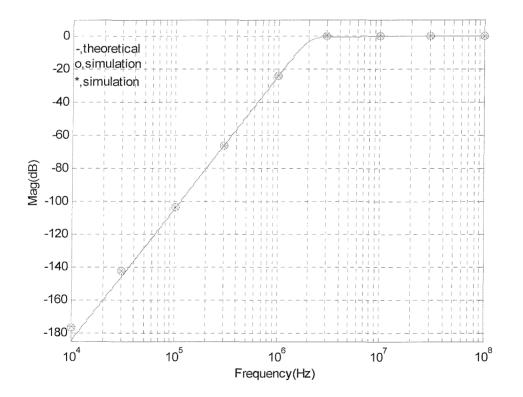

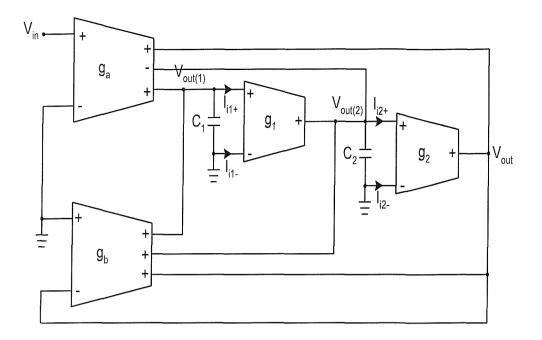

| Fig. 4-19 (a) Amplitude-frequency responses of node voltages, $V_{out(2)}$ (high-pass), $V_{out}$                       | (1) (band-      |

| pass), and $V_{out(0)}$ (low-pass)                                                                                      | 122             |

| <b>Fig. 4-19 (b)</b> Amplitude-frequency responses of branch currents, $I_{ot}(0)$ , $I_{otl}(\Delta)$ , $I_{co}(\Box)$ | ), and $I_{cl}$ |

| (*)                                                                                                                     | 123             |

| <b>Fig. 4-20 (a)</b> Amplitude-frequency responses of node voltages, $V_{out}(x)$ , $V_{out(l)}(o)$ ,                   |                 |

| and $V_{out(2)}(\Delta)$                                                                                                | 123             |

| <b>Fig. 4-20 (b)</b> Amplitude-frequency responses of branch currents, $I_{il+}(x)$ , $I_{il-}(o)$ ,                    |                 |

| $I_{i2+}(\Delta)$ , and $I_{i2-}(\Box)$                                                                                 | 124             |

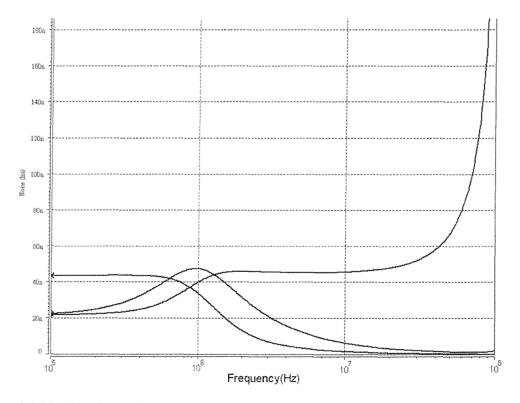

| Fig. 4-21 Noise simulation results: amplitude-frequency responses of node voltages,                                     | $V_{out(2)}$    |

| (high-pass), $V_{out(l)}$ (band-pass), and $V_{out(0)}$ (low-pass) of Fig. 4-17                                         |                 |

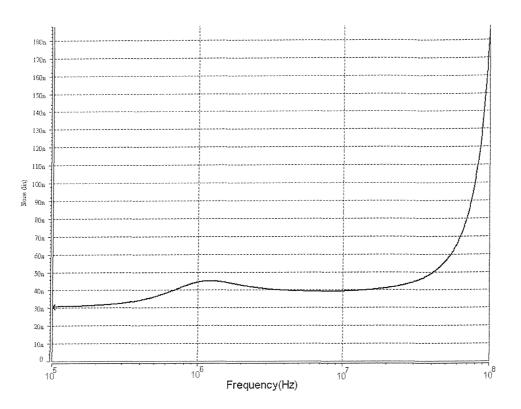

| Fig. 4-22 Noise simulation results: amplitude-frequency responses of Fig. 4-18                                          | 125             |

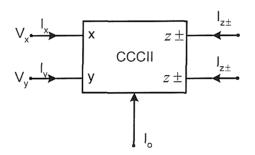

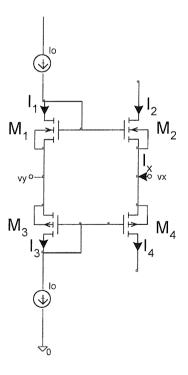

| Fig. 5-1 CCCII functional block                                                                                         | 128             |

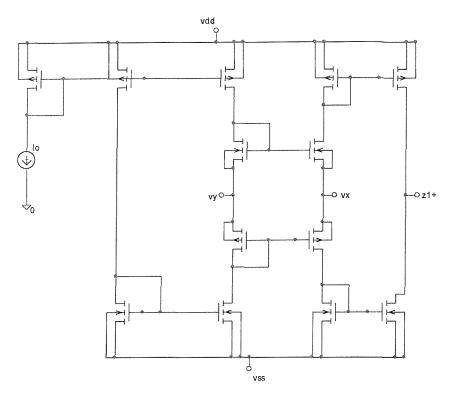

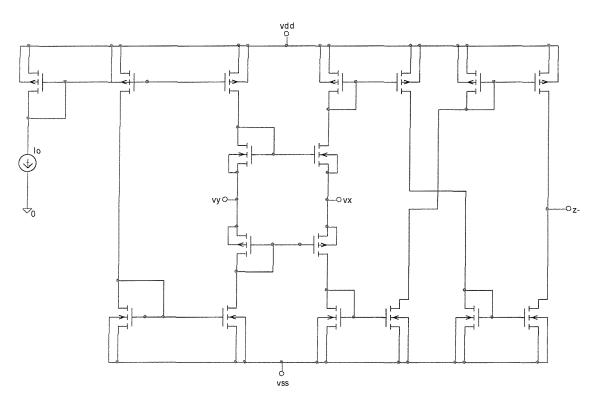

| Fig. 5-2 (a) CMOS implementation of a plus-type CCCII                                                                   | 129             |

| Fig. 5-2 (b) CMOS implementation of a minus-type CCCII                                                                  | 129             |

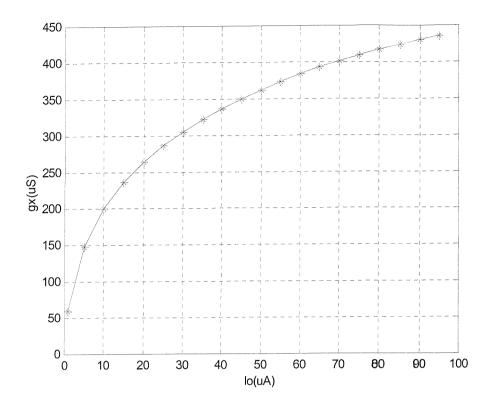

| <b>Fig. 5-2 (c)</b> Relationship between $G_x$ (=1/ $R_x$ ) and $I_o$ for the CMOS CCCII [61-62]                        | 130             |

| Fig. 5-3 Translinear loop in the CMOS implementation of a CCCII                                                         | 130             |

| Fig. 5-4 Multifunctional CCCII-C biquad [63]                                                                            | 133             |

| Fig. 5-5 Multifunctional CCCII-C biquad [64]                                                                            | 133             |

| Fig. 5-6 Multifunctional CCCII-C biquad [65]                                                                            | 134             |

| Fig. 5-7 Multifunctional CCCII-C biquad [66]                                                                            | 134             |

| Fig. 5-8 Multifunctional OTA-C biquad [22]                                                                              | 136             |

| Fig. 5-9 Multifunctional OTA-C biquad [23-4(a)]                                                                         |                 |

| Fig. 5-10 Multifunctional OTA-C biquad [23-5(a)]                                                                        | 137             |

| Fig. 5-11 Universal OTA-C biquad [24]                                                                                   | 137             |

| Fig. 5-12 Universal OTA-C biquad [25]                                                                | 138 |

|------------------------------------------------------------------------------------------------------|-----|

| Fig. 5-13 Universal OTA-C biquad [26]                                                                | 138 |

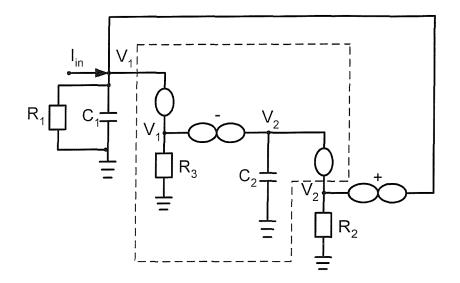

| Fig. 5-14 A nullor symbol with a nullator and a norator                                              | 139 |

| Fig. 5-15 Realization of the first equation in Eq. (5-7)                                             | 140 |

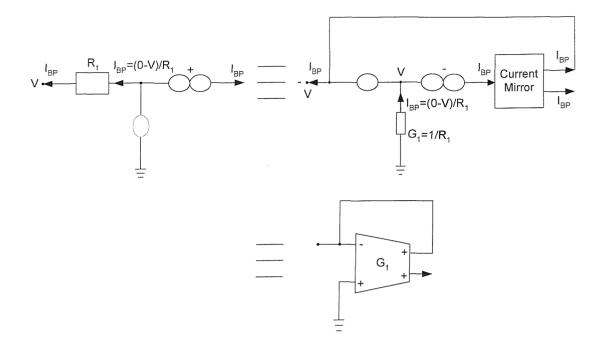

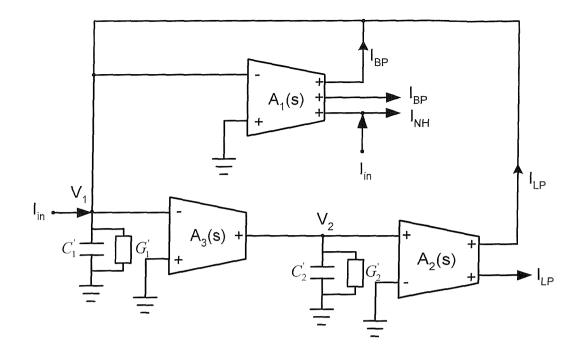

| Fig. 5-16 Realization of Eq. (5-7)                                                                   | 141 |

| Fig. 5-17 Realization of Eq. (5-7) with an available output current signal                           | 142 |

| Fig. 5-18 Realization of Eq. (5-7) with two available output current signals, $I_{BP}$ and           |     |

| <i>I<sub>LP</sub></i>                                                                                | 143 |

| Fig. 5-19 New biquad filter model.                                                                   | 144 |

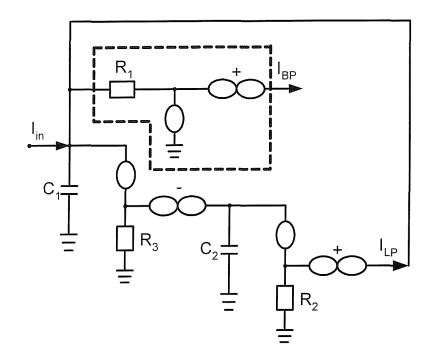

| Fig. 5-20 Fundamental nullor- <i>R</i> topology                                                      | 145 |

| Fig. 5-21 Implementation derived from the new biquad filter model based on                           |     |

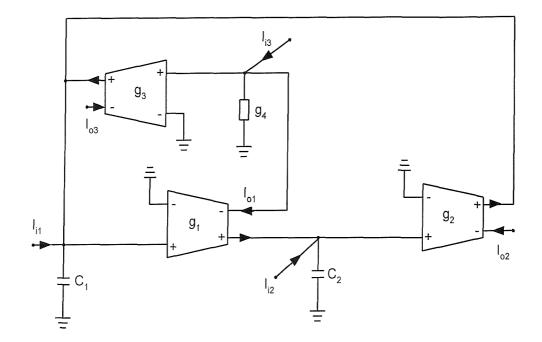

| CCCIIs                                                                                               | 147 |

| Fig. 5-22 Two equivalent nullor- <i>G</i> topologies of an OTA                                       | 148 |

| Fig.5-23 Nullor equivalence                                                                          | 148 |

| <b>Fig. 5-24</b> Two equivalent nullor- <i>G</i> topologies of a single-input OTA                    | 150 |

| <b>Fig. 5-25</b> Two Equivalent nullor- $R_i$ or $G_i$ topologies                                    | 151 |

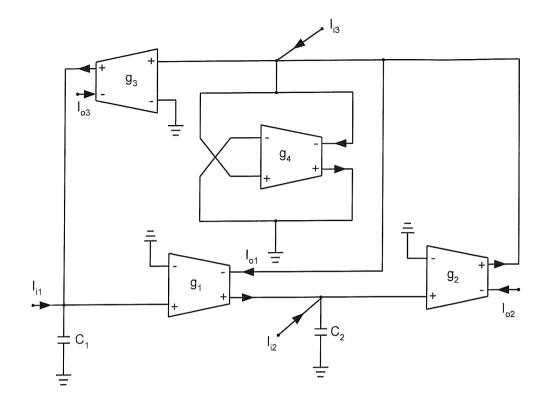

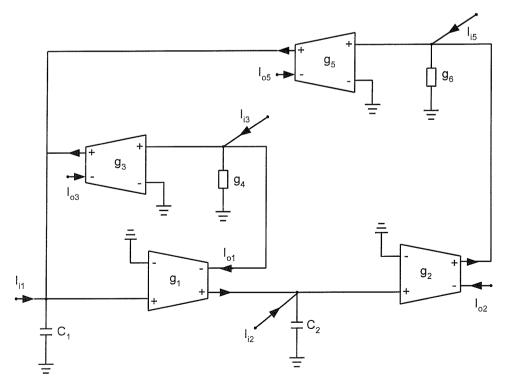

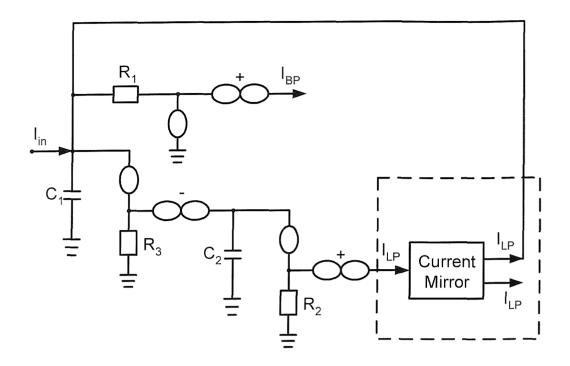

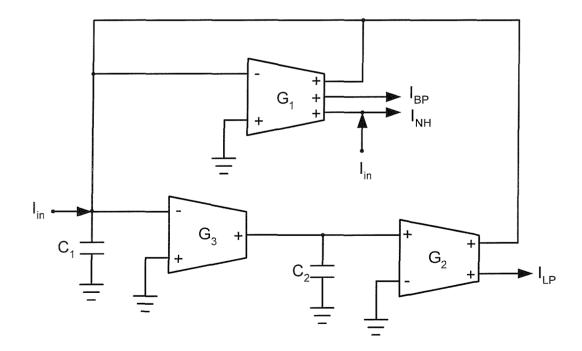

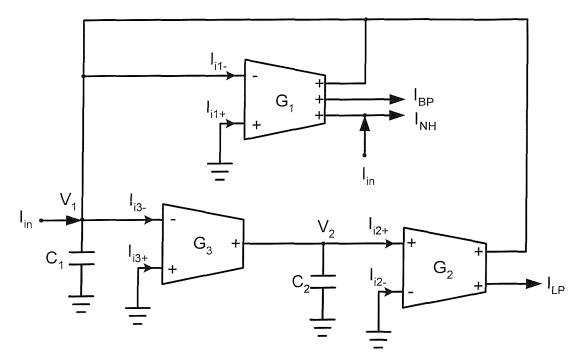

| Fig. 5-26 Implementation derived from the new biquad filter model based on OTAs                      | 151 |

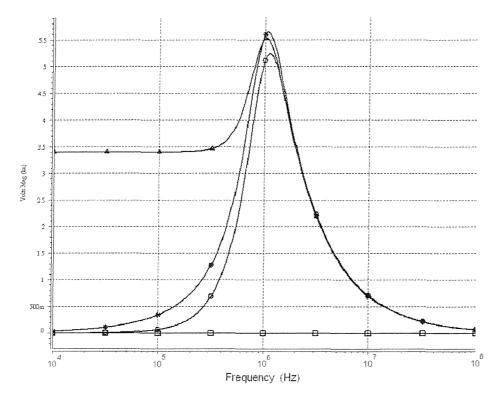

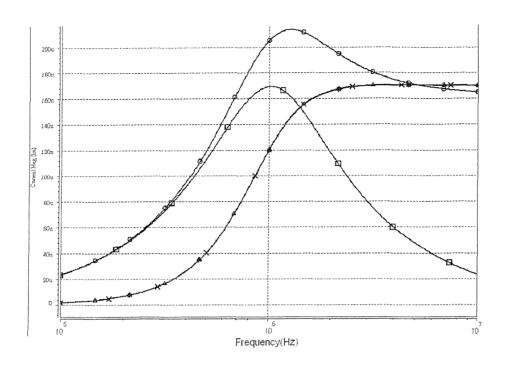

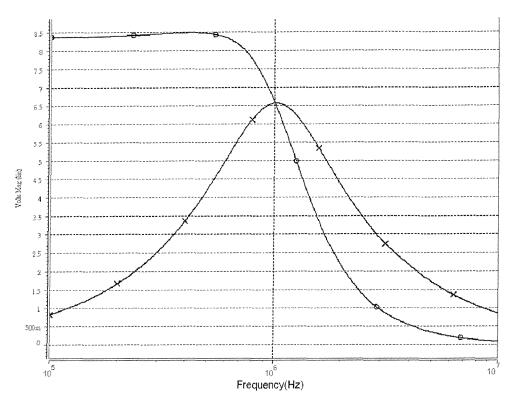

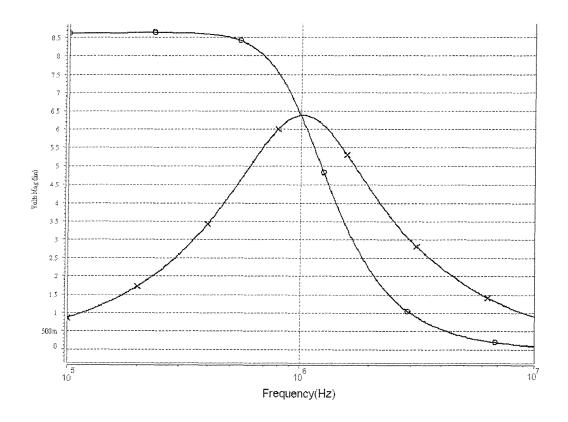

| Fig. 5-27 LP, BP and BR amplitude frequency responses Fig. 5-26                                      | 153 |

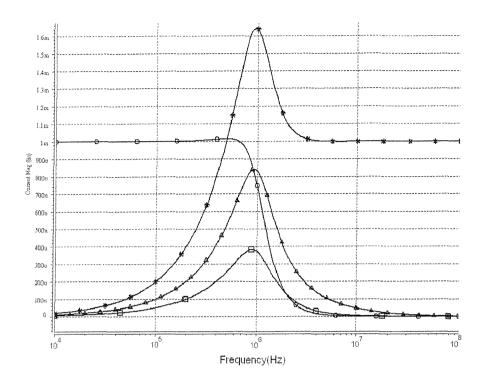

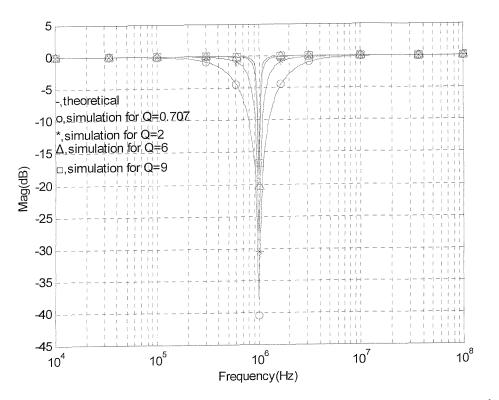

| Fig. 5-28 Band-pass amplitude frequency responses with Q=0.707, 2, 6, and 10                         | 153 |

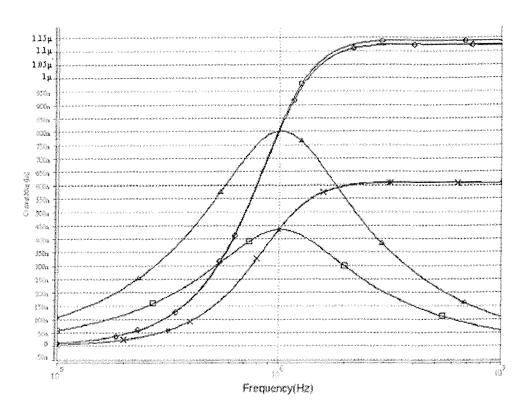

| Fig. 5-29 Band-reject amplitude frequency responses with Q=0.707, 2, 6, and 10                       | 154 |

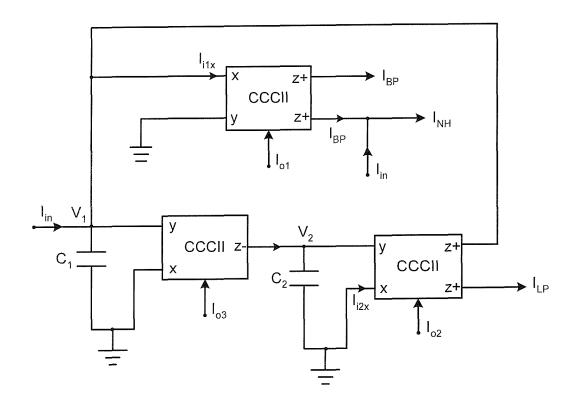

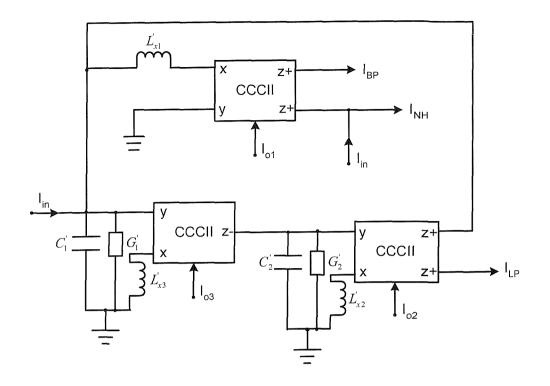

| Fig. 5-30 CCCII-based implementation                                                                 | 154 |

| <b>Fig. 5-31</b> (a) Amplitude-frequency responses of node voltages, $V_1(x)$ , and $V_2(o)$         | 155 |

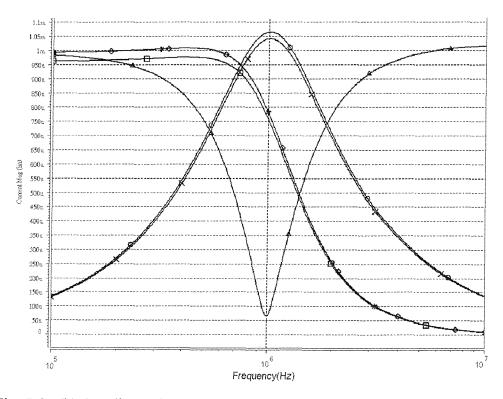

| <b>Fig. 5-31</b> (b) Amplitude-frequency responses of branch currents, $I_{ilx}(x)$ , $I_{BP}(0)$ ,  |     |

| $I_{NH}(\Delta), I_{i2x}(\Box), \text{ and } I_{LP}(*, \Diamond).$                                   | 155 |

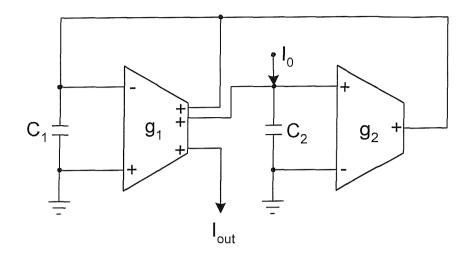

| Fig. 5-32 OTA-based implementation                                                                   | 156 |

| <b>Fig. 5-33</b> (a) Amplitude-frequency responses of node voltages, $V_1$ (x), and $V_2$ (o)        | 156 |

| <b>Fig. 5-33</b> (b) Amplitude-frequency responses of branch currents, $I_{il+}(x)$ , $I_{il-}(0)$ , |     |

| $I_{i2}(\Delta), I_{i2+}(\Box), I_{i3+}(*), \text{ and } I_{i1-}(\Diamond).$                         | 157 |

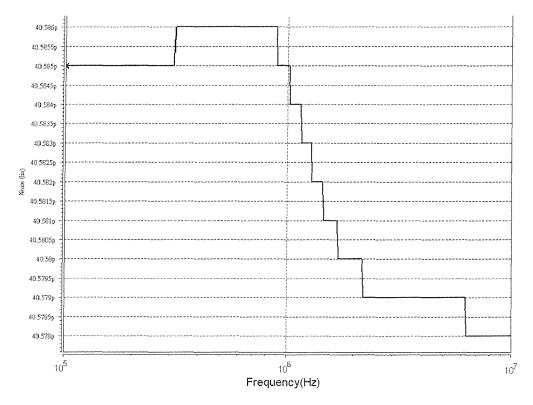

| Fig. 5-34 Noise simulation result: low-pass amplitude-frequency response of Fig. 5-30                | 157 |

| Fig. 5-35 Noise simulation result: low-pass amplitude-frequency response of Fig. 5-32                |     |

| Fig. 6-1 2 <sup>nd</sup> -order DIMOC filter structure                                               | 161 |

| Fig. 6-2 Fourth-order voltage-mode OTA-C high-pass filter                                            | 164 |

| Fig. 6-3 Fourth-order voltage-mode OTA-C all-pass filter                                             | 164 |

| Fig. 6-4 Fourth-order voltage-mode OTA-C general all-pass filter                                     | 165 |

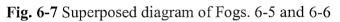

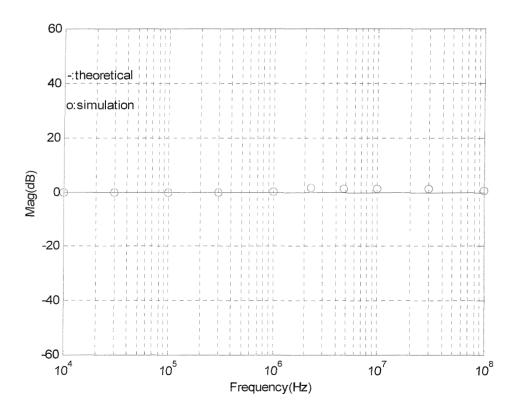

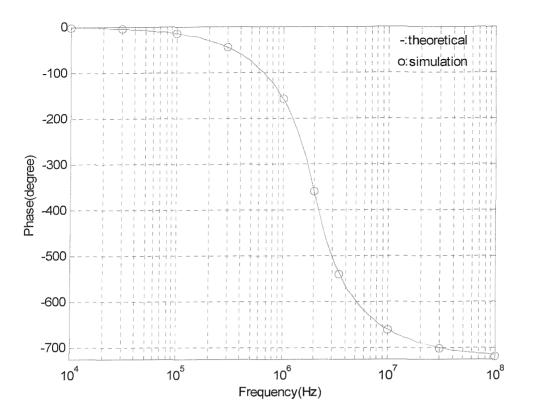

| Fig. 6-5 Amplitude-frequency response (OTA-based high-pass)                                          | 167 |

| Fig. 6-6 Amplitude-frequency response (CCCII-based high-pass)16                                          | 7 |

|----------------------------------------------------------------------------------------------------------|---|

| Fig. 6-7 Superposed diagram of Fogs. 6-5 and 6-616                                                       | 8 |

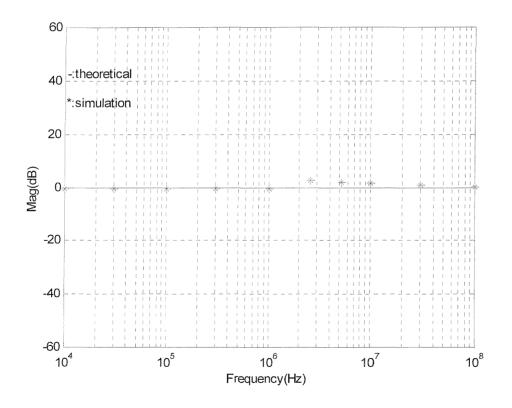

| Fig. 6-8 (a) Amplitude-frequency response (OTA-based all-pass)16                                         | 8 |

| Fig. 6-8 (b) Phase-frequency response (OTA-based all-pass)16                                             | 9 |

| Fig. 6-9 (a) Amplitude-frequency response (CCCII-based all-pass)16                                       | 9 |

| Fig. 6-9 (b) Phase-frequency response (CCCII-based all-pass)17                                           | 0 |

| Fig. 6-10 (a) Superposed diagram of Figs. 6-8 (a) and 6-9 (a)176                                         | 9 |

| Fig. 6-10 (b) Superposed diagram of Figs. 6-8 (b) and 6-9 (b)17                                          | 1 |

| Fig, A1-1 Preliminary synthesized filter structure                                                       | 8 |

| Fig. A1-2 Synthesized filter structure of Eq. (A1-1)                                                     | 9 |

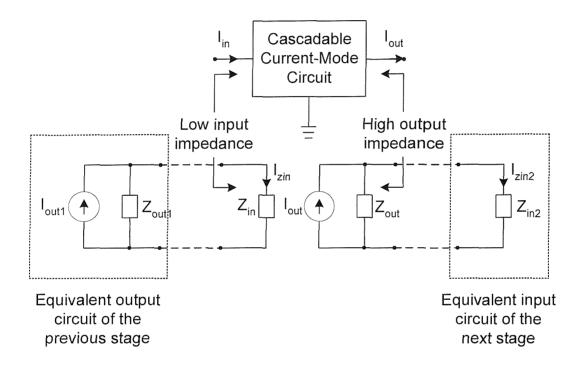

| Fig. A2-1 Input and output relationships of a cascadable current-mode circuit190                         | ) |

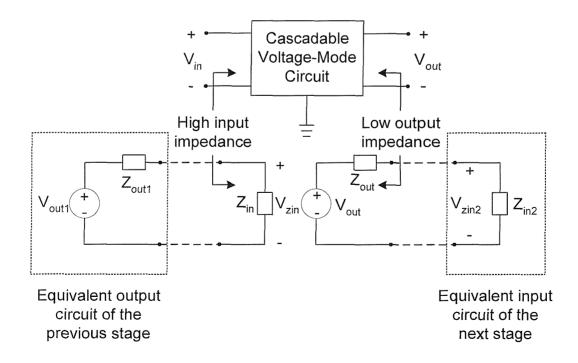

| Fig. A2-2 Input and output relationships of a cascadable voltage-mode circuit19                          | 1 |

| Fig. A4-1 Non-ideal implementation of the unified OTA-based biquad filter20                              | 4 |

| Fig. A4-2 Preliminary non-ideal implementation of the unified OTA-based biquad filter                    |   |

| without the non-ideal effects of $\beta(s)$ and $\alpha(s)$                                              | 5 |

| Fig.A5-1 Current-mode OTA-C low-pass biquad using MISOC synthesis method20                               | 7 |

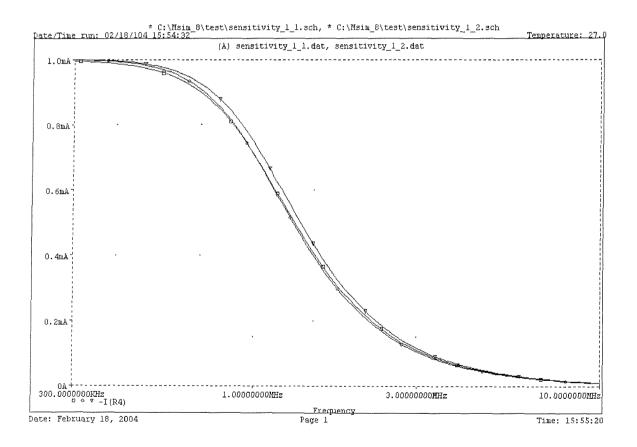

| Fig. A5-2 PSpice sensitivity results of Fig. A5-1 with 5 % component tolerance                           |   |

| ( $\Box$ , nominal; $\diamond$ , $C_1$ with $\pm 5\%$ error; $\nabla$ , $C_2$ with $\pm 5\%$ error)207   | 7 |

| Fig. A5-3 PSpice sensitivity results of Fig. A5-1 with 5 % component tolerance                           |   |

| ( $\Box$ , nominal; $\diamond$ , worst case, both $C_1$ and $C_2$ with $\pm 5\%$ error)208               | 3 |

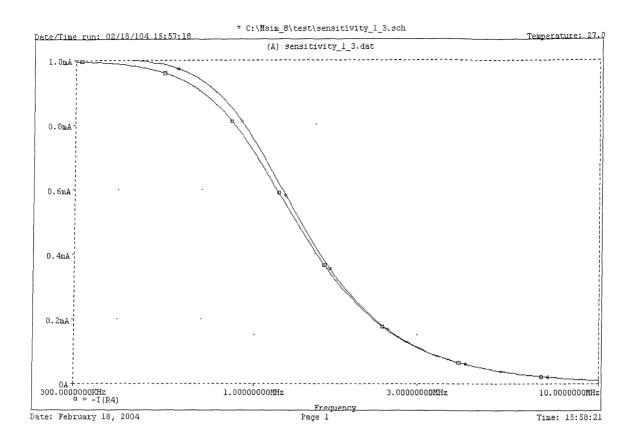

| Fig. A5-4 Voltage-mode OTA-C all-pass biquad                                                             | 9 |

| ( $\Box$ , nominal; $\diamond$ , $C_1$ with $\pm 10\%$ error; $\nabla$ , $C_2$ with $\pm 10\%$ error)209 | ) |

| Fig. A5-6 PSpice sensitivity results of Fig. A5-4 with 10 % component tolerance                          |   |

| ( $\Box$ , nominal; $\diamond$ , worst case, both $C_1$ and $C_2$ with $\pm 10\%$ error)210              | ) |

| Fig. A5-7 Unified CCCII-based biquad filter                                                              | L |

| ( $\Box$ , nominal; $\diamond$ , $C_1$ with $\pm 5\%$ error; $\nabla$ , $C_2$ with $\pm 5\%$ error)211   |   |

| Fig. A5-9 PSpice sensitivity results of Fig. A5-7 with 5 % component tolerance                           |   |

| ( $\Box$ , nominal; $\diamond$ , worst case, both $C_1$ and $C_2$ with $\pm 5\%$ error)                  |   |

## Chapter 1 Introduction

The most elegant solution to a filter synthesis problem is to decompose analytically the required filter transfer function into a set of equations that can be realized using simple analogue processing blocks such as integrators. The analytical synthesis approach has many benefits; for example the ability to generate filter circuits in a systematic and structured way, and the ability to obtain filter circuits with different transfer functions (i.e. responses) simply by suitable choice of equations. Furthermore, analytical synthesis offers the designer explicit relations that provide insight into the filter's behaviour. This analytical synthesis method was demonstrated in the following three approaches.

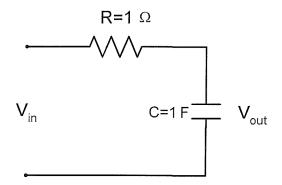

I. Differential-analyzer technique [1-2]: In many electrical problems involving transducers or energy conversion, an input variable (stimulus) x(t) produces an output (response) y(t) related to x(t) by a linear differential equation

$$\frac{d^{n}y}{dt^{n}} + a_{n-1}\frac{d^{n-1}y}{dt^{n-1}} + \dots + a_{0}y = b_{m}\frac{d^{m}x}{dt^{m}} + b_{m-1}\frac{d^{m-1}x}{dt^{m-1}} + \dots + b_{0}x$$

(1-1)

where the  $a_i$ ,  $b_k$  are given constant coefficients, and  $n \ge m$ . The dynamic input-output relationship expressed by Eq. (1-1) is brought out more clearly if we write it in terms of a time-invariant linear transfer operator H(p), i.e.,

$$y(t) = H(p)x(t) = \frac{b_m p^m + b_{m-1} p^{m-1} + \dots + b_0}{p^n + a_{n-1} p^{n-1} + \dots + a_0} x(t) \quad \left(p \equiv \frac{d}{dt}\right)$$

(1-2)

Eq. (1-2) is rewritten as

$$y = b_n x + \frac{1}{p} (b_{n-1} x - a_{n-1} y) + \frac{1}{p^2} (b_{n-2} x - a_{n-2} y) + \dots + \frac{1}{p^n} (b_0 x - a_0 y)$$

(1-3)

where  $b_i = 0$  for i > m. Introduce the n new variables

$$v_{1} = y - b_{n}x$$

$$v_{2} = a_{n-1}y - b_{n-1}x + \frac{dv_{1}}{dt}$$

$$v_{3} = a_{n-2}y - b_{n-2}x + \frac{dv_{2}}{dt}$$

....

$$v_{n} = a_{1}y - b_{1}x + \frac{dv_{n-1}}{dt}$$

$$0 = a_{0}y - b_{0}x + \frac{dv_{n}}{dt}$$

(1-4)

The given differential equation (1-4) is equivalent to the system of n first-order equations

$$\frac{dv_{n}}{dt} = b_{0}x - a_{0}y$$

$$\frac{dv_{n-1}}{dt} = v_{n} + b_{1}x - a_{1}y$$

$$\frac{dv_{n-2}}{dt} = v_{n-1} + b_{2}x - a_{2}y$$

.....

$$\frac{dv_{1}}{dt} = v_{2} + b_{n-1}x - a_{n-1}y$$

$$y = v_{1} + b_{n}x$$

(1-5)

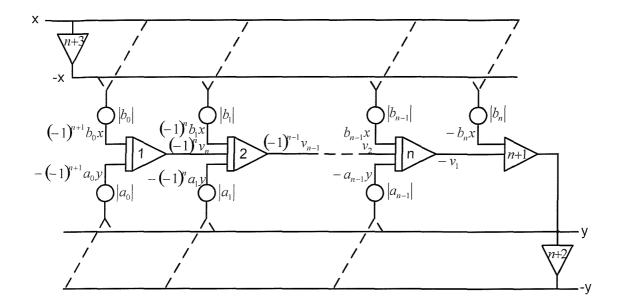

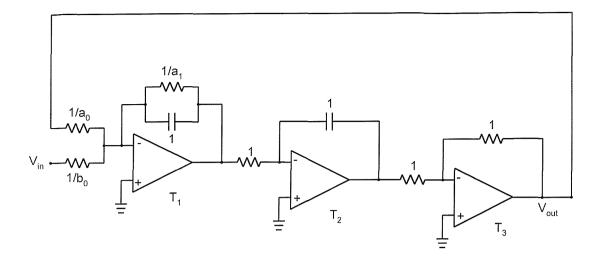

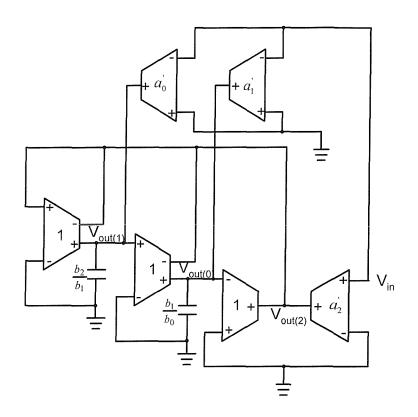

These relations are implemented by a number of operational amplifiers (OAs) and resistors to realize integrators, summer/phase inverters, and coefficient-setting potentiometers, shown in Fig. 1-1.

Fig. 1-1 Implementation of the differential-analyzer technique [1-2]

Although the iterative approach of the differential-analyzer technique is quite attractive, the implementation shown in Fig. 1-1 suffers from the use of too many active elements and resistors.

**II. Tow-Thomas algebraic decomposition technique [3-5]:** The disadvantage, use of too many components, of the above approach was improved by the analytical synthesis method for the Tow-Thomas biquad [3-5], where the second-order low-pass transfer function is manipulated algebraically until a set of equations are produced which are then realized using two integrators and an inverting amplifier. It is also sometimes called the "ring of 3 circuit". The analytical synthesis method is shown as follows. Let the voltage-mode low-pass transfer function be

$$\frac{V_{out}}{V_{in}} = \frac{-b_0}{s^2 + a_1 s + a_0}$$

(1-6)

We wish to manipulate the equation until it has a form that can be identified with simple circuits. Rewrite Eq. (1-6) as

$$\left(s^{2} + a_{1}s + a_{0}\right)V_{out} = -b_{0}V_{in}$$

(1-7)

Divide this equation by the factor  $(s^2 + a_1 s)$ , it becomes

$$\left[1 + \frac{a_0}{s(s+a_1)}\right] V_{out} = \frac{-b_0}{s(s+a_1)} V_{in}$$

(1-8)

This equation can be manipulated to produce

$$V_{out} = \left[\frac{-a_0}{(s+a_1)}V_{out} + \frac{-b_0}{(s+a_1)}V_{in}\right]\left(\frac{-1}{s}\right)(-1)$$

(1-9)

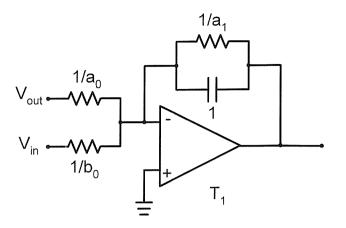

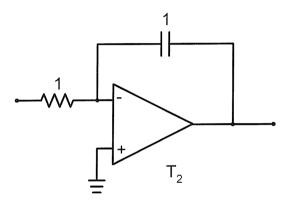

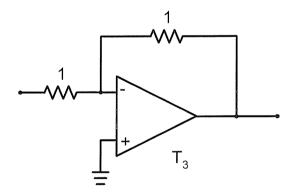

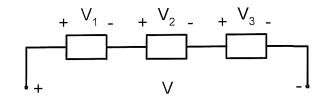

Starting at the right-hand side of this equation, we recognize that the (-1) term may be realized by an inverting circuit of gain 1. Similarly, the factor (-1/s) is realized by an inverting integrator. Two operations are indicated by the remaining factor. The circuit realization must produce a sum of voltages, and it must have a transfer function of the form  $1/(s + a_1)$ . The three circuits that provide these three operations are shown in Fig. 1-2. The circuit marked T<sub>1</sub>, where the OA is the active element, sums voltages V<sub>out</sub> and V<sub>in</sub> with appropriate multiplication, and also realizes the first-order transfer function with a circuit called a lossy integrator. The circuit marked T<sub>2</sub> is the standard inverting integrator circuit, and the circuit marked T<sub>3</sub> is an inverting circuit of unity gain. If we connect the three circuits together, including a feedback connection of the output V<sub>out</sub> to the input, the result is the circuit shown in Fig. 1-3 (in which the component values are normalized and can be de-normalized to meet the designer's requirement). This is called the biquad circuit, the ring of 3 circuit, or the Tow-Thomas biquad.

Therefore, the Tow-Thomas biquad uses 3 OAs, 6 resistors, and 2 capacitors much simpler than 7 OAs, 15 resistors, and 2 capacitors employed by differential-analyzer technique for realizing a second-order low-pass transfer function.

Fig. 1-2 Three circuits provided for the three parts in Eq. (1-9)

Fig. 1-3 Tow-Thomas biquad [3-5]

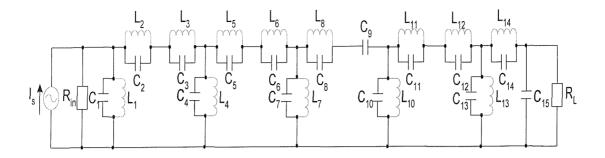

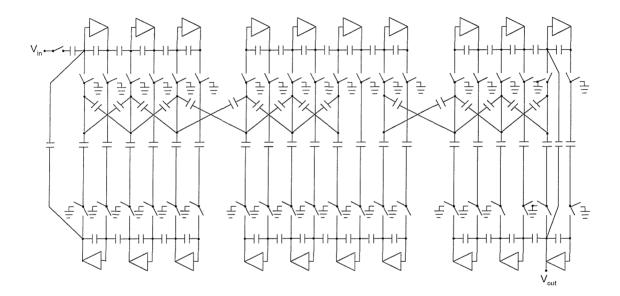

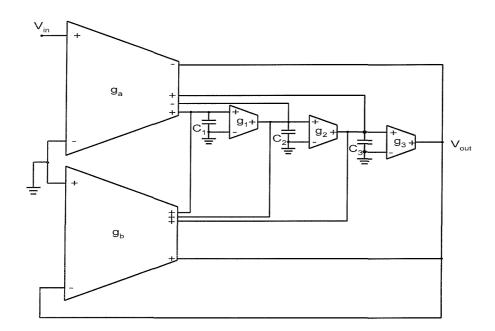

III. Ping-Sewell matrix decomposition technique [6]: A methodology has been developed for the design of switched-capacitor (SC) ladder simulation filters by using OAs. The design procedures for integrated ladder filter design by operational simulation are regularized in terms of matrix decomposition. This provides a systematic framework for the derivation of standard circuits. A wide range of circuits can be derived by adopting different matrix factorizations, notably LU and UL decomposition, including both existing and novel structure. Each circuit is now seen to belong to a certain family, dependent on the type of matrix factorization employed. A detailed comparison of various SC circuit structures has been undertaken and some notable conclusions are: the left-LUD method is the best choice for filters with very narrow and very wide passbands; the leapfrog method is the best choice for sharp transition low-pass filter design; and cascade biquads are the best choice for moderately selective low-pass and band-pass filter design. A 20<sup>th</sup>-order band-pass ladder (Fig. 1-4) is simulated by the left-LUD circuit (Fig. 1-5). As can be seen, the structure is very regular and the long unswitched capacitor op-amp chains have been broken by introducing two negative elements into the prototype. Some special design techniques can be applied to produce efficient circuits in other techniques such as continuous-time active-RC filters.

Fig. 1-4 20<sup>th</sup>-order band-pass ladder prototype

Fig. 1-5 Left-LUD SC ladder simulation with broken loops

The three synthesis methods described are very useful in developing filter structures in a formal manner. Particularly, since methods I and III can be used to design nth-order filters with different filtering functions but method II (algebraic decomposition technique) only for the second-order filtering synthesis, this thesis presents a new formal method for synthesizing nth-order filters starting from algebraically decomposing a single complicated equation representing an nth-order filter transfer function with different responses; under the constraint that the generated set of equations must be realizable using simple circuitry. The motivation behind this work is to develop an efficient analytical synthesis approach for high-order current-/voltage-mode filters.

Which active element is appropriately used in the new analytical synthesis method? Two active elements that have received considerable attention from the research community over the last two decades in analogue filter design are: operational transconductance amplifiers (OTAs), and second-generation current conveyors (CCIIs). The most attractive tunable transconductance element is the operational transconductance amplifier (OTA). The transconductance g of an OTA is adjustable within the range of several decades by a supplied bias current  $I_{abc}$  (amplifier bias current). Therefore, the OTA provides linear electronic tunability and a wide tunable range of its transconductance gain. Moreover, it is easy to control its parasitic distortion due to only ordinary parasitic capacitances and conductances existed at its input and output ports unlike the second-generation current conveyor (CCII) with additional parasitic inductance, and non-ideal frequency-dependent current and voltage transfer constraints (referring to Appendix 4). Few recently reported CCIIbased high-order filter structures [67-72] were proposed and had shown that too many resistors were unavoidable unlike complimentary OTA-based high-order filter structures [7-20] without the need of resistors. The following three main advantages of the OTA,

- tunable transconductances,

- easier control of its non-ideal factors,

- suitable for integration due to the absence of resistors,

lead us to choose the OTA as the active element to synthesize high-order voltage/current-mode filter transfer functions in this thesis.

Over the last decade or so numerous voltage-mode and current-mode high-order OTA-C filter structures have been reported [7-20]. Such structures have often been developed with different design criteria in mind, including reduced number of active elements, single-input OTAs, grounded capacitors, and simple design methods. It has shown in [13], that there are *three main important criteria* that need to be considered when generating OTA-C filter structures. The *three main important criteria* are:

- filters use grounded capacitors because they have smaller chip area than the floating counterpart, and because they can absorb equivalent shunt capacitive parasitics;

- filters employ only single-input OTAs to overcome the feed-through effects due to finite input parasitic capacitances associated with double-input OTAs;

- filters have the least number of components (passive and active) for a given order to reduce power consumption, chip areas, and noise.

Despite the extensive literature on active filters [7-20], none of the high-order OTA-C filters are capable of achieving the above *three main important criteria* simultaneously and without trade-offs. Therefore, there is still a need to develop new high-order filter structures that offer more advantages than existing structures which is the main motivation of the research discussed in this thesis.

On the other hand, the OTAs and CCIIs mentioned earlier are powerful analogue building blocks, combining voltage and current-mode capability. A number of novel filter functions and topologies [7-72] have been explored on the broader front of current-mode and voltage-mode analogue filters, opening up wider areas of interest. Despite the extensive literature on active filters, none of the biquads are capable of achieving the following *five performance parameters* simultaneously and without trade-offs,

- universal filtering (low-pass, high-pass, band-pass, notch, and all-pass),

- minimum components count (three active elements, two grounded capacitors, and no resistors),

- independent  $\omega_o$  and  $\omega_o/Q$  tunability,

- no need to impose component choice conditions to realize specific filtering functions (which leads to no influence resulted from fabrication tolerances and drifts during operating), and

• no need to employ additional active elements to provide filter current outputs explicitly.

Therefore, there is still a need to develop new biquadratic structures that offer more advantages than existing structures which is another motivation of the research described in this thesis.

### **Motivation Summary of This Thesis**

Following the above statements, the motivation, for this thesis, has two main strands:

(i) Develop an efficient analytical synthesis approach to decompose a single complicated equation representing an nth-order filter transfer function with different responses into a set of simple equations for realising high-order current-/voltage-mode OTA-C filters which are optimal in terms of the *three main important criteria* stated above and without trade-offs.

(ii) Despite the extensive literature on voltage-mode and current-mode filter design as outlined earlier [21-66], there is still a need to investigate and develop new active filter biquads that have less component counts, only three active elements and two grounded capacitors but without any resistors, and exhibit desirable VLSI features including grounded passive elements, or enjoy the *five performance parameters* stated above without trade-offs.

### **Contributions and Thesis Structure**

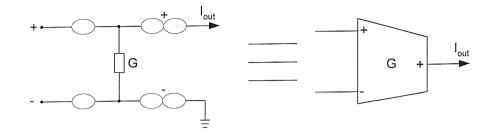

This research has shown that the new analytical synthesis method decomposes a complicated nth-order filter transfer function with different responses into a set of simple equations which can be implemented using simple circuitry. Two current-mode and three voltage-mode nth-order filter structures with the least passive and active component count are presented. Furthermore, the produced filter circuits have two attractive features: grounded capacitors and single-input OTAs, and two more beneficial VLSI realisations: equal transconductance and equal capacitance for two

new voltage-mode filter structures. This research has also demonstrated how a filter model based on nullators and norators (whose definitions are shown in Section 5.2 based on Fig. 5-14) can facilitate the development of two *unified* biquads that are capable of achieving simultaneously a number of key important performance parameters and without trade-offs. Therefore, it is hoped that the methods and structures proposed in this thesis will contribute to the area of analogue signal processing and IC design.

The remainder of this thesis is organized as follows.

Chapter 2 provides a survey of the most relevant and related works and outlines the necessary background information that is helpful for the understanding of the discussed subject. Based upon four design principles (in order to meet the three important criteria: using single-input OTAs, grounded capacitors, and the least number of components).

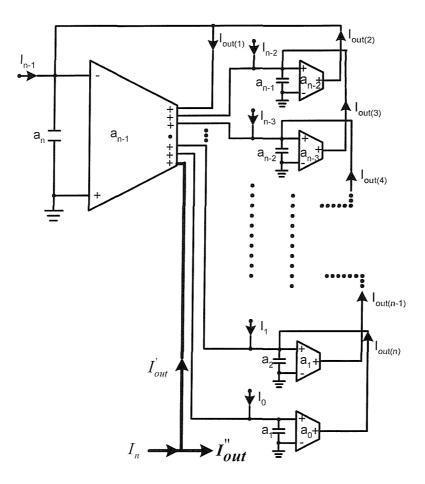

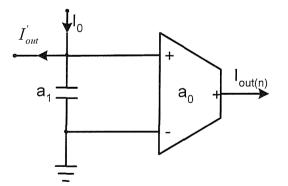

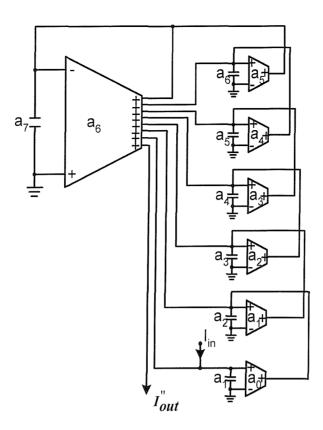

Chapter 3 presents two new current-mode analytical synthesis methods for high-order current mode OTA-C (Operational Transconductance Amplifier and Capacitor) filters by using a succession of innovative algebra manipulation to solve an nth-order current transfer function and generate n simple and realizable equations. Their two associated canonical filtering structures are then proposed. Different filter orders and functions can be obtained from the general filter structures by suitable selection either of current injection(s) at the filter inputs or of current extraction(s) at the filter outputs.

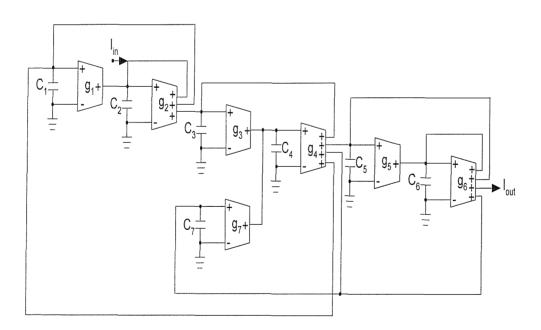

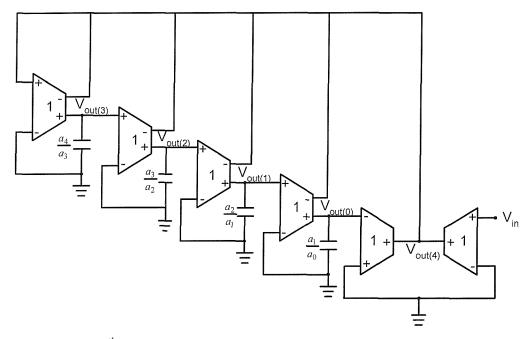

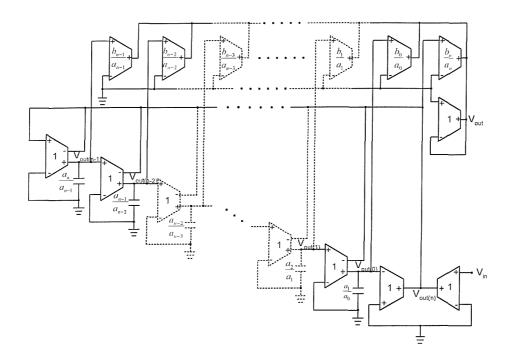

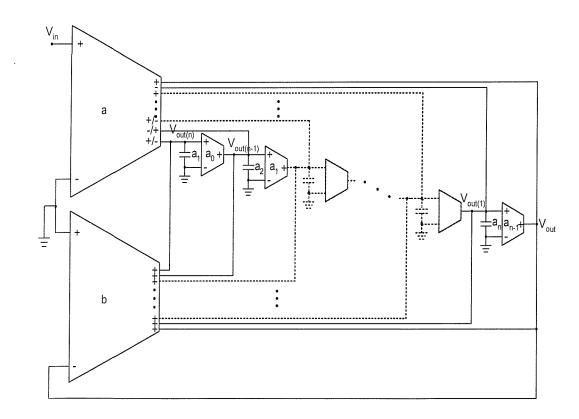

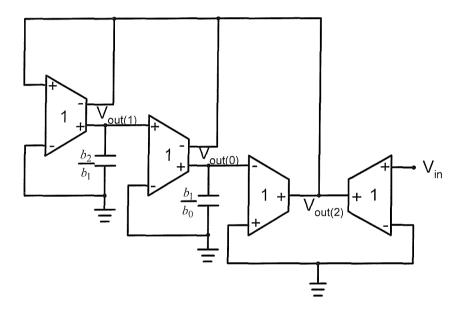

Chapter 4 presents two new voltage-mode analytical synthesis methods and three new high-order voltage-mode filter structures that employ only single-input OTAs, grounded capacitors, and the least number of components when compared with recently reported structures [7-20]. It has been shown how decomposing analytically an nth-order voltage transfer function into n+1 simple realisable transfer functions using OTA-C circuits produces the first filter structure that employs fewer active elements than the recently reported methods and offers simultaneous multiple outputs. Realizing the general transfer function by using the more effective synthesis approach different from the linear combination of each output signal of the first filter structure leads to the second filter structure which can realize any kind of voltage transfer functions, for

example, elliptic filter functions, employing the minimum components, only 2n+2 single-input OTAs, and only n grounded capacitors. The first filter structure enjoys the advantage of single biasing and easy control due to equal transconductance design. The second filter structure achieves the benefit of easy integrated circuit fabrication without tuning the values of capacitors due to equal capacitance design [86]. The second analytical synthesis method produces the third filter structure, a new nth-order OTA-C all-pass filter, far simpler in structure than the recently reported work [7-20].

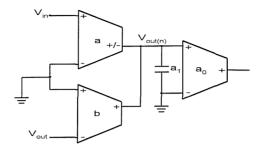

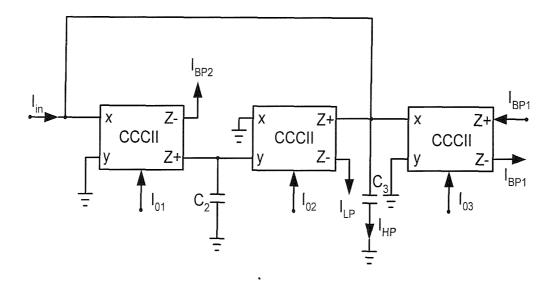

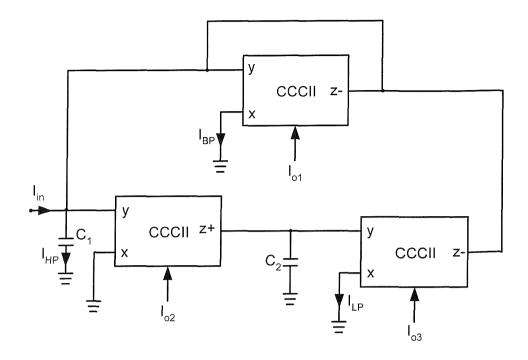

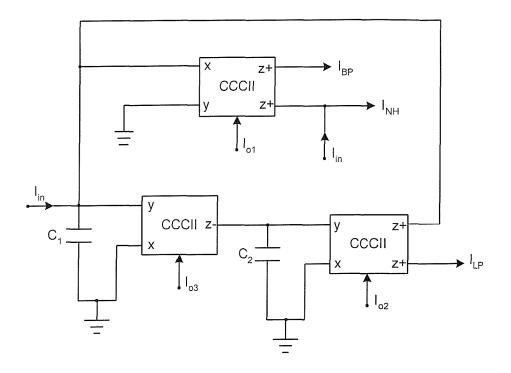

Chapter 5 designs a new *unified* biquad filter model based on nullators, norators, current mirrors and passive R (resistor) and C (capacitor) elements. Two implementations derived from the new biquad filter model by using second generation current-controlled conveyors (CCCIIs) and operational transconductance amplifiers (OTAs) are also proposed. The two biquad implementations are capable of achieving *five filter performance parameters* simultaneously and without trade-offs, including universal filtering, minimum components count and independent control of  $\omega_o$  and  $\omega_o/Q$ . This is unlike recently reported filter structures which make certain trade-offs that emphasize some parameters at the cost of others.

Chapter 6 presents a comparative analysis including a comparison between the current-mode and voltage-mode analytical synthesis methods presented in Chapters 3 and 4, and a comparison between the unified OTA-based and CCCII-based biquad filters presented in Chapter 5. It is supplied for the designers to select an appropriate synthesis method and filter structure.

Chapter 7 summarizes the new current-mode and voltage-mode analytical synthesis methods and their associated filter structure achieving the *three main important criteria*, and two unified OTA-based and CCCII-based biquad filters achieving the *five performance parameters*. Moreover, the complimentary parts of the researches, expanding the innovative core methods to surrounding useful techniques and promoting the theoretical basement to the practical applications, are suggested in Chapter 7 to be the prospective future work.

### **List of Publications**

The work presented in this thesis has resulted in the following conference and journal publications:

[1] Chun-Ming Chang, and Bashir M. Al-Hashimi, "Analytical synthesis of currentmode high-order OTA-C filters", IEEE Trans. Circuits & Syst.-I, vol. 50, no. 9, pp. 1188-1192, Sept. 2003. (This paper is relevant to the synthesis method discussed in Chapter 3.)

[2] Chun-Ming Chang, Bashir M. Al-Hashimi, Yichuang Sun, and J. Neil Ross, "New high-order filter structures using single-ended-input OTAs and grounded capacitors", IEEE Trans. Circuits & Syst.-I, accepted for publication on 2 Dec. 2003. (This paper is relevant to the first synthesis method discussed in Chapter 4.)

[3] Chun-Ming Chang, and Bashir M. Al-Hashimi, "Analytical synthesis of voltagemode OTA-C all-pass filters for high frequency operation", Proc. IEEE/ISCAS, vol. I, pp. 461-464, Bangkok, Thailand, May, 2003. (This paper is relevant to the second synthesis method discussed in Chapter 4.)

[4] Chun-Ming Chang, Bashir M. Al-Hashimi, and J. Neil Ross, "Unified active filter biquad structures", IEE Proc.-Circuits Devices Syst., accepted for publication on 7 Jan. 2004. (This paper is relevant to Chapter 5.)

## Chapter 2 Background and Literature Review

This Chapter outlines the necessary background information, including OTA and CCII symbols and biquads are introduced in Sections 2.1 and 2.2. The active current-mode and voltage-mode filters are discussed in Section 2.3 and their biquad classification in Section 2.4. A survey of the most relevant and related works is reviewed in Section 2.5 and concluded in Section 2.6 to lead to the research direction of this thesis.

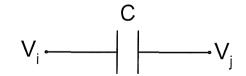

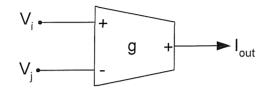

### 2.1 OTA Symbol and Biquad

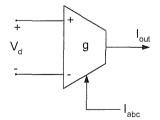

The operational transconductance amplifier (OTA) is one of the powerful analogue building blocks. Its functional block is shown in Fig. 2-1 (a). The input-output relationship of an OTA is

$$I_{out} = gV_d \tag{2-1}$$

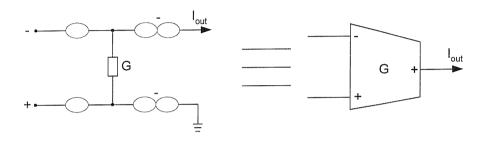

Fig. 2-1 (a) OTA functional block

The transconductance g represents the output current/input voltage ratio  $I_{out}/V_d$ . It is adjustable within the range of several decades by a supplied bias current  $I_{abc}$ (amplifier bias current). The CMOS implementations of the plus-type and minus-type OTAs are shown in Fig. 2-1 (b) and (c) [80], respectively. The simulated relationship between g and  $I_{abc}$  is shown in Fig. 2-1 (d) under  $\pm 2.5$ V supply voltages, and  $W/L=5\mu/1\mu$  and  $10\mu/1\mu$  for NMOS transistors and PMOS transistors, respectively. (Note that the CMOS implementations and the relevant simulated relationship between g and  $I_{abc}$  are used to validate the filter simulation described through out this thesis.) Therefore, the OTA provides linear electronic tunability and a wide tunable range of its transconductance gain.

Fig. 2-1 (b) CMOS implementation of a plus-type OTA [80]

Fig. 2-1 (c) CMOS implementation of a minus-type OTA [80]

Fig. 2-1 (d) Relationship between g and  $I_{abc}$  for the CMOS OTA [80]

Fig. 2-2 Matched differential pair in the CMOS implementation of an OTA

The core theory of the CMOS implementation of an OTA is relevant to the matched differential pair shown in Fig. 2-2. The detail relationship [74, 75] between the output current signal, 2i, and the input voltage difference,  $V_+ - V_-$ , is derived as follows.

Suppose  $k_1 = k_2 = k$  and  $V_{T1} = V_{T2} = V_T$  because of two matched transistors.

Then

$$I + i = k (V_{GS1} - V_T)^2$$

(2-2)

$$I - i = k \left( V_{GS2} - V_T \right)^2$$

(2-3)

And

$$V_{+} - V_{-} \equiv V = V_{GS1} - V_{GS2} = \left(\sqrt{\frac{I+i}{k}} + V_{T}\right) - \left(\sqrt{\frac{I-i}{k}} + V_{T}\right) = \sqrt{\frac{I+i}{k}} - \sqrt{\frac{I-i}{k}}$$

(2-4)

Do the square operation for both sides of Eq. (2-4).

$$V^{2} = \frac{2I}{k} - 2\sqrt{\frac{I^{2} - i^{2}}{k^{2}}} = \left(\frac{2}{k}\right)\left(I - \sqrt{I^{2} - i^{2}}\right)$$

(2-5)

Namely,

$$\sqrt{I^2 - i^2} = I - \frac{kV^2}{2}$$

(2-6)

Do the square operation for both sides of Eq. (2-6).

$$I^{2} - i^{2} = I^{2} + \frac{k^{2}V^{4}}{4} - kIV^{2}, \text{ i.e., } i^{2} = kIV^{2} - \frac{k^{2}V^{4}}{4}$$

(2-7)

Do the square root for both sides of Eq. (2-7).

$$i = \sqrt{kI}V\sqrt{1 - \frac{kV^2}{4I}} \tag{2-8}$$

Therefore, the transconductance

$$g \equiv \frac{2i}{V_{+} - V_{-}} = \frac{2i}{V} = 2\sqrt{kI}\sqrt{1 - \frac{kV^{2}}{4I}} = 2\sqrt{kI}\left(1 - \frac{kV^{2}}{8I}\right)$$

(2-9)

The term  $\sqrt{1 - \frac{kV^2}{4I}}$ , or  $\left(1 - \frac{kV^2}{8I}\right)$  causes the nonlinear distortion for large signal

inputs.

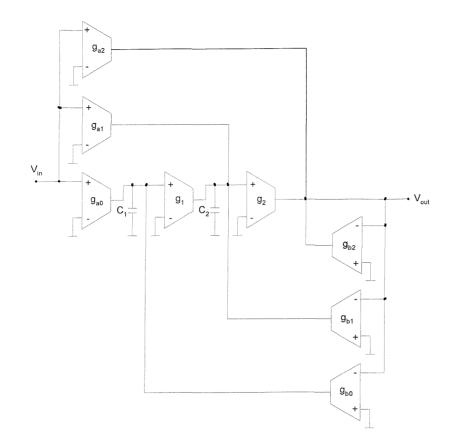

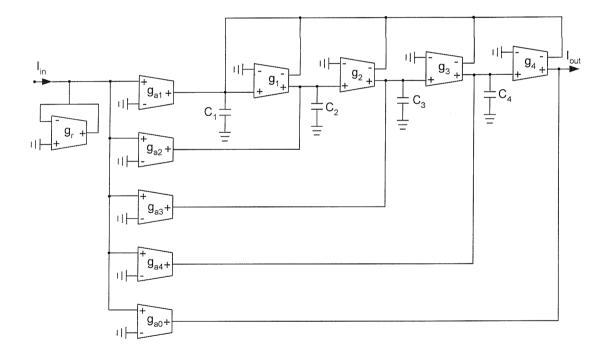

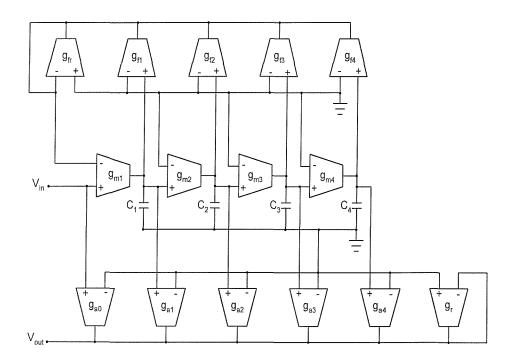

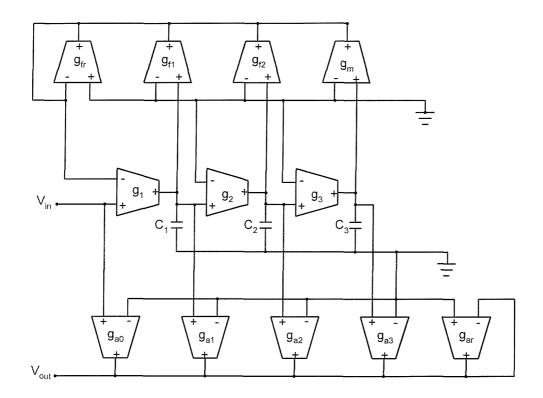

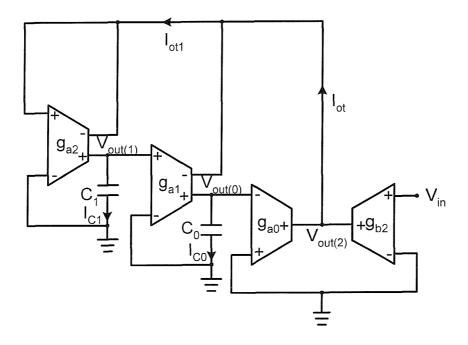

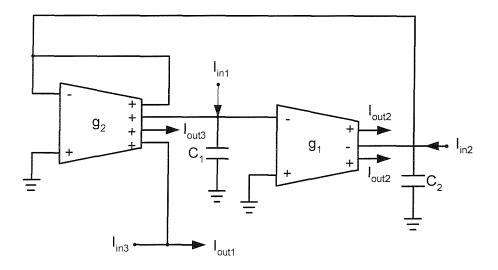

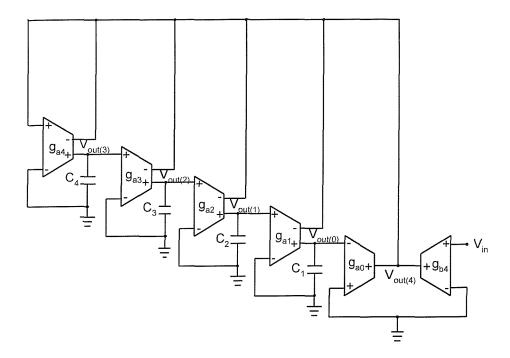

An OTA-based realisation of a universal biquad proposed by Nawrocki and Klein [21] in 1986 is shown in Fig. 2-3.

Fig. 2-3 Block diagram of voltage-mode OTA-C universal biquad [21]

The biquadratic transfer function is given by

$$H(s) = \frac{V_{out}}{V_{in}} = \frac{a_2 s^2 + a_1 s + a_0}{b_2 s^2 + b_1 s + b_0}$$

(2-10)

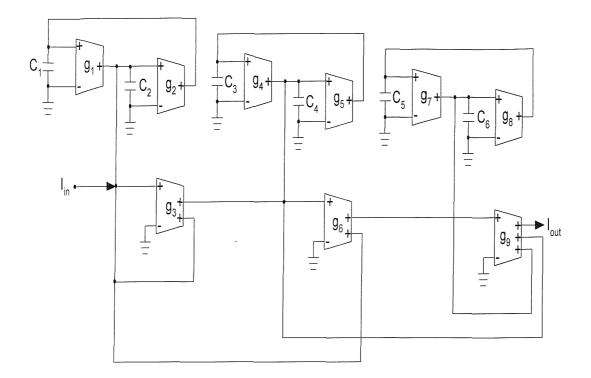

with  $a_0 = g_{a0}g_1g_2$ ,  $a_1 = g_{a1}g_2C_1$ ,  $a_2 = g_{a2}C_1C_2$ ,  $b_0 = g_{b0}g_1g_2$ ,  $b_1 = g_{b1}g_2C_1$ , and  $b_2 = g_{b2}C_1C_2$ . The different types of biquadratic filters result from the following specialisations of the numerator in Eq. (2-10):

- (i) low-pass filter:  $a_1 = a_2 = 0$

- (ii) high-pass filter:  $a_0 = a_1 = 0$

- (iii) band-pass filter:  $a_0 = a_2 = 0$

- (iv) band-reject filter:  $a_1 = 0$ , and  $a_0 = a_2$

(v) all-pass filter:

$$a_0 = b_0$$

,  $a_1 = -b_1$ , and  $a_2 = b_2$

The other way of the above filter analysis, i.e., filter synthesis, may be interesting to the reader. Using the new voltage-mode synthesis method proposed in Section 4.2, a new synthesized filter structure is obtained and has two fewer OTAs than that shown in Fig. 2-3. Appendix 1 shows the detailed synthesis process.

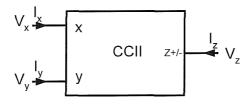

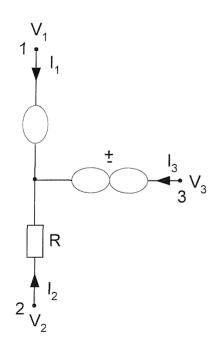

### 2.2 CCII Symbol and Biquad

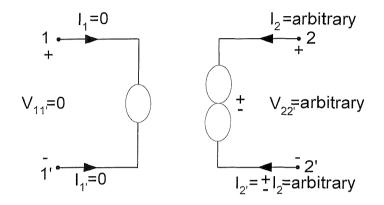

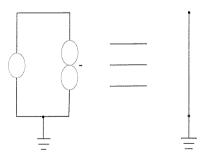

Although the design using OTAs shown in Fig. 2-3 is most suitable for integration due to the absence of resistors in the circuit, performance limitations of OTAs such as poor bandwidths and poor output drive capabilities may restrict the overall operating performance [28]. The high-performance second-generation current conveyor (CCII) is an attractive alternative to the OTA in this application because of their higher bandwidths and improved current drive capabilities [28]. From its introduction in 1970 by Sedra and Smith [29], CCIIs, whose functional block is shown in Fig. 2-4, have been proved to be functionally flexible and versatile, rapidly gaining acceptance as both a theoretical and practical building block. From 1985 to 1990, high performance implementations have emerged, to enable conveyors to challenge successfully traditional voltage operational amplifier circuits in areas such as active filters, oscillators, and amplifiers [30]. The input-output relationship of a CCII is

$$\begin{bmatrix} I_{y} \\ I_{z\pm} \\ V_{x} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ \pm 1 & 0 & 0 \\ 0 & 1 & 0 \end{bmatrix} \begin{bmatrix} I_{x} \\ V_{y} \\ V_{z} \end{bmatrix}$$

(2-11)

where the positive and negative signs refer to output terminals z+ and z-, respectively.

Fig. 2-4 CCII functional block

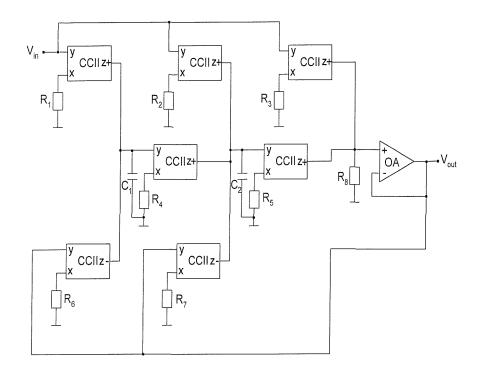

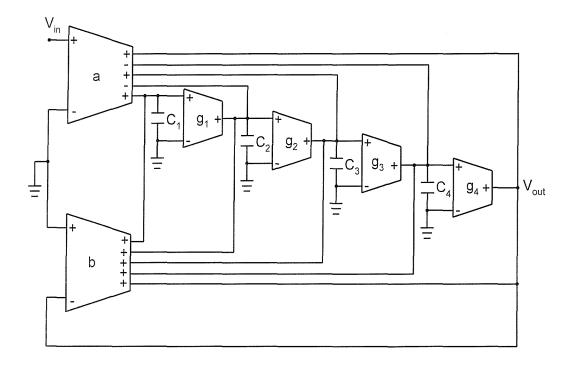

A CCII-based universal biquad, which is the counterpart of Fig. 2-3, proposed by Toumazou and Lidgey [28] in 1986 is shown in Fig. 2-5.

Circuit analysis of Fig. 2-5 yields the following voltage transfer function:

$$\frac{V_{out}}{V_{in}} = \frac{s^2 C_1 C_2 R_4 R_5 / R_3 + s C_1 R_4 / R_2 + 1 / R_1}{s^2 C_1 C_2 R_4 R_5 / R_8 + s C_1 R_4 / R_7 + 1 / R_6}$$

(2-12)

Specialisations of the numerator in Eq. (2-12) result in the following filter functions:

(i) highpass filter: R<sub>2</sub> = R<sub>1</sub> = ∞

(ii) lowpass filter: R<sub>3</sub> = R<sub>2</sub> = ∞

(iii) bandpass filter: R<sub>1</sub> = R<sub>3</sub> = ∞

(iv) bandreject filter: R<sub>2</sub> = ∞, and R<sub>3</sub> = R<sub>1</sub>

(v) allpass filter: R<sub>1</sub> = R<sub>2</sub> = R<sub>3</sub>, R<sub>6</sub> = R<sub>7</sub> = R<sub>8</sub>, and current conveyor with grounded resistor R<sub>2</sub> must change its output to be z-.

Fig. 2-5 Block diagram of voltage-mode CCII-based universal biquad [28]

In this thesis, Chapter 5 will introduce the CMOS implementations and the simulated relationship between transconductance  $g_x (= 1/R_x)$  and bias current  $I_o$  of the second-generation current-controlled conveyor (CCCII) which is an improved active element of the CCII and will be used to implement a unified biquad.

#### 2.3 Active Current-Mode and Voltage-Mode Filters

In 1989, Roberts and Sedra proposed that circuits based on current amplifiers operate at higher signal bandwidths, greater linearity and larger dynamic range, than their voltage-based circuit counter-parts [73]. Current-mode circuits have emerged over the last decade as an important class of analogue circuits. One particularly important aspect of the current amplifier is found in the influence of feedback on the amplifier bandwidth. It has been shown that properly applied current feedback will cause the upper -3dB frequency to remain constant and independent of the closed loop gain. This characteristic is extremely important in a circuit like a pipeline analogue-digital converter where the residue amplifier must have large bandwidth. A current amplifier having a gain of  $2^{N}$  where N is the number of bits in the pipe would not lose bandwidth compared to a voltage amplifier [76]. These recent advances in integrated circuit technologies have meant that state-of-the-art analogue IC design is now able to exploit the potential of current-mode analogue signal processing, providing attractive solutions for many circuit and system problems. Active filters can be divided into two classes: voltage-mode and current-mode, shown in Fig. 2-6. A voltage mode circuit is defined as a circuit which both the input and output signals are voltages. A current mode circuit has input and output signals which are both currents. Internally, however, the signal may transfer repeatedly between voltage and current [81].

Fig. 2-6 Active filter classification

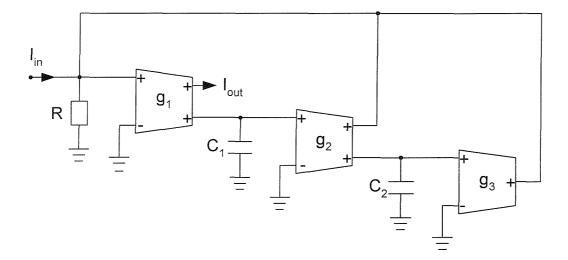

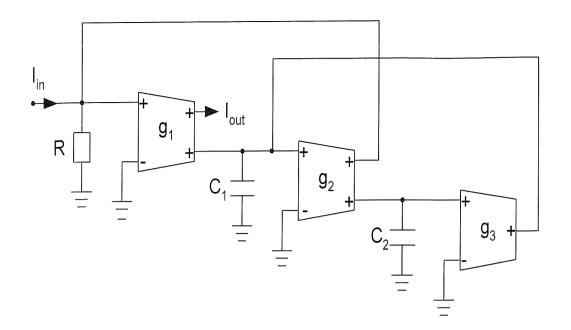

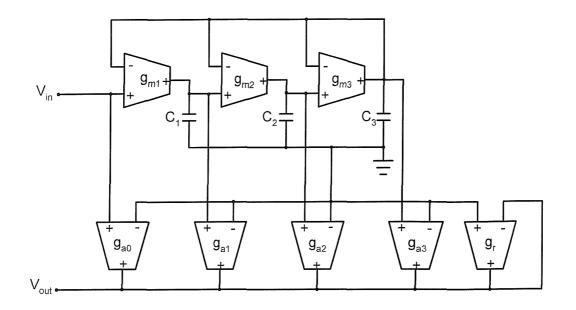

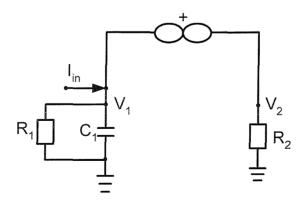

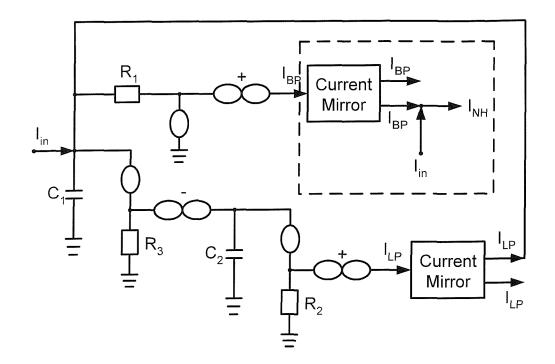

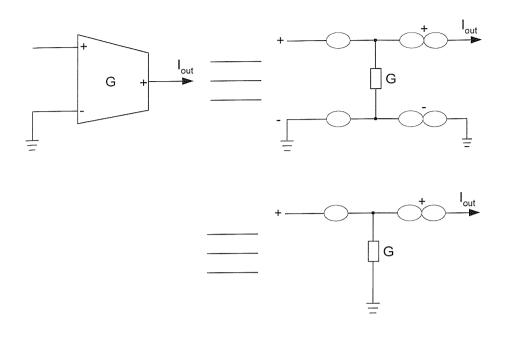

The OTAs and CCIIs described in Sections 2.1 and 2.2 are powerful analogue building blocks, combining voltage and current-mode capability. A number of novel circuit functions and topologies have been explored on the broader front of current-mode analogue circuits, opening up wider areas of interest. A current-mode OTA-based universal biquad and a CCII-based universal biquad proposed by Chang et al. [26] and Toker and Özoğuz [31] in 2000 are shown in Figs. 2-7 and 2-8, respectively.

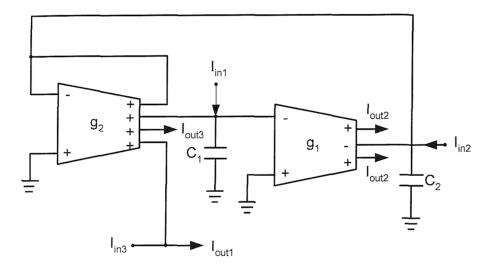

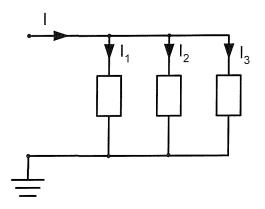

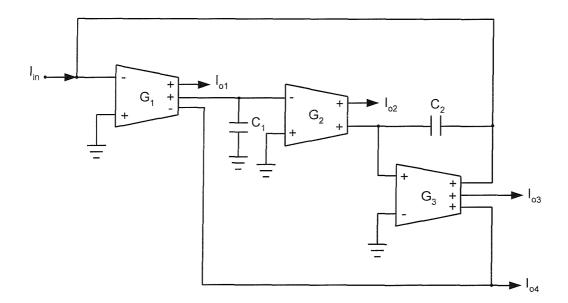

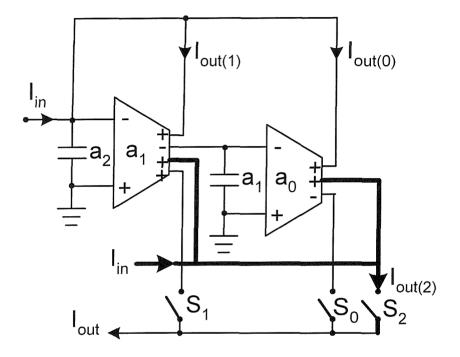

Using current mirrors, an OTA may have multiple output terminals of both positive and negative polarity as shown in Fig. 2-7. Circuit analysis yields the following current transfer functions of Fig. 2-7:

$$I_{out1} = \frac{\left[s^2 C_1 C_2 I_{in3} + s C_1 g_2 (I_{in3} - I_{in2}) + g_1 g_2 (I_{in3} - I_{in1})\right]}{s^2 C_1 C_2 + s C_1 g_2 + g_1 g_2}$$

(2-13)

$$I_{out2} = \frac{\left[-sC_2g_1I_{in1} - g_1g_2(I_{in1} - I_{in2})\right]}{s^2C_1C_2 + sC_1g_2 + g_1g_2}$$

(2-14)

$$I_{out3} = \frac{\left[sC_1g_2I_{in2} + g_1g_2I_{in1}\right]}{s^2C_1C_2 + sC_1g_2 + g_1g_2}$$

(2-15)

Fig. 2-7 Current-mode OTA-C universal biquad [26]

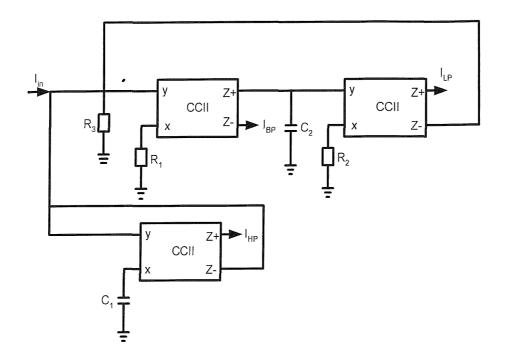

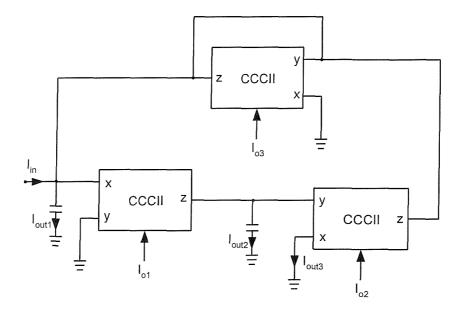

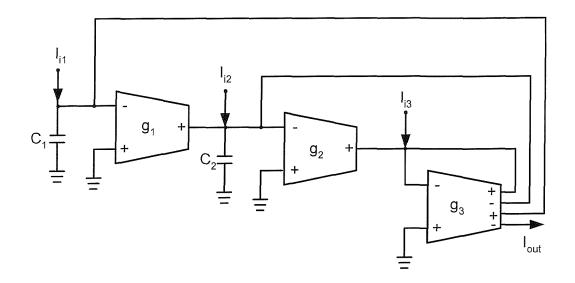

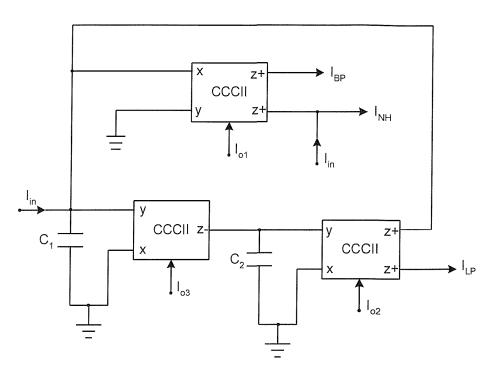

Similarly, current mirrors make additional output terminals for the CCIIs shown in Fig. 2-8. Circuit analysis of Fig. 2-8 yields the following transfer functions:

$$\frac{I_{HP}}{I_{in}} = \frac{s^2 C_1 C_2}{s^2 C_1 C_2 + s C_2 G_3 + G_1 G_2}$$

(2-16)

$$\frac{I_{LP}}{I_{in}} = \frac{G_1 G_2}{s^2 C_1 C_2 + s C_2 G_1 + G_1 G_2}$$

(2-17)

$$\frac{I_{BP}}{I_{in}} = \frac{sC_2G_1}{s^2C_1C_2 + sC_2G_1 + G_1G_2}$$

(2-18)

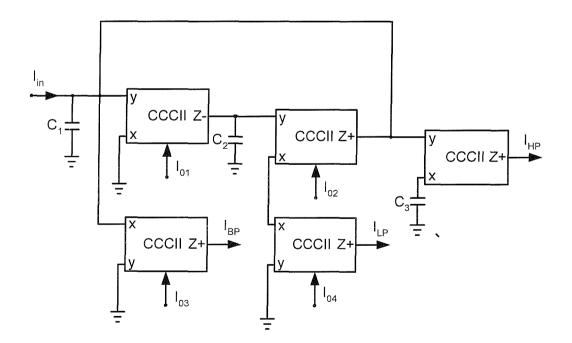

Fig. 2-8 Current-mode CCII-based universal biquad [31]

### 2.4 Biquad Classification

There are five generic, normalized, biquadratic filtering transfer functions which are:

$$\frac{a_{0}}{a_{2}s^{2} + a_{1}s + a_{0}}, (low - pass)$$

$$\frac{a_{1}s}{a_{2}s^{2} + a_{1}s + a_{0}}, (band - pass)$$

$$\frac{a_{2}s^{2}}{a_{2}s^{2} + a_{1}s + a_{0}}, (high - pass)$$

$$\frac{a_{2}s^{2} + a_{0}}{a_{2}s^{2} + a_{1}s + a_{0}}, (band - reject)$$

$$\frac{a_{2}s^{2} - a_{1}s + a_{0}}{a_{2}s^{2} + a_{1}s + a_{0}}, (all - pass)$$

(2-19)

Summing a low-pass output signal, and a high-pass output signal, a band-reject output signal can be obtained:

$$\frac{a_2s^2}{a_2s^2 + a_1s + a_0} + \frac{a_0}{a_2s^2 + a_1s + a_0} = \frac{a_2s^2 + a_0}{a_2s^2 + a_1s + a_0}$$

(2-20)

An all-pass output signal can be obtained by summing a high-pass output, an inverting-type band-pass output, and a low-pass output signals.

$$\frac{a_2s^2}{a_2s^2 + a_1s + a_0} + \frac{-a_1s}{a_2s^2 + a_1s + a_0} + \frac{a_0}{a_2s^2 + a_1s + a_0} = \frac{a_2s^2 - a_1s + a_0}{a_2s^2 + a_1s + a_0}$$

(2-21)

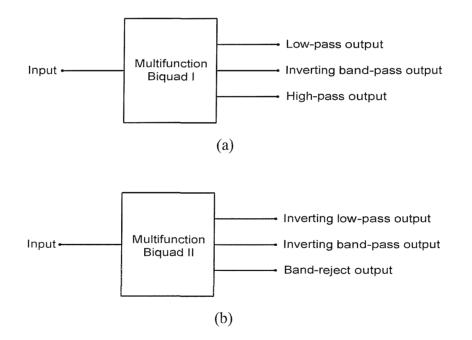

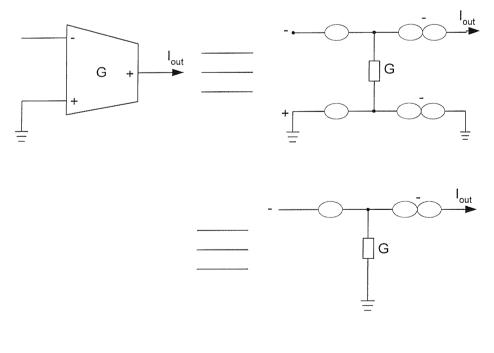

Therefore, a low-pass output signal, an inverting-type band-pass output signal, and a high-pass output signal are a set of fundamental generic filtering signals to construct all of the five generic filtering signals, i.e., low-pass, band-pass, high-pass, band-reject, and all-pass. The block diagram of multifunction biquad I is shown in Fig. 2-9 (a).

Fig. 2-9 (a) and (b) Block diagrams of single-input, three-output multifunction biquads I and II

The other set of fundamental generic filtering signals to construct all of the five generic filtering signals are an inverting-type low-pass output signal, an inverting-type band-pass output signal, and a band-reject output signal. A high-pass signal can be obtained by summing a band-reject and an inverting-type low-pass output signals, namely:

$$\frac{a_2s^2 + a_0}{a_2s^2 + a_1s + a_0} + \frac{-a_0}{a_2s^2 + a_1s + a_0} = \frac{a_2s^2}{a_2s^2 + a_1s + a_0}$$

(2-22)

An all-pass signal can be obtained by summing a band-reject and an inverting-type band-pass output signals, namely,

$$\frac{a_2s^2 + a_0}{a_2s^2 + a_1s + a_0} + \frac{-a_1s}{a_2s^2 + a_1s + a_0} = \frac{a_2s^2 - a_1s + a_0}{a_2s^2 + a_1s + a_0}$$

(2-23)

The block diagram of multifunction biquad II is shown in Fig. 2-9 (b).

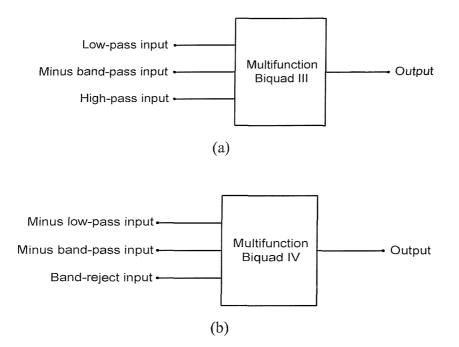

Fig. 2-10 (a) and (b) Block diagrams of three-input, single-output multifunction biquads III and IV

It is also possible to obtain multifunction biquads using three inputs and single output. The block diagrams of multifunction biquads III and IV are shown in Figs. 2-10 (a) and (b). Note that the "low-pass input" presented in Fig. 2-10 (a) means "the input leading to a low-pass output", the "minus band-pass input" presented in Figs. 2-10 (a) and (b) means "the input leading to an inverting-type band-pass output", and so on.

The classification is used to simplify the review of the recently reported various biquads in the next section.

#### 2.5 Literature Review

In Sections 2.5.1 and 2.5.2, the detailed literature reviews will be focused on OTAand CCII-based biquad filters and high-order filters, respectively. The literature review will lead to the research direction of this thesis presented in the next section.

#### 2.5.1 Review of OTA- and CCII-Based Biquads

To simplify the review, OTA-based biquads are separated from CCII-based biquads.

#### **OTA-Based Biquads**

To simplify the review, the biquad has been divided into two parts, current mode and voltage mode as shown in Fig. 2-6.

#### **Current-Mode OTA-Based biquads**

A second-order current-mode filter using four OTAs and two grounded capacitors was presented in 1996 [22]. It can realize low-pass, band-pass, high-pass, and band-reject filtering functions but without all-pass filtering function unless component matching conditions is used. Also, independent control of  $\omega_o$  and  $\omega_o/Q$  cannot be achieved. In the same year, although a variety of current-mode continuous-time integrator loop filter architectures incorporating OTA and grounded capacitors were generated [23], the best one in [23] retains the same advantages and disadvantages as that in [22]. Employing one fewer OTA, i.e., only three OTAs, but one floating capacitor in addition to one grounded capacitor to construct a current-mode biquad was proposed [24]. The current-mode filter in [24] needs one component matching condition to realize five generic biquadratic functions and cannot provide independent control of  $\omega_o$  and  $\omega_o/Q$ . The current-mode biquad proposed in [24] was improved by the circuit [25], which employed two grounded capacitors instead of one floating and one grounded capacitors. All the biquads proposed in [25] don't require any component matching conditions. However, they cannot enjoy the independent control of  $\omega_o$  and  $\omega_o/Q$ . In 2000, Chang and Pai [26] proposed employing only two OTAs and two grounded capacitors, the minimum active and passive components, to realize a current-mode universal biquad which can simultaneously realize low-pass, band-pass, high-pass, band-reject, and all-pass filtering functions without the need of any critical constraints. However, it still suffers from the disadvantage: no independent control of  $\omega_o$  and  $\omega_o/Q$ .

#### Voltage-Mode OTA-Based biquads

In 1998, a voltage-mode OTA-C biquad using three OTAs, one floating and one grounded capacitors was proposed [24]. The voltage-mode biquad needs component matching conditions to realize low-pass and all-pass filtering functions and does not provide the independent control of  $\omega_o$  and  $\omega_o/Q$ . The voltage-mode biquad proposed in [24] was improved by three further circuits in [25]. The first two biquads employed two grounded capacitors instead of one floating and one grounded capacitors, and the third biquad employed only two instead of three OTAs. Moreover, all the biquads in [25] don't require any component matching conditions. However, they cannot enjoy the independent control of  $\omega_o$  and  $\omega_o/Q$ . In 2002, a voltage-mode universal biquadratic filter with one input and five outputs was proposed [27]. However, it uses five OTAs to realize such a multifunction biquad filter.

#### **CCII-Based Biquads**

To simplify the review, the biquad has been divided into two parts, current mode and voltage mode as shown in Fig. 2-6, and classified as multifunction biquads I, II, III, and IV as outlined in Section 2.4.

#### Current-Mode Multifunction Biquad I/II:

In 1992, Senani [46] proposed a universal current-mode biquad which employs seven current conveyors in addition to two grounded capacitors and three grounded resistors.

This biquad suffers from the following two disadvantages: requirement of one matching condition to realize an all-pass signal, and no orthogonal control of  $\omega_o$  and Q. The universal filter was improved by Chang [47] in 1993. It does not need any component matching conditions and enjoys the orthogonal control of  $\omega_o$  and Q. The component count of the universal filter in [47] was reduced in [48] to five current conveyors, two grounded capacitors, and three resistors. Moreover, the proposed universal filter [48] enjoys no component matching and the independent control of  $\omega_{a}$ and O. In 1995, Soliman presented a current-mode universal filter using four CCIIs, three grounded capacitors, and three grounded resistors with independent control of  $\omega_{o}$  and Q but poor performance at high frequency [49]. Abuelma'atti and Khan [50] replaced one CCII with one operational transconductance amplifier (OTA) from Soliman's biquad to design a low component current-mode universal filter. The universal biquad was further improved by Chang and Tu using four dual-output CCIIs, two grounded capacitors, and two grounded resistors to realize five generic biquad functions from the same structure [51]. In 1997, Özoğuz and Acar used four CCIIs, two floating capacitors, and two floating resistors to realize a universal currentmode biquad [52]. In 1998, a high output impedance current-mode multifunction filter employing three CCIIs, one grounded capacitor, one floating capacitor, two grounded resistors, and one floating resistor was proposed by Özoğuz et al. [53]. The use of a floating capacitor and a floating resistor makes the circuit unsuitable for integrated circuit implementation. Moreover, it cannot enjoy low active sensitivities as high quality factor is necessary. Wang and Lee presented a versatile multi-input-multioutput biquad structure [54], which can realize either a three-input single-output or a single-input three-output universal biquad by using three current conveyors. The proposed construction has many advantageous features but still has the two disadvantages: no independent control of  $\omega_o$  and  $\omega_o/Q$  and the limitation for high frequency operation. In 2000, Toker and Özoğuz proposed an insensitive currentmode universal filter using three dual output current conveyors, two grounded capacitors, and three grounded resistors which, again, suffered from the limitation for high frequency operation [31]. In 2002, the three-current-output universal biquad filter without the advantage: independent control of  $\omega_o$  and  $\omega_o/Q$  was realized by using only two plus-type CCIIs, two capacitors, and two resistors [58]. Recently, a single-CCIIbased universal biquad filter with three inputs and three outputs was proposed using

one active element, two grounded capacitors and two grounded resistors which cannot enjoy the independent control of  $\omega_o$  and  $\omega_o/Q$  [59].

In summary, the current-mode CCII-based universal biquads started with seven active elements and two capacitors [46-47], reduced to five active elements and two capacitors [48], four active elements and three capacitors [49-50], four active elements and two capacitors [51-52], then three active elements and two capacitors [53-54, 31], and then two active elements and two capacitors [58], and finally one active element and two capacitors [59].

#### Voltage-Mode Multifunction Biquad I/II:

In 1991, a current-feedback amplifier (CFA), which is equivalent to a plus-type second-generation current conveyor (CCII) with a voltage follower [32], was proposed. In 1994, Chang et al. [33] presented a voltage-mode notch, low-pass, and band-pass filter using three CFAs, which are equivalent to three plus-type secondgeneration current conveyors and three voltage followers, six active elements in total. In 1994 and 1995, Soliman [34] and Senani et al. [35] proposed two different types of Kerwin-Huelsman-Newcomb-equivalent biquads. Each realizes low-pass, band-pass, and high-pass filter transfer functions, using five plus-/minus-type second-generation current conveyors (CCII±), two capacitors and six or seven resistors, respectively. In 1995, Celma et al. presented a voltage-mode universal biquad using three CCIIs, and three voltage followers [36], still six active elements in total. Therefore, before 1996, voltage-mode CCII-based biquads were realized by employing five to six active elements. In 1997, Horng et al. [37] proposed a voltage-mode multifunction filter, using four CCII+, but three capacitors, and five resistors. In the same year, Chang [38] presented five voltage-mode multifunction biquadratic filters, each of which employs four CCII±, two grounded capacitors, and three-five resistors. In 1999, Chang and Lee [39] proposed a simpler voltage-mode low-pass, band-pass, and high-pass filter. This employed only two current conveyors, two grounded capacitors, and three grounded/floating resistors. Recently, a single-CCII-based low-pass, band-pass, highpass, and band-reject biquad filter was presented using one CCII, two grounded capacitors and two grounded resistors [59]. Both the multifunction biquads [39, 59] suffer from no independent control of  $\omega_o$  and  $\omega_o/Q$ .

In summary, the voltage-mode CCII-based biquads started by employing six active elements and two capacitors [33, 36], were reduced to five active elements and two capacitors [34-35], four active elements and three capacitors [37], four active elements and two capacitors [38], then two active elements and two capacitors [39], and finally one active element and two capacitors [59].

#### Current-Mode Multifunction Biquad III/IV:

In 1991, Chang and Chen [54] published a universal active current biquad with independent control of  $\omega_{\rho}$  and Q using five CCIIs, two grounded capacitors, and five grounded resistors. Chang et al. improved their previous universal current-mode biquad by using one fewer CCII [55]. In 1999, a universal current-mode active filter was presented by Günes et al., which contains three dual-output current conveyors, two grounded capacitors and two grounded resistors [56]. Recently, Wang and Lee [57] presented a versatile multi-input-multi-output biquad structure, which can realize either a three-input single-output or a single-input three-output universal biquad by using three current conveyors. The proposed circuit has a number of advantageous features but still has the two disadvantages: no independent  $\omega_o$  and Q control and the limitation for high frequency operation. In 2002, the three-current-input universal biquad filter was realized by using only two plus-type CCIIs, two capacitors, and two resistors [58] (which is a three-input and three-output universal biquad filter). Recently, a single-CCII-based universal biquad filter with three inputs and three outputs was proposed using one active element, two grounded capacitors and two grounded resistors [59]. The latest two universal biquads [58, 59] suffer from no independent control of  $\omega_o$  and  $\omega_o/Q$ .

In summary, the current-mode CCII-based universal biquads started with five active elements [54], were reduced to four active elements [55], then three active elements [56-57], and then two active elements and two capacitors [58], and finally one active element and two capacitors [59].

#### Voltage-Mode Multifunction Biquad III/IV:

The earlier work [40-44] cannot be realized by using only grounded passive elements, namely, capacitors and resistors. Also, they cannot enjoy the independent control of  $\omega_o$  and  $\omega_o/Q$  and the high-input impedance at their three input terminals

simultaneously. Furthermore, they suffer from either inverting type input signals or component choice conditions. Although a high-input impedance universal biquad was proposed [45], the biquad suffers from all of the earlier existing disadvantages. In 2003, the author presented a biquad filter [60] with the addition of advantages such as employment of only grounded capacitors, no need of inverting type input signals, and no need of component matching condition. However, the biquad filter still suffers from (i) employment of one floating resistor, (ii) one input terminal without highinput impedance, and (iii) no independent control of  $\omega_{\rho}$  and  $\omega_{\rho}/Q$ .

#### 2.5.2 Review of OTA- and CCH-Based High-Order Filters

Section 2.5.1 has provided literature review of biquad filters capable of generating second-order filtering functions. In this section, to simplify the review, OTA-based high-order filters are separate from CCII-based high-order filters.

#### **OTA-Based High-Order Filters**