UNIVERSITY OF SOUTHAMPTON

Advanced Characterisation

and Modelling of SiGe HBT's

Yue Teng, Tang

A thesis submitted for the degree of

Doctor of Philosophy

Department of Electronics and Computer Science

Faculty of Engineering and Applied Science

May 2000

UNIVERSITY OF SOUTHAMPTON

**ABSTRACT**

FACULTY OF ENGINEERING AND APPLIED SCIENCE

DEPARTMENT OF ELECTRONICS AND COMPUTER SCIENCE

Doctor of Philosophy

ADVANCED CHARACTERISATION AND MODELLING OF SiGe HBT's

by Yue Teng, Tang

This thesis investigates advanced characterisation and modelling techniques for silicon-germanium heterojunction bipolar transistor (SiGe HBT's). Two characterisation techniques are proposed and evaluated to enable, as much as is possible, direct electrical extraction of physical device characteristics which are unique to SiGe HBT's, as opposed to standard silicon-only bipolar transistors. Principal objectives motivating the new characterisation techniques are the elimination of silicon control devices and the use of widely available measurement apparatus.

A new electrical method for extracting the bandgap difference across the neutral base of a SiGe HBT is proposed. The method is able to extract the bandgap difference across the neutral base without the need of time consuming and expensive characterisation tools such as SIMS. Also, it does not require detailed modelling of the SiGe HBT, such as bandgap narrowing effect. The accuracy of the method is assessed. Numerical simulations and measurement results proved that the proposed method could achieve its predicted function.

The bandgap difference across the neutral base extraction method is further developed for extracting the parasitic potential barrier height in a SiGe HBT. The proposed method is shown to be able to extract the parasitic potential barrier heights at the emitter-base and collector-base junctions of SiGe HBT's simultaneously in conjunction with numerical space-charge layer modelling using doping secondary-ion-mass spectroscopy (SIMS) profile data. It provides a more direct measure of parasitic barrier-related quantities and does not depend upon a detailed knowledge of the temperature dependence of SiGe density of states functions, carrier mobility, etc.. Numerical simulations and measurement results show that the method gives useful and representative values regarding the parasitic potential barrier height.

Finally, the potential of a proposed novel lateral SiGe HBT structure for high performance rf/microwave applications is assessed. Various issues regarding the lateral structure, including base definition and base contact, are discussed. Compared to a state-of-the art vertical SiGe HBT structure, the lateral structure is found to have many advantages for low power rf/microwave applications. A realistic comparison is carried out by means of full 2-D numerical simulation. Numerical simulation results indicate that a lateral SiGe HBT structure can potentially out-perform a vertical structure in term of low power and high frequency performance.

# Contents

|                                                                                                     |              |

|-----------------------------------------------------------------------------------------------------|--------------|

| <b>Abstract</b>                                                                                     | <b>iii</b>   |

| <b>List of Figures</b>                                                                              | <b>vii</b>   |

| <b>Acknowledgement</b>                                                                              | <b>xvii</b>  |

| <b>List of Symbols</b>                                                                              | <b>xviii</b> |

| <b>1 Introduction</b>                                                                               | <b>1</b>     |

| <b>2 Theory of Heterojunction Bipolar Transistors</b>                                               | <b>7</b>     |

| 2.1 Material Properties of Strained $Si_{1-x}Ge_x$ . . . . .                                        | 7            |

| 2.1.1 Bandgap Narrowing Due to Heavy Doping Effects . . . . .                                       | 10           |

| 2.1.2 SiGe Growth using UHV/CVD . . . . .                                                           | 12           |

| 2.2 Electrical Properties of $Si/Si_{1-x}Ge_x/Si$ HBT's . . . . .                                   | 13           |

| 2.2.1 Collector Current and Current Gain . . . . .                                                  | 14           |

| 2.2.2 Base Transit Time . . . . .                                                                   | 17           |

| 2.2.3 Output Conductance . . . . .                                                                  | 18           |

| 2.3 Numerical Device Modelling in Medici and Atlas . . . . .                                        | 19           |

| 2.4 Boron Out-diffusion and Parasitic Barrier Formation . . . . .                                   | 22           |

| 2.5 Theory of Previous SiGe HBT Characterisation Technique of Parasitic Potential Barrier . . . . . | 25           |

| 2.5.1 Slotboom Method . . . . .                                                                     | 25           |

| 2.5.2 Le Tron <i>et al.</i> Method . . . . .                                                        | 27           |

| 2.6 Figure of Merits for High Frequency Bipolar Transistor Performance .                            | 28           |

|          |                                                                                                                                                             |           |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 2.6.1    | Figure of merit $f_T$                                                                                                                                       | 28        |

| 2.6.2    | Figure of merit $f_{max}$                                                                                                                                   | 30        |

| <b>3</b> | <b>Lateral Bipolar Transistor</b>                                                                                                                           | <b>32</b> |

| 3.1      | Issues Facing High Frequency RF/Microwave Lateral Bipolar Transistor Technology                                                                             | 33        |

| 3.2      | Advantages of the Lateral Bipolar Transistor                                                                                                                | 37        |

| 3.3      | The Hybrid Mode Lateral Bipolar Transistor                                                                                                                  | 39        |

| 3.4      | Conclusion                                                                                                                                                  | 44        |

| <b>4</b> | <b>An Electrical Method for Measuring The Difference in Bandgap across the Neutral Base in SiGe HBT's</b>                                                   | <b>45</b> |

| 4.1      | Introduction                                                                                                                                                | 45        |

| 4.2      | Theory                                                                                                                                                      | 48        |

| 4.3      | Experimental Procedure                                                                                                                                      | 55        |

| 4.4      | Experimental Results                                                                                                                                        | 59        |

| 4.5      | Numerical Results                                                                                                                                           | 64        |

| 4.6      | Conclusion                                                                                                                                                  | 73        |

| <b>5</b> | <b>An Experimental Method for Simultaneous Extraction of Parasitic Potential Barrier Heights at Emitter-Base and Collector-Base Junctions of SiGe HBT's</b> | <b>74</b> |

| 5.1      | Introduction                                                                                                                                                | 74        |

| 5.2      | Theory                                                                                                                                                      | 77        |

| 5.3      | Numerical Simulation Results                                                                                                                                | 82        |

| 5.4      | Experimental Measurement Results                                                                                                                            | 85        |

| 5.5      | Conclusions                                                                                                                                                 | 92        |

| <b>6</b> | <b>Theoretical Comparison of a Proposed Novel SiGe HBT with Existing Advanced Vertical SiGe HBT Technology</b>                                              | <b>94</b> |

| 6.1      | Proposed Lateral SiGe HBT                                                                                                                                   | 96        |

| 6.2      | Vertical SiGe HBT used for Comparison to the Proposed Lateral SiGe HBT Structure                                                                            | 102       |

|                                                                                                                          |            |

|--------------------------------------------------------------------------------------------------------------------------|------------|

| 6.3 Comparison between the Proposed Lateral SiGe HBT and the Vertical<br>SiGe HBT of Kondo <i>et. al.</i> [10] . . . . . | 110        |

| 6.4 Conclusion . . . . .                                                                                                 | 115        |

| <b>7 Conclusions and Further Work</b>                                                                                    | <b>116</b> |

| <b>A Philips Unified Mobility model</b>                                                                                  | <b>120</b> |

| <b>B Derivation of the Electrical Bandgap Grading Extraction Technique</b>                                               | <b>122</b> |

| <b>C Error analysis of the bandgap difference across neutral base extrac-<br/>tion method</b>                            | <b>126</b> |

| C.1 Error Analysis for High Emitter Doping . . . . .                                                                     | 126        |

| C.2 General Error Analysis . . . . .                                                                                     | 128        |

| <b>D Kondo device and proposed lateral device input files and 2-D cross<br/>sectional diagrams</b>                       | <b>129</b> |

| <b>E Base resistance and Collector/Base depletion capacitance extraction<br/>using Z parameters.</b>                     | <b>147</b> |

| <b>F List of publications</b>                                                                                            | <b>152</b> |

| <b>Bibliography</b>                                                                                                      | <b>153</b> |

# List of Figures

|     |                                                                                                                                                                                                                                                                                                          |    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

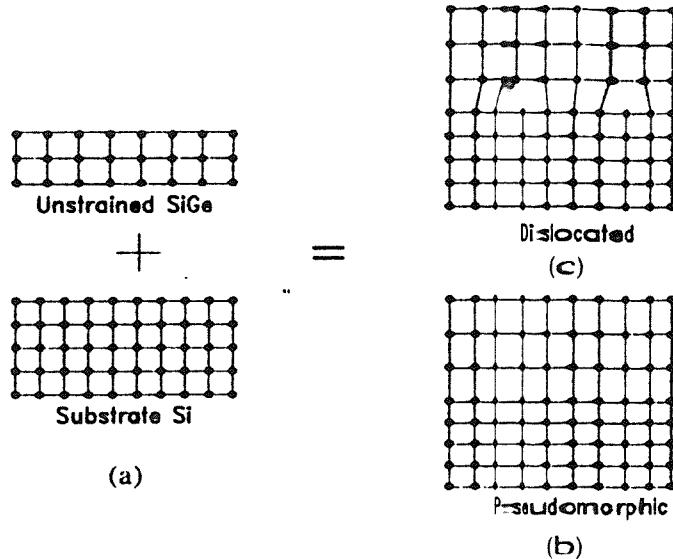

| 2.1 | 2-Dimensional crystal structure representations [38] of (a) growing SiGe alloy on silicon substrate forming (b) pseudomorphic growth with the lattice constant difference accommodated by tetragonal strain or (c) structural dislocations or defects. . . . .                                           | 8  |

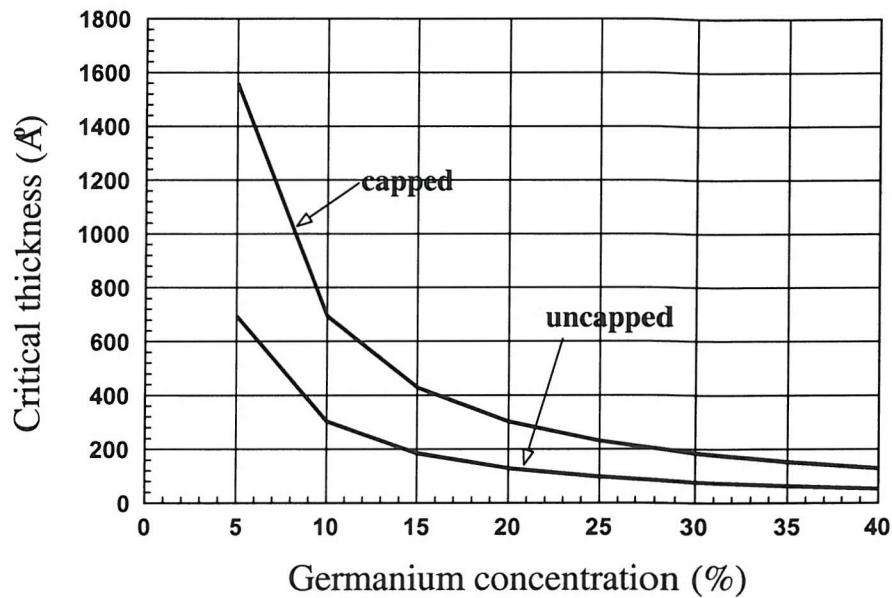

| 2.2 | Plot showing the critical thickness versus germanium concentration of a strained SiGe layer with and without silicon capping [41, 40]. . . . .                                                                                                                                                           | 9  |

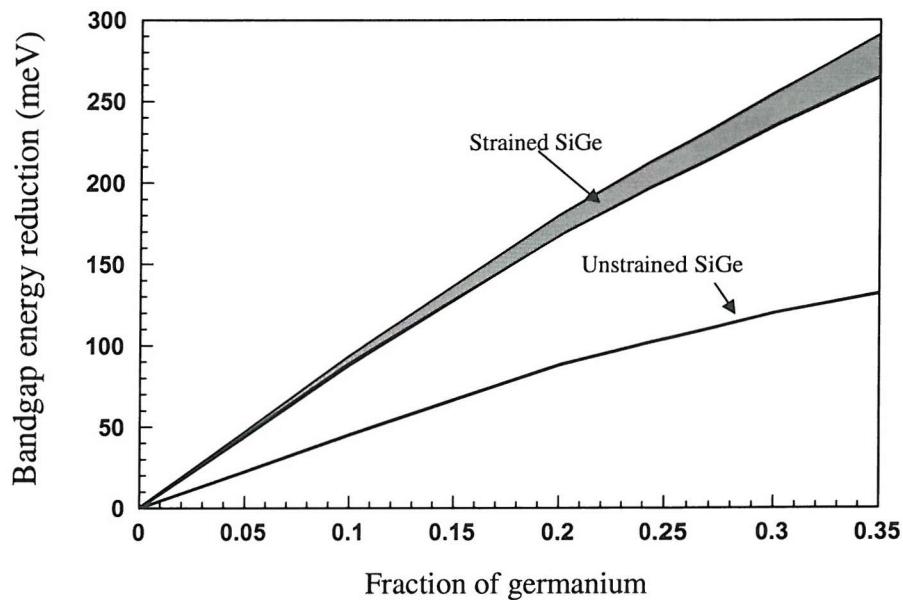

| 2.3 | Plot of bandgap reduction due to germanium for strained SiGe layer (after [42]) and unstrained SiGe layer (after [43]) at temperature 90K. . . . .                                                                                                                                                       | 9  |

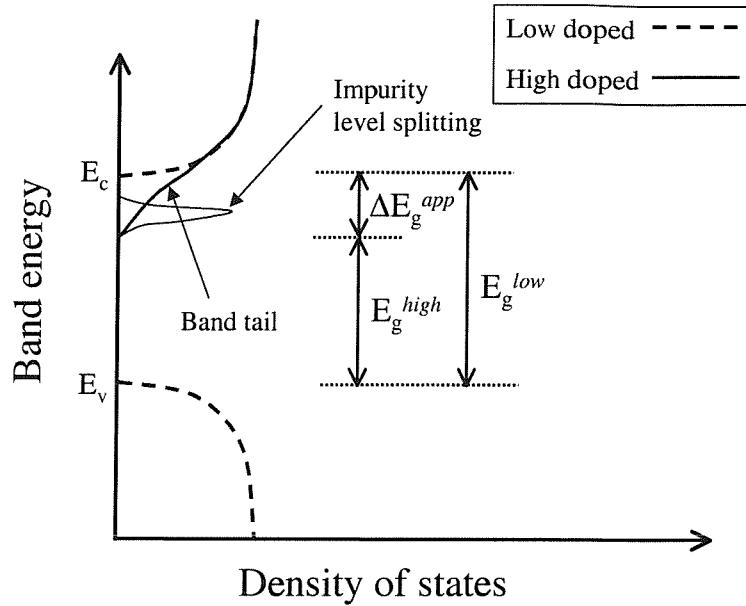

| 2.4 | Figure illustrating the heavy doping effect on the bandgap of n-type silicon [46]. $E_g^{high}$ is the resultant bandgap due to heavy doping effect and $E_g^{low}$ is the bandgap without heavy doping effect. $\Delta E_g^{app}$ is the apparent bandgap narrowing due to heavy doping effect. . . . . | 11 |

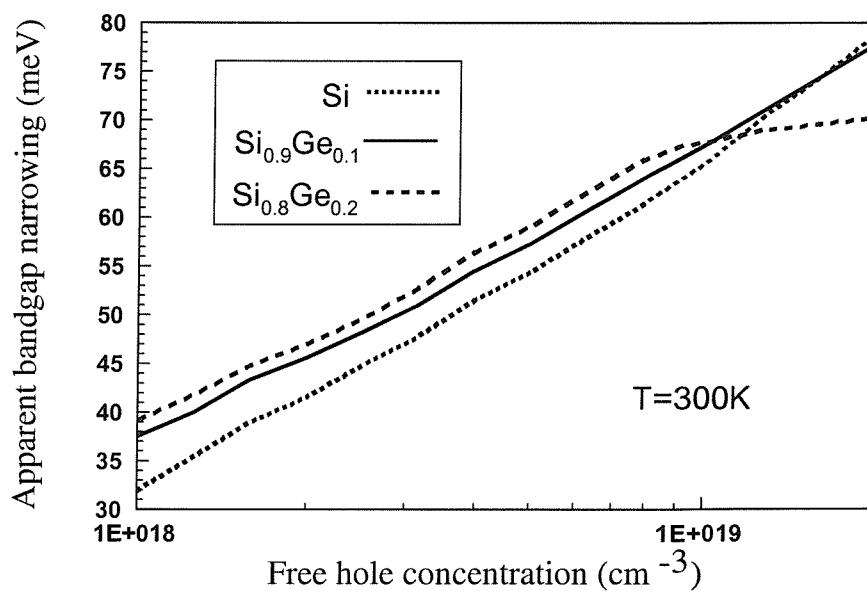

| 2.5 | Apparent bandgap narrowing due to heavy doping effects for three different germanium concentrations (0%, 10%, 20%) at a temperature of 300K [45]. . . . .                                                                                                                                                | 11 |

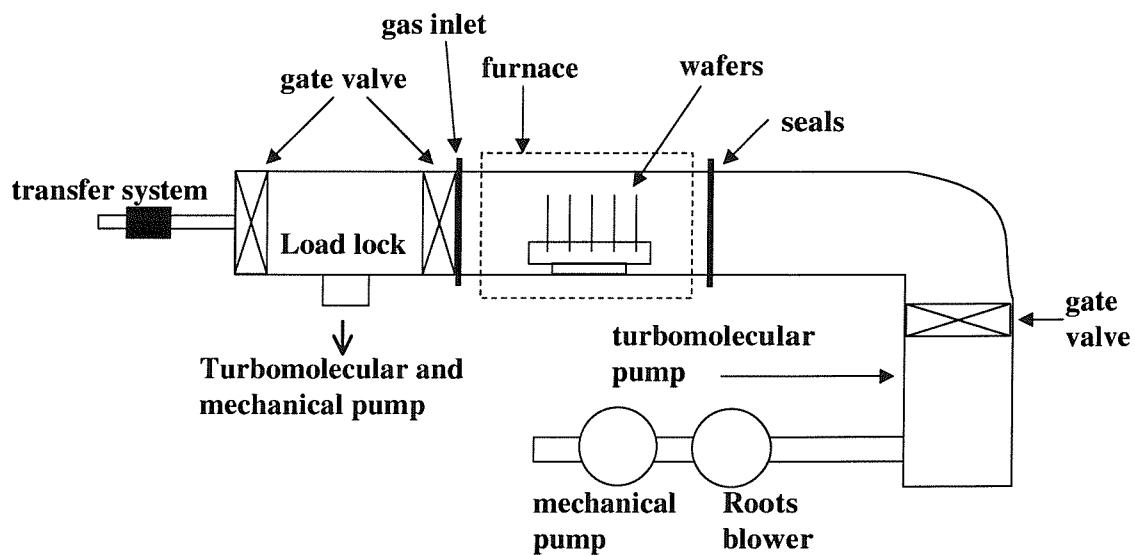

| 2.6 | Schematic diagram of a UHV/CVD reactor (after Meyerson [8, 50]). . .                                                                                                                                                                                                                                     | 12 |

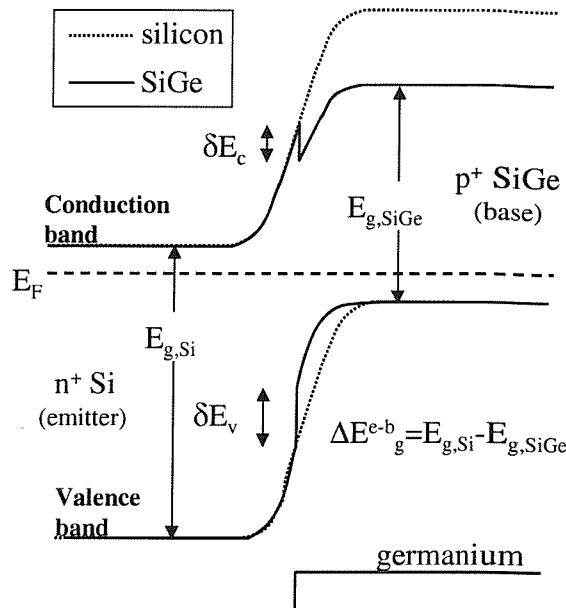

| 2.7 | Figure illustrating the effect of SiGe strained layer on the bandgap of emitter-base junction for an abrupt Si/SiGe interface. . . . .                                                                                                                                                                   | 14 |

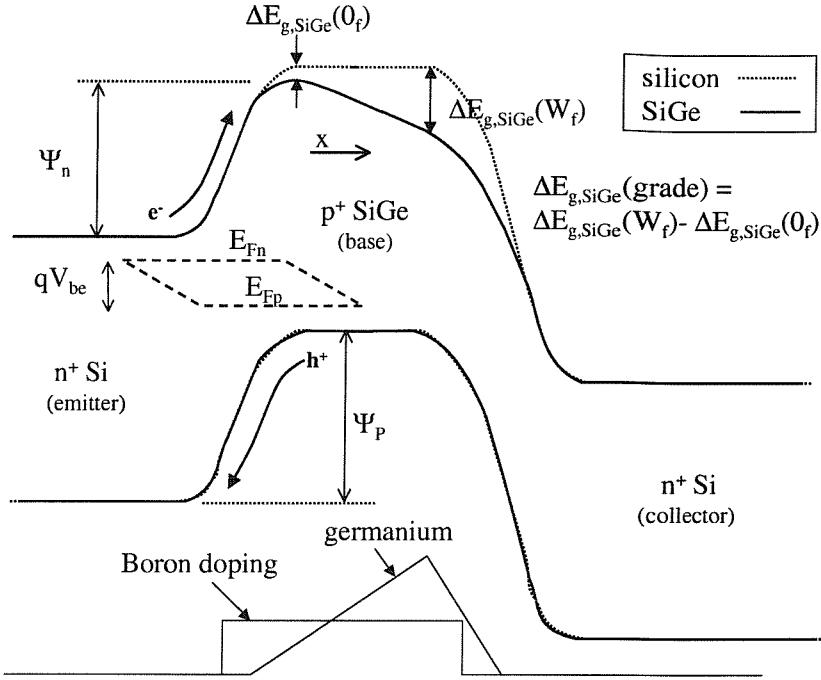

| 2.8 | Bandgap energy diagram across a graded SiGe HBT in forward active mode of operation. $0_f$ and $W_f$ are the electrical boundaries of the neutral base region on the emitter and collector sides of the base, respectively. . . . .                                                                      | 15 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

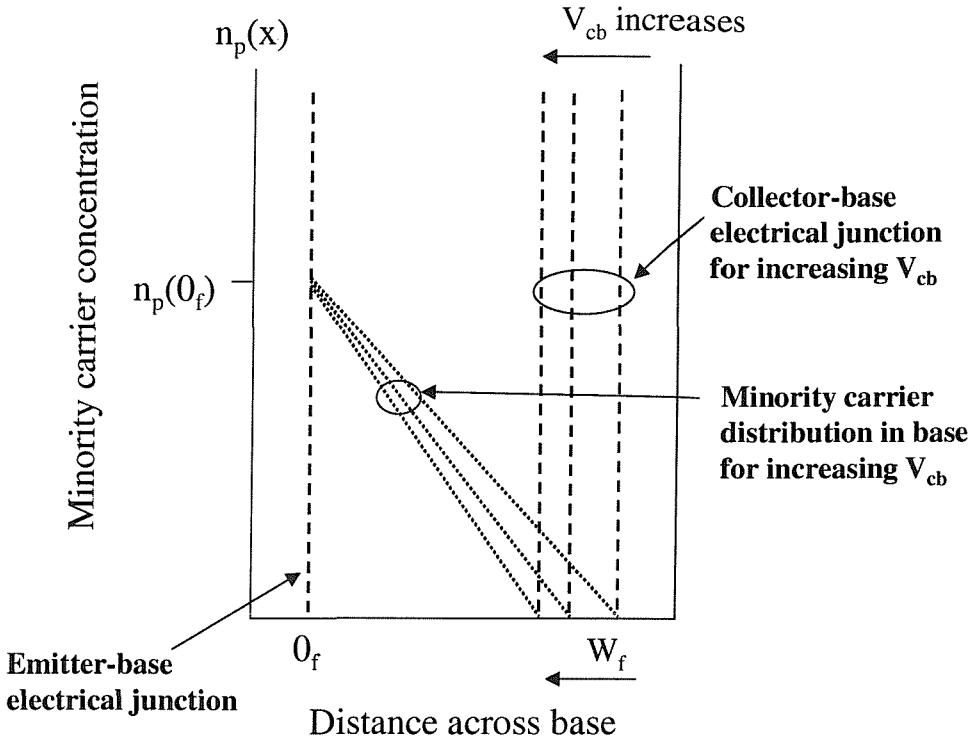

| 2.9  | Minority carrier distribution in an n-p-n transistor for increasing collector-base reverse bias voltage in forward active mode. $n_p$ is the electron concentration in a p-type. . . . .                                                                                                                                                                                                                                                                                                    | 19 |

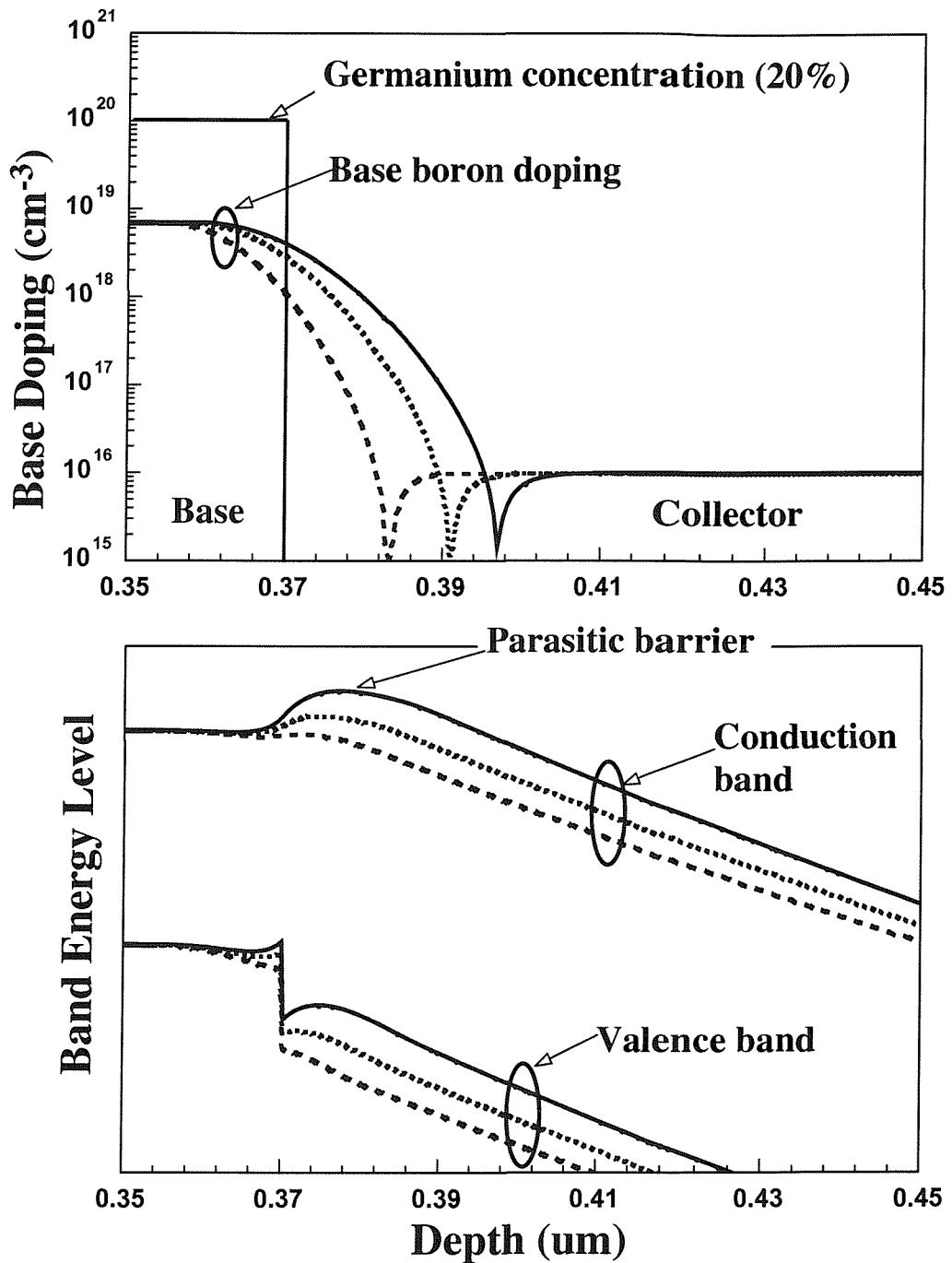

| 2.10 | Figure showing the effect of boron out-diffusion on the device energy band at the collector-base junction based on results of numerical simulation using Medici. Three types of base boron doping distributions, with different base widths, are shown together with their corresponding band energy diagrams. The size and height of the parasitic potential barriers are dependent on the amount of out-diffusion and can exist at both emitter-base and collector base junction. . . . . | 24 |

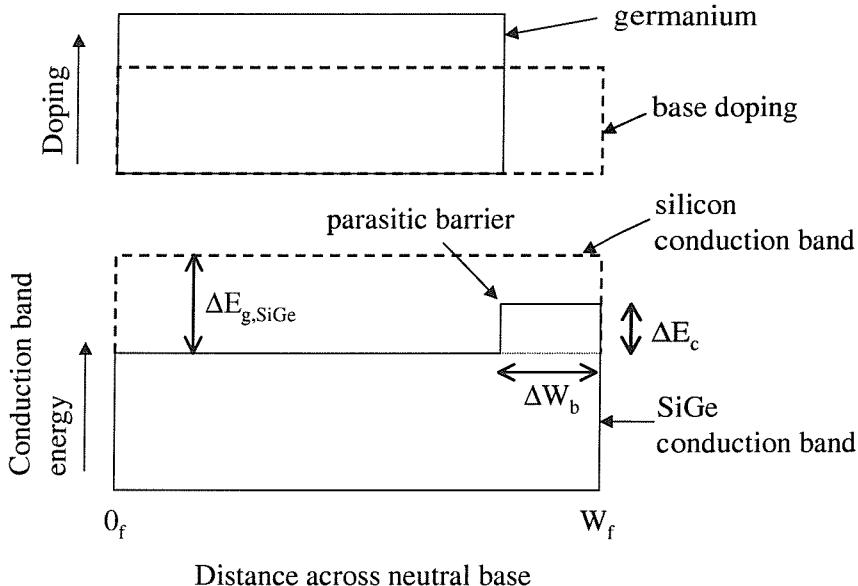

| 2.11 | The effect of boron out-diffusion on the conduction band for uniform box-like boron and germanium doping (after [20]). . . . .                                                                                                                                                                                                                                                                                                                                                              | 25 |

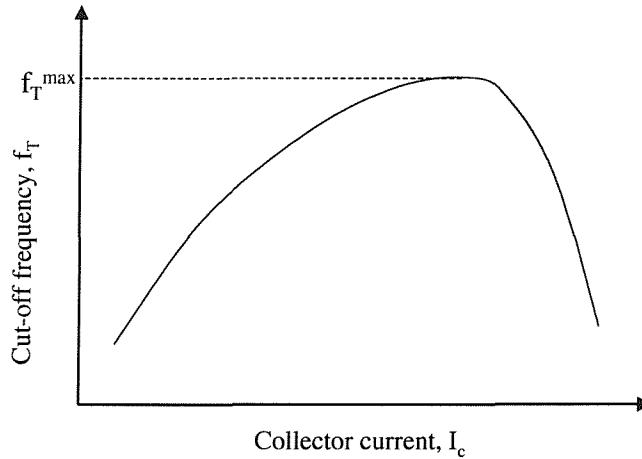

| 2.12 | Behaviour of cut-off frequency, $f_T$ , for increasing collector current, $I_c$ . . . . .                                                                                                                                                                                                                                                                                                                                                                                                   | 30 |

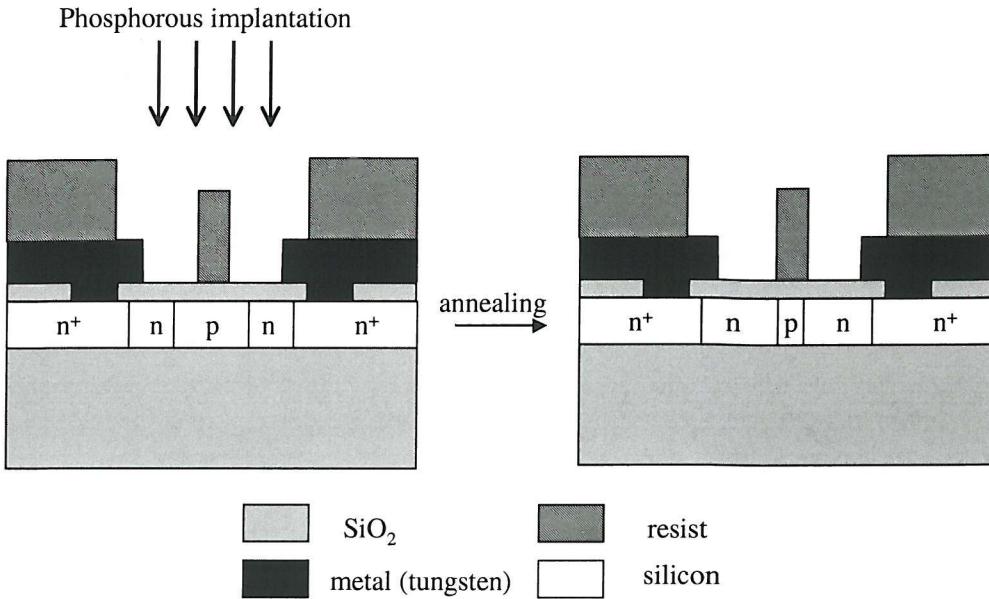

| 3.1  | Resist is used to pattern the base region and it acts as an implantation mask. Due to high-temperature stability of tungsten, an annealing step could be performed to drive the phosphorous dopant further into the base region to reduce the base width [29]. . . . .                                                                                                                                                                                                                      | 34 |

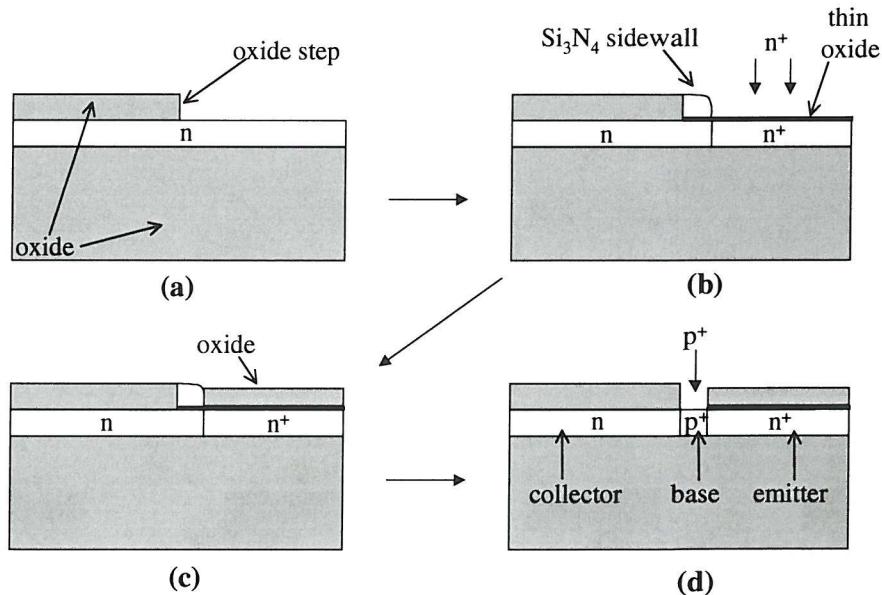

| 3.2  | The sidewall technique used by Sugii <i>et al.</i> [75] to make an 80nm wide base. (a) Oxide step formation, (b) the formation of $Si_3N_4$ sidewall and emitter implantation, (c) emitter oxide growth, (d) $Si_3N_4$ and thin oxide strip followed by base implantation. . . . .                                                                                                                                                                                                          | 34 |

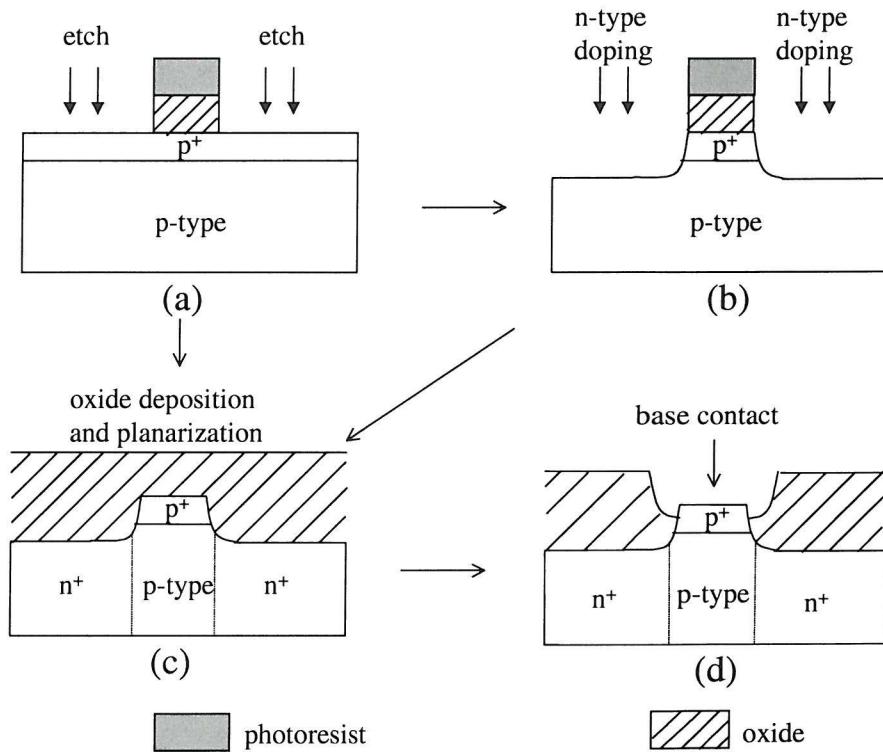

| 3.3  | Figure illustrating the lateral bipolar transistor process flow used by Sturm <i>et al.</i> [31] which enables metal contact on top of the entire base. This method can be use in conjunction with a lithographically defined base. . . . .                                                                                                                                                                                                                                                 | 35 |

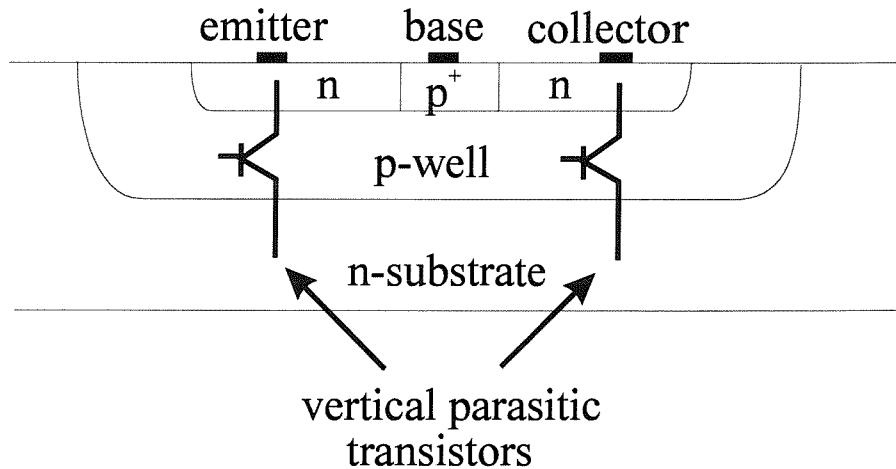

| 3.4  | Figure illustrating the common isolation problem associated with lateral bipolar transistor caused by two parasitic vertical bipolar transistor that are inherently present in the structure. . . . .                                                                                                                                                                                                                                                                                       | 36 |

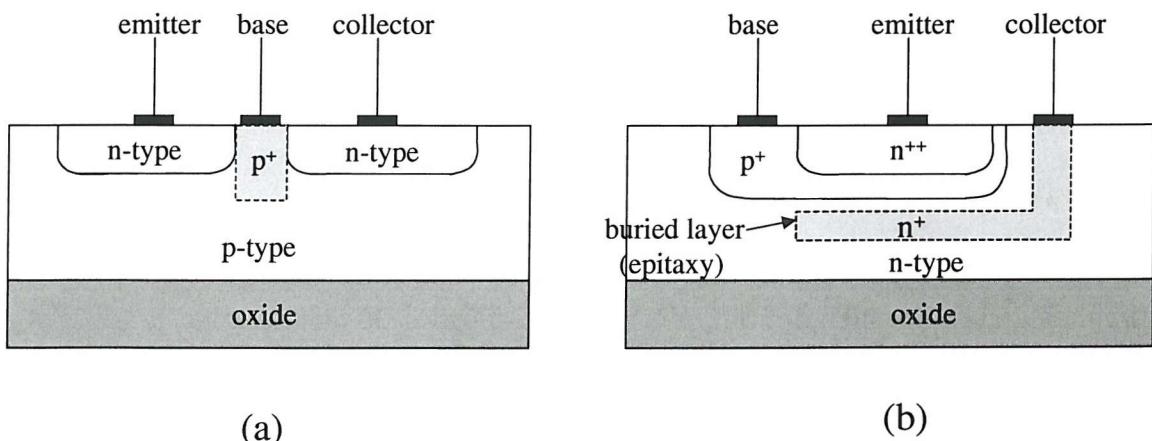

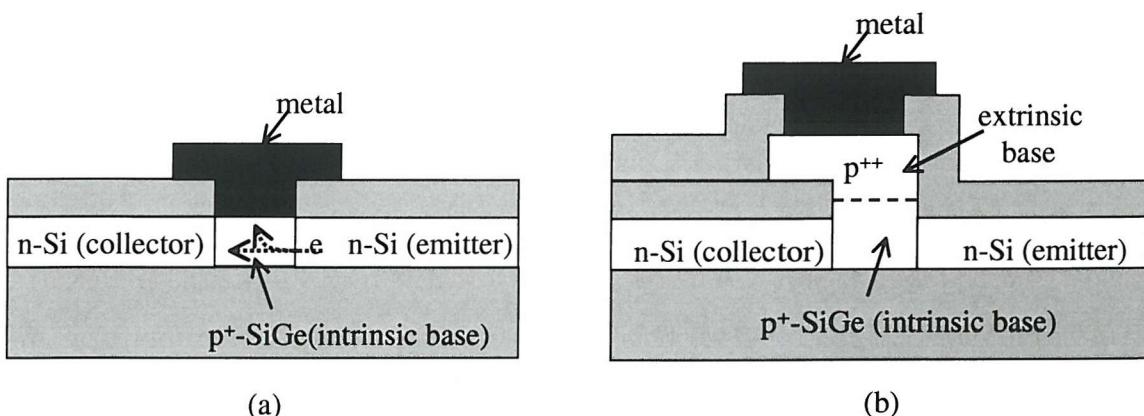

| 3.5  | The basic structures of (a) Lateral Bipolar Transistor and (b) Vertical Bipolar Transistor. . . . .                                                                                                                                                                                                                                                                                                                                                                                         | 37 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

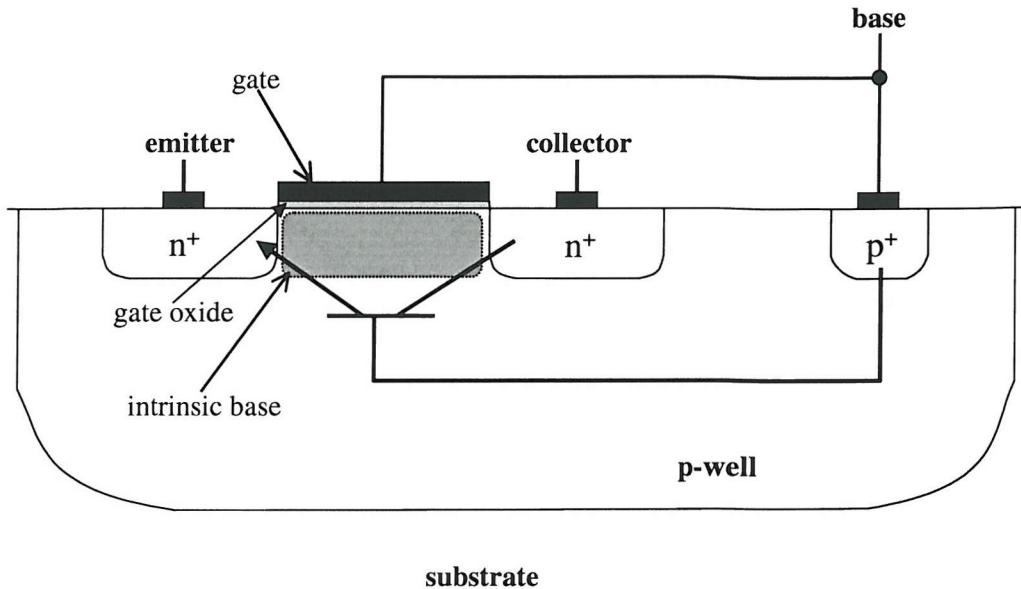

| 3.6 | Lateral bipolar transistor operating in hybrid mode where the base and gate are connected together. The intrinsic base region, where the depletion region that results in pseudo-heterojunction effect in the lateral bipolar transistor base is also shown in the figure. . . . .                                                                                                                                                                                                                                         | 40 |

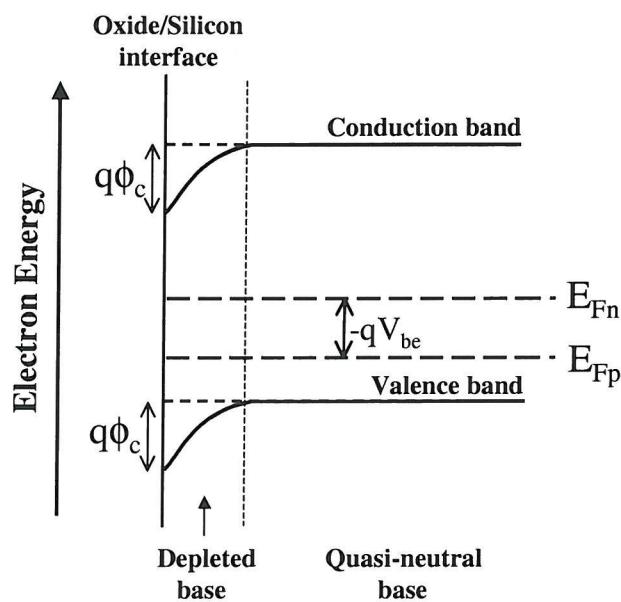

| 3.7 | Energy band diagram for conventional lateral BJT (solid lines) and the hybrid mode lateral BJT (broken lines), across the emitter-intrinsic base junction in the direction parallel and close to the oxide-silicon interface. . . . .                                                                                                                                                                                                                                                                                      | 41 |

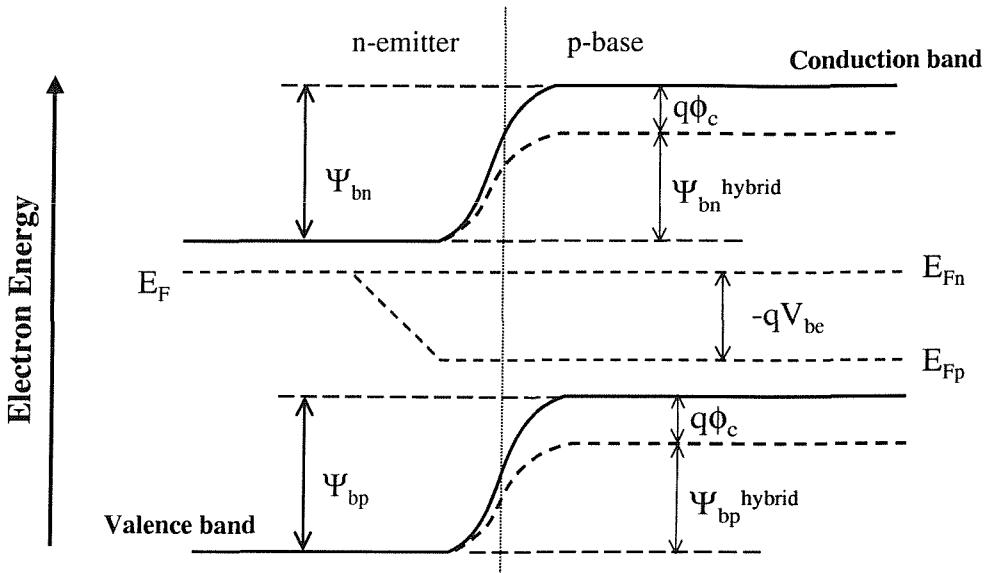

| 3.8 | Diagram indicating the major electron (solid lines) and hole (broken lines) current components in the hybrid-mode lateral BJT. . . . .                                                                                                                                                                                                                                                                                                                                                                                     | 42 |

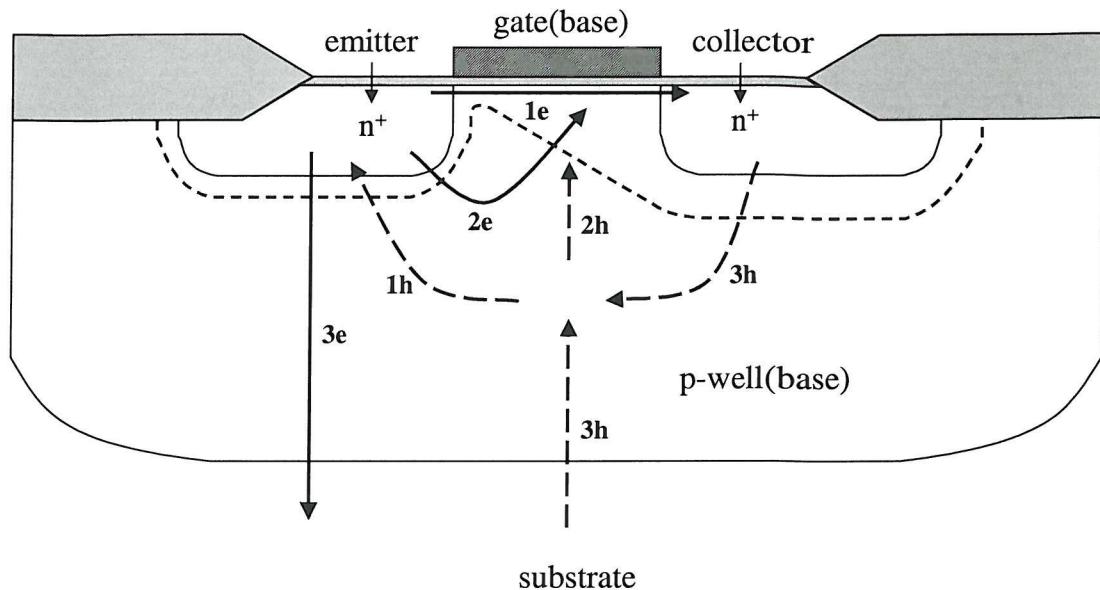

| 3.9 | Energy band diagram for conventional lateral BJT (solid lines) and the hybrid mode lateral BJT (broken lines), through the intrinsic base in the direction perpendicular to the surface. . . . .                                                                                                                                                                                                                                                                                                                           | 42 |

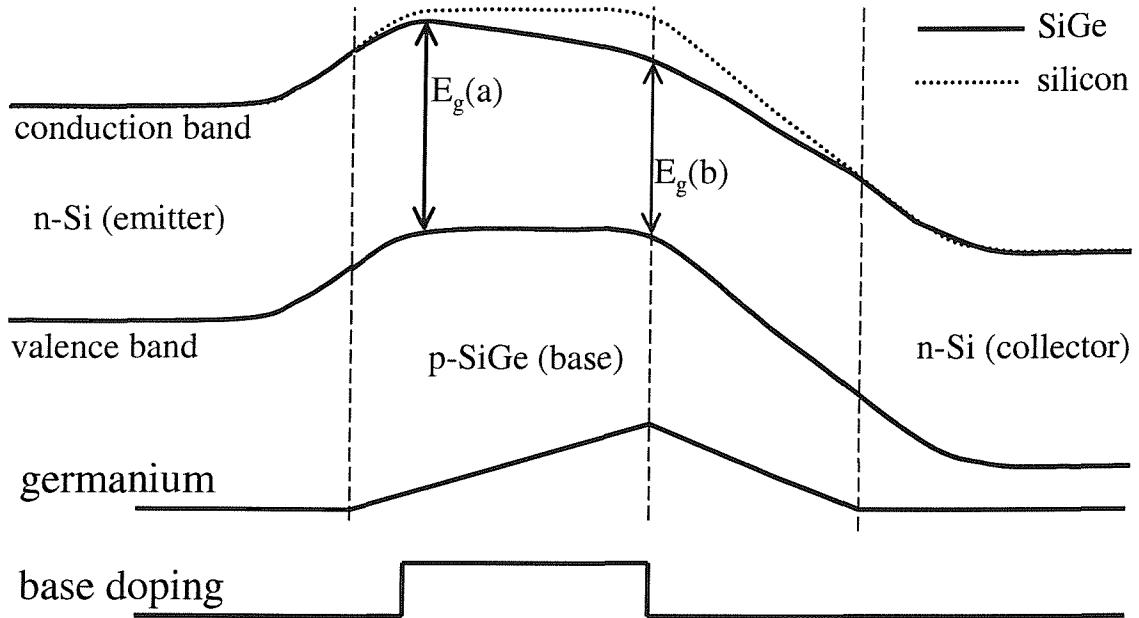

| 4.1 | Figure showing the effect of grading the germanium concentration across the base region on the device band energy. The difference in bandgap across the neutral base is equivalent to $E_g(a) - E_g(b)$ . . . . .                                                                                                                                                                                                                                                                                                          | 46 |

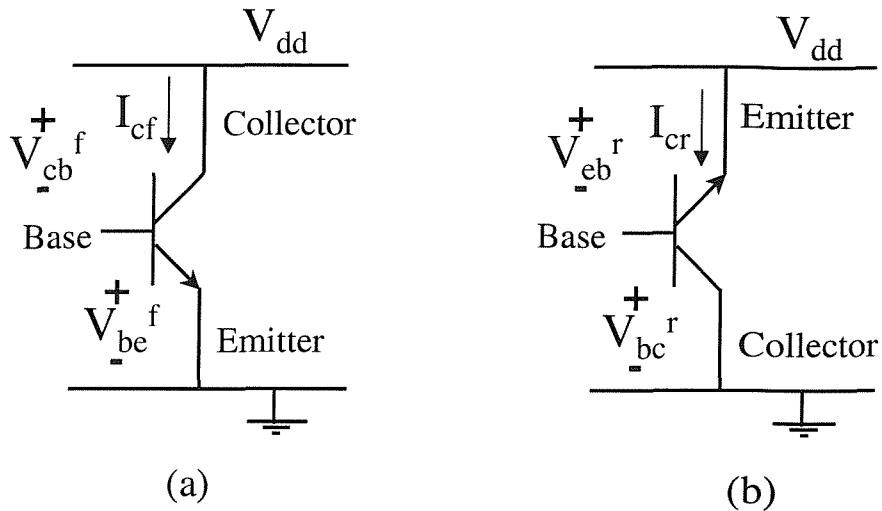

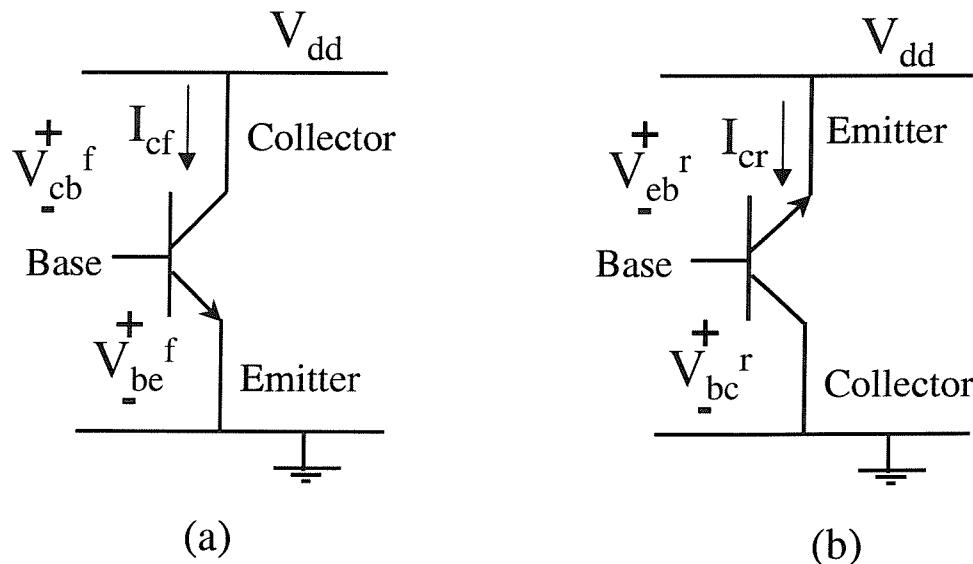

| 4.2 | Circuit diagram of an n-p-n transistor illustrating the bias condition and the current flow when the transistor is biased at the (a) forward active region of operation, and (b) reverse active region of operation. . . . .                                                                                                                                                                                                                                                                                               | 49 |

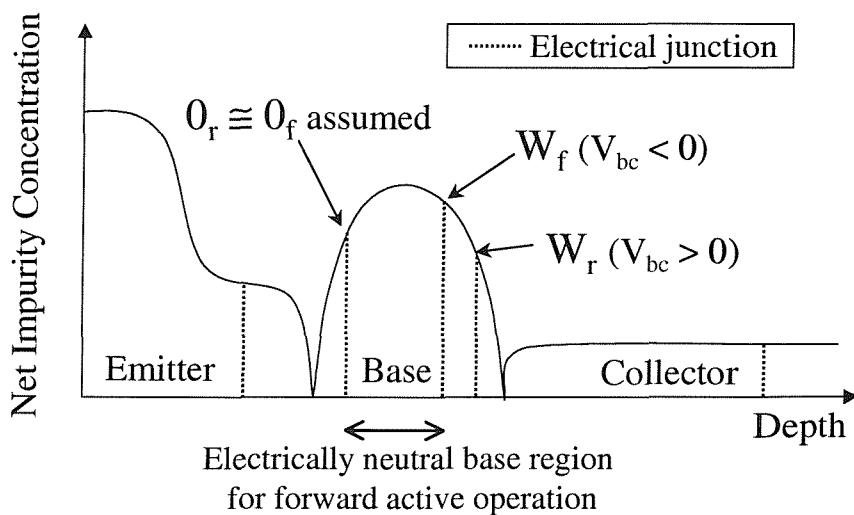

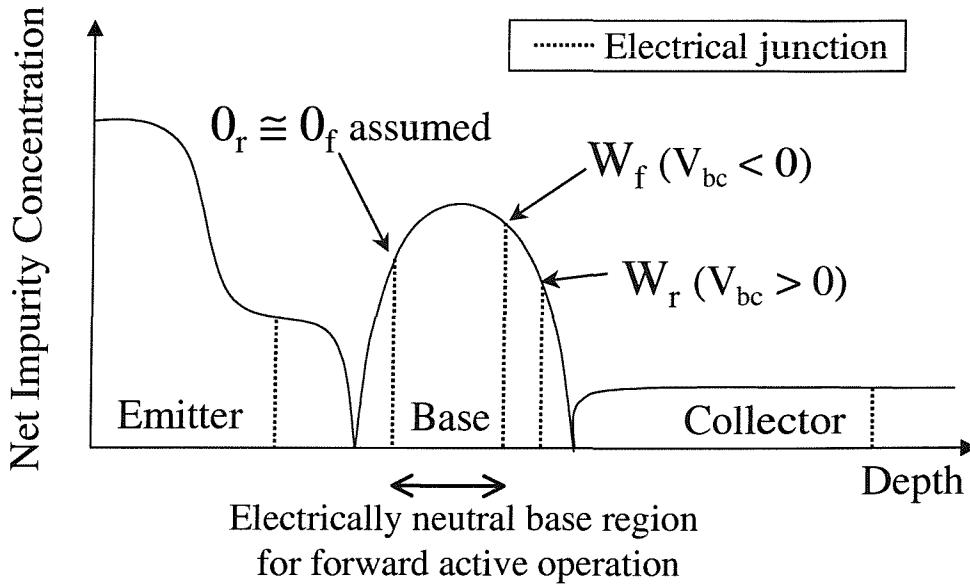

| 4.3 | Figure illustrating the difference of the neutral base boundary positions in the forward active region mode and reverse active region mode. For a highly doped base, which is common for a SiGe HBT, the position of $0_r$ for zero emitter-base bias can be made very close to the position of $0_f$ for normal forward emitter-base junction reverse bias, in reverse active operation. This is because most of the space-charge layer movement will take place in the lower-doped emitter side of the junction. . . . . | 49 |

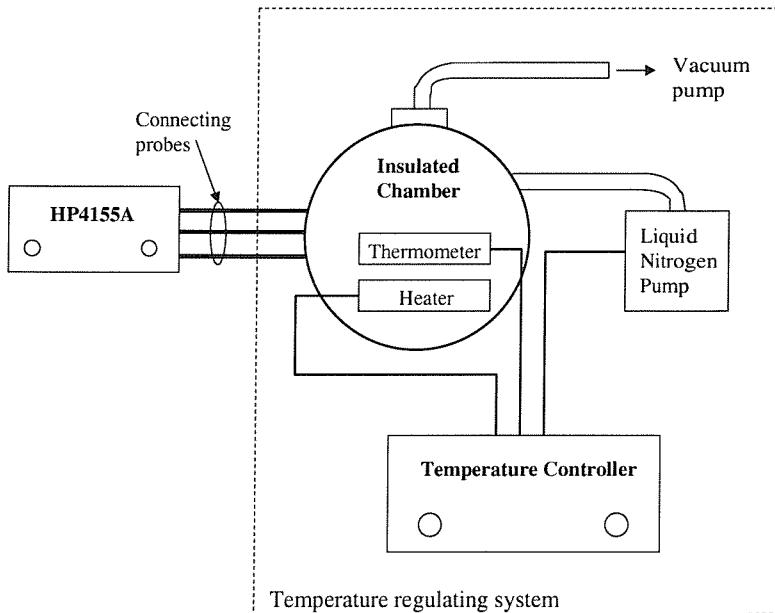

| 4.4 | Figure shows the experimental setup for the proposed bandgap difference extraction technique. It consisted mainly of the HP4155A parameter analyzer and a temperature regulating system. . . . .                                                                                                                                                                                                                                                                                                                           | 55 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

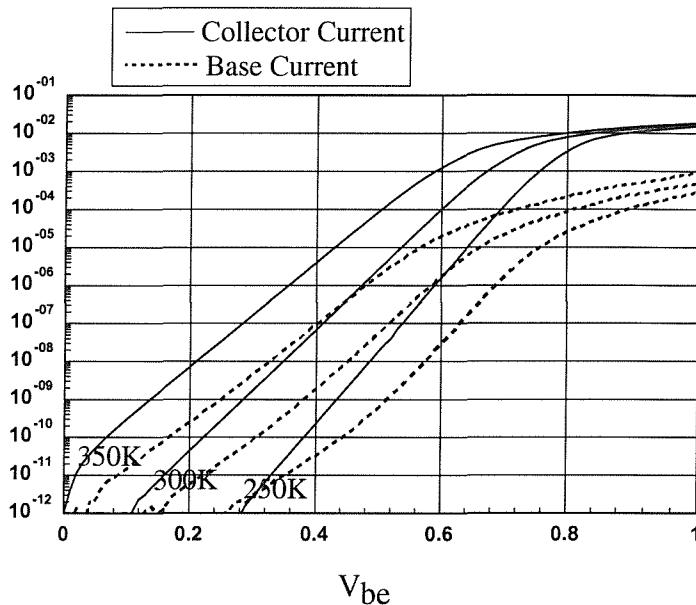

| 4.5  | Gummel plot for increasing temperature shows that the collector and base current increases with temperature. As a result, the $V_{be}^f$ has to be lowered for increasing temperature in order to maintain low operating current. . . . .                                                                                                                                                                                                                       | 56 |

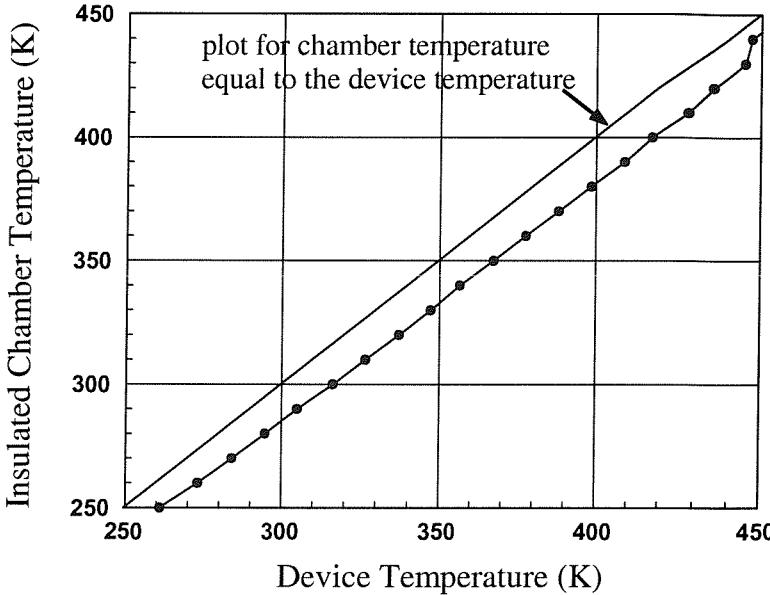

| 4.6  | Figure shows the difference between the insulated chamber temperature (i.e. metal plate temperature) measured by thermometer and the device temperature measured using gummel plot. . . . .                                                                                                                                                                                                                                                                     | 57 |

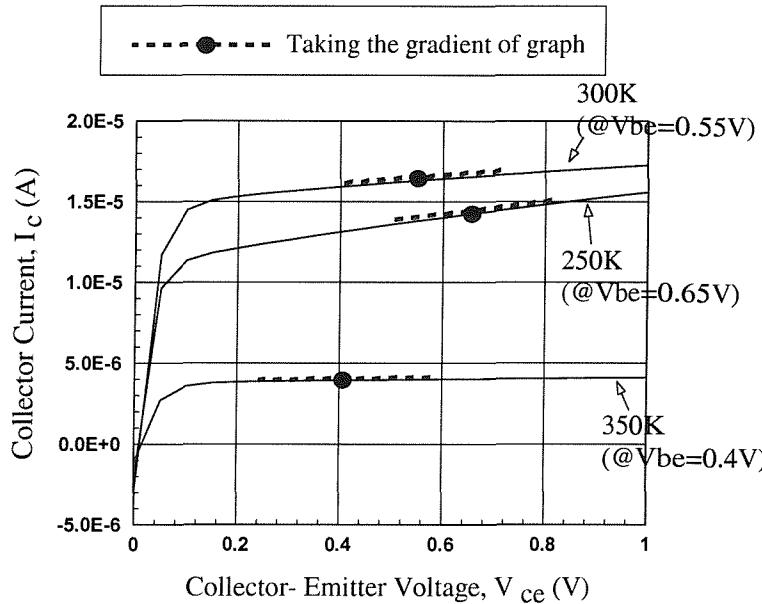

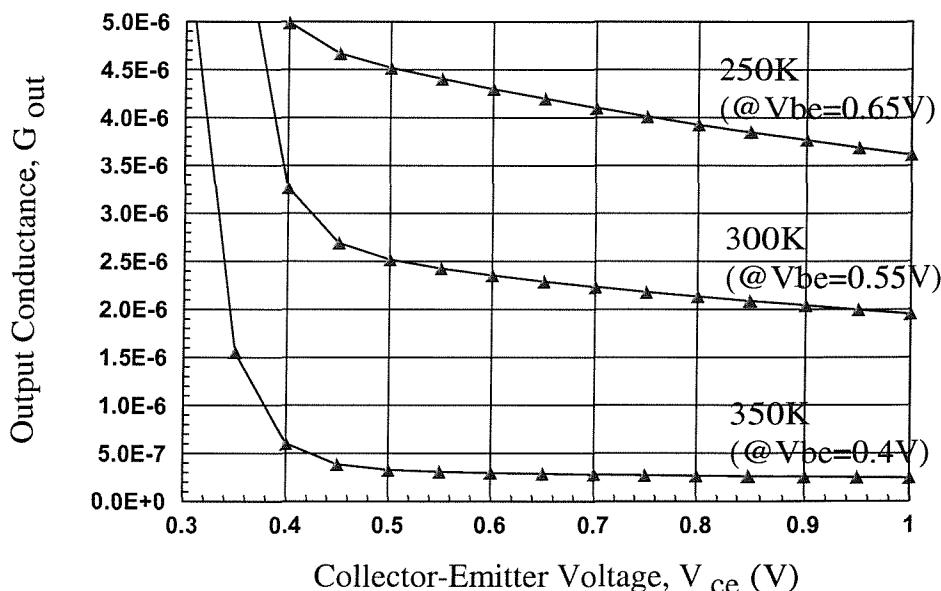

| 4.7  | Figure illustrating dc output conductance extraction of the SiGe HBT (with 5nm spacers) for forward active operation, at 250K, 300K and 350K, by measuring the gradient of the collector bias <i>vs</i> collector current graph. . . . .                                                                                                                                                                                                                        | 58 |

| 4.8  | Figure showing the output conductance for increasing $V_{ce}$ , at 250K, 300K and 350K, extracted using HP4155A parameter analyzer. . . . .                                                                                                                                                                                                                                                                                                                     | 58 |

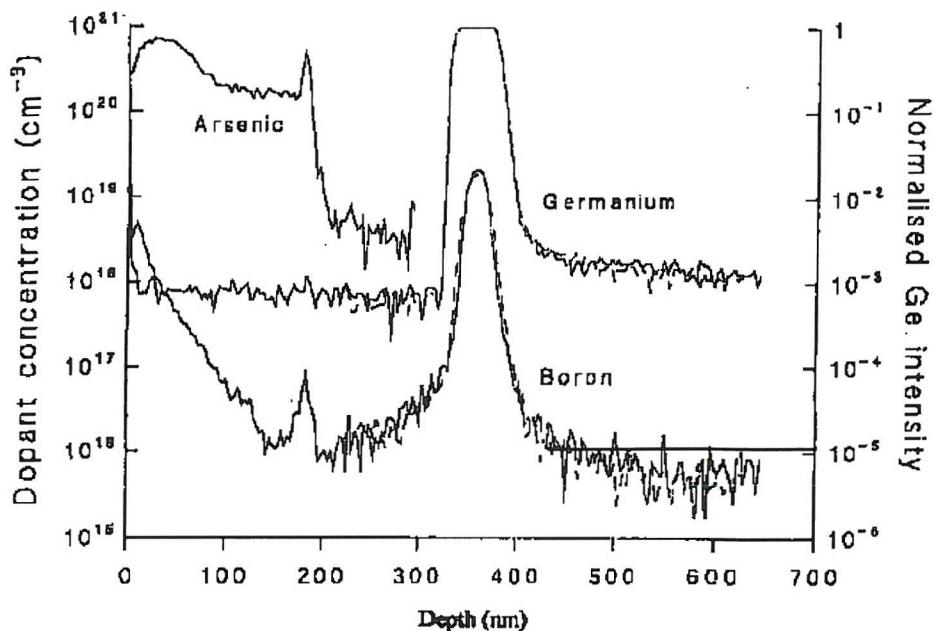

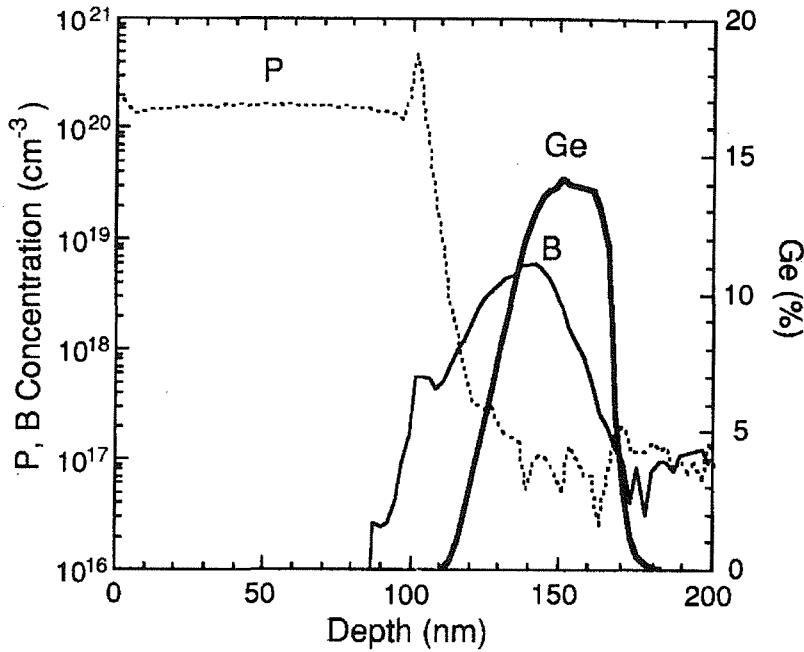

| 4.9  | SIMS profile of Device A and Device B, used for the experimental verification of the measurement technique. . . . .                                                                                                                                                                                                                                                                                                                                             | 60 |

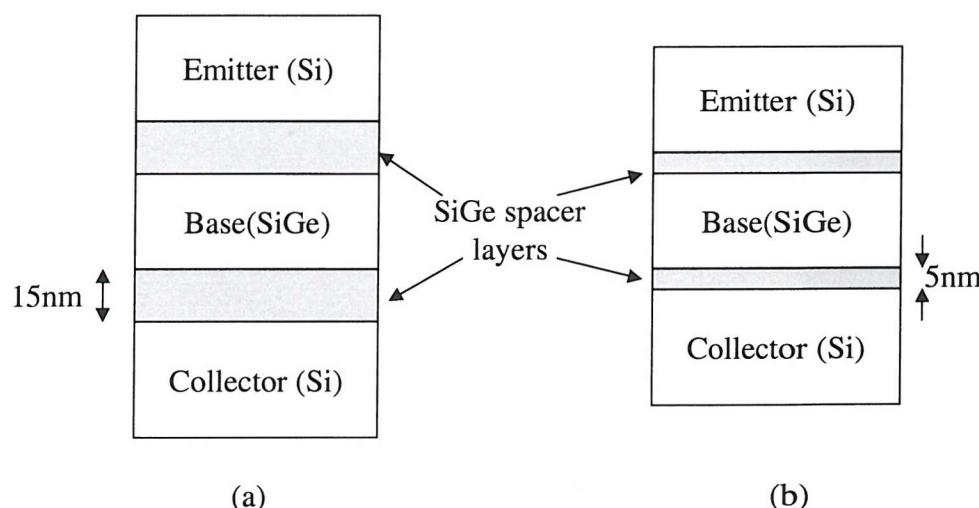

| 4.10 | (a) Device A, with 15nm wide undoped SiGe base spacers at the emitter and collector sides of the base, used for experimental measurements, (b) Device B, with 5nm wide undoped SiGe base spacers at the emitter and collector sides of the base, used for experimental measurements. .                                                                                                                                                                          | 60 |

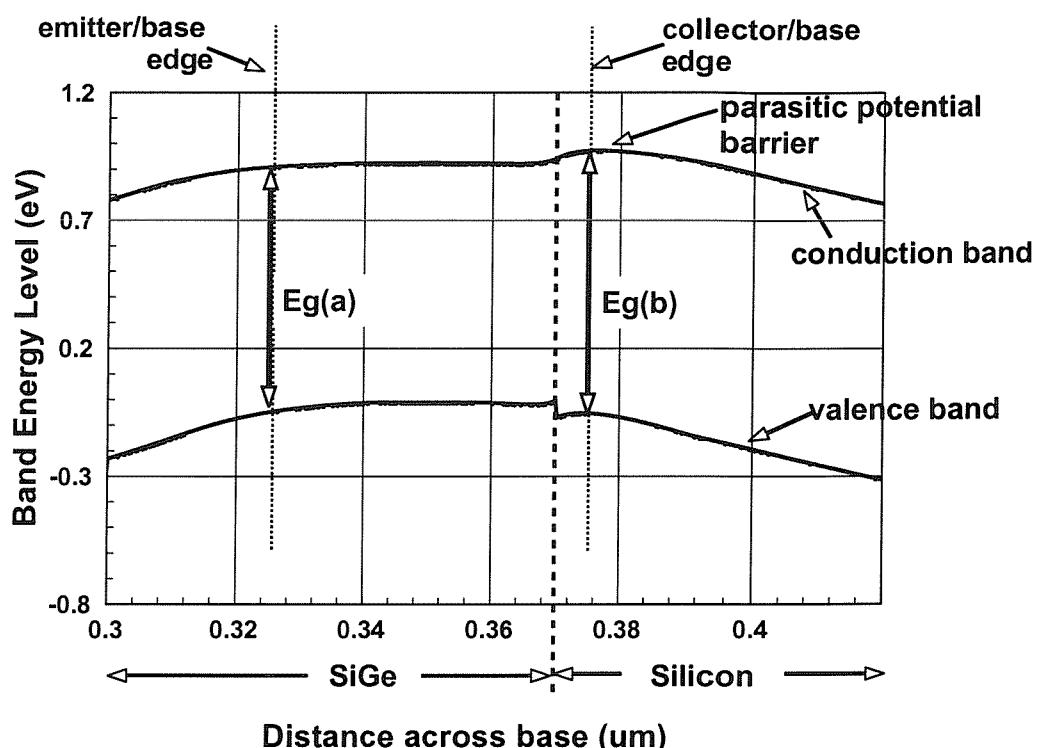

| 4.11 | Base conduction and valence band energy diagram illustrating possible physical bandgap energy in Device B which was used in experimental measurement. It is shown that the neutral base edge at the collector side resides in the silicon region (parasitic barrier region) whereas the neutral base edge at the emitter side resides in the SiGe region. The bandgap difference across the neutral base is therefore equivalent to $E_g(a) - E_g(b)$ . . . . . | 61 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

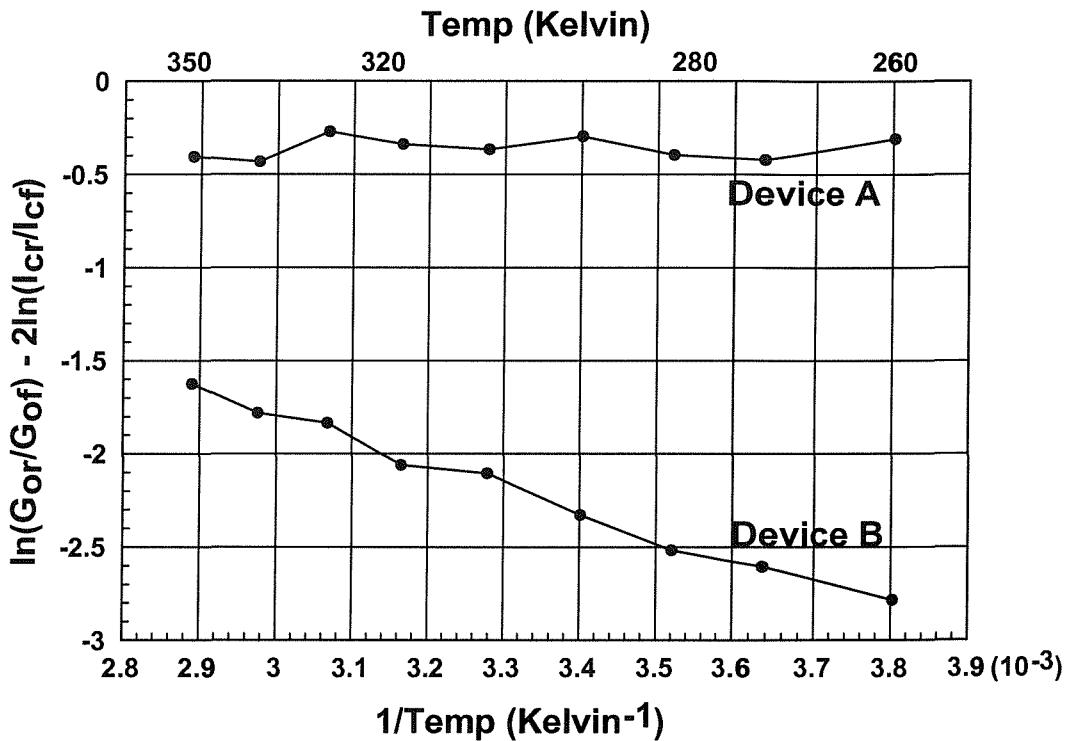

| 4.12 Experimental results obtained for Device A (15nm spacers) and Device B (5nm spacers), where bandgap grading across the neutral base (slope of graph) are extracted and found to be 0.002 eV and -0.104 eV respectively. The slopes of the curves give the bandgap difference across the neutral base divided by Boltzmann's constant $k$ for each case. Note that a negative slope indicates a retarding electric field and a positive slope indicates a positive retarding electric field in the base. . . . .                                                                          | 62 |

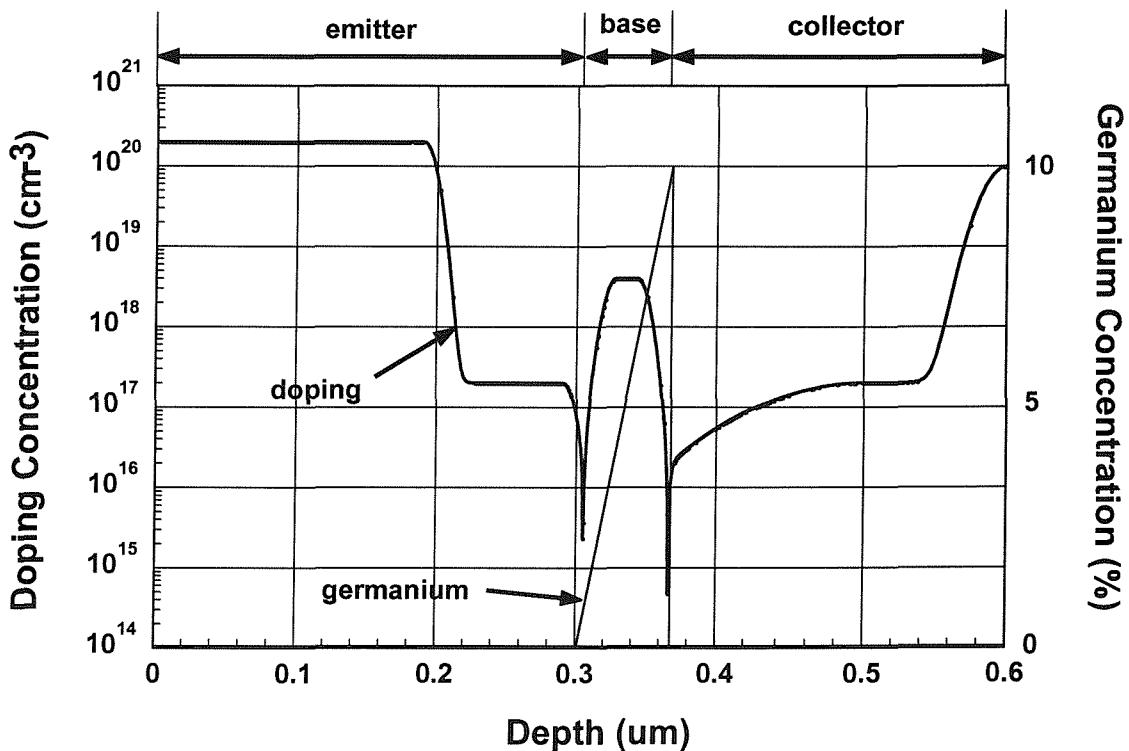

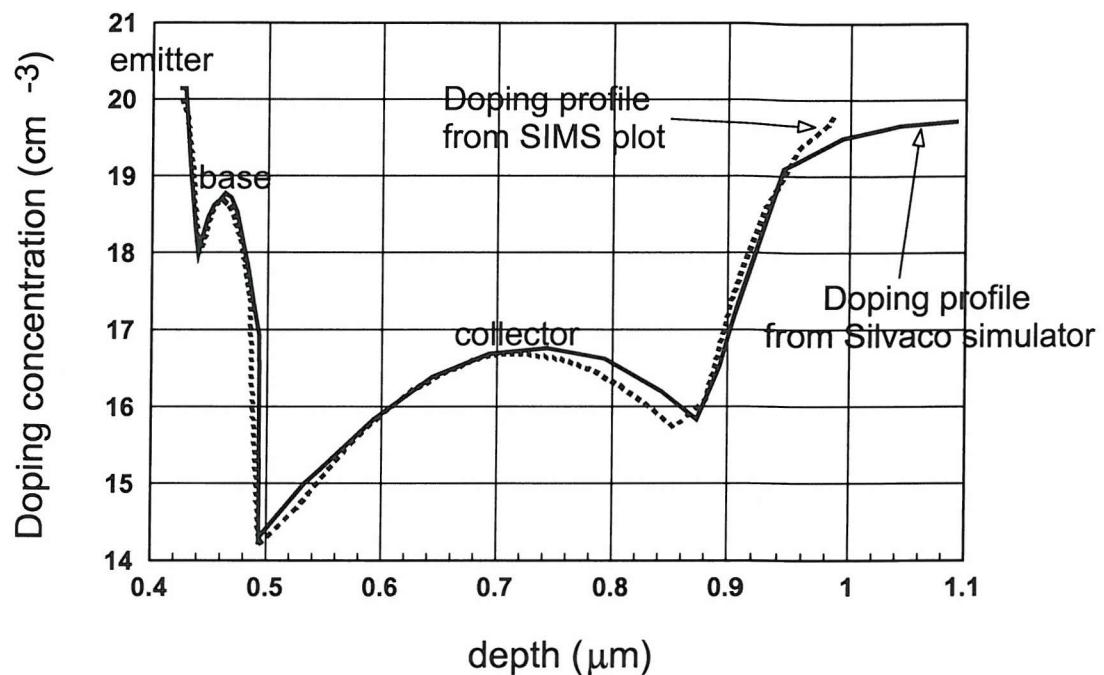

| 4.13 Net impurity profile for high performance device structure from [11], used in numerical simulations to produce the results shown in Figures 4.14 and 4.16. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                       | 64 |

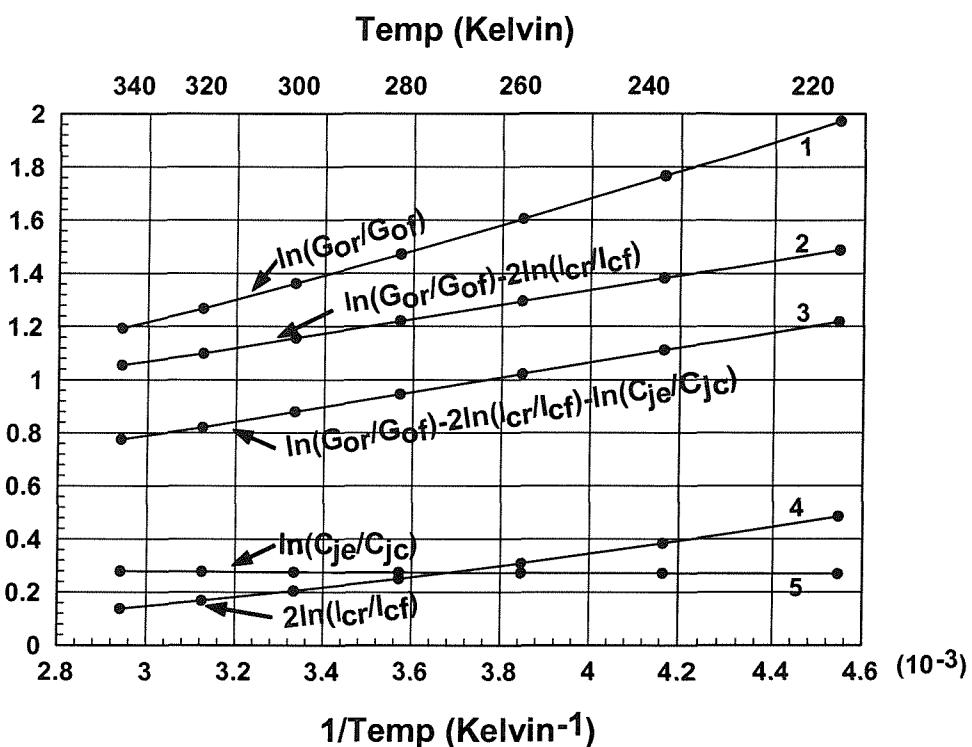

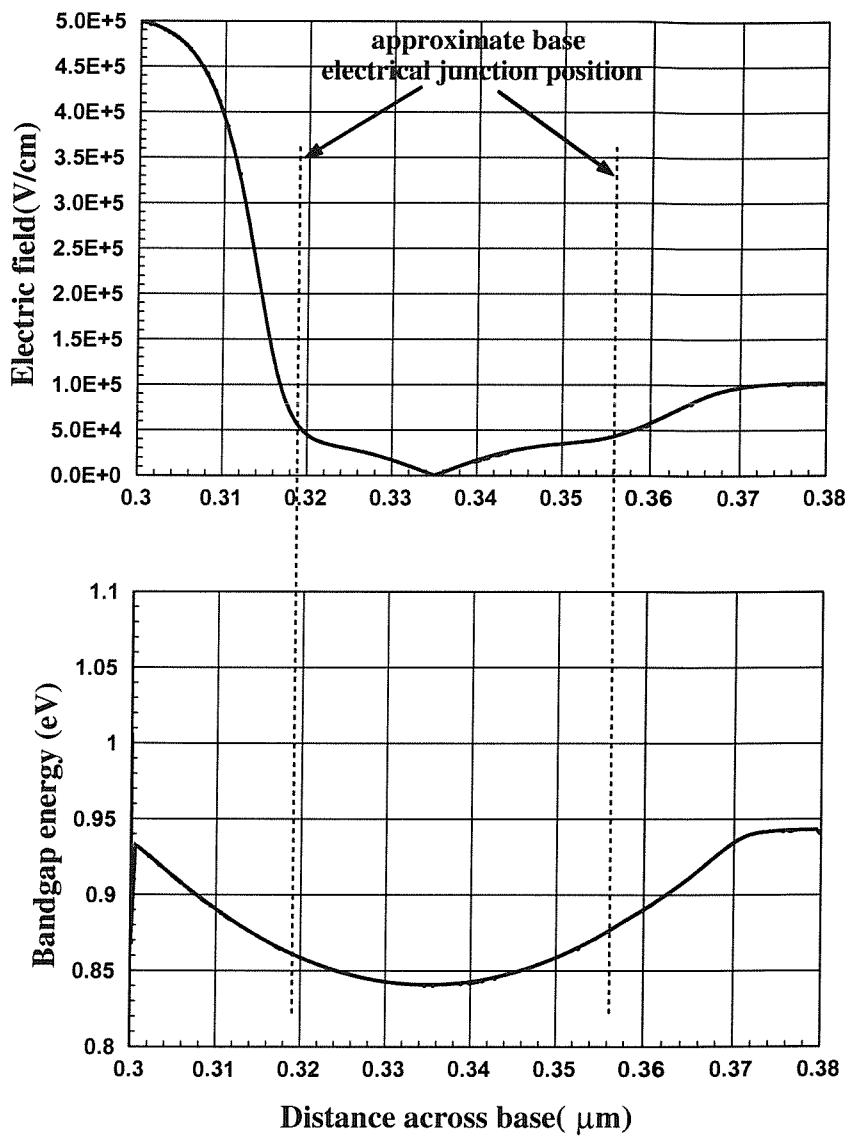

| 4.14 Numerical simulations of Equation 4.14 for the device structure shown in Figure 4.13, where various terms are included. The germanium grading between metallurgical junctions was 10% increasing towards the collector. The slopes of curves #2 and #3 give the bandgap difference across the neutral base divided by Boltzmann's constant $k$ . The positive slope indicates that the bandgap is smaller by 0.023 eV at the collector side of the neutral base region than at the emitter side in agreement with the internally defined device in the 2-D numerical simulation. . . . . | 66 |

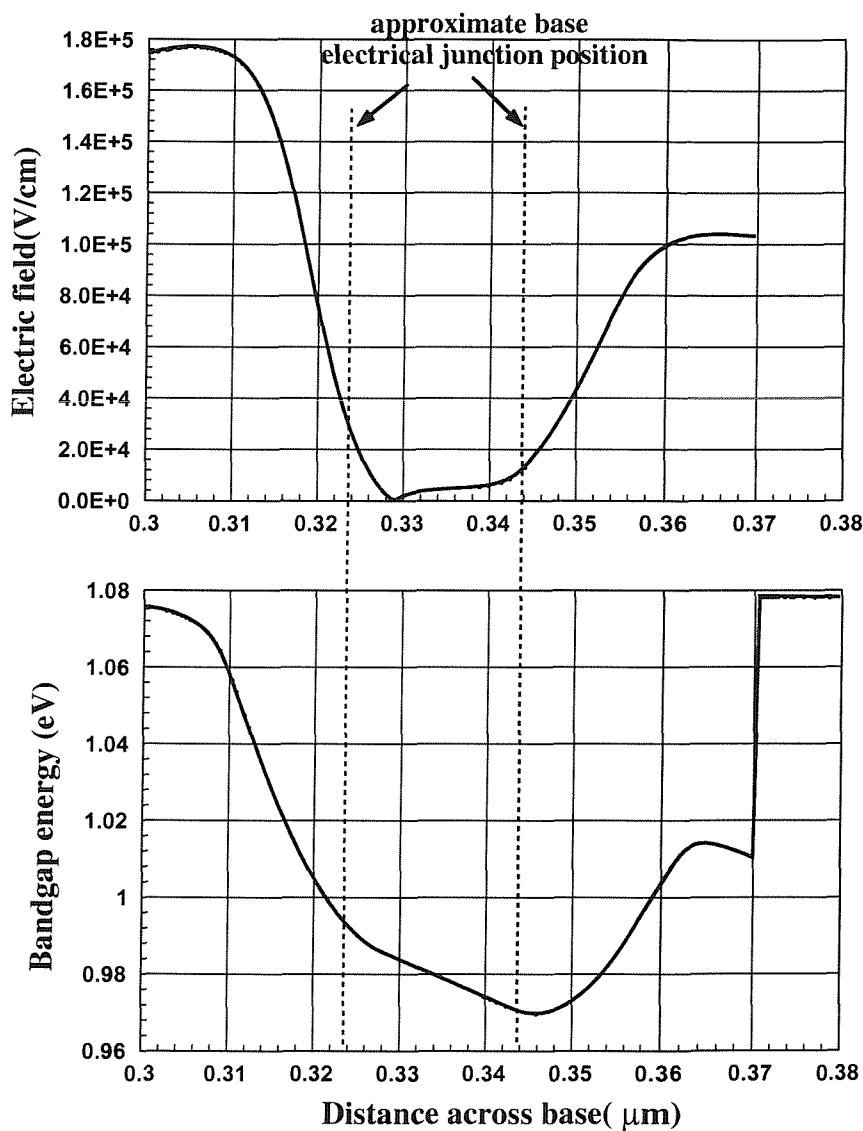

| 4.15 Plot showing the bandgap variation across the base metallurgical junction, where germanium concentration increases from 0 to 10% linearly towards the collector, for device structures shown in Figure 4.13. With the approximated base electrical junctions positions using the electric field across the base for zero bias collector-base and emitter-base junctions, the bandgap difference across the neutral base is found to be 0.022 eV. . . . .                                                                                                                                 | 67 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

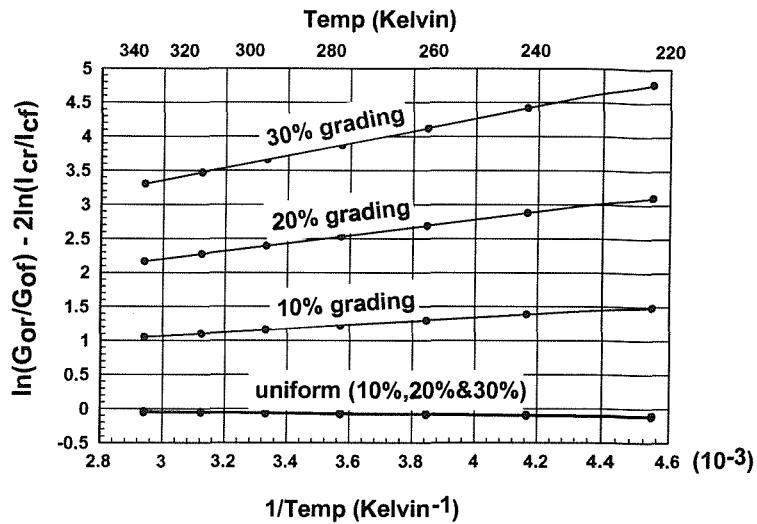

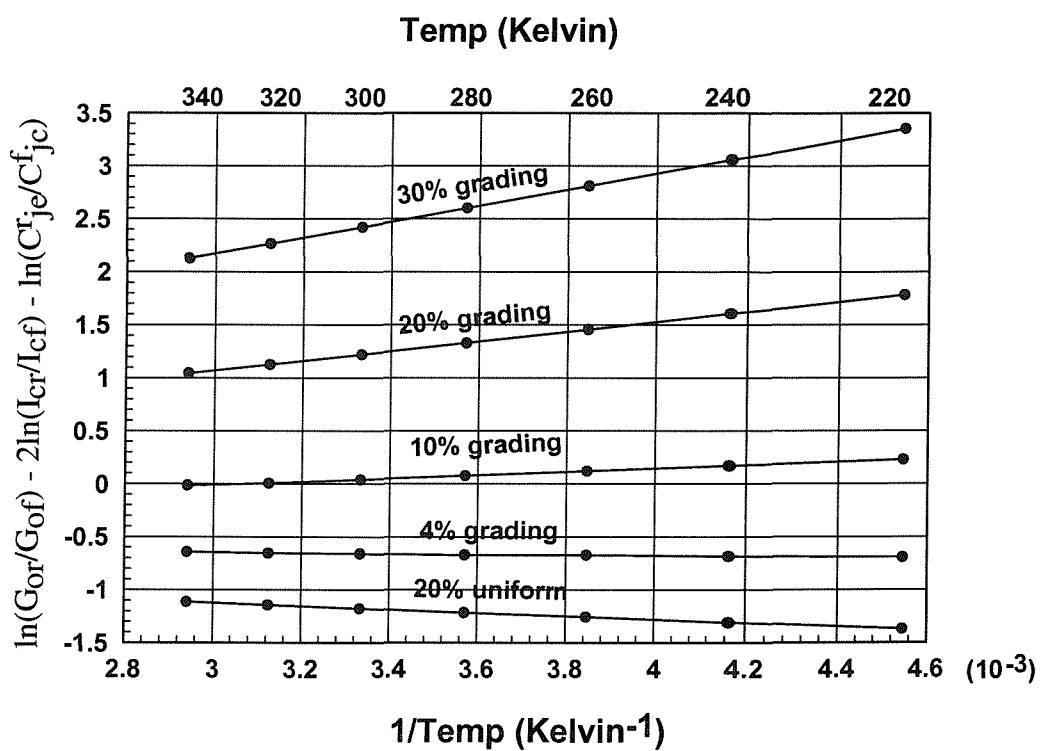

| 4.16 Numerical simulations demonstrating the bandgap grading measurement technique for the device structure show in Figure 4.13. Without taking into consideration the capacitance term in Equation 4.14, results for various amounts of bandgap grading are shown. The slopes of the curves give the bandgap difference across the neutral base divided by Boltzmann's constant $k$ for each case. . . . .                                                             | 68 |

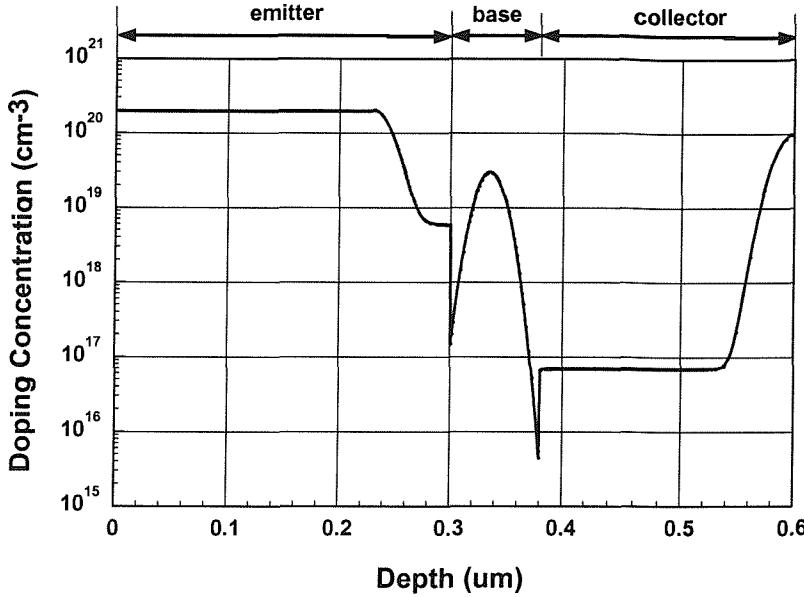

| 4.17 Net impurity profile of high speed device structure from [2], used in numerical simulations to produce the results shown in Figures 4.18 to 4.20. . . . .                                                                                                                                                                                                                                                                                                          | 69 |

| 4.18 Numerical simulations of Equation 4.14 for the device structure shown in Figure 4.17 for 20% uniform germanium concentration in the base, where various terms are included. The slope of curve #5 gives the bandgap difference across the neutral base divided by Boltzmann's constant $k$ . The negative slope of curve #5 indicates that the bandgap is larger by 0.014 eV at the collector side of the neutral base region than at the emitter side. . . . .    | 70 |

| 4.19 Numerical simulation results showing the variation in bandgap energy across the neutral base region due to both germanium and impurity induced bandgap reduction for the device impurity profile shown in Figure 4.17. With the approximated base electrical junctions positions using the electric field across the base for zero bias collector-base and emitter-base junctions, the bandgap difference across the neutral base is found to be 0.015 eV. . . . . | 71 |

| 4.20 Numerical simulations demonstrating the bandgap grading measurement technique for the device structure shown in Figure 4.17 where results for various amount of bandgap grading are shown. The slopes of the curves give the bandgap difference across the neutral base divided by Boltzmann's constant $k$ for each case. . . . .                                                                                                                                 | 72 |

|     |                                                                                                                                                                                                                                                                                                                                                                                       |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

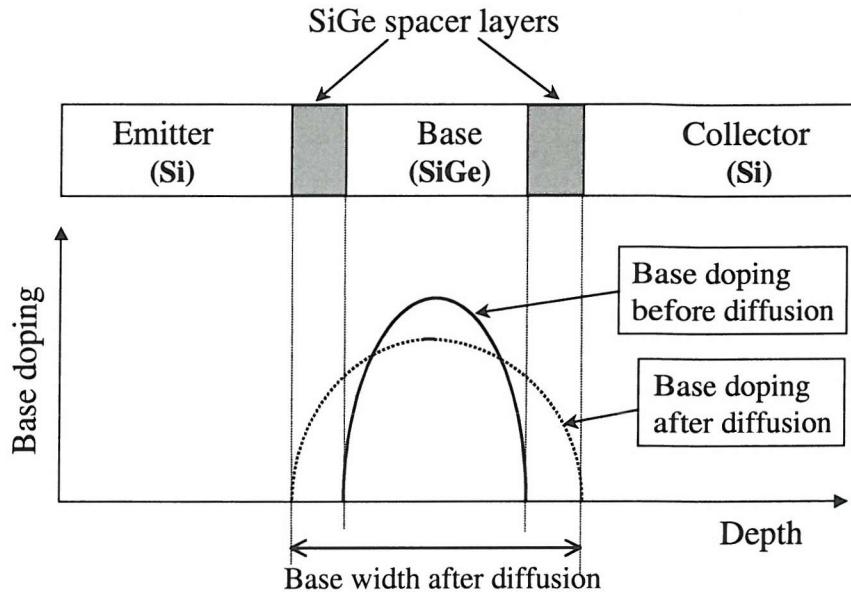

| 5.1 | Figure showing the diffusion of boron doping from it's original position and the use of SiGe spacer layers to contain the base boron doping inside the SiGe base region. . . . .                                                                                                                                                                                                      | 76 |

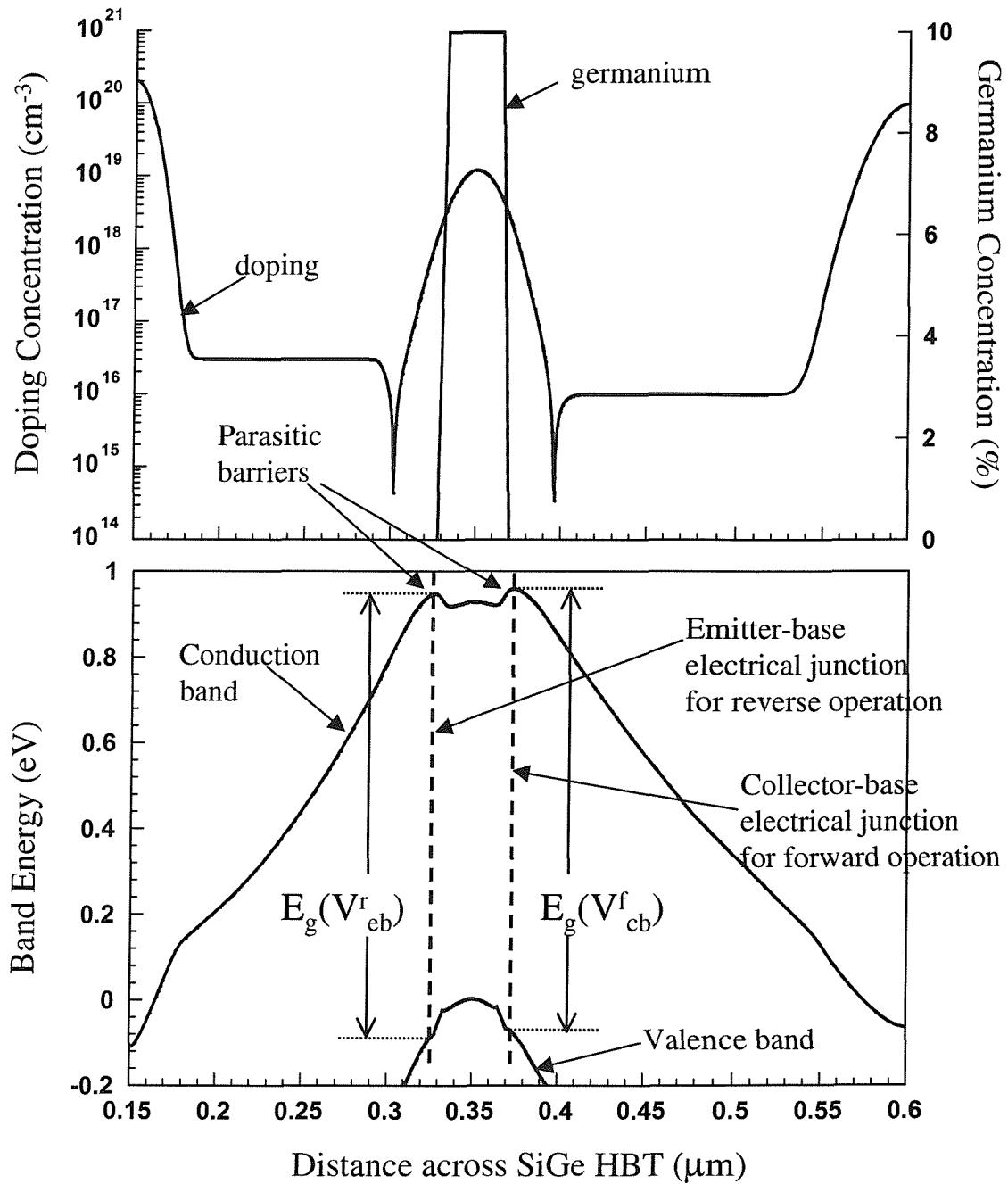

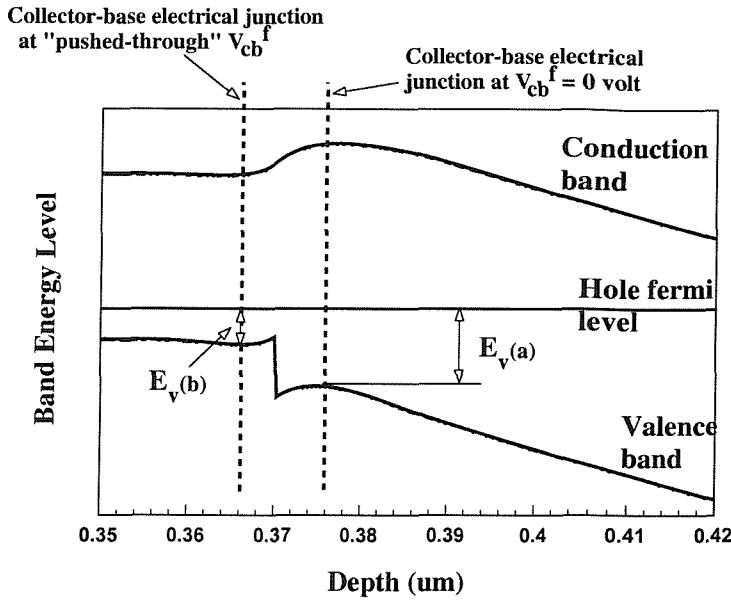

| 5.2 | Figure illustrates, with the aid of numerical simulations [56], the effect of doping profile and germanium concentration on the base conduction and valence energy bands for a SiGe HBT where boron out-diffusion exists. Parasitic barriers are shown to exist at zero bias. The positions of $E_g(V_{cb}^f)$ and $E_g(V_{eb}^r)$ used in Equation (5.2) are also indicated. . . . . | 78 |

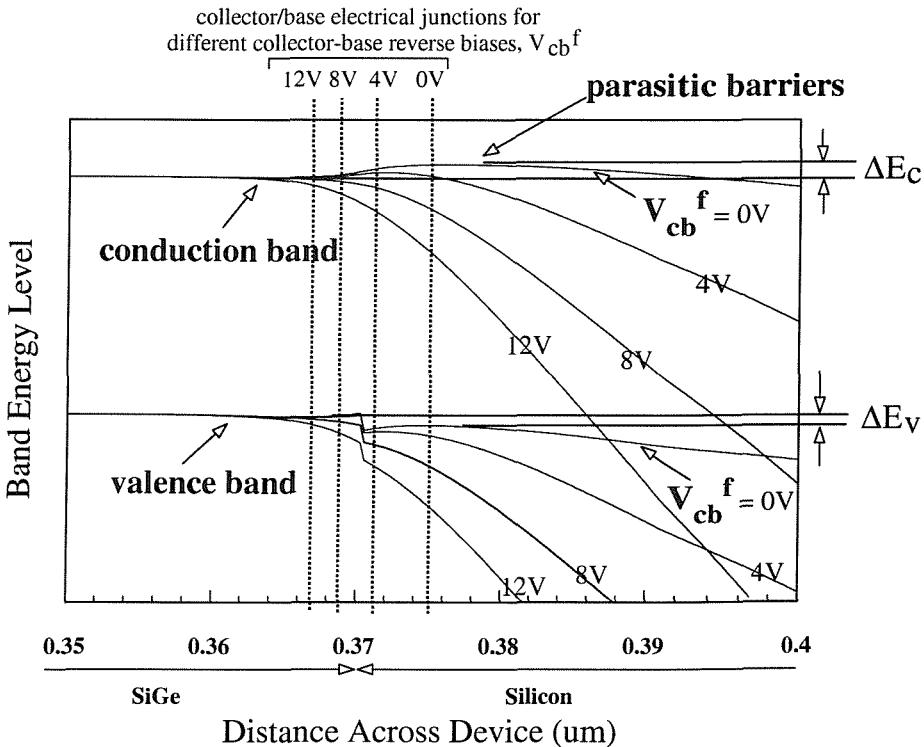

| 5.3 | Figure illustrates, with the aid of numerical simulations [56], the dependence of the collector-base parasitic barrier's shape on $V_{cb}^f$ . It shows the movement of the electrical junction with regards to $V_{cb}^f$ , and also how the parasitic energy barrier can be lowered by increasing $V_{cb}^f$ . $\Delta E_c$ and $\Delta E_v$ are also indicated. . . . .            | 79 |

| 5.4 | Figure showing the valence band variation at the collector-base junction due to non-uniform base doping. The offset between the hole fermi level and the valence band decreases with increasing $V_{cb}^f$ and the total valence band changes, $\Delta E_v$ , is equivalent to $E_v(a) - E_v(b)$ . . . . .                                                                            | 81 |

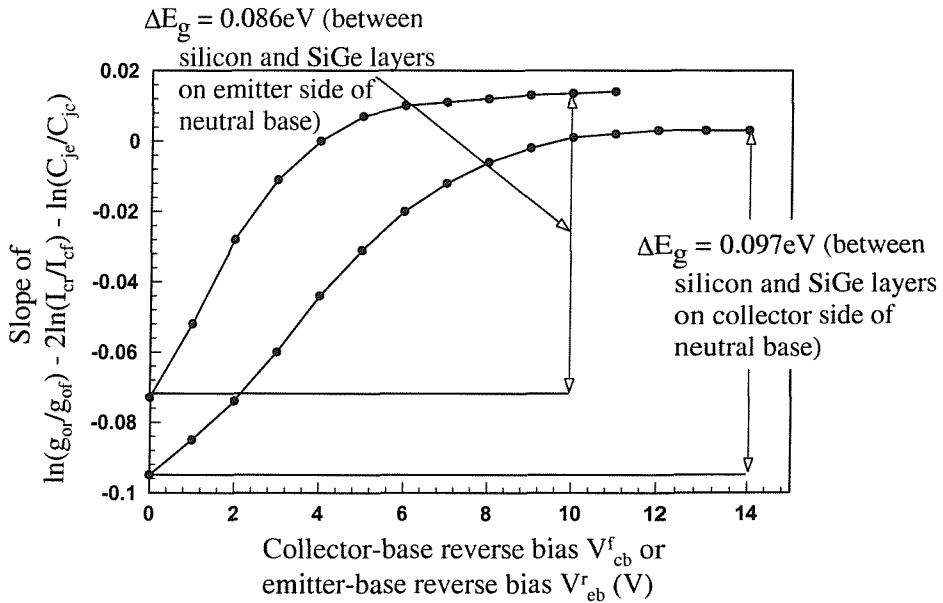

| 5.5 | Figure showing the change of the slope of Equation 5.3 (i.e. $E_g(V_{eb}^r) - E_g(V_{cb}^f)$ ) with regarding to the increasing $V_{cb}^f$ for the parasitic barrier at the collector-base junction of the simulated device. . . . .                                                                                                                                                  | 83 |

| 5.6 | Figure showing the change of the slope of Equation 5.3 (i.e. $E_g(V_{eb}^r) - E_g(V_{cb}^f)$ ) with regarding to the increasing $V_{eb}^r$ for the parasitic barrier at the emitter-base junction of the simulated device. . . . .                                                                                                                                                    | 83 |

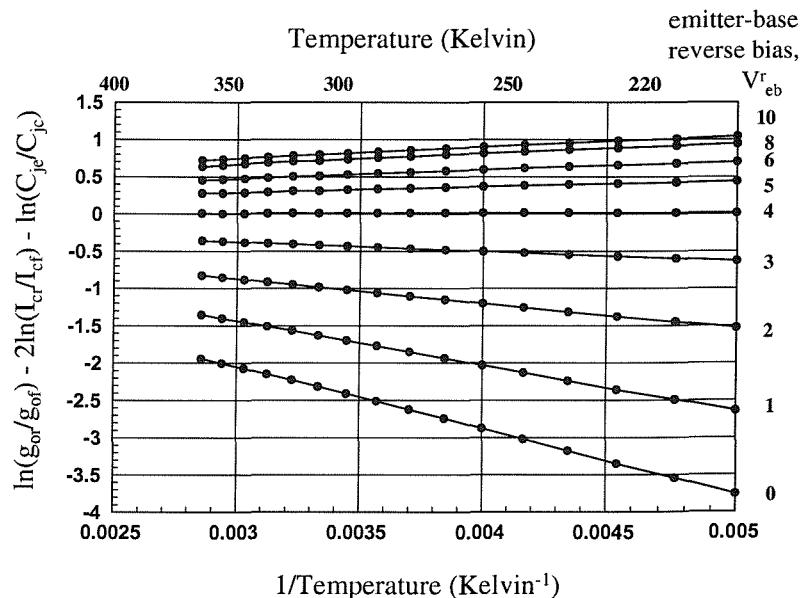

| 5.7 | Plots of the slope of $\ln(g_{or}/g_{of}) - 2 \ln(I_{cr}/I_{cf}) - \ln(C_{je}/C_{jc})$ vs $V_{cb}^f$ (or $V_{eb}^r$ for the emitter-base junction) were used to "measure" the emitter-base and collector-base bandgap variation across the parasitic barrier of the simulated device. . . . .                                                                                         | 84 |

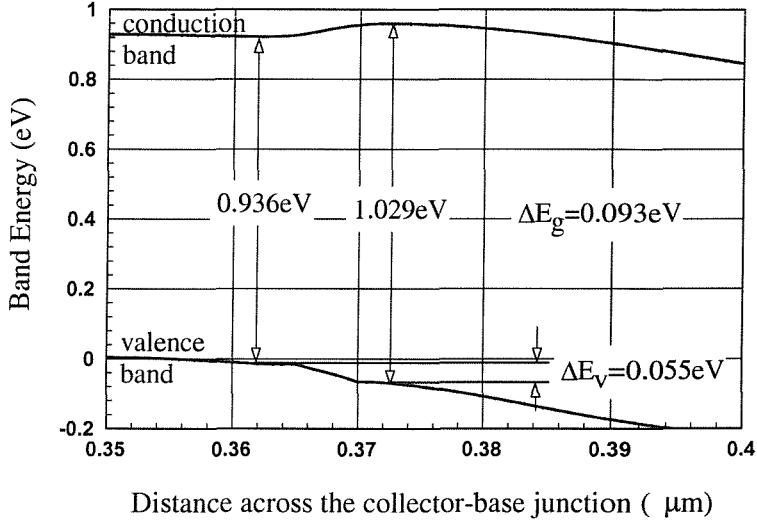

| 5.8 | Band energy diagram of the collector-base junction for $V_{cb}^f = 0V$ plotted from internal simulation data. $\Delta E_g$ and $\Delta E_v$ are found to be 0.093 eV and 0.055 eV, respectively. . . . .                                                                                                                                                                              | 85 |

|      |                                                                                                                                                                                                                                                                                                                           |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

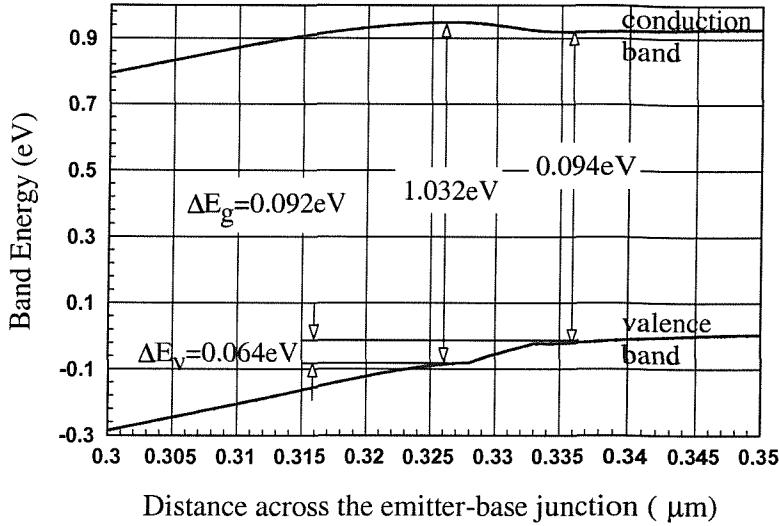

| 5.9  | Band energy diagram of the emitter-base junction for $V_{eb}^r = 0V$ plotted from internal simulation data. $\Delta E_g$ and $\Delta E_v$ are found to be $0.092\text{ eV}$ and $0.064\text{ eV}$ , respectively. . . . .                                                                                                 | 86 |

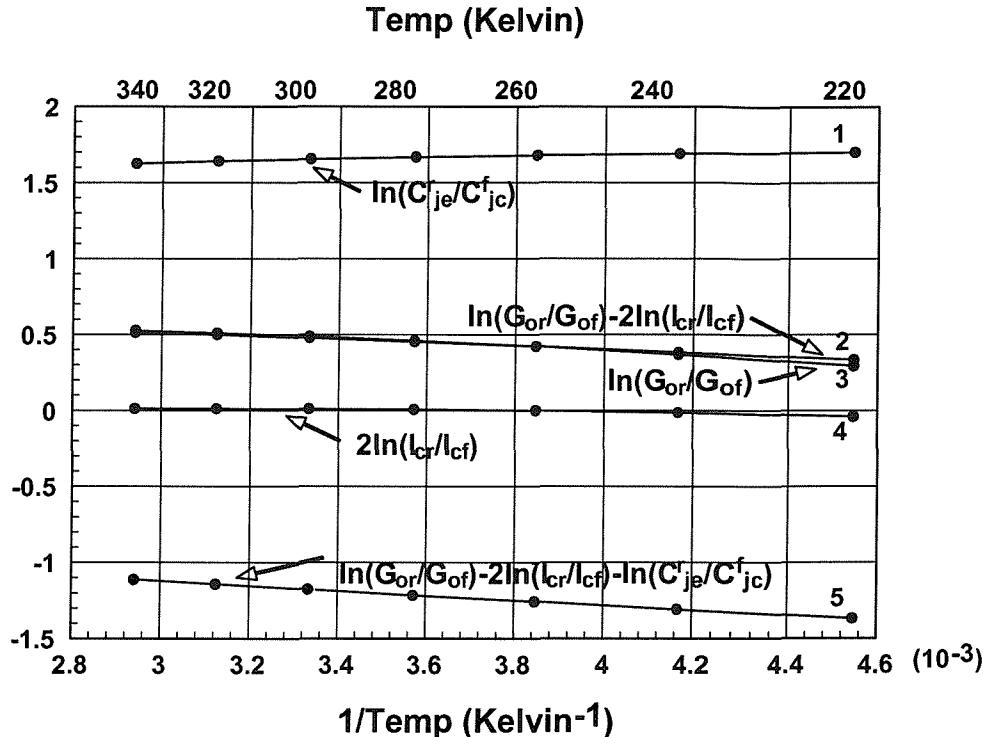

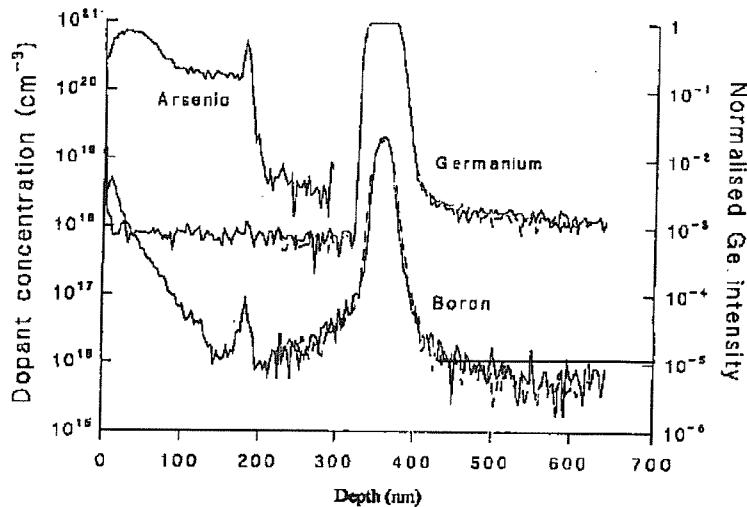

| 5.10 | Doping profile from SIMS of the fabricated n-p-n SiGe HBT device measured for experimental verification of the new proposed method. . . . .                                                                                                                                                                               | 87 |

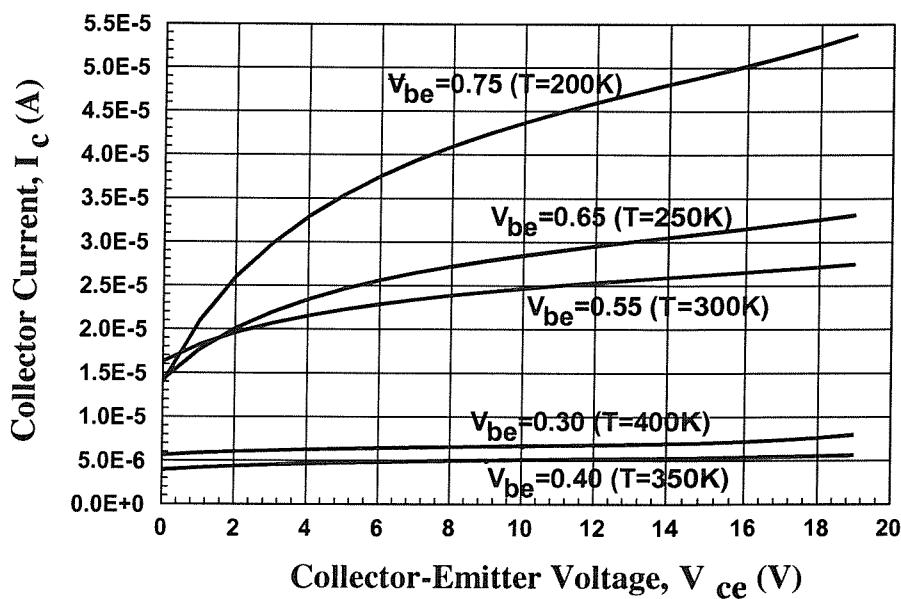

| 5.11 | The collector current, $I_c$ , versus the reverse biased collector-base voltage, $V_{cb}^f$ , showing that the forward active mode base-collector junction can be reverse biased up to $19\text{ V}$ without breaking down. . . . .                                                                                       | 87 |

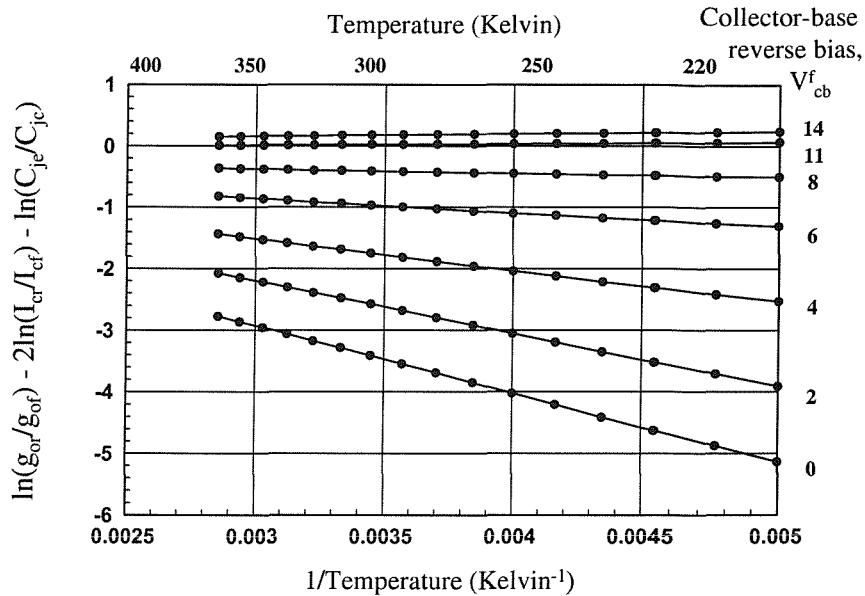

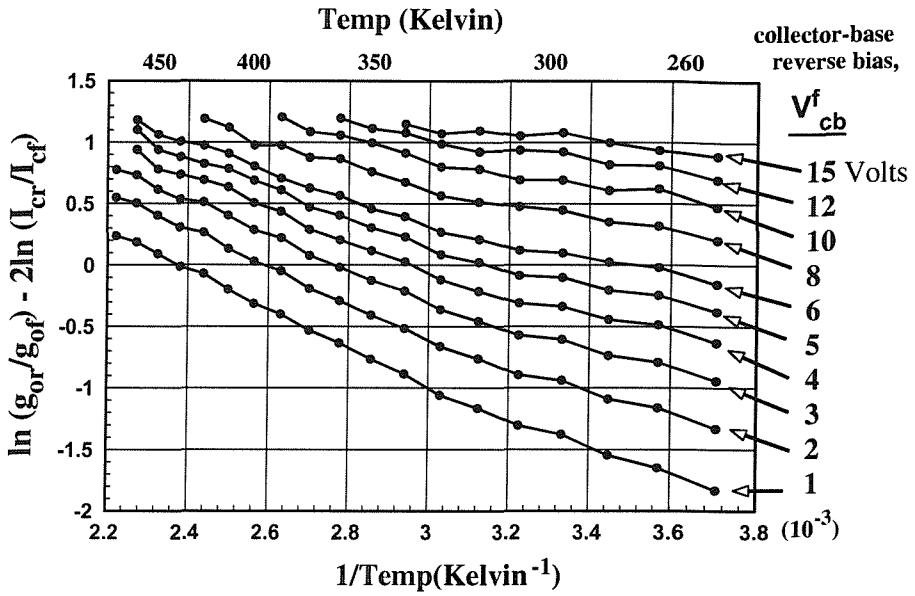

| 5.12 | The slope of $\ln(g_{or}/g_{of}) - 2\ln(I_{cr}/I_{cf})$ indicates that a rather large bandgap variation, $\Delta E_g$ , is present in the measured device as the slope changes considerably with collector-base reverse bias $V_{cb}^f$ . . . . .                                                                         | 88 |

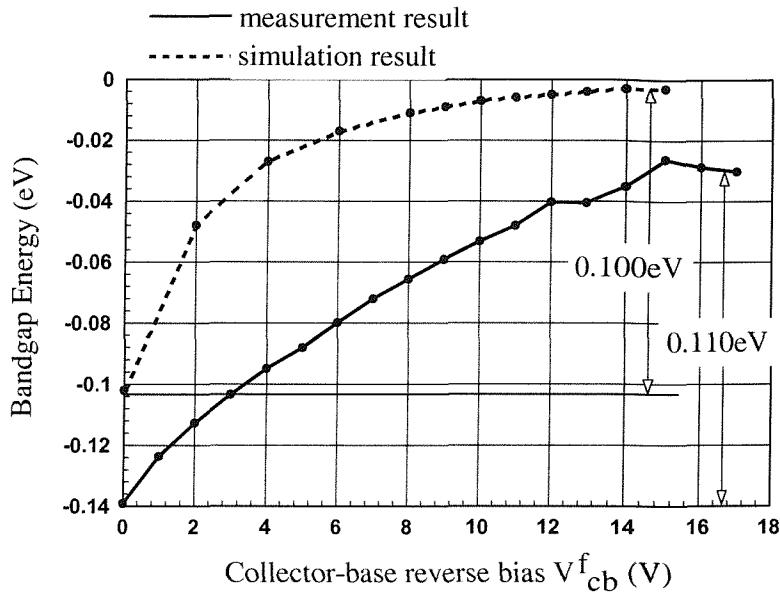

| 5.13 | The plot illustrates the changes of bandgap with increasing collector-base reverse bias $V_{cb}^f$ . $\Delta E_g$ of $0.110\text{ eV}$ and $0.100\text{ eV}$ were extracted from the measurement results and simulation results, respectively. . . . .                                                                    | 89 |

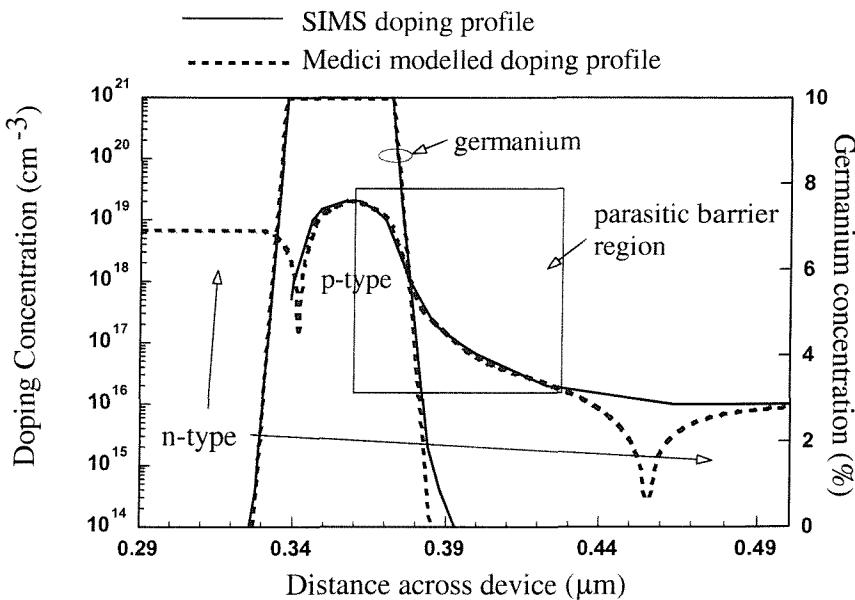

| 5.14 | The modelling of the measured n-p-n SiGe HBT device doping profile using semiconductor device simulator Medici. Note that the highlighted part of the boron profile, where the collector-base parasitic barrier exists, is modelled very closely in order to reproduce the measurement results in the simulation. . . . . | 89 |

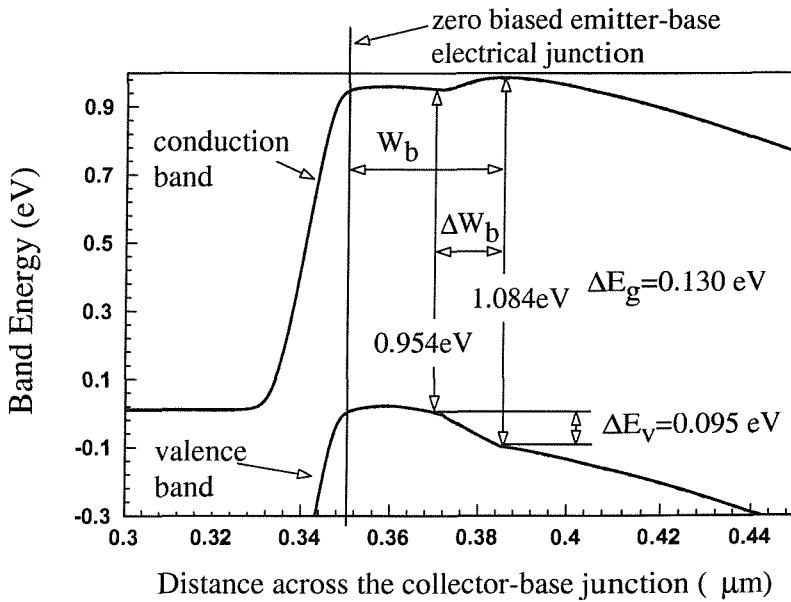

| 5.15 | Simulated band energy diagram of the collector-base junction for $V_{cb}^f = 0V$ plotted from internal simulation data of experimentally measured device. Modelled $\Delta E_g$ and $\Delta E_v$ are $0.130\text{ eV}$ and $0.095\text{ eV}$ , respectively. . . . .                                                      | 90 |

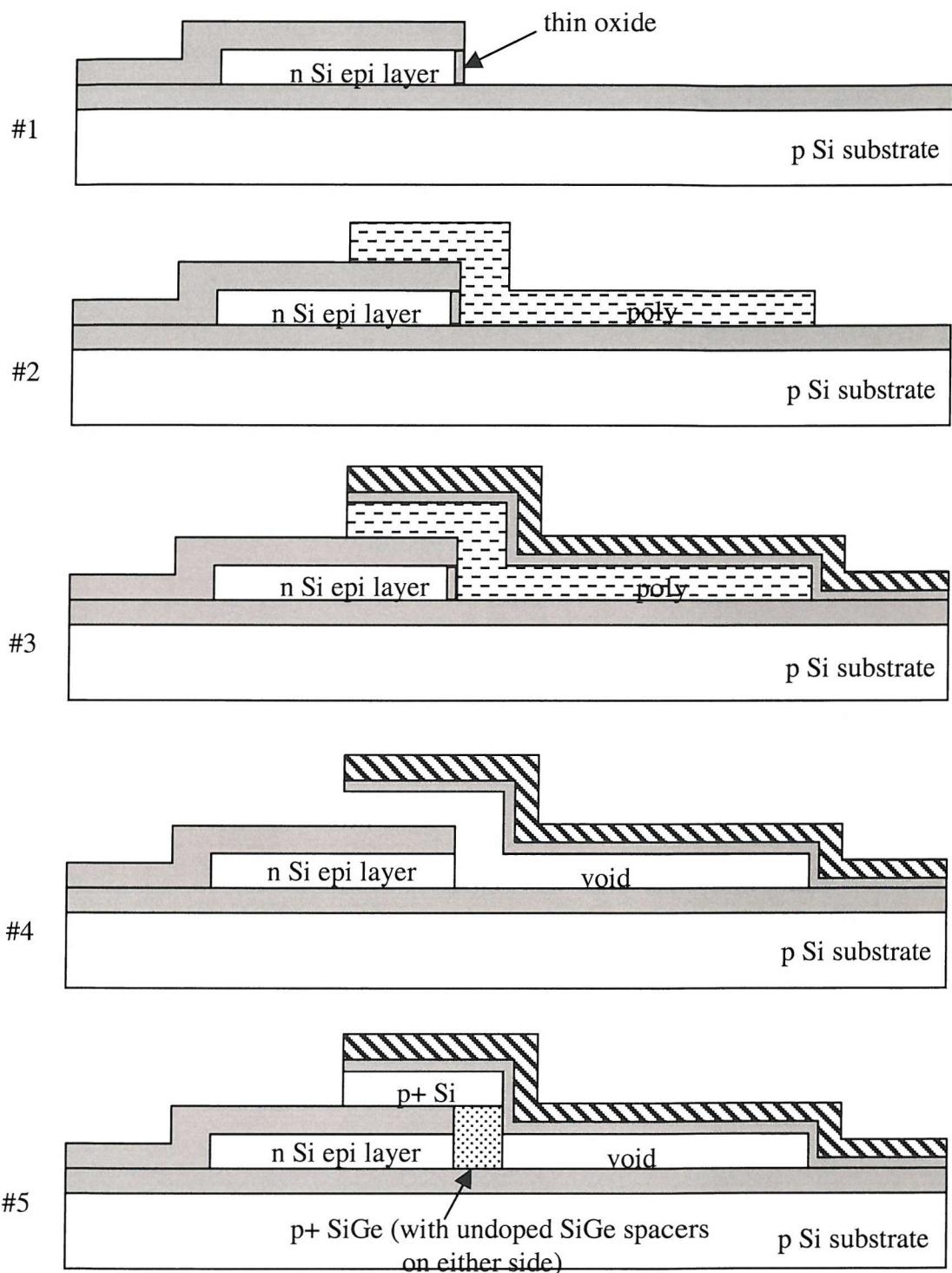

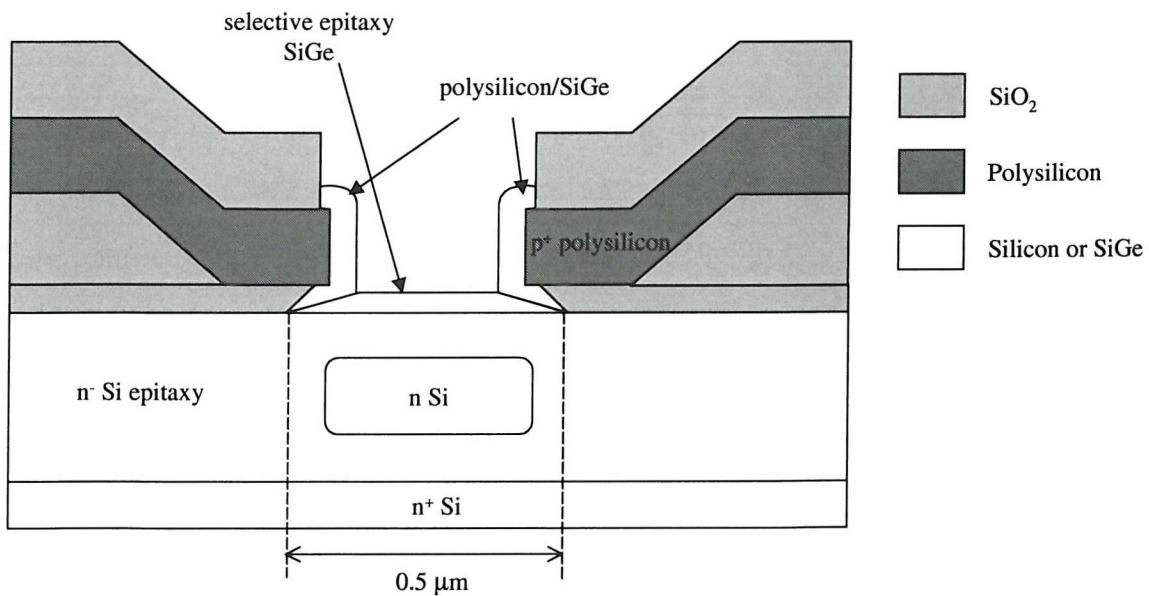

| 6.1  | First page of figures illustrating the process flow of the Lateral SiGe HBT. . . . .                                                                                                                                                                                                                                      | 97 |

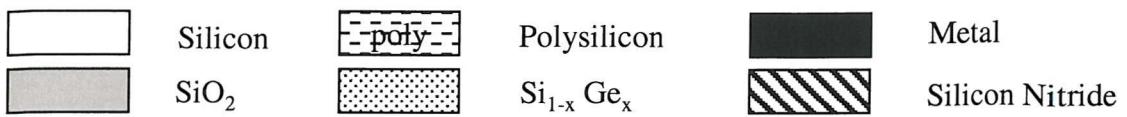

| 6.2  | Second page of figures illustrating the process flow of the Lateral SiGe HBT. . . . .                                                                                                                                                                                                                                     | 98 |

|                                                                                                                                                                                                                                                                                                               |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

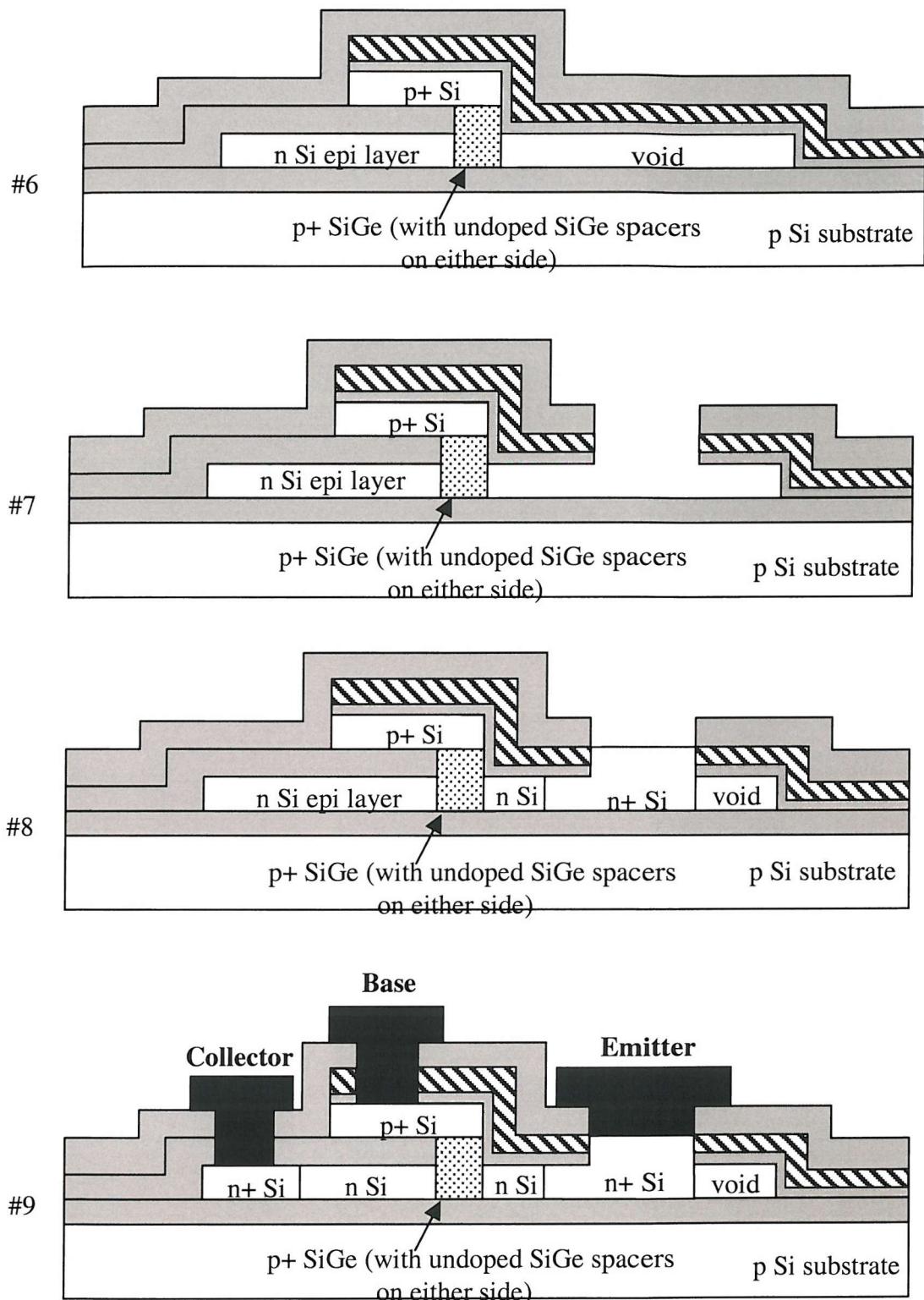

| 6.3 (a) Illustrates how the SiGe base layer is expected to grow from the seed hole. (b) An example of the kind of high performance base structure (with its undoped SiGe spacers $i$ ) that could be potentially possible with this LPCVD growth technique, in order to suppress boron out diffusion. . . . . | 100 |

| 6.4 (a) Base contact structure with base metal contact close to the intrinsic base (active base) region. (b) Base contact structure of the proposed lateral SiGe HBT, with an extrinsic base region to reduce base current. . . . .                                                                           | 101 |

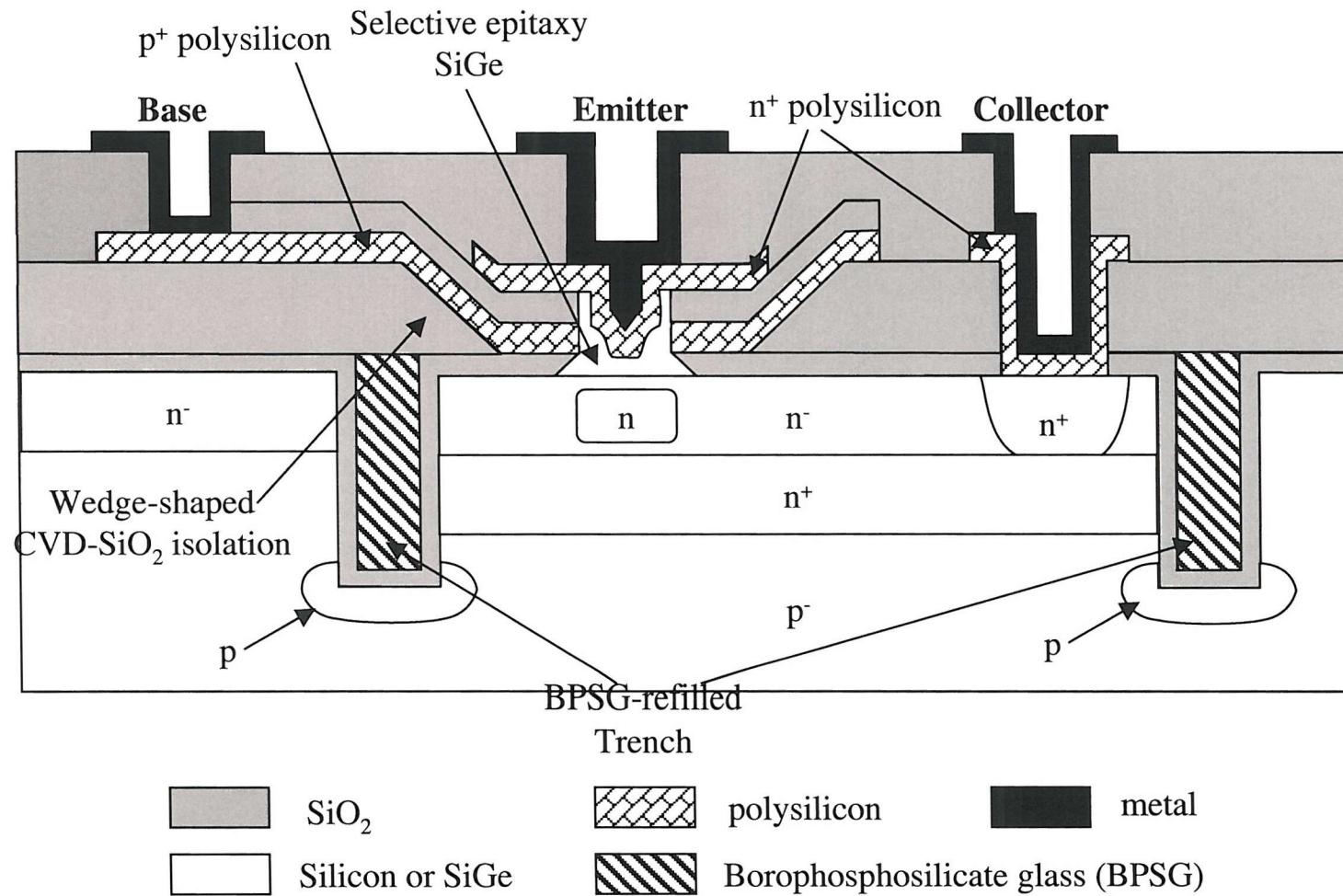

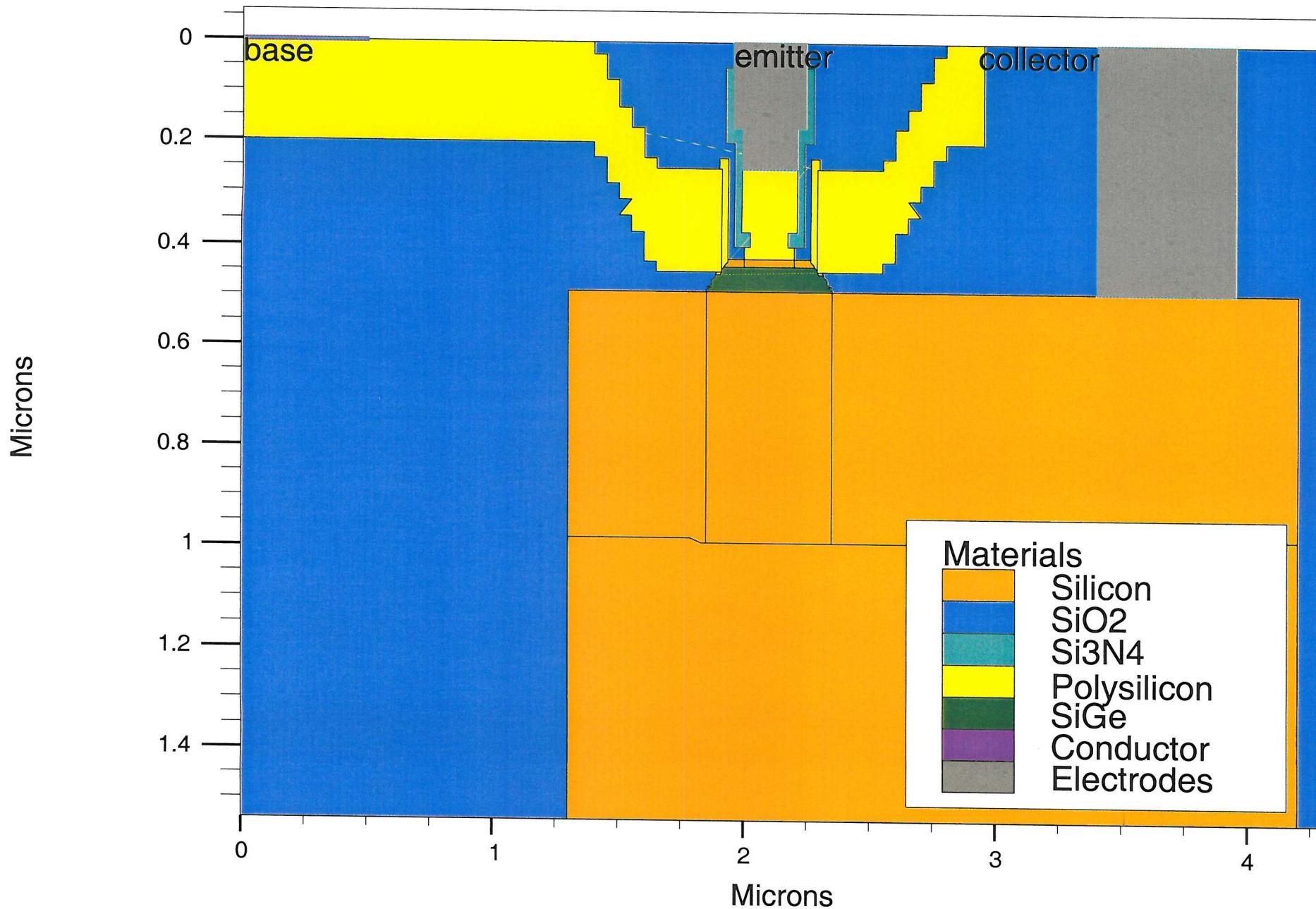

| 6.5 The Kondo's device structure. . . . .                                                                                                                                                                                                                                                                     | 103 |

| 6.6 The simultaneous formation of SiGe base on the $n^-$ collector with the self-aligned polysilicon/SiGe base contact on the $p^+$ polysilicon sidewall. . . . .                                                                                                                                             | 104 |

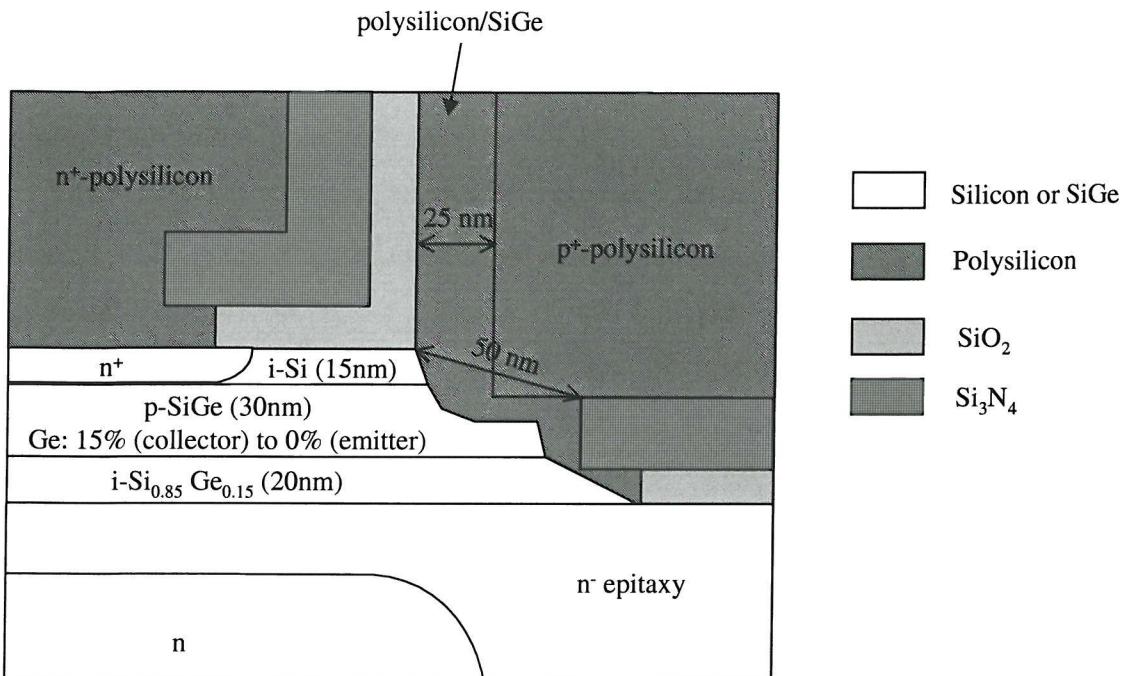

| 6.7 Figure illustrating cross section of the base structure of Kondo's transistor [10]. . . . .                                                                                                                                                                                                               | 105 |

| 6.8 Figure illustrating the SIMS profile of the Kondo device [10]. . . . .                                                                                                                                                                                                                                    | 106 |

| 6.9 Figure shows the doping profile in the published Kondo device and the profile used in the Atlas simulation. . . . .                                                                                                                                                                                       | 107 |

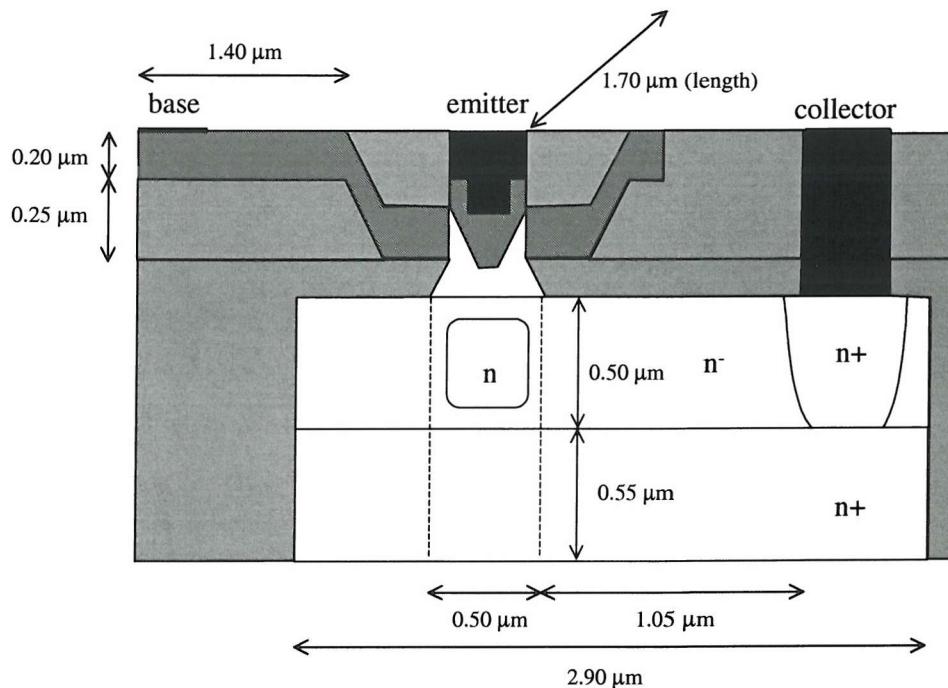

| 6.10 Figure shows the dimension of the Kondo structure used in Atlas. . . . .                                                                                                                                                                                                                                 | 107 |

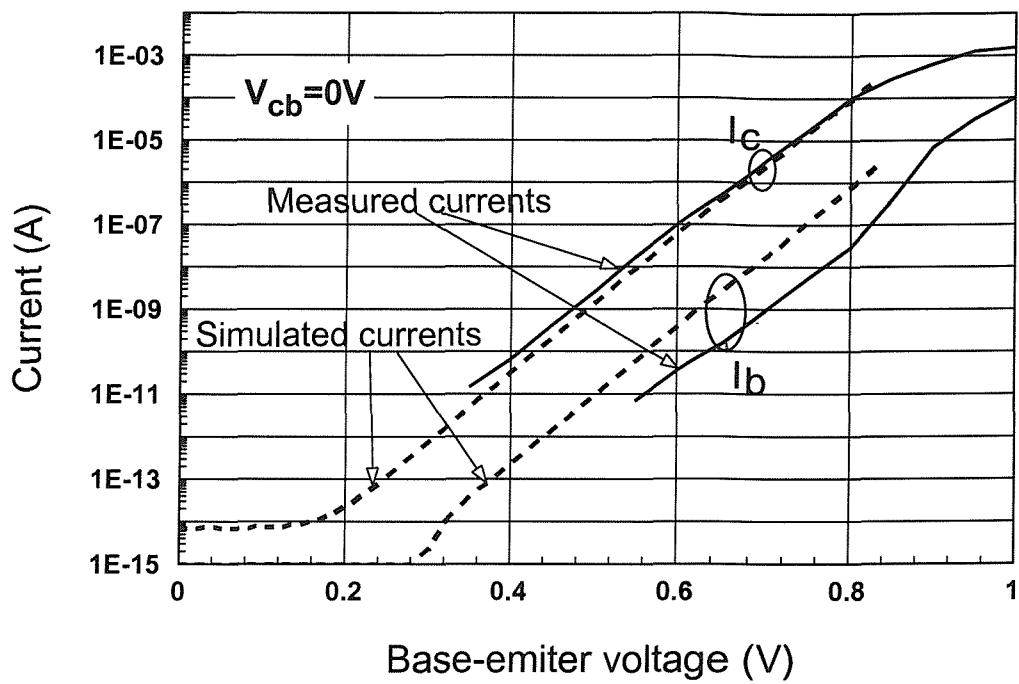

| 6.11 Gummel plot comparing the collector and base current from the published Kondo device with those obtained from simulation. . . . .                                                                                                                                                                        | 108 |

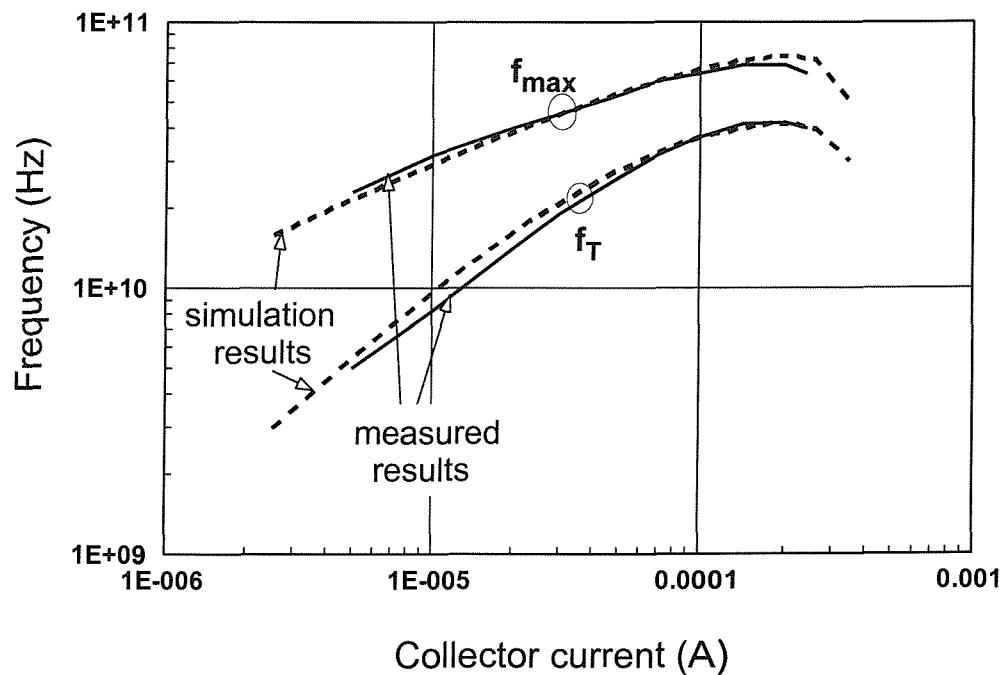

| 6.12 $f_{max}$ and $f_T$ plot with regarding to current from published Kondo device and those from simulation results. . . . .                                                                                                                                                                                | 108 |

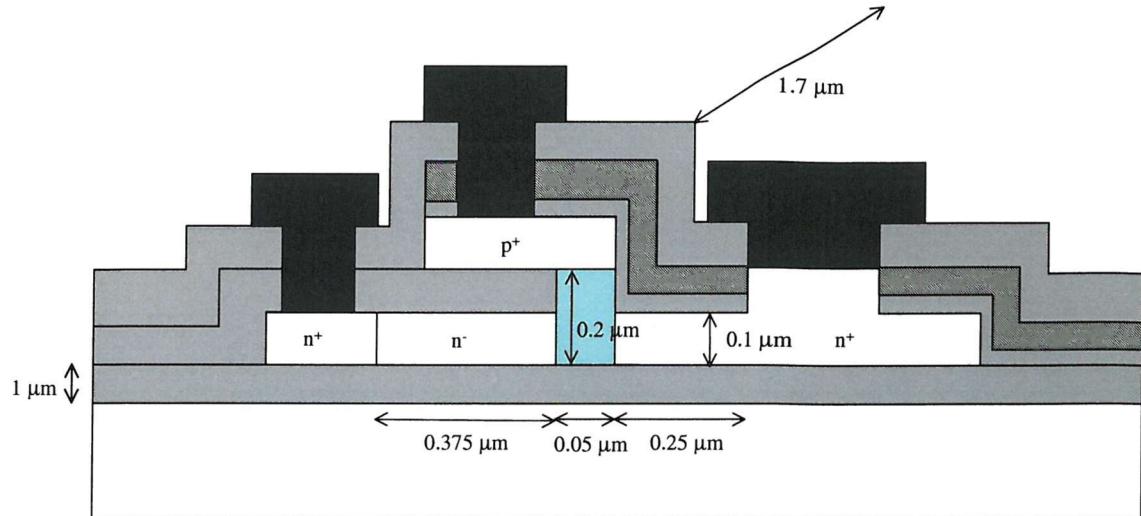

| 6.13 Figure showing the structural dimension of the proposed lateral SiGe HBT used in the Atlas modelling. . . . .                                                                                                                                                                                            | 111 |

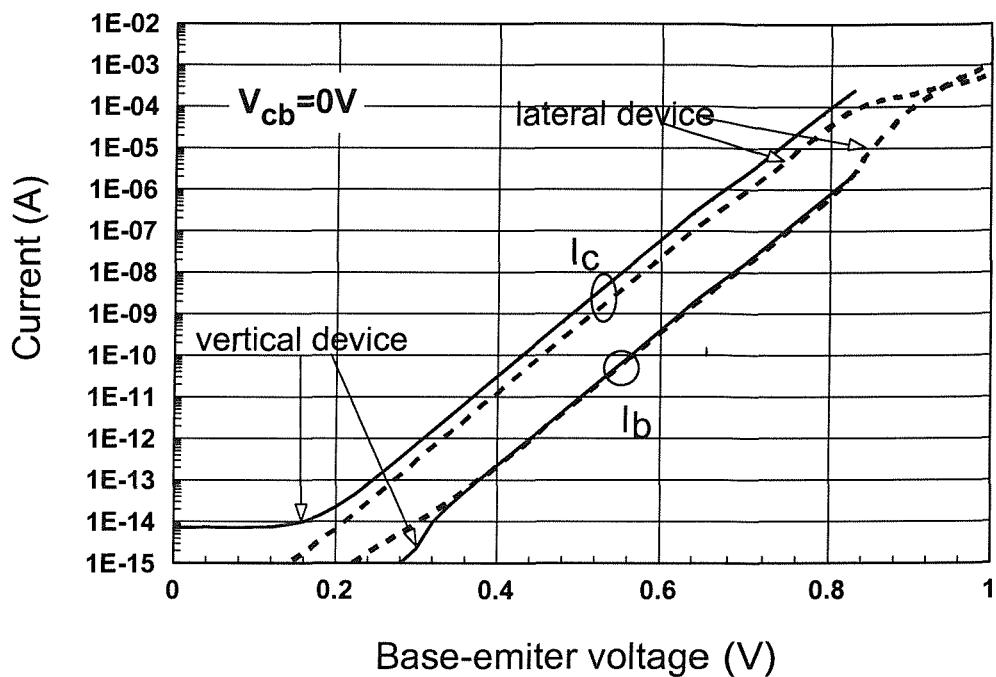

| 6.14 The gummel plots from the Atlas modelling of the lateral and vertical device. . . . .                                                                                                                                                                                                                    | 112 |

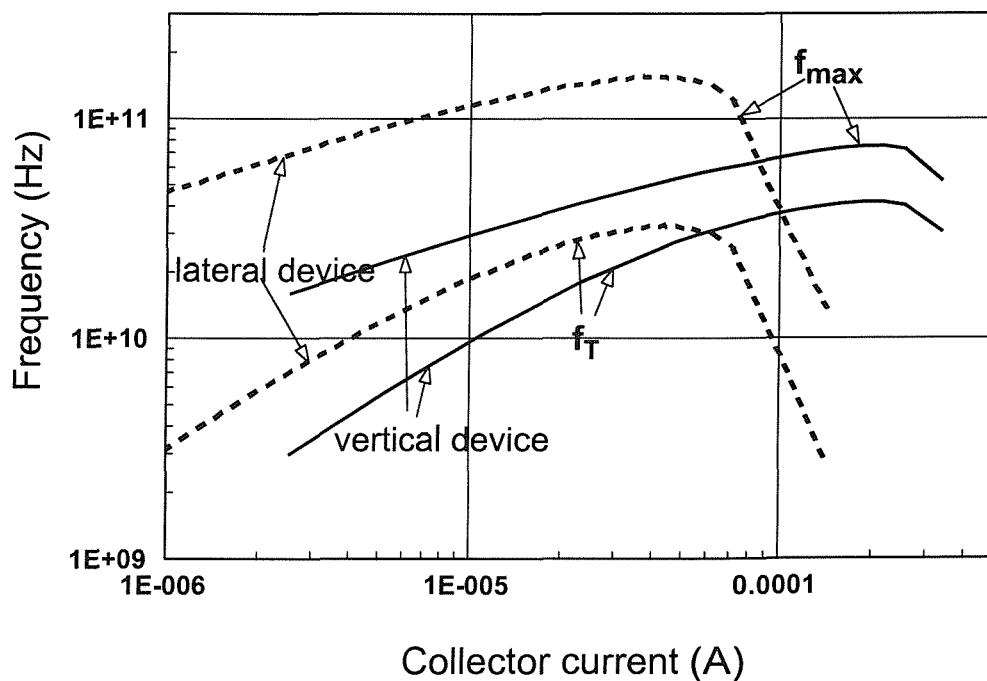

| 6.15 The $f_T$ and $f_{max}$ vs collector current plots from Atlas modelling of the lateral and vertical device. . . . .                                                                                                                                                                                      | 112 |

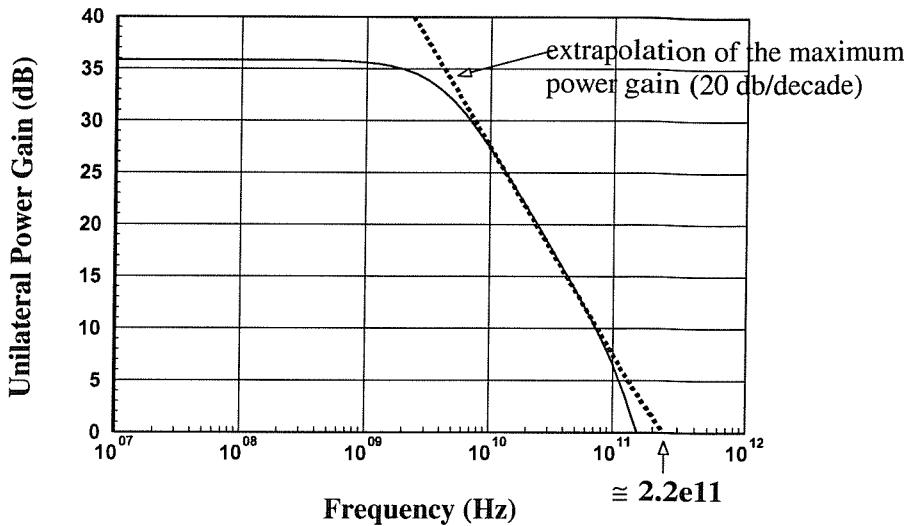

| 6.16 The extrapolated $f_{max}$ of the lateral device is found to be approximately 220 GHz. This is consistence with the first order approximation of $f_{max}$ using Equation 6.8. . . . .                                                                                                                   | 114 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| B.1 | Circuit diagram of an n-p-n transistor illustrating the bias condition and the current flow when the transistor is biased at the (a) forward active region of operation, and (b) reverse active region of operation.                                                                                                                                                                                                                                               | 122 |

| B.2 | Figure illustrating the difference of the neutral base position in the forward active region mode and reverse active region mode. For a highly doped base, which is common for a SiGe HBT, the position of $0_r$ can be made very close to the position of $0_f$ for low emitter/base junction reverse bias, in reverse active operation, because most of the space-charge layer movement will take place in the lower-doped emitter side of the junction. . . . . | 123 |

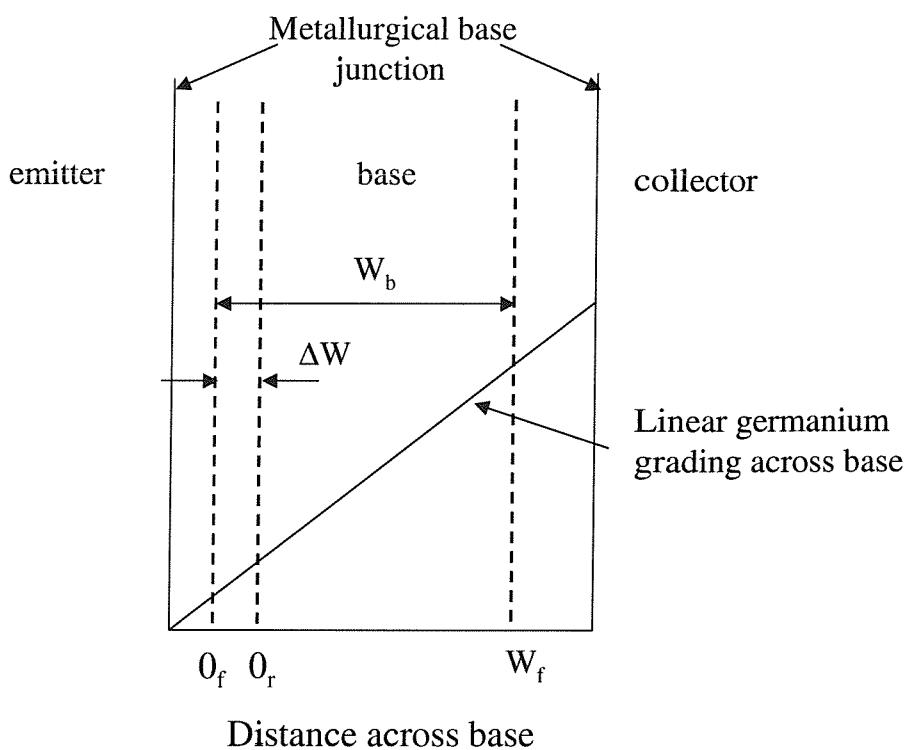

| C.1 | Figure showing difference between the emitter-base electrical junction positions for forward bias, $0_f$ , and zero reverse bias, $0_r$ . It was assumed to be similar in the neutral base bandgap difference extraction method and it is found that the error can be approximated by $\Delta W/W_b$ . . . .                                                                                                                                                       | 127 |

| D.1 | The Kondo device structure generated by input file. . . . .                                                                                                                                                                                                                                                                                                                                                                                                        | 141 |

| D.2 | The proposed lateral device structure generated by input file. . . . .                                                                                                                                                                                                                                                                                                                                                                                             | 146 |

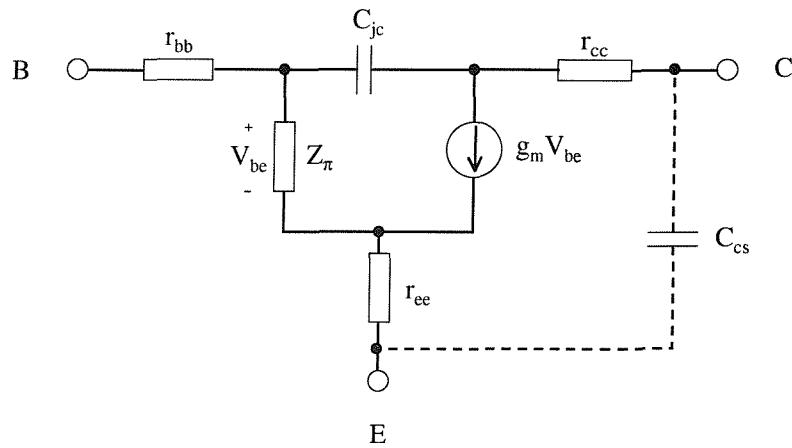

| E.1 | Small signal hybrid- $\pi$ model representation of bipolar transistor. . . .                                                                                                                                                                                                                                                                                                                                                                                       | 147 |

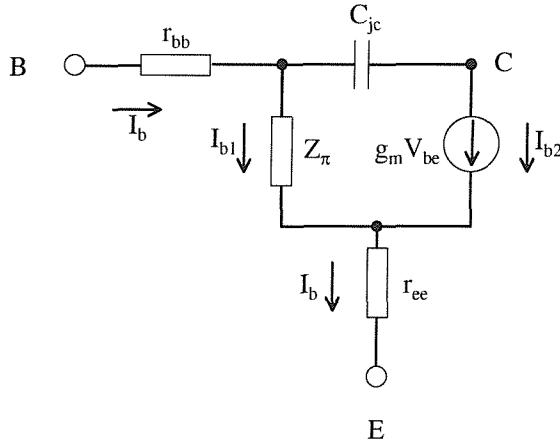

| E.2 | Bipolar transistor's hybrid- $\pi$ equivalent model for zero collector current (i.e. $I_c = 0V$ ) . . . . .                                                                                                                                                                                                                                                                                                                                                        | 148 |

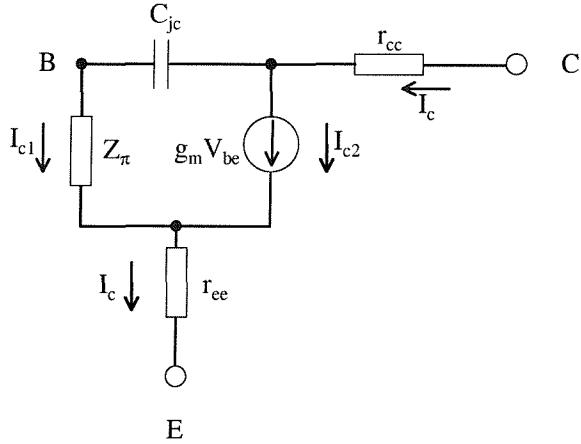

| E.3 | Bipolar transistor's hybrid- $\pi$ equivalent model for zero base current (i.e. $I_b = 0V$ ) . . . . .                                                                                                                                                                                                                                                                                                                                                             | 149 |

# Acknowledgement

First of all, I thank my Lord Jesus Christ for making all this possible for me.

I would like to thank my family for their trust, support and patience with me for the last 3 years.

A special acknowledgement must go to my supervisor Dr. John Hamel for his valuable guidance and support in every part of this work. His enthusiasm and readiness to help is something I will always appreciate.

Thanks must also go to Prof. Peter Ashburn for providing the SiGe HBT devices for this work.

I will like to express my gratitude to all my fellow researchers in the microelectronic group for their friendliness and many football games. It is good fun to work in a relaxing environment. Many thanks to all the clean room staff for their help and advice. And the microelectronics group secretaries, nothing will go smoothly without you all.

Finally, my brothers and sisters in church, your support and prayers kept me going. Thank you very much.

Yue Teng, Tang

# List of Symbols

|                            |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| $0_f$                      | Emitter side of neutral base in forward active mode                        |

| $0_r$                      | Emitter side of neutral base in reverse active mode                        |

| $A_c$                      | Collector-base junction area                                               |

| $A_e$                      | Emitter-base junction area                                                 |

| $\beta$                    | Common emitter current gain                                                |

| $\beta_{ac}$               | a.c. common emitter current gain                                           |

| $BV_{CEO}$                 | Breakdown voltage between the emitter and collector with base open circuit |

| $C_\pi$                    | Collector-base capacitance in small-signal hybrid- $\pi$ model             |

| $C_{cs}$                   | Collector-substrate capacitance                                            |

| $C_{jc}$                   | Collector-base depletion capacitance                                       |

| $C_{je}$                   | Emitter-base depletion capacitance                                         |

| $D_n$                      | Electron diffusion coefficient                                             |

| $D_{nb}$                   | Electron diffusion coefficient in base                                     |

| $\epsilon$                 | Dielectric permittivity                                                    |

| $\epsilon_s$               | Permitivity of silicon                                                     |

| $E_c$                      | Conduction band energy                                                     |

| $\Delta E_c$               | Parasitic potential barrier height                                         |

| $\delta E_c$               | Conduction band discontinuity                                              |

| $E_g$                      | Bandgap energy                                                             |

| $\Delta E_g$               | Bandgap narrowing                                                          |

| $\Delta E_g(\text{grade})$ | Bandgap grading across the neutral base                                    |

| $\Delta E_g^{\text{app}}$  | Apparent bandgap narrowing due to heavy doping effect                      |

| $\Delta E_g^{e-b}$         | Bandgap difference between emitter and base                                |

| $E_F$                      | Fermi level                                                                |

| $E_{Fn}$                   | Electron quasi-fermi level                                                 |

| $E_{Fp}$                   | Hole quasi-fermi level                                                     |

| $E_v$                      | Valence band energy                                                        |

| $\Delta E_v$               | Valence band variation across a parasitic potential barrier width          |

| $\delta E_v$               | Valence band discontinuity                                                 |

| $f_{max}$                  | Unity power gain frequency                                                 |

| $f_T$                      | Cut-off frequency                                                          |

| $f_T^{\max}$               | Peak cut-off frequency                                                     |

| $g_m$                      | Transconductance                                                           |

| $g_{of}$                   | Output conductance in forward active mode                                  |

| $g_{or}$                   | Output conductance in reverse active mode                                  |

|          |                                                                |

|----------|----------------------------------------------------------------|

| $G_b$    | Base Gummel number                                             |

| $G_n$    | Electron generation rate                                       |

| $G_p$    | Hole generation rate                                           |

| $h$      | Planck's constant                                              |

| $h_{FE}$ | Common emitter current gain                                    |

| $I_b$    | Base current                                                   |

| $I_c$    | Collector current                                              |

| $I_{cf}$ | Collector current in forward active mode                       |

| $I_{cr}$ | Collector current in reverse active mode                       |

| $J_c$    | Collector current density                                      |

| $J_n$    | Electron current density                                       |

| $J_p$    | Hole current density                                           |

| $k$      | Boltzmann's constant                                           |

| $\mu_n$  | Electron mobility                                              |

| $\mu_p$  | Hole mobility                                                  |

| $m_e$    | Electron effective mass                                        |

| $m_h$    | Hole effective mass                                            |

| $n$      | Electron concentration                                         |

| $n_{ib}$ | Effective intrinsic carrier concentration in base              |

| $n_{ie}$ | Effective intrinsic carrier concentration                      |

| $n_{io}$ | Intrinsic carrier concentration                                |

| $n_p$    | Electron concentration in p-type                               |

| $N_b$    | Base doping concentration                                      |

| $N_c$    | Effective density of states in the conduction band             |

| $N_e$    | Emitter doping concentration                                   |

| $N_v$    | Effective density of states in the valence band                |

| $N_A$    | Acceptor concentration                                         |

| $N_D$    | Donor concentration                                            |

| $\rho_s$ | Surface charge density                                         |

| $p$      | Hole concentration                                             |

| $q$      | Charge of an electron                                          |

| $Q_b$    | Total stored charge in base                                    |

| $r_\pi$  | Effective input resistance in small-signal hybrid- $\pi$ model |

| $r_{bb}$ | Base resistance in small-signal hybrid- $\pi$ model            |

| $r_{cc}$ | Collector resistance in small-signal hybrid- $\pi$ model       |

| $r_{ee}$ | Emitter resistance in small-signal hybrid- $\pi$ model         |

|              |                                                                     |

|--------------|---------------------------------------------------------------------|

| $R_b$        | Base resistance                                                     |

| $R_c$        | Collector resistance                                                |

| $R_e$        | Emitter resistance                                                  |

| $R_n$        | Electron recombination rate                                         |

| $R_p$        | Hole recombination rate                                             |

| <br>         |                                                                     |

| $\tau_b$     | Base transit time                                                   |

| $\tau'_c$    | Collector charging time                                             |

| $\tau_{cbd}$ | Collector-base depletion region transit time                        |

| $\tau_e$     | Emitter delay                                                       |

| $\tau_{ebd}$ | Emitter-base depletion region delay                                 |

| $\tau_{ec}$  | Total delay across the bipolar transistor from emitter to collector |

| $\tau_{je}$  | Total emitter depletion layer charging time                         |

| $\tau_n$     | Electron lifetime                                                   |

| $\tau_p$     | Hole lifetime                                                       |

| $T$          | Absolute temperature                                                |

| <br>         |                                                                     |

| $\phi_c$     | Potential increase in depletion region in hybrid mode bipolar       |

| $\psi$       | Electrostatic potential                                             |

| $\Psi_n$     | Electron injection barrier                                          |

| $\Psi_p$     | Hole injection barrier                                              |

| <br>         |                                                                     |

| $V_b$        | Base voltage                                                        |

| $V_{bc}^r$   | Base-collector voltage at reverse active mode                       |

| $V_{be}$     | Base-emitter voltage                                                |

| $V_{be}^f$   | Base-emitter voltage at forward active mode                         |

| $V_{bi}$     | Build in voltage                                                    |

| $V_c$        | Collector voltage                                                   |

| $V_{cb}$     | Collector-base voltage                                              |

| $V_{cb}^f$   | Collector-base voltage at forward active mode                       |

| $V_{dd}$     | Power supply voltage                                                |

| $V_{eb}^r$   | Emitter-base voltage at reverse active mode                         |

| $v_{scl}$    | Scattering limited velocity                                         |

| $V_A$        | Early voltage                                                       |

| $V_T$        | Thermal voltage                                                     |

| <br>         |                                                                     |

| $W$          | Width                                                               |

| $W_b$        | Neutral base width                                                  |

| $\Delta W_b$ | Parasitic potential barrier width                                   |

| $W_f$        | Collector side of neutral base for forward active mode              |

| $W_{jc}$     | Collector-base depletion layer width                                |

| $W_{je}$     | Emitter-base depletion layer width                                  |

| $W_r$        | Emitter side of neutral base for reverse active mode                |

# Chapter 1

## Introduction

The studies into Heterojunction Bipolar transistor (HBT) technology have been intensified enormously for the past 10 years as homojunction technology (mainly silicon) is moving closer to the predicted limit of its capability. It has attracted much attention because of both the device performance and the low cost for many applications such as over 10-*Gb/s* optical communication systems, LAN, and wireless communication system [1]. Advancement in silicon germanium (SiGe) technology, demonstrated by producing various high performance devices, has proved that SiGe HBT has the potential to be the future silicon-based bipolar technology, taking over from the currently dominant silicon technology. Schuppen *et al.* [2] have fabricated double-mesa type SiGe heterojunction bipolar transistors using MBE where it is possible to obtain a record maximum frequency of oscillation up to 160 *GHz* for a 2-emitter finger HBT in common emitter configuration. By employing Ultra High Vacuum/Chemical Vapour Deposition (UHV/CVD) system, Oda *et al.* [3] have achieved cut-off frequency up to 130 GHz and current gain up to 29,000 with graded and uniform germanium profiles, respectively. For IC applications, Strohm *et al.* [4] have fabricated a SiGe MMIC amplifier delivering gain up to 4 *dB* at 26 *GHz*. In fact, SiGe HBTs were successfully implemented in a 16 Gb/s multiplexer IC [5] and also in ICs (including selector, multiplier, D flip-flop) for a 20 Gb/s optical transmitter [6]. For analogue applications, Harame *et al.* [7] have fabricated a 12-bit D/A converter with SiGe HBT devices in an 8 inch wafer manufacturing line. Also, beta-Early voltage product ( $\beta V_A$ ), a key property for analogue devices which measures the quality of the current source, of an

impressive 48,000 was reported in [1] for SiGe transistor. Referring to [1], the SiGe heterojunction transistor is fast enough to replace gallium arsenide in many commercial applications, including digital cellular telephones and wireless LANs. Most importantly, it can be made, with modest increase in processing complexity, on existing process lines. Also, it may be integrated with conventional circuits such as sub-micron VLSI CMOS to form SiGe HBT Bipolar/BiCMOS process. SiGe HBT Bipolar/BiCMOS technology has a unique opportunity in the wireless marketplace because it can provide the performance of III-V HBTs and the integration/cost benefits of silicon bipolar/BiCMOS [7, 8].

The introduction of germanium into the base of silicon bipolar transistor, thereby forming a strained SiGe layer, alters the physical properties of the transistor and enhances the performance of the bipolar transistor tremendously. Germanium has smaller bandgap compared to silicon, thereby reduces the base bandgap in a SiGe base. By using strained SiGe layer in the base to induce bandgap narrowing, heterojunctions are formed at the collector-base junction and the emitter-base junction of the transistor. The reduction of base bandgap results in the lowering of the electron injection barrier from emitter into base. This increases electron injection into base and therefore causes the increase of collector current and hence current gain. As current gain increases, higher base doping can be used without destroying the current gain. High base doping allows the use of thinner base to reduce the forward transit time without compromising the base resistance or fearing that the base will be ‘punched through’ by depletion region penetration across the base, due to a reverse collector-base bias. It also increases the device output resistance by allowing less depletion region penetration per unit of collector-base applied voltage. Reducing forward transit time improves the high frequency performance of device by increasing the cut-off frequency. Therefore, it is possible to engineer the base bandgap according to the purpose of the transistor. This is known as bandgap engineering where the base bandgap can be adjusted according to the germanium profile and the amount of germanium introduced.

One popular method of base bandgap engineering is to grade the bandgap across the base [8]-[12]. Bandgap grading introduced into the base region of a SiGe HBT

induces a drift field which aids minority carrier transport by accelerating the injected minority carriers as they traverse the base, resulting in lower base transit time. In short, the base bandgap of SiGe HBT can be engineered to enhance device performance, thereby making it suitable for a wide range of high-speed analogue and RF applications.

As device modelling is an essential part of device or circuit designing, it is necessary for new parameters which characterise the behaviour of SiGe HBT to be extracted in order to be included in the physical model. In Chapter 4 of this thesis, a new electrical method is developed to measure the bandgap difference across the neutral base of a SiGe HBT. The base bandgap profile controls the flow of minority carriers and the difference of bandgap across the neutral base determines several other important properties of the transistor including output conductance and base transit time. However, determining the actual bandgap difference across the neutral base can be a complicated matter because, other than the effect of germanium, the base bandgap is also affected by other physical properties such as heavy doping effect. There is no currently existing electrical method that directly measures the bandgap difference across the neutral base. Useful information regarding the impact of germanium on device performance in a SiGe HBT is obtained [13, 14] through comparison with a silicon device that does not contain germanium. However, these methods require the processing of a separate set of silicon devices that have similar doping profile as the SiGe devices. Also, they rely on physical information of silicon and SiGe such as mobility, effective masses and so on. Physical information regarding SiGe is not currently well established and therefore is not always easily available. The proposed new method does not require a silicon control device or rely upon physical information of silicon and SiGe. Using this proposed new method, only the resultant bandgap difference across the neutral base is measured directly from the transistor. Therefore it gives an accurate measurement of the actual bandgap difference across the neutral base inside the transistor. This new method was verified numerically and demonstrated experimentally, and was published in the 1997 Workshop on High Performance Electron Devices for Microwave and Optoelectronic Applications [15]. It has been accepted for publication by the Journal of IEEE Transactions on Electron Devices [16].

In Chapter 5, a new electrical method for extraction of parasitic potential barrier heights of SiGe HBT's is presented. Parasitic energy barriers, which do not generally exist in homojunction silicon bipolar transistor, are found to exist in SiGe HBT [17]-[19], if boron is allowed to out-diffuse beyond the SiGe layer boundaries during fabrication of a double heterojunction SiGe HBT. As a result, boron dopant, which defines the transistor's base, is found in the adjacent collector and emitter silicon regions. Since silicon has larger bandgap than SiGe, the bandgap near the edges of the neutral base widens up. This bandgap widening manifests itself as a parasitic energy barrier at both the emitter-base and collector-base junctions. These barriers can have an adverse effect on the SiGe HBT performance. Slotboom *et al.* [20] have shown that the barriers can severely degrade the collector current and cut-off frequency of the device. One way to estimate these parasitic barrier heights has been proposed by Le Tron *et al.* [21] through analysing the temperature dependence of the collector current. This method relies on accurate modelling of the temperature dependence of the silicon and SiGe density of states and carrier mobility. It also requires a control device, a SiGe HBT device (without any parasitic barriers). It requires the same doping profile as the SiGe HBT with parasitic barriers. Here, as shown in Chapter 5, the Le Tron *et al.* method is refined by using the temperature dependence of the ratio of the small signal a.c. output conductance in forward and reverse active operation. This new method is able to simultaneously extract the parasitic potential barrier heights at emitter-base and collector-base junctions of a SiGe HBT. The method is capable of independently determining the height of each barrier without the need for comparison to control devices or a knowledge of the temperature dependence of internal physical properties such as the density of states and carrier mobility. This new method was verified numerically and demonstrated experimentally, and was published in the 28th European Solid-State Device Research Conference [22]. It is to be submitted to the Journal of IEEE Transactions on Electron Devices [23].

Most existing high speed and low power bipolar transistors , suitable for a wide range of high speed analogue and RF applications, make use of the vertical bipolar structure [2, 10, 12]. A narrow base, which is essential for high speed SiGe HBT, can

be grown epitaxially in a vertical bipolar structure using UHV/CVD or Molecular Beam Epitaxy (MBE) [3], [24]-[27]. Especially the approaches using selective epitaxy of the base have proven successful since a record cut-off frequency of  $130\text{GHz}$  [3],  $f_{max}$  of  $107\text{ GHz}$  and ECL gate delay of  $6.7\text{ ps}$  [28], and CML gate delay of  $11\text{ps}$  [26] were achieved with this approach. However, the basic vertical structure has some weaknesses. Its main disadvantage lies on the fact that its whole structural alignment (emitter-base-collector) is buried vertically into the silicon substrate. This means that only the emitter can be conveniently contacted from the silicon surface. Self-aligned polysilicon contact and highly doped epitaxial buried layer are therefore required in order to connect the base and collector, respectively, from the silicon surface. This increases the device terminal resistances and capacitances significantly. In many instances, extra processing steps need to be implemented in order to reduce these resistances and capacitances.

The advancement of photolithography process has created an upsurge of interest in lateral bipolar transistors [29]-[31]. Deep sub-micron lithography processes have made possible the production of a thin lateral base down to approximately  $0.1\text{ }\mu\text{m}$ . Before this, lateral bipolar transistors have always been handicapped by a wide base structure. With a thin base, high speed lateral bipolar transistors can be realised. In comparison to a vertical structure, the base lateral structure has the advantage of easy accessibility to the base and collector regions from the silicon surface as its emitter-base-collector are aligned parallel to the silicon surface. Also it is more compatible with existing Thin Film Silicon-on Insulator (TFSOI) CMOS technology where epi thickness is about  $0.1\text{ }\mu\text{m}$  [32]. Therefore, it becomes a strong candidate for integrated Bipolar CMOS (BiCMOS) process [32], which is highly versatile and especially suitable for low power, low noise and high performance analogue circuits such as RF amplifiers, filters and mixers in wireless communication systems. In Chapter 3, various issues regarding lateral bipolar structures are discussed. The discussion is focused on evaluating the potential of the lateral SiGe device structure for high speed and low power applications. A new mode of lateral bipolar transistor operation, known as the hybrid mode [33], is also discussed. If the hybrid lateral bipolar transistor is designed correctly, it is able to induce virtual heterojunction