Received 30 August 2022; accepted 19 September 2022. Date of publication 26 September 2022; date of current version 12 October 2022. The review of this article was arranged by Associate Editor Zhixiang Zou.

Digital Object Identifier 10.1109/OJPEL.2022.3209540

# A Generalized Phase-Shift PWM Extension for Improved Natural and Active Balancing of Flying Capacitor Multilevel Inverters

GEORGIOS KAMPITSIS <sup>1</sup> (Member, IEEE), EFSTRATIOS I. BATZELIS <sup>2</sup> (Senior Member, IEEE), ANTONIS KOLOKASIS <sup>1</sup> (Member, IEEE), ELISON MATIOLI <sup>3</sup> (Senior Member, IEEE), AND BIKASH C. PAL <sup>1</sup> (Fellow, IEEE)

<sup>1</sup>Department of Electrical and Electronic Engineering, Imperial College London, London SW7 2AZ, U.K.

<sup>2</sup>School of Electronics and Computer Science, University of Southampton, Southampton SO17 1BJ, U.K.

<sup>3</sup>Power and Wide Bandgap Electronics Research Laboratory, École Polytechnique Fédérale de Lausanne, 1015 Lausanne, Switzerland

${\tt CORRESPONDING\ AUTHOR:\ GEORGIOS\ KAMPITSIS\ (e-mail:\ g. kampits is @imperial.ac.uk)}$

The work of Georgios Kampitsis was supported by the European Union's Horizon 2020 Research and Innovation Program under the Marie Sklodowska-Curie Grant Agreement 891035. The work of Efstratios Batzelis was supported by the Royal Academy of Engineering through the Engineering for Development Research Fellowship Scheme under Grant RF\201819\18\86. The work of Bikash C. Pal was supported by the Resilient Operation of Sustainable Energy Systems (ROSES) U.K.-China (EPSRCNSFC) Programme on Sustainable Energy Supply under Grants EP\(T\)021713\(T\)1 and NSFC-52061635102.

ABSTRACT The emergence of wide bandgap power devices has brought the attention back to the flying capacitor (FC) multilevel inverters with a large number of stages, in an effort to increase the power density by minimizing the passive components. The main challenge that such systems face, particularly the ones based on high-frequency Gallium-Nitride devices and small-value ceramic capacitors, relate to the stringent requirements for precise and fast capacitor balancing. Conventional *natural balancing* techniques exhibit poor settling times, while most improved natural balancing methods are not easily scalable to more than five levels. The alternative of *active balancing* normally requires one isolated sensor per FC which increases the overall system cost and footprint, or a single ac-side sensor that is more compact but calls for sophisticated PWMs that again are not available for multiple levels. In this paper we introduce a generalized pulse width modulation (PWM) strategy based on the phase-shift and carrier swapping principles for an arbitrary number of levels. We provide an easy and intuitive method for the extraction of the PWM pattern, the switching states, and their sequence. Simulations were carried out in Matlab/Simulink and experimental tests were conducted on a single-phase 7-level GaN inverter prototype. Not only is the extended PWM advantageous in natural balancing, but it also provides the right zero switching states for ac-side FC sensing in active balancing.

**INDEX TERMS** Active balancing, flying capacitor, gallium nitride, multilevel inverters, natural balancing, pulse width modulation, switching states, wide band gap semiconductors.

#### I. INTRODUCTION

In recent years, there has been an increasing number of power transfer applications that pose strict volume and weight constrains on the energy conversion systems. The most demanding applications are found in the transportation sector, including electric and hybrid aircraft propulsion systems [1], [2] and electric vehicle charges [3]. Stationary applications, such as PV generators [4], power factor correction (PFC) systems [5] and various medium voltage applications [6] also benefit from more compact and lightweight converters, as this is translated to lower installation cost.

A potential answer to this need can be provided by wide bandgap (WBG) power semiconductors in multilevel inverter (MLI) topologies. The high switching frequency capabilities of these devices (in the hundreds of kHz to a few MHz range) allow the minimization, even elimination, of the magnetic components and the replacement of electrolytic capacitors with lightweight and reliable ceramic capacitors [7]. Moreover, the overall efficiency and power density gain brings a further reduction to the physical dimensions of the cooling system [8].

Miniaturized multilevel converters have lately gained more attention with advancements on the monolithic integration of several Gallium Nitride devices on a single chip, as has been demonstrated in [9], [10], [11]. The flying capacitor (FC) inverter with a large number of stages is the most appropriate topology for such applications, due to the high energy density of ceramic capacitors, the absence of clamping diodes and the requirement for a single input DC source. Authors of [3] and [5] have demonstrated 7-level FC inverters for PFC and PV applications and have competed in the Google/IEEE Little box challenge for the world's smallest 2 kW grid connected converter. Further, a 9-level and a 13-level GaN-based FC MLIs were designed and developed in [2] and [4], respectively, that have demonstrated record-braking power densities for aviation and renewable energy applications. Another reason for the increased attention to the GaN-based FC topologies is the limited breakdown voltage capabilities of the GaN transistors. More specifically, state-of-the-art GaN devices are typically characterized by low to medium voltage capabilities (200 to 600 V breakdown), hence the series connection of FC topology and its voltage sharing properties prove to be beneficial for utilizing GaN transistors.

However, as the total inverter capacitance gets lower with miniaturization, regulating the FC voltage becomes more challenging. Internal non-idealities, such as the transistors' voltage drop and timing mismatches, caused by the dead-time and the drivers' propagation delay [12], [13], may cause the FC to drift from their nominal voltage. Additionally, external conditions, such as load disturbances [21], [22] or input source nonidealities [23] may also lead to FC voltage drift. Such nonnominal FC voltage variations need to be contained quickly to avoid operation of the transistors in non-rated conditions and the risk of system failure. Therefore, a fast and reliable capacitor balancing technique, either natural (passive) or active, is particularly important for future GaN-based MLIs.

Natural balancing is the most widely used and cost-effective solution and is based on pulse width modulation (PWM) techniques that ensure that the average current of all FC over a fundamental cycle is zero [14]. Among the different PWM strategies, the conventional level-shifted PWM techniques, namely the phase disposition (PD), phase opposition disposition (POD) and alternative phase opposition disposition (APOD), fail to properly balance the FC due to the insufficient number of generated switching state around zero crossing, which we will later prove that is key for optimal natural balancing. In fact, only a single independent state is produced, which is attributed to the inherent structure of these PWM techniques that require a level shift of the carriers only in the Y-axis, thus keeping the two sets of carriers separated at either sides of the reference around zero crossing. On the other hand, the phase shifted PWM (PSPWM) can successfully balance the FC, while maintaining a low implementation cost. However, it exhibits a very slow balancing response in low modulation indices. Authors of [15], [16], [17], [18] introduced modified phase disposition PWMs (MPDPWM) based on discontinuous reference waveforms or multiple trapezoidal-shaped carriers that combine improved natural balancing performance with low output harmonic content. Even though this technique is expandable to any number of levels, N, it generates the same switching states around zero crossing as the PSPWM and is thus characterized by similarly poor natural balancing performance.

To address this problem, a finite state machine executed in cyclical fashion has been proposed in [19]. This methodology is generated by decoding the conventional Phase Disposition (PDPWM) and the Centered Space Vector PWM (CSVPWM) [20], [21] to identify the target voltage level for each phase leg. Although flexible, this approach is not applicable with a common microcontroller unit (MCU), but it rather requires a fast field-programmable gate array (FPGA) device. Additionally, the computational cost needed for calculating the next state might be a limiting factor for high-switching-speed GaN inverters.

A promising alternative proposes the modification of the traditional PSPWM technique (MPSPWM) by swapping a subset of the carrier signals either at their intersecting point [22] or at the lowest carrier level (zero level) [23]. This method leads to optimal utilization of the redundant zero switching states (ZSS), i.e., the states that correspond to zero output voltage, at negligible extra computational cost. Unfortunately, however, the MPSPWM strategy has not been scaled for inverters with more than five levels to this day. As the number of levels increases, the swapping combinations increase exponentially with unpredictable switching sequences and no guarantee for natural balancing. It remains today an unresolved issue to generalize the MPSPWM to an arbitrary number of levels with a clear carrier swapping mechanism and deterministic pulse sequence.

The natural balancing limitations can be overcome by adopting a closed-loop *active balancing* strategy that regulates the FC voltages at the right level regardless of the disturbance. However, most such methods rely on galvanic isolated measurements across each FC [24], [25], [26], [27], [28], thus increasing significantly the total system cost and footprint, especially in MLIs with a large number of stages. Real-time state estimation algorithms have been proposed in [13], [29], [30], [31], which require the knowledge of just the inverter output current, but are characterized by high computational burden and low response speed, rendering them not-applicable in fast GaN-based MLIs.

A viable alternative for accurate FC measurements with minimum component count adopts the concept of *ac-side monitoring*, which involves sampling the inverter output voltage at specific switching states and extracting the FC voltages from these measurements [32], [33], [34], [35]. Particularly, we have demonstrated in [32] increased measurement bandwidth and accuracy by combining the MPSPWM of [22] with a bidirectional clamping circuit, making the approach ideal for high-frequency GaN MLIs. Yet, this measurement method requires the production of all ZSS from the PWM, which is feasible for up to 5-level inverters with MPSPWM. It is therefore apparent that a generalized PWM strategy with maximum

utilization of the redundant switching states is equally favorable for both natural and active balancing, and such a PWM for more than 5 levels is currently missing from the literature.

In this study, we aim to address this emerging need by extending the MPSPWM to any number of levels. The key contribution is the *derivation of an intuitive and deterministic pattern* for the carrier swapping, applicable to an *arbitrary number of levels*, which allows for generalization of that PWM to what we denote hereinafter as *carrier–swapping PWM* (CSPWM).

We also provide guidelines for the extraction of the generated switching states and their sequence, which lead directly to the system of linear equations to be solved in ac-side monitoring applications, avoiding additional analysis and simulations. The proposed carrier pattern exhibits a series of merits such as switching state symmetry, smooth carriers' transition, implementation simplicity allowing the use of an MCU, and straightforward FC voltage extraction in ac-side monitoring systems.

To the best of the authors knowledge, this is the first time to introduce a generalized PWM strategy for FC MLI that produces the right ZSS and is scalable to any number of levels, thus ensuring optimal natural balancing and allowing application of a fast and precise ac-side voltage monitoring for active balancing.

The rest of the paper is structured as follows: the balancing mechanisms in a FC MLI are discussed in Section II, followed by the proposed CSPWM in Section III. Switching model simulation and results from the analytical approach are given in Section IV. Section V is dedicated to the experimental verification of the extended PWM and Section VI summarizes the concluding remarks.

#### **II. BALANCING MECHANISMS IN FC MLIS**

The goal of this section is to introduce the balancing mechanisms in FC MLIs using a 5-level inverter as a benchmark, demonstrate how the proposed CSPWM is favorable for both natural and active balancing, and explain the extension challenges.

#### A. NATURAL BALANCING

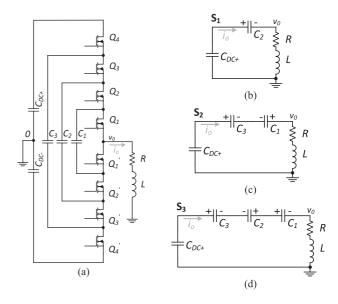

The way that natural balancing PWMs help reduce the FC voltage error is though harmonic current injection over the inverter output load by means of dissipation of the imbalanced energy [36], [37], [38], [39]. The analysis that follows considers a simple R-L load to illustrate the phenomenon (Fig. 1), but parasitic losses (e.g., in the semiconductor devices, eddy currents, high frequency skin effect) further speed-up the balancing process in practice [38].

Well established algorithmic methods based on frequency domain transformation [40], [41], [42] and more recent average-value models in time domain [36], [37] have shown that the FC voltage dynamics under natural balancing contain two exponential decay components: (i) a minor fast component that depends on the load level, and (ii) a dominant slower component that relates to the amplitude modulation index,  $m_a$ .

**FIGURE 1.** (a) Schematic diagram of a single phase 5-level FC inverter feeding an R-L load. (b-d) Equivalent circuits that correspond to the three zero switching states  $S_1$ – $S_3$ .

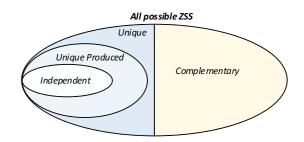

FIGURE 2. Venn diagram describing the classification of the ZSS.

According to [23], the worst-case scenario holds for zero  $m_a$ , when the theoretical natural balancing time constant becomes infinite, as the damping factor and the common mode term tend to zero. Therefore, fast natural balancing under  $m_a = 0$  ensures a satisfying performance for all other operating conditions as well, which indicates that ZSS are of primary importance for any such PWM.

Before we continue with the natural balancing analysis, it is important to introduce a classification of the different ZSS with the help of the Venn diagram in Fig. 2. The number of *all possible* ZSS that can be produced with the switching combinations depends only on the number of levels of the FC inverter and is unrelated to the PWM strategy. These ZSS can be divided into two non-overlapping groups, the *unique* ZSS, involving the conduction of the top-side dc-link capacitor  $C_{DC+}$ , and their *complementary* states, corresponding to the conduction of the low-side  $C_{DC-}$ . A PWM strategy will produce only a subset of the available *unique* ZSS, namely the *unique* produced ZSS. In general, every ZSS involves a combination of FCs which may be different from other ZSSs or may be the same as the synthesis of other ZSSs. Only

**TABLE 1.** Zero Switching States For A 5-Level FC Inverter

| State |     |   |   |   |   |                                                                                                                                      |

|-------|-----|---|---|---|---|--------------------------------------------------------------------------------------------------------------------------------------|

| $S_1$ | (b) | 0 | 0 | 1 | 1 | $v_{DC}/2-v_{C2} = \Delta v_{C2}$                                                                                                    |

| $S_2$ | (c) | 1 | 0 | 0 | 1 | $\begin{array}{rcl} v_{DC}/2 - v_{C2} & = \Delta v_{C2} \\ v_{DC}/2 - v_{C3} + v_{CI} & = \Delta v_{C3} - \Delta v_{CI} \end{array}$ |

|       | (d) | 0 | 1 | 0 | 1 | $v_{DC}/2 - v_{C3} + v_{C2} - v_{C1} = \Delta v_{C3} - \Delta v_{C2} + \Delta v_{C1}$                                                |

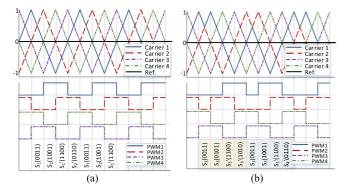

FIGURE 3. Carrier waveforms and respective PWM signals for zero output voltage of a 5-level FC inverter with (a) PSPWM and (b) CSPWM strategies.

a subset of the *unique produced* ZSS involves independent combination of FCs, i.e., the expression of the FCs in the output voltage is different in every ZSS. This group is denoted here as *independent* ZSS and has particular importance, as shown next.

Let us consider the 5-level FC inverter benchmark of Fig. 1. The inverter has six possible ZSS in total, the *unique*  $S_I$ - $S_3$  referring to the top-side dc-link capacitor (see Fig. 1(b)–(d)) and their *complementary*  $S_I'$ – $S_3'$  corresponding to the low-side conduction path. Table 1 shows how the inverter output voltage relates to the FC voltages,  $v_{Ci} = v_{DC} \cdot i/(N-1) - v_{Ci}$  (i = 1, ..., N-2), or more conveniently to the respective voltage deviations from their nominal value  $\Delta v_{Ci}$ . The *complementary* ZZS are omitted in Table 1 for conciseness.

The conventional PSPWM generates only two *unique produced* ZSS ( $S_1$  and  $S_2$ ), according to Fig. 3(a), in the following sequence:  $S_1(0011)$ – $S_2(1001)$ – $S_1'(1100)$ – $S_2'(0110)$ . The corresponding equations (rows 1 and 2 in Table 1) show that  $C_2$  contributes to the output voltage independently (row 1) and hence  $\Delta v_{C2}$  will quickly get to zero. On the other hand,  $C_1$  and  $C_3$  jointly participate in the generation of the output voltage (row 2) that entails that the difference ( $\Delta v_{C3}$ – $\Delta v_{C1}$ ) will converge to zero, but not the individual  $\Delta v_{C3}$  and  $\Delta v_{C1}$ , as explained in [36]. In other words, the three FCs do not get exposed to the output current independently (number of *independent* ZSS < number of FC), which results in suboptimal natural balancing.

On the contrary, the CSPWM generates all *unique* ZSS  $(S_1-S_3)$  as demonstrated in [22] and shown graphically in Fig. 3(b). This method is based on swapping two carriers at their meeting point. In this example, carriers 1 and 2 swap direction when they simultaneously reach the 0.5 mark in every period. A complete switching sequence is now comprised by 8 ZSS:  $S_1(0011)-S_3(1001)-S_1'(1100)-S_3'$

(0101)– $S_1(0011)$ – $S_2(1010)$ – $S_1'(1100)$ – $S_2'(0110)$ . Here, the sets of *unique*, *unique* produced and *independent* ZSS fortunately coincide, and more importantly the number of *independent* ZSS is equal to the number of FC. This means that all FC contribute to the output voltage in an independent manner within two switching cycles, which is translated to fast and symmetrical natural balancing.

An effective mathematical formulation of this independence is via the relation of the FC voltage deviations  $\Delta v_{Ci}$  with the inverter output voltage during the state  $S_j$ ,  $v_o(S_j)$ , given in matrix form in (1) for this example. This system of equations, referred to hereinafter as  $v_o = P \times \Delta v_C$ , can show whether the considered ZSS are independent or not: the FCs are independently expressed in the output voltage if, and only if, the system of equations has a unique solution  $\Delta v_c = P^{-1} \times v_o$  expressed in (2), i.e., when the P matrix is invertible.

$$\begin{bmatrix} v_0(S_1) \\ v_0(S_2) \\ v_0(S_3) \end{bmatrix} = \begin{bmatrix} 0 & 1 & 0 \\ -1 & 0 & 1 \\ 1 & -1 & 1 \end{bmatrix} \times \begin{bmatrix} \Delta v_{C1} \\ \Delta v_{C2} \\ \Delta v_{C3} \end{bmatrix} \leftrightarrow$$

$$\mathbf{v_0} = \mathbf{P} \times \mathbf{\Delta} \mathbf{v_C} \tag{1}$$

$$\begin{bmatrix} \Delta v_{C1} \\ \Delta v_{C2} \\ \Delta v_{C3} \end{bmatrix} = \begin{bmatrix} 0.5 & -0.5 & 0.5 \\ 1 & 0 & 0 \\ 0.5 & 0.5 & 0.5 \end{bmatrix} \times \begin{bmatrix} v_0(S_1) \\ v_0(S_2) \\ v_0(S_3) \end{bmatrix} \leftrightarrow$$

$$\Delta v_c = P^{-1} \times v_o$$

(2)

This analysis shows that fast natural balancing is achieved when the PWM produces a number of *independent* ZSS equal to the FC count, and that this condition holds true when  $v_0 = P \times \Delta v_C$  has a unique solution. The objective of this paper is to derive a PWM that satisfies just that for any number of levels.

#### **B. ACTIVE BALANCING**

Such a PWM that generates the "right" amount of independent ZSS is also a requirement for active balancing that employs ac-side monitoring. For example, in [32] we show that the FC voltages can be extracted by clamping (i.e., saturating) and sampling the inverter voltage solely during the ZSS. This method increases the resolution and accordingly broadens the measurement bandwidth to more than 200 kHz, allowing its application in high frequency GaN-based inverters. At the same time, the circuit complexity and cost are kept to a minimum, by using a single, non-isolated sensor per phase.

The only prerequisite is to apply a PWM strategy that relates the output voltage with the FC voltages  $v_o = P \times \Delta v_C$  in a way that we can extract the latter from the former, i.e., the system is fully observable and has a unique solution  $\Delta v_c = P^{-1} \times v_o$ . Interestingly, this is the same condition for optimal natural balancing, that is to produce a number of *independent* ZSS equal to the FC count. Although this has been established for N = 5 in [32], it remains an open challenge for an arbitrary number of levels N.

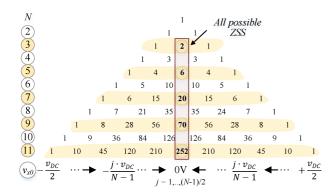

FIGURE 4. Pascal's triangle representing the redundant switching states in an FC MLI with arbitrary number of levels.

The main conclusion here is that both natural and active balancing benefit from a PWM that produces *independent* ZSS of equal number to the FC count. This observation is further elaborated next and utilized to assess whether a PWM satisfies that condition by checking the rank of matrix P in  $v_0 = P \times \Delta v_C$ .

## C. EXTENSION CHALLENGES

In a 5-level inverter, the MPSPWM method dictates that a single carrier swapping of any neighboring carriers at their intersecting point is sufficient for introducing the missing ZSS, i.e.,  $S_3$ . However, in higher order MLIs, there is no guideline in literature for which carrier pairs should be exchanged nor details on the correct number of swaps in one period. This leads to hundreds, even thousands of possible carrier swapping combinations. For instance, a 9-level FC inverter has 8 carrier signals that can be arranged in more than 750 swapping combinations. Most of them, however, still produce an insufficient number of switching states or do not result in an adequate number of *independent* ZSS.

The first task for breaking down the PWM extension complexity is to identify *all possible* ZSS for any number of levels. In this study, we introduce an intuitive representation of the degree of redundancy of each generated voltage level in a FC MLI through the Pascal's Triangle, shown in Fig. 4. Each element in the triangle shows the number of states that produce the voltage level that is indicated in the base of the triangle for the number of levels given in the row. For example, the outer edges always correspond to the maximum output voltage  $\pm v_{DC}/2$ , whereas the central column corresponds to 0 V, i.e., the number of *all possible* ZSS. It is evident that only MLIs with odd number of levels can produce zero output voltage, which is why these are the most widely used MLIs, both commercially and in academic reports.

The number of *all possible* ZSS shown in the central column can be calculated via the central binomial coefficient,  $P_b$ , given in (3), while the number of the *unique* ZSS is  $P_b/2$ .

$$P_b = \frac{(2 \cdot n)!}{(n!)^2}$$

, where  $n = \frac{N-1}{2}$  (3)

TABLE 2. Zero Switching States For A 5-Level FC Inverter

| Number of levels (N) | Number of FC (N <sub>FC</sub> ) | Unique ZSS<br>(P <sub>b</sub> /2) | Independent ZSS<br>from PSPWM<br>(n) | Extra ZSS<br>required<br>(N <sub>ex</sub> ) |

|----------------------|---------------------------------|-----------------------------------|--------------------------------------|---------------------------------------------|

| 3                    | 1                               | 1                                 | 1                                    | 0                                           |

| 5                    | 3                               | 3                                 | 2                                    | 1                                           |

| 7                    | 5                               | 10                                | 3                                    | 2                                           |

| 9                    | 7                               | 35                                | 4                                    | 3                                           |

| 11                   | 9                               | 126                               | 5                                    | 4                                           |

In the general case of an N-level inverter, there are  $N_{FC} = N$ -2 flying capacitors, meaning we need at least N-2 independent ZSS for a unique solution in  $v_0 = P \times \Delta v_C$ . However, the phase-shift switching pattern produces only n = (N-1)/2 unique ZSS. This is because in one switching period there are N-1 switching states, half of which are unique, and the other are the complementary ones. However, n is always smaller than  $N_{FC}$ , with the exception of N = 3. This means that an increasing number of additional ZSS, proportional to the number of levels, are required for an independent system of equations. The amount of extra switching states  $N_{ex}$  is given by (4).

$$N_{ex} = N_{FC} - n = \frac{N-3}{2} = n-1 \tag{4}$$

Table 2 summaries the number of unknown variables,  $N_{FC}$ , the maximum possible ZSS,  $P_b/2$ , the *independent* ZSS produced by the PSPWM, n, and the additional ZSS needed,  $N_{ex}$ , for various levels. It is evident that the PSPWM is appropriate only for a 3-level inverter and a 5- level inverter indeed requires one extra state as already demonstrated earlier.

A key observation regarding the CSPWM is that a single swapping of two carriers generates one new pair of switching states (a unique one and its complementary) while, all the original states are still produced. This is because every swapping splits the switching sequence into two distinct periods, as shown in Fig. 3(b):

- the original carrier sequence {12,34}, marked with the gray area, and

- the new sequence with swapped carriers {21,34} high-lighted with the yellow area.

This reveals that the minimum number of swapping actions,  $N_{sw}$ , should be equal to  $N_{ex}$ , e.g., 2 swaps for a 7-level inverter, 3 swaps for 9-level and so on. Yet, depending on the selection of the carrier pairs to be swapped, the resulting system of equations can be independent, overdetermined, or inconsistent. The following section is dedicated in identifying the PWM strategy with the right swapping actions that lead to the desired independence condition for any number of levels.

## **III. PROPOSED CARRIER SWAPPING PWM EXTENSION**

Here we present the analytical methodology to produce the generalized PWM strategy with optimal ZSS utilization. The guidelines given in the following subsections aim to provide the reader with a single and straightforward modulation pattern, thus addressing the almost-chaotic carrier swapping

**TABLE 3.** Zero Switching States For A 7-Level FC Inverter

| State    | $Q_I$ | $Q_2$ | <b>Q</b> <sub>3</sub> | <b>Q</b> <sub>4</sub> | <b>Q</b> 5 | $Q_6$ | $v_{\theta}$                                                                            |

|----------|-------|-------|-----------------------|-----------------------|------------|-------|-----------------------------------------------------------------------------------------|

| $S_1$    | 0     | 0     | 0                     | 1                     | 1          | 1     | $\Delta v_{C3}$                                                                         |

| $S_2$    | 1     | 0     | 0                     | 0                     | 1          | 1     | Δvc4 - Δvc1                                                                             |

| $S_3$    | 1     | 1     | 0                     | 0                     | 0          | 1     | Δvc5 - Δvc2                                                                             |

| $S_4$    | 0     | 0     | 1                     | 1                     | 0          | 1     | $\Delta v_{C5}$ - $\Delta v_{C4}$ + $\Delta v_{C2}$                                     |

| $S_5$    | 0     | 1     | 1                     | 0                     | 0          | 1     | $\Delta v_{C5}$ - $\Delta v_{C3}$ + $\Delta v_{C1}$                                     |

| $S_6$    | 0     | 0     | 1                     | 0                     | 1          | 1     | $\Delta v_{C4}$ - $\Delta v_{C3}$ + $\Delta v_{C2}$                                     |

| $S_7$    | 0     | 1     | 0                     | 0                     | 1          | 1     | $\Delta v_{C4}$ - $\Delta v_{C2}$ + $\Delta v_{C1}$                                     |

| $S_8$    | 1     | 0     | 0                     | 1                     | 0          | 1     | $\Delta v_{C5}$ - $\Delta v_{C4}$ + $\Delta v_{C3}$ - $\Delta v_{C1}$                   |

| $S_9$    | 1     | 0     | 1                     | 0                     | 0          | 1     | $\Delta v_{C5}$ - $\Delta v_{C3}$ + $\Delta v_{C2}$ - $\Delta v_{C1}$                   |

| $S_{I0}$ | 0     | 1     | 0                     | 1                     | 0          | 1     | $\Delta v_{C5}$ - $\Delta v_{C4}$ + $\Delta v_{C3}$ - $\Delta v_{C2}$ + $\Delta v_{C1}$ |

combinations. The generated pattern shall hold true for any number of stages and shall coincide with the already existing MPSPWM when N = 5.

The following analysis considers a 7-level inverter as an example, therefore, it is useful to introduce all possible ZSS of the 7-level inverter in Table 3.

#### A. UNIQUE ZSS MATRIX FROM PSPWM

The first step is to identify the original ZSS produced by the conventional PSPWM for N levels and capture them in a binary matrix format,  $S_{PS(N)}$ , the size of which is  $n \times (N-1)$ . This matrix has an insufficient number of states (see Table 2), but it forms the basis for the steps that follow. The so-called *unique ZSS matrix* for a 7-level inverter is given in (5), corresponding to  $S_1$ - $S_3$ . In the general case of N levels:

- The 1<sup>st</sup> row (*S*<sub>1</sub>) comprises of '0' in the half leftmost elements and '1' in the other half, i.e., the *n* top transistors in the high-side of the bridge leg conduct (e.g., *Q*<sub>4</sub>-*Q*<sub>6</sub> for 7 levels).

- Every other state can be found by performing the logical operation of *circular right shift* on the previous state [43], i.e., shifting the bit-series to the right by one bit and filling in the leftmost position with the rightmost bit that was shifted out (e.g.,  $S_2$  is produced by shifting  $S_1$ , and  $S_3$  from shifting  $S_2$ ).

- This is performed *n*-1 times, so that all *n* unique ZSS that can be produced by PSPWM are captured in *S*<sub>PS(N)</sub>.

$$S_{PS(7)} = \begin{bmatrix} S_1 \\ S_2 \\ S_3 \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 1 & 1 & 1 \\ 1 & 0 & 0 & 0 & 1 & 1 \\ 1 & 1 & 0 & 0 & 0 & 1 \end{bmatrix}$$

(5)

## **B. CARRIER SWAPPING**

The next step requires the identification of the carriers that are good candidates for swapping. A pair of carriers that guaranties the production of new unique switching states are the neighboring ones with adjacent "01" or "10" pairs in every line of the  $S_{PS}$  matrix. In the 7-level inverter example, carriers 2 and 3 correspond to adjacent "01" bits in the 1<sup>st</sup> line in (5) while carriers 6 and 1 correspond to adjacent "10" bits. All the potential carrier exchanges are reported in (6). However, the two carrier pairs in the same row are  $180^{\circ}$  phase shifted and should not be swapped simultaneously; exchanging a second

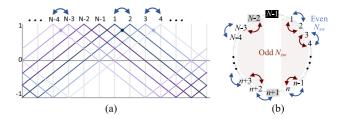

FIGURE 5. (a) Proposed carrier exchange pattern for *N*-level inverter and even number of *N*<sub>sw</sub>. (b) Representation of the proposed swapping pattern for both odd and even number of exchanges.

pair of the same line within the same fundamental period would cancel out the effect of the first pair, meaning that fewer *unique* ZSS will be generated.

Potential Swaps (7) =

$$\begin{bmatrix} \{3, 4\} \text{ and } \{1, 6\} \\ \{4, 5\} \text{ and } \{1, 2\} \\ \{5, 6\} \text{ and } \{2, 3\} \end{bmatrix}$$

(6)

From the remaining n potential swaps (one per row), a combination of  $N_{SW} = N_{ex} = n$ -1 should be selected. Given that any carrier can be part of only one swapping pair, we end up with an easy and intuitive swapping pattern that meets the aforementioned requirements, as explained below and illustrated in Fig. 5:

- The triangle carriers are swapped sequentially in pairs of 2, except for two carriers, that is  $N_{SW} = n$ -1 swaps in total

- If  $N_{SW}$  is even, the exchange sequence will be {12}, {34}, ..., {N-4,N-3}, whereas the last two carriers (N-2 and N-1) are not swapped (e.g., {12} and {34} in the 7-level example). This is graphically shown in Fig. 5(a), where the respective carriers change direction whenever they meet.

- If  $N_{SW}$  is odd, the exchange sequence will be  $\{12\}$ , ...,  $\{n,n-1\}$  and  $\{n+2,n+3\}$ , ..., $\{N-3,N-2\}$  (e.g.,  $\{12\}$ ,  $\{34\}$  and  $\{67\}$  for 9 levels). In other words, the first n consecutive carriers are swapped, leaving the carrier n+1 unaffected and then swapping the following n-2 carriers.

The complete swap pattern is depicted in Fig. 5(b), where the carrier labels are placed onto a circle and the proposed exchanges are shown with blue arrows for even  $N_{SW}$  and red arrows for odd  $N_{SW}$ . This pattern satisfies all the set requirements and holds for FC MLIs of any number of levels. Implementation of this swap mechanism is quite straightforward in any MCU and constitutes essentially the proposed CSPWM.

For natural balancing applications, realizing this swap pattern is the sole step required. For active balancing employing ac-side monitoring, the additional step of extracting the FC voltages from the output voltage remains; the following sections explain how this is done.

#### C. THE EXTENDED ZSS MATRIX

Calculation of the FC voltages implies forming the  $v_o = P \times \Delta v_C$  relation, which in turn entails composing the coefficients matrix P. To do that, we first need to derive the *independent ZSS matrix*  $S_{I(N)}$  that is produced with the proposed swapping pattern.  $S_{I(N)}$  will incorporate the standard states generated by the PSWPM  $S_{PS(N)}$  plus the additions  $S_{SW(N)}$  introduced by the carrier swapping.

The new switching states  $S_{SW(N)}$  can be extracted from the original state matrix  $S_{PS(N)}$  once we identify *which* states are affected by the carrier swap and *how*:

- Swapping a set of carriers  $\{i, i+1\}$  will affect a single state, that is the one with different bits at these positions, i.e., "01" or "10" bit sequence in the columns (i, i+1). In the 7-level example, the exchange  $\{12\}$  will act upon  $S_2 = \mathbf{10}$ 0011, while the  $\{34\}$  swap will affect  $S_I = 00\mathbf{01}$ 11.

- Each state affected gets the respective bits swapped, so that a new ZSS is generated. In the 7-level example,  $S_2$  is transformed into  $S_7 = \mathbf{01}0011$ , and  $S_1$  into  $S_6 = 00\mathbf{10}11$ .

The matrix form of the newly generated states  $S_{SW(N)}$  is of  $N_{SW}$  x (N-1) size. For the 7-level inverter,  $S_{SW(7)}$  is given in (7), where the exchanges are marked with bold text.

$$S_{SW(7)} = \begin{bmatrix} S_6 \\ S_7 \end{bmatrix} = \begin{bmatrix} 0 & 0 & 1 & 0 & 1 & 1 \\ 0 & 1 & 0 & 0 & 1 & 1 \end{bmatrix}$$

(7)

Now the matrix that incorporates all independent switching states,  $S_{I(N)}$ , can be derived by concatenating matrices  $S_{PS(N)}$  and  $S_{SW(N)}$ , leading to a (N-2) x (N-1) matrix. An example of the  $S_{I(7)}$  is presented in (8).

$$S_{I(7)} = \begin{bmatrix} S_{PS(7)} \\ S_{SW(7)} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 1 & 1 & 1 \\ 1 & 0 & 0 & 0 & 1 & 1 \\ 1 & 1 & 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 & 1 & 1 \\ 0 & 1 & 0 & 0 & 1 & 1 \end{bmatrix}$$

(8)

#### **D.** SOLUTION TO THE SYSTEM OF EQUATIONS $v_o = P \times \Delta v_C$

The final step of this analytical methodology is to solve  $v_o = P \times \Delta v_C$ , which requires determination of the coefficient matrix P. This calculation is based on the principle that the conduction and current direction of a FC is determined by the state of the two neighboring transistors between which the FC positive terminal is connected to. More specifically, the capacitor  $C_i$

- does not conduct when the devices Q<sub>j</sub> and Q<sub>j+1</sub> are both on (1) or both off (0),

- contributes to the output voltage with a positive sign (+1) when  $Q_j$  is off (0) and  $Q_{j+1}$  is on (1) and

- contributes to the output voltage with a negative sign (-1) when  $Q_j$  is on (1) and  $Q_{j+1}$  is off (0).

Thus, the contribution of capacitor  $C_j$  in the output voltage during the state  $S_i$  can be modeled by subtracting the j bit from the j+1 bit in i row of  $S_{I(N)}$ , as described in (9).

$$P_{(N)}(i, j) = S_{T(N)}(i, j + 1) - S_{I(N)}(i, j),$$

$i, j = 1, ..., N - 2.$  (9)

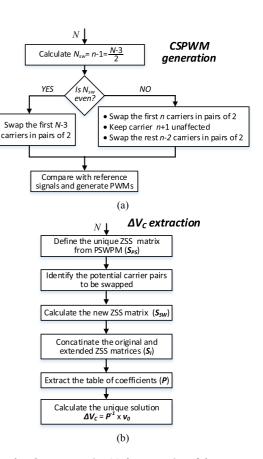

FIGURE 6. Flowcharts presenting (a) the generation of the CSPWM pattern for enhanced natural balancing and (b) the extraction of the  $\Delta V_C$  measurements for the ac-side monitoring and for an arbitrary umber of levels.

Since  $S_{I(N)}$  holds a set of *independent ZSS* equal in number to the FC count, the resulting  $P_{(N)}$  matrix will always be of square size  $(N-2) \times (N-2)$  with a rank equal to the FC count and will *always be invertible*.  $P_{(7)}$  of the 7-level example is given in (10). The flying capacitor's voltage deviation can now be extracted by finding the inverse of the coefficient matrix,  $P^{-1}$ , and solving  $\Delta v_c = P^{-1} \times v_o$ .

$$\boldsymbol{P}_{(7)} = \begin{bmatrix} 0 & 0 & 1 & 0 & 0 \\ -1 & 0 & 0 & 1 & 0 \\ 0 & -1 & 0 & 0 & 1 \\ 0 & 1 & -1 & 1 & 0 \\ 1 & -1 & 0 & 1 & 0 \end{bmatrix}$$

(10)

The previous analysis is summarized in the flowcharts of Fig. 6 and is implemented in the Matlab code that accompanies this paper.

An important feature of the proposed PWM extension methodology is that it always generates fully symmetrical switching states within one full period, i.e., double of the switching period. This is a key requirement for achieving fast natural balancing, as explained in [22]. An additional benefit of this approach is that the produced ZSS and their sequence in time are generated analytically without the need for complex or time-consuming simulations. This feature, along with the

straightforward derivation of the solution to the system of equations for the FC voltages allows the direct application of the precise measurement system of [32] for active balancing. It is worth noting that in case this ac-side monitoring system is to implemented, the inverter switching frequency should be bounded by the limits of (11), according to [32], where  $\omega$  is the angular fundamental frequency and  $T_{ADC}$  is the sample and hold time of the analogue-to-digital converter (ADC) module that captures the inverter switching node.

$$F_{sw_{\min}}^{\max} = \frac{1 \pm \sqrt{1 - 2 \cdot T_{ADC} \cdot \omega \cdot (N - 1)^2}}{2 \cdot T_{ADC} \cdot (N - 1)}$$

(11)

On the contrary, if the application relies only on the improved natural balancing provided by the CSPWM, there is no practical limitation for the switching frequency. The proposed CSPWM hardly adds any computational cost, compared to the traditional PSPWM, allowing its implementation in a conventional microprocessor, as will be verified in Section V.

Overall, the proposed modulation method is an improved alternative to the traditional PSPWM any FC, with better natural balancing response, possibility to easily measure the FC voltages from a single point, with minimal added computational complexity but at the cost of slightly higher THD, as will be shown in the following Section

#### IV. SIMULATION RESULTS

The purpose of this section is to evaluate the scalability of the proposed PWM pattern and its dynamic performance for natural balancing against other conventional and state of the art PWMs. To this end, we have implemented the described analytical models along with detailed switching models of the entire 7-level FC inverter in Matlab/Simulink.

## A. ANALYTICAL APPROACH

This analysis aims to validate that the prosed swapping pattern generates the right set of independent ZSS for any level and compare that to other PWMs in literature. The process starts with the generation of the triangle waveforms, followed by the calculation of the crossing points between carriers and the extraction of the ZSS for the selected carrier exchange option.

To highlight the complexity of extending the CSPWM without a known pattern, we have implemented an exhaustive search for the optimum solution when two pairs of carriers are swapped in a 7-level inverter. The criteria for selecting the best combination are:

- 1) The system of equation should have a unique solution, i.e., all ZSS are *independent*.

- The PWM sequence should have fully symmetrical ZSS, which means that a complete sequence is comprised by an equal number of *unique* and *complemen*tary ZSS.

- 3) The system should not be overdetermined i.e., the number of *independent* ZSS is equal to the FC count.

Fig. 7 summarizes all the possible swapping combinations in a color-coded 2D table format. Every row has the same first pair of triangles and the second pair changes with different

|                  |                  | 1-2 & 3-6<br>(4) |           |                                        |           |

|------------------|------------------|------------------|-----------|----------------------------------------|-----------|

| 1-3 & 2-4        | 1-3 & 2-5        | 1-3 & 2-6        | 1-3 & 4-5 | 1-3 & 4-6                              | 1-3 & 5-6 |

|                  |                  | (6)<br>1-4 & 2-6 |           | ······································ |           |

|                  |                  | (5)              |           |                                        |           |

| 1-5 & 2-3        | 1-5 & 2-4        | 1-5 & 2-6        | 1-5 & 3-4 | 1-5 & 3-6                              | 1-5 & 4-6 |

|                  |                  | (6)<br>1-6 & 2-5 |           |                                        |           |

|                  |                  | (4)              |           |                                        | (5)       |

|                  | 2-3 & 4-6<br>(5) |                  |           |                                        |           |

|                  | 2-4 & 3-6        |                  |           |                                        |           |

| 2-5 & 3-4        | 2-5 & 3-6<br>(4) | 2-5 & 4-6        |           |                                        |           |

| 2-6 & 3-4<br>(5) | 2-6 & 3-5<br>(5) | 2-6 & 4-5<br>(5) |           |                                        |           |

| 3-4 & 5-6<br>(5) |                  |                  |           |                                        |           |

| 3-5 & 4-6<br>(6) |                  |                  |           |                                        |           |

| 3-6 & 4-5<br>(4) |                  |                  |           |                                        |           |

FIGURE 7. All possible combinations of exchanging two pairs of carriers in a 7-level inverter. The color coding indicates underdetermined systems (in gray), overdetermined systems (in yellow), independent systems with non-symmetrical states (in light red) and independent systems and symmetrical ZSS (in dark-green, proposed pattern).

columns. Every cell contains two pieces of information: the carrier swapping combination and the number of unique ZSS. We can group the cells in four categories:

- The cells with gray background indicate that the ZSS are not *independent* even if the number of the *unique* produced ZSS is greater than  $N_{FC} = 5$  (i.e., the system  $v_o = P \times \Delta v_C$  is underdetermined).

- The cells in light-red shading have an equal number of independent ZSS and FC count, but some states do not come into complementary pairs, i.e., the ZSS are nonsymmetrical.

- The combinations in yellow color give a set of independent ZSS which are more in numbers than the FC count, i.e., overdetermined system. This hinders the acside monitoring system implementation, since it is not straightforward to form and solve the system of equations.

- Lastly, the cells in dark-green color satisfy all the set criteria by producing exactly as many *independent* ZSS as the FC count. Simultaneously, the natural balancing is optimal, while the FC voltages extraction in ac-side monitoring is easier. The proposed pattern corresponds to the top-left cell (1,1), but a close look reveals that all green cells are essentially the same pattern but with different carrier numbering. In fact, all of them can be generated from the proposed pattern by selecting an arbitrarily carrier as the starting point, i.g., starting the swapping sequence with the carrier 1, or 2, or ...6. The main conclusion here is that the set requirements are met only with the proposed pattern.

Further to the exhaustive search, we validated the expandability of the proposed pattern using the Matlab code that

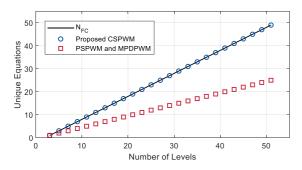

FIGURE 8. Number of independent equations generated by the CSPWM, the PSPWM and the MPDPWM for a wide range of levels.

**TABLE 4.** Matlab/Simulink Simulation Parameters

| Parameter | Levels | Rload | VDC | $F_{sw}$ | $C_{DC^+},$ $C_{DC^-}$ | $C_{FC}$ | $L_F$ |

|-----------|--------|-------|-----|----------|------------------------|----------|-------|

|           | 7 to13 |       |     |          |                        |          |       |

accompanies this paper. The provided code generates the matrices  $S_{SP}$ ,  $S_{SW}$  and  $S_I$ , it calculates the coefficient table P and solves the system of equations  $\Delta v_c = P^{-1} \times v_o$ , by computing the inverse  $P^{-1}$ , for any number of levels N (input). Repetitive execution of the Matlab script for a wide range of levels proves that the CSPWM pattern always generates an independent system of equation with symmetrical states. This is graphically illustrated in Fig. 8 that shows the rank of the equation matrices for the CSPWM (blue circle markers), the PSPWM and the MPDPWM (both in red square markers) for N = 3, ..., 51. The rank of these matrices represents the number of independent equations. It is evident that only the proposed PWM pattern produces an adequate number of independent equations, equal to the number of FC, marked with black sold line. This in turn means that, contrary to alternative methods, the CSPWM allows all FC to be independently expressed at the inverter output voltage for any number of levels, leading to optimal natural balancing.

#### **B. SWITCHING MODEL SIMULATIONS**

Here we investigate the natural balancing performance for the proposed CSPWM pattern against the conventional PSPWM and the modified PDPWM, during an instantaneous imbalance. Such imbalance can be caused by load disturbances or grid-side asymmetries and will be reflected to the capacitor voltage levels. Yet, the most representative short-term imbalance condition, that is also implementable and reproducible in the experimental setup, is the step change to the DC voltage. It is expected that the implemented PWMs will compensate for the voltage imbalance, leading the system back to stability. The simulation parameters are listed in Table 4.

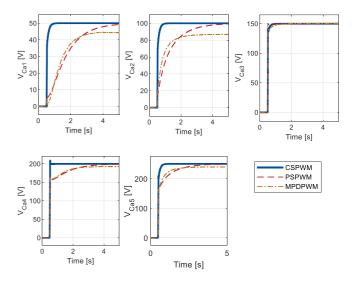

For the first test we simulated a 3-phase 7-level FC inverter operating at 16.67 kHz and feeding a symmetrical resistive load of 10  $\Omega$  through an inductive filter of 270  $\mu$ H. The star

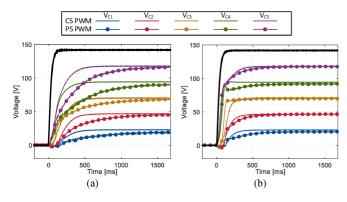

**FIGURE 9.** Natural balancing response of a 7-level FC inverter operated with the CSPWM, the PSPWM, the MPDPWM, during a step change of the dc-link voltage from 0 V to 300 V. The worst-case scenario of  $m_a=0$  is simulated

neutral was connected to the dc-link mid-point. We investigated the worst-case scenario of  $m_a = 0$ , which corresponds to the maximum balancing time, as mentioned in Section II, and thus, it best highlights the strength or weakness of a PWM scheme. Fig. 9 shows the FC voltages during a step change of the dc-link from 0 V to 300 V. It is evident that the CSPWM pattern exhibits the fastest natural balancing response for all FC compared to the conventional PSPWM and the MPDPWM. The only exception is the middle capacitor ( $C_3$  for the 7-level inverter) for which the PSPWM and MPDPWM are marginally faster. This is attributed to the fact that  $C_3$  is contributing independently to the inverter output voltage (state  $S_1 = 000111$ ) twice as many times as in the CSPWM.

It is worth noting that the natural balancing settling time is affected by the switching frequency, as formulated in [36], [37] for the PSPWM. However, the CSPWM performs better compared to other PWM methos, and the settling time is the smallest possible for the given switching frequency.

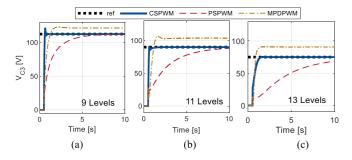

Further to the 7-level MLI results, we have developed the switching models of a 9-, 11-, and 13-level inverter to validate the performance of the generalized CSPWM for a larger number of levels and thus prove the extension effectiveness of the proposed pattern. The rest of the simulation parameters are kept the same as the 7-level test, tabulated in Table 4. For presentation coherence, we only plot the response of  $C_3$  during natural balancing in Fig. 10. This graph highlights the advantages of the CSPWM for faster natural balancing and more precise capacitor level compared to the commonly used PSPWM and the state-of-the-art MPDPWM.

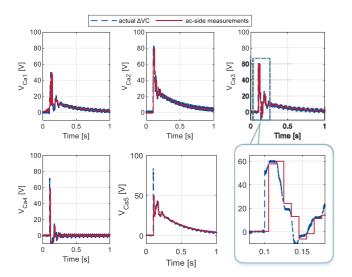

Further to the natural balancing simulations we investigated the performance of the ac-side monitoring system with an analytical calculation of the  $\Delta V_C$  signals [32]. To record a

FIGURE 10. Natural balancing response of C<sub>3</sub> in a (a) 9-level, (b) 11-level and (c) 13-level FC inverter with different modulation strategies, during a step change of the dc-link voltage from 0 V to 300 V.

FIGURE 11. FC voltage deviation during a step change of the dc-link voltage from 200 V to 300 V. The ac-side measurements are plotted against the actual  $\Delta V_C$  signals.

sharp FC voltage variation, the inverter was subjected to a step dc-link change from  $v_{DC} = 200 \text{ V}$  to  $v_{DC} = 300 \text{ V}$  while the modulation index was fixed at  $m_a = 0.8$ . The measurements extracted from the ac-side sensing are plotted against the actual FC voltage deviation signals in Fig. 11. Although the sampling rate is very high (one sample per ZSS, i.e., the sampling frequency is  $F_{SW}/(N-1)$ ) the measurements are updated once every zero crossing of the inverter output voltage, thus twice in one fundamental period, as can be seen from the zoomed view in Fig. 11. This is a typical feature of an ac-side monitoring approach which, despite the relatively small update frequency, is proven to be effective for active balancing [32], [33], [34], [35].

Even under such harsh conditions, the analytical extraction of the  $\Delta V_C$  values is accurate allowing the application of an active balancing scheme.

Another important characteristic of any PWM strategy is the total harmonic distortion (THD) of the generated output current. To quantify the THD of the PWMs under investigation, we simulated the MLIs for a wide range of levels (from 7

**TABLE 5.** Output Current THD For Different Number of Levels and Modulation Strtegies

| Levels | PSPWM  | MPDPWM | CSPWM  |

|--------|--------|--------|--------|

| 7      | 1.29 % | 1.66 % | 1.86 % |

| 9      | 0.72 % | 1.34 % | 1.11 % |

| 11     | 0.67 % | 0.95 % | 0.86 % |

| 13     | 0.57 % | 0.93 % | 0.77 % |

TABLE 6. List of Components of The 7-Level Inverter Prototype

| Main and              | d Filter Bo                | oard        | Clamping Circuit      |                   |              |         |  |

|-----------------------|----------------------------|-------------|-----------------------|-------------------|--------------|---------|--|

| Component             | Component Part No          |             |                       |                   | Pι           | art No  |  |

| DC-link<br>Capacitors |                            |             | M                     | OSFETs            | STD81        | N60DM2  |  |

| microcontroller       | F28                        | F28384D     |                       | umentation<br>Amp | AD842        | 21ARMZ  |  |

| Current sensor        | MLX                        | 91221       | Oper                  | ation Amp         | OP/          | A2189   |  |

| Voltage isolator      | ACPL                       | -C87A       | Zen                   | er Diodes         | KDZV'        | ΓFTR20B |  |

| ADC module            | ADS                        | $R_S$ $R_S$ |                       | $R_S$             | $200 \Omega$ |         |  |

| Filter Inductors      | Filter Inductors 1140-2711 |             | $v_{1}$ K-RC $v_{DD}$ |                   | 1            | 12V     |  |

|                       |                            | Power       | Board                 | 1                 |              |         |  |

| Compone               | nt                         |             |                       | Part No           |              |         |  |

|                       |                            | (           | C5750X6S2W225K250KA   |                   |              |         |  |

| Flying Capa           | citors                     | $C_I$       | $C_2$                 | $C_3$             | $C_4$        | $C_5$   |  |

|                       |                            | 6p1s        | 9p1s                  | 14p1s             | 16p1s        | 20p1s   |  |

| GaN Devi              | ces                        |             | EPC2034               |                   |              |         |  |

| Gate Driv             | UCC27611DRVT               |             |                       |                   |              |         |  |

| Digital isol          | ator                       |             | Si8610BC-B-IS         |                   |              |         |  |

| Power isola           | ator                       |             | MTU1S1205MC           |                   |              |         |  |

| $F_{sw}$              |                            |             |                       | 66.667 kHz        |              |         |  |

to 13 levels) with the parameters of Table 4 and a fixed amplitude modulation index of 0.8, under steady state conditions. All simulations were executed with a discrete step of 200 ns and the THD was calculated during 4 fundamental cycles. The results tabulated in Table 5 show that the PSPWM generates the lowest harmonics followed by the MPDPWM and then the CSPWM. However, the difference in THD between the proposed PWM and the conventional PSPWM falls with the number of levels from 0.57% to only 0.2%. This could be considered a small price to pay for an improved natural balancing and a very cost-effective and compact measurement system that results from the direct expression of all FC at the inverter switching node.

The simulation results have demonstrated that the proposed PWM extension pattern generates an adequate number of independent equations with symmetrical switching states for any number of levels at the cost of slightly higher THD of the output current. The CSPWM leads to fastest natural balancing response with accurate steady state FC voltages and direct expression of all FC to the inverter switching node for a precise voltage measurement through a simple, cost effective and compact ac-side circuit.

#### V. EXPERIMENTAL VERIFICATION

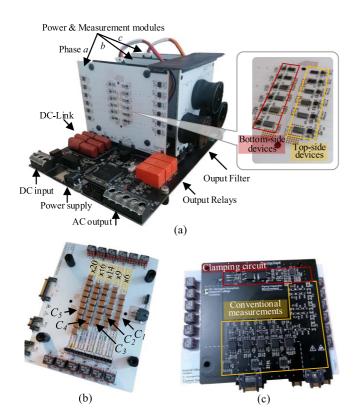

For the experimental evaluation of the proposed CSPWM extension we have designed and developed a 7-level all-GAN inverter depicted in Fig. 12, with the components and parameters listed in Table 6. The DC-link is located in the main printed circuit board (PCB) and each of its capacitors,  $C_{DC+}$

FIGURE 12. (a) GaN MLI prototype used for the experimental validation. (b) Bottom view of a single phase-leg board. (c) FC measurement module.

and  $C_{DC}$ , is comprised by 12 parallel connected polypropylene film capacitors, with a total capacitance of 12 · 4.7  $\mu$ F = 56.4  $\mu$ F. The main board also holds the DC and AC input and output measurement sensors and the microcontroller.

A single phase-leg PCB, shown in Fig. 12(b) in white solder mask, holds the twelve EPC2034 transistors, their gate drivers (UCC27611), and the accompanying power and digital isolators (MTU1S1205MC and Si8610BC-B-IS, respectively). Each FC, mounted on the back side of this PCB, consists of several parallel connected multi-layer ceramic capacitors (MLCC), to reach 10  $\mu$ F. The number of parallel MLCCs is proportional to the voltage stress of every FC, as the selected components (C5750X6S2W225K250KA) exhibit a sharp decline of their capacitance with the applied DC bias [44].

The measurement module, shown in Fig. 12(b) in black solder mask, is dedicated for monitoring the FC voltages with two methods: i) the conventional galvanically isolated voltage divider and ii) the ac-side monitoring system proposed in [32].

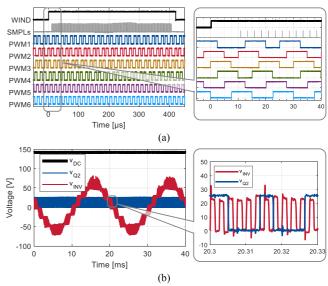

The switching frequency was set to  $F_{sw} = 66.667$  kHz, which corresponds to a ZSS pulse-width of 2.5  $\mu$ s. The implemented CSPWM is presented in Fig. 13(a). Carriers {1, 2} and {3, 4} switch positions at their intersecting point, while carriers 5 and 6 remain unaffected, as can be seen from the zoomed view on the right. The black trace indicates a region close to the output voltage zero crossing, where the ZSS are manifested with the longest possible pulse width. More details for this ac-side monitoring method may be found in [32].

FIGURE 13. (a) Experimental measurements of the proposed CSPWM sequence for a 7-Level inverter. The gray trace indicates the sampling timing of the inverter output voltage close to the zero-crossing point, marked with a black trace. (b). Input and output voltage waveforms for the 7-level inverter when  $v_{DC}=140$  V. The transistor's  $Q_2$  drain-source voltage is also included in the same graph.

The gray peaks represent the instances of the different ZSS and can be used for sampling the inverter switching node to obtain  $v_o(S_I)$ . The system was initially tested in steady state conditions under  $v_{DC}=140$  V, as demonstrated in Fig. 13(b). In this graph the input and output voltage waveforms are plotted, along with transistor's  $Q_2$  drain-source voltage.

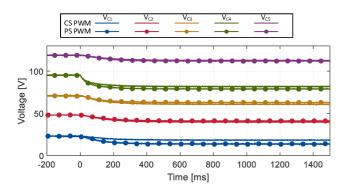

## A. NATURAL BALANCING UNDER DISTURBANCES

The natural balancing response of the proposed CSPWM was initially evaluated against the conventional PSPWM under a sharp voltage change on the dc-link. More specifically,  $v_{DC}$ was originally set to zero and subsequently was increased to 140 V in a step manner. At the same time, the modulation index was set to zero,  $m_a = 0$ , so that only the ZSS contribute to the natural balancing. The FC voltage measurements were recorded for two scenarios: a) no-load conditions and b) the inverter feeding an RL load with  $R = 10 \Omega$  and L = $270 \mu H$ . The results are plotted in Fig. 14, where the CSPWM is shown in solid lines and the PSPWM with circle marks. Comparing (a) with (b), we observe faster response in high loads as the imbalance energy is dissipated more rapidly. But in both scenarios the CSPWM has enhanced natural balancing response with 3 times lower settling time (10% to 90%) than the PSPWM (calculated as an average over all FC). It is only  $C_3$  voltage that exhibits slightly faster response with the PSPWM and RL load, as explained in Section IV.

#### **B. NATURAL BALANCING AT PERMANENT ASYMMETRIES**

With the second experiment we evaluate the performance of the CSPWM in an inherent/permanent system asymmetry. To this end, we introduced an abrupt imbalance at  $t_0 = 0$ , with

FIGURE 14. Natural balancing response of the CSPWM against the PSPWM during a step change of the dc-link (black trace) and (a) no-load conditions and (b) the inverter feeding an RL load.

FIGURE 15. FC voltages measured under step-wise asymmetry introduced on  $C_4$ .

the form of a resistor,  $R_{asym} = 47 \text{ k}\Omega$ , connected across  $C_4$ . The oscilloscope waveforms for the FC voltages are plotted over time in Fig. 15, where the solid lines correspond to the proposed CSPWM and the traces with circle marker to the PSPWM. The results highlight that the CSPWM helps the FC maintain a smaller voltage deviation especially  $C_1$  and  $C_4$ , compared to the PSPWM.

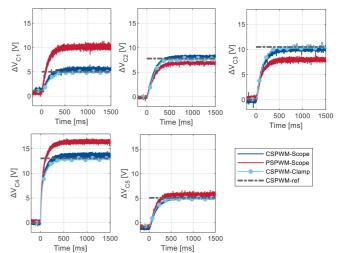

#### C. AC-SIDE MONITORING

Lastly, the same test conditions are applied to demonstrate the extraction of the FC voltage deviation,  $\Delta V_C$ , through the ac-side monitoring system of [32]. Please also note that the introduction of the clamping circuit on the switching node of the inverter will not affect the natural balancing response, due to the minimal added parasitic components.

Having the coefficient table of the 7-level inverter from the analytical method (10), we can solve the system of equations (1) just by sampling the inverter output on every ZSS. Fig. 16 shows the results of the analytical solution with light-blue traces and round markers in comparison to the respective oscilloscope measurements (in dark blue color). The gray dash-dotted lines correspond to the true-RMS measurements via a digital multimeter, before and after the asymmetry. For sake of completeness, we have also included the FC voltage

**FIGURE 16.** Voltage variation the FC (a)  $\Delta v_{CI}$ , (b)  $\Delta v_{C2}$ , (c)  $\Delta v_{C3}$ , (d)  $\Delta v_{C4}$  and (e)  $\Delta v_{C5}$ , when a step-like asymmetry is introduced in  $C_4$  of a 7-level inverter at  $t_0=0$  and  $v_{DC}=140$  V. Comparison between traditional voltage devider sensor and analytical extraction method.

deviation when the PSPWM strategy is applied (red traces), which of course cannot lead to an analytical solution.

The analytical extraction of the FC voltages always gives a valid solution that perfectly coincides with the reference (multimeter) measurements. In fact, it approximates the  $\Delta V_C$  values even better than the oscilloscope, whose samples deviate slightly from the true RMS measurements as the oscilloscope needs to contain the entire  $V_C$  waveform with finite resolution within the screen, to avoid the overdrive phenomenon [45].

The experimental results showed that the proposed PWM extension is advantageous not only in natural balancing but also helps with the calculation of the FC voltage levels in a simple, accurate and compact method, ideal for the next generation GaN-based MLIs.

### VI. CONCLUSION

In this work we have introduced a generalized PWM strategy for FC MLIs, that ensures enhanced natural and active balancing. The methodology is based on swapping a predefined set of neighboring carriers within two consecutives switching cycles and the pattern is applicable to any number of levels. The result of this analytical method is the extraction of the independence ZSS, their sequence in time and system of equations that relates the FC voltages to the inverter output voltage. The proposed PWM always generates fully symmetrical switching states and the unique solution to the system of equations allows direct application of a compact and fast ac-side FC monitoring system that can subsequently be used for active balancing. The implementation simplicity of the generalized CSPWM hardly adds any computational cost, thus favouring the use of a readily available and cost-effective microprocessors instead of sophisticated FPGAs. The advantages of the CSPWM come at a cost of slightly higher THD of the inverter

output current. Simulation and experimental results on a 7-to 13-level GaN-based inverter validate the improved natural balancing response of the CSPWM during sudden dc-link voltage variations and its enhanced performance in system asymmetries. The extended CSPWM pattern can be a very useful tool for the next generation high-power density and high-frequency GaN MLIs.

#### REFERENCES

- [1] C. B. Barth et al., "Design, operation, and loss characterization of a 1-kW GaN-based three-level converter at cryogenic temperatures," *IEEE Trans. Power Electron.*, vol. 35, no. 11, pp. 12040–12052, Nov. 2020, doi: 10.1109/TPEL.2020.2989310.

- [2] T. Modeer, N. Pallo, T. Foulkes, C. B. Barth, and R. C. N. Pilawa-Podgurski, "Design of a GaN-based interleaved nine-level flying capacitor multilevel inverter for electric aircraft applications," *IEEE Trans. Power Electron.*, vol. 35, no. 11, pp. 12153–12165, Nov. 2020, doi: 10.1109/TPEL.2020.2989329.

- [3] Y. Lei et al., "A 2-kW single-phase seven-level flying capacitor multilevel inverter with an active energy buffer," *IEEE Trans. Power Electron.*, vol. 32, no. 11, pp. 8570–8581, Nov. 2017, doi: 10.1109/TPEL.2017.2650140.

- [4] C. B. Barth et al., "Design and control of a GaN-based, 13-level, flying capacitor multilevel inverter," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 8, no. 3, pp. 2179–2191, Sep. 2020, doi: 10.1109/JESTPE.2019.2956166.

- [5] S. Qin, Y. Lei, Z. Ye, D. Chou, and R. C. N. Pilawa-Podgurski, "A high-power-density power factor correction front end based on seven-level flying capacitor multilevel converter," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 7, no. 3, pp. 1883–1898, Sep. 2019, doi: 10.1109/JESTPE.2018.2865597.

- [6] P. Trochimiuk, R. Kopacz, K. Frac, and J. Rabkowski, "Medium voltage power switch in silicon carbide—A comparative study," *IEEE Access*, vol. 10, pp. 26849–26858, 2022, doi: 10.1109/ACCESS.2022.3156277.

- [7] G. Kampitsis, R. van Erp, and E. Matioli, "Ultra-high power density magnetic-less DC/DC converter utilizing GaN transistors," in *Proc. IEEE Appl. Power Electron. Conf. Expo.*, 2019, pp. 1609–1615. doi: 10.1109/APEC.2019.8721783.

- [8] R. van Erp, G. Kampitsis, and E. Matioli, "Efficient microchannel cooling of multiple power devices with compact flow distribution for high power-density converters," *IEEE Trans. Power Electron.*, vol. 35, no. 7, pp. 7235–7245, Jul. 2020, doi: 10.1109/TPEL.2019.2959736.

- [9] R. van Erp, R. Soleimanzadeh, L. Nela, G. Kampitsis, and E. Matioli, "Co-designing electronics with microfluidics for more sustainable cooling," *Nature*, vol. 585, no. 7824, pp. 211–216, Sep. 2020, doi: 10.1038/s41586-020-2666-1.

- [10] L. Nela, R. Van Erp, G. Kampitsis, H. K. Yildirim, J. Ma, and E. Matioli, "Ultra-compact, high-frequency power integrated circuits based on GaN-on-Si Schottky barrier diodes," *IEEE Trans. Power Electron.*, vol. 36, no. 2, pp. 1269–1273, Feb. 2021,doi: 10.1109/TPEL.2020.3008226.

- [11] L. Nela, G. Kampitsis, J. Ma, and E. Matioli, "Fast-switching trianode Schottky barrier diodes for monolithically integrated GaN-on-Si power circuits," *IEEE Electron Device Lett.*, vol. 41, no. 1, pp. 99–102, Jan. 2020, doi: 10.1109/LED.2019.2957700.

- [12] J. Celikovic, R. Das, H.-P. Le, and D. Maksimovic, "Modeling of capacitor voltage imbalance in flying capacitor multilevel DC-DC converters," in *Proc. 20th Workshop Control Model. for Power Electron.* (COMPEL), 2019, pp. 1–8. doi: 10.1109/COMPEL.2019.8769615.

- [13] P. B. Malidarreh, D. A. Khaburi, and J. Rodriguez, "Capacitor voltage imbalance reduction in flying capacitor modular multilevel converters by using model predictive control," in *Proc. 11th Power Electron., Drive Syst., Technol. Conf.*, 2020, pp. 1–4. doi: 10.1109/PED-STC49159.2020.9088411.

- [14] R. Stela, "Natural capacitor voltage balance in multilevel flying capacitor converters. A review of research achievements," *Power Electron. Drives*, vol. 1, no. 2, pp. 5–33, 2016, doi: 10.5277/ped160201.

- [15] A. M. Y. M. Ghias, J. Pou, G. J. Capella, V. G. Agelidis, R. P. Aguilera, and T. Meynard, "Single-carrier phase-disposition PWM implementation for multilevel flying capacitor converters," *IEEE Trans. Power Electron.*, vol. 30, no. 10, pp. 5376–5380, Oct. 2015, doi: 10.1109/TPEL.2015.2427201.

- [16] B. P. McGrath and D. G. Holmes, "Enhanced voltage balancing of a flying capacitor multilevel converter using phase disposition (PD) modulation," *IEEE Trans. Power Electron.*, vol. 26, no. 7, pp. 1933–1942, Jul. 2011, doi: 10.1109/TPEL.2010.2097279.

- [17] A. Shukla, A. Ghosh, and A. Joshi, "Natural balancing of flying capacitor voltages in multicell inverter under PD carrier-based PWM," *IEEE Trans. Power Electron.*, vol. 26, no. 6, pp. 1682–1693, Jun. 2011, doi: 10.1109/TPEL.2010.2089807.

- [18] A. M. Y. M. Ghias, J. Pou, G. J. Capella, P. Acuna, and V. G. Agelidis, "On improving phase-shifted PWM for flying capacitor multilevel converters," *IEEE Trans. Power Electron.*, vol. 31, no. 8, pp. 5384–5388, Aug. 2016, doi: 10.1109/TPEL.2016.2521803.

- [19] B. P. McGrath, T. Meynard, G. Gateau, and D. G. Holmes, "Optimal modulation of flying capacitor and stacked multicell converters using a state machine decoder," *IEEE Trans. Power Electron.*, vol. 22, no. 2, pp. 508–516, Mar. 2007, doi: 10.1109/TPEL.2006.889932.

- [20] B. P. McGrath and D. G. Holmes, "Multicarrier PWM strategies for multilevel inverters," *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 858–867, Aug. 2002, doi: 10.1109/TIE.2002.801073.

- [21] B. P. McGrath, D. G. Holmes, and T. Lipo, "Optimized space vector switching sequences for multilevel inverters," *IEEE Trans. Power Electron.*, vol. 18, no. 6, pp. 1293–1301, Nov. 2003, doi: 10.1109/TPEL.2003.818827.

- [22] S. Thielemans, A. Ruderman, B. Reznikov, and J. Melkebeek, "Improved natural balancing with modified phase-shifted PWM for single-leg five-level flying-capacitor converters," *IEEE Trans. Power Electron.*, vol. 27, no. 4, pp. 1658–1667, Apr. 2012, doi: 10.1109/TPEL.2011.2169993.

- [23] A. Ibrayeva, V. Ten, Y. L. Familiant, and A. Ruderman, "PWM strategy for improved natural balancing of a four-level H-bridge flying capacitor converter," in Proc. Intl Aegean Conf. Elect. Machines Power Electron. (ACEMP), Intl Conf. Optim. Elect. Electron. Equip. (OPTIM) Intl Symp. Adv. Electromechanical Motion Syst. (ELECTROMOTION), 2015, pp. 311–316. doi: 10.1109/OPTIM.2015. 7426747.

- [24] A. Dekka, A. Ramezani, S. Ouni, and M. Narimani, "A new five-level voltage source inverter: Modulation and control," *IEEE Trans. Ind. Appl.*, vol. 56, no. 5, pp. 5553–5564, Sep./Oct. 2020, doi: 10.1109/TIA.2020.3000712.

- [25] A. M. Y. M. Ghias, J. Pou, M. Ciobotaru, and V. G. Agelidis, "Voltage-balancing method using phase-shifted PWM for the flying capacitor multilevel converter," *IEEE Trans. Power Electron.*, vol. 29, no. 9, pp. 4521–4531, Sep. 2014, doi: 10.1109/TPEL.2013. 2285387.

- [26] A. M. Y. M. Ghias, J. Pou, V. G. Agelidis, and M. Ciobotaru, "Voltage balancing method for a flying capacitor multilevel converter using phase disposition PWM," *IEEE Trans. Ind. Electron.*, vol. 61, no. 12, pp. 6538–6546, Dec. 2014, doi: 10.1109/TIE.2014.2320216.

- [27] C. Feng, J. Liang, and V. G. Agelidis, "Modified phase-shifted PWM control for flying capacitor multilevel converters," *IEEE Trans. Power Electron.*, vol. 22, no. 1, pp. 178–185, Jan. 2007, doi: 10.1109/TPEL.2006.886600.

- [28] M. Khazraei, H. Sepahvand, K. A. Corzine, and M. Ferdowsi, "Active capacitor voltage balancing in single-phase flying-capacitor multilevel power converters," *IEEE Trans. Ind. Electron.*, vol. 59, no. 2, pp. 769–778, Feb. 2012, doi: 10.1109/TIE.2011.2157290.

- [29] H. Nademi, A. Das, and L. Norum, "Nonlinear observer-based capacitor voltage estimation for sliding mode current controller in NPC multilevel converters," in *Proc. IEEE Trondheim PowerTech*, 2011, pp. 1–7. doi: 10.1109/PTC.2011.6019429.

- [30] A.-M. Lienhardt, G. Gateau, and T. A. Meynard, "Stacked multicell converter: Digital sliding mode observation of flying capacitor voltages," in *Proc. IECON 32nd Annu. Conf. IEEE Ind. Electron.*, 2006, pp. 2115–2120. doi: 10.1109/IECON.2006.347799.

- [31] H. Chen, S. Tang, Z. Zeng, and J. Wang, "Flying capacitor voltages estimation in flying capacitor multilevel DC-DC converters based on peak inductor current detection and output voltage measurement," in *Proc. IEEE Energy Convers. Congr. Expo.*, 2020, pp. 5744–5750. doi: 10.1109/ECCE44975.2020.9235687.

- [32] G. Kampitsis, E. Batzelis, P. D. Mitcheson, and B. C. Pal, "A clamping-circuit-based voltage measurement system for high-frequency flying capacitor multilevel inverters," *IEEE Trans. Power Electron.*, vol. 37, no. 10, pp. 12301–12315, Oct. 2022, doi: 10.1109/TPEL.2022.3174062.

633

- [33] G. Gateau, M. Fadel, P. Maussion, R. Bensaid, and T. A. Meynard, "Multicell converters: Active control and observation of flying-capacitor voltages," *IEEE Trans. Ind. Electron.*, vol. 49, no. 5, pp. 998–1008, Oct. 2002, doi: 10.1109/TIE.2002.803200.

- [34] Y. Li and B. Wu, "A novel DC voltage detection technique in the CHB inverter-based STATCOM," *IEEE Trans. Power Del.*, vol. 23, no. 3, pp. 1613–1619, Jul. 2008, doi: 10.1109/TPWRD.2008.919251.

- [35] G. Farivar, A. M. Y. M. Ghias, B. Hredzak, J. Pou, and V. G. Agelidis, "Capacitor voltages measurement and balancing in flying capacitor multilevel converters utilizing a single voltage sensor," *IEEE Trans. Power Electron.*, vol. 32, no. 10, pp. 8115–8123, Oct. 2017, doi: 10.1109/TPEL.2016.2633278.

- [36] A. Ruderman and B. Reznikov, "Five-level single-leg flying capacitor converter voltage balance dynamics analysis," in *Proc. 35th Annu. Conf. IEEE Ind. Electron.*, 2009, pp. 486–491. doi: 10.1109/IECON.2009.5414970.

- [37] A. Ruderman, B. Reznikov, and M. Margaliot, "Simple analysis of a flying capacitor converter voltage balance dynamics for DC modulation," in *Proc. 13th Int. Power Electron. Motion Control Conf.*, 2008, pp. 260–267. doi: 10.1109/EPEPEMC.2008.4635276.

- [38] S. Thielemans, A. Ruderman, B. Reznikov, and J. Melkebeek, "Simple time domain analysis of a 4-level H-bridge flying capacitor converter voltage balancing," in *Proc. IEEE Int. Conf. Ind. Technol.*, 2010, pp. 818–823. doi: 10.1109/ICIT.2010.5472616.

- [39] A. Ruderman and B. Reznikov, "Simple time domain averaging methodology for flying capacitor converter voltage balancing dynamics analysis," in *Proc. IEEE Int. Symp. Ind. Electron.*, 2010, pp. 1064–1069. doi: 10.1109/ISIE.2010.5636907.

- [40] T. A. Meynard, M. Fadel, and N. Aouda, "Modeling of multilevel converters," *IEEE Trans. Ind. Electron.*, vol. 44, no. 3, pp. 356–364, Jun. 1997, doi: 10.1109/41.585833.

- [41] X. Yuang, H. Stemmler, and I. Barbi, "Self-balancing of the clamping-capacitor-voltages in the multilevel capacitor-clamping-inverter under sub-harmonic PWM modulation," *IEEE Trans. Power Electron.*, vol. 16, no. 2, pp. 256–263, Mar. 2001, doi: 10.1109/63.911150.

- [42] R. H. Wilkinson, T. A. Meynard, and H. du Toit Mouton, "Natural balance of multicell converters: The general case," *IEEE Trans. Power Electron.*, vol. 21, no. 6, pp. 1658–1666, Nov. 2006, doi: 10.1109/TPEL.2006.882951.

- [43] "Bitwise operation," Wikipedia. Wikipedia, Jun. 2022. [Online]. Available: https://en.wikipedia.org/wiki/Bitwise\_operation

- [44] TDK, "Characterization Sheet (Multilayer Ceramic Chip Capacitors)," C5750X6S2W225K250KA datasheet, Jan. 4, 2016. [Online]. Available: https://product.tdk.com/system/files/dam/doc/product/capacitor/ceramic/mlcc/charasheet/c5750x6s2w225k250ka.pdf

- [45] "Understanding oscilloscope bandwidth, rise time and signal fidelity," Tektronix, Oct. 2008. [Online]. Available: https: //people.ece.ubc.ca/robertor/Links\_files/Files/TEK-Understanding-Scope-BW-tr-Fidelity.pdf

**EFSTRATIOS I. BATZELIS** (Senior Member, IEEE) received the Ph.D. degree from the National Technical University of Athens, Athens, Greece, in 2016. Since 2021, he has been a Lecturer with the University of Southampton, Southampton, U.K. and a Research Fellow with the Royal Academy of Engineering, London, U.K., working on solar integration in developing countries. In 2019, he was a Research Fellow with Imperial College London, London, U.K., where he held an EU Marie-Curie individual Fellowship on photovoltaic control and

integration during 2017–2019 His research interests include renewable energy technologies and distributed energy resources, mainly solar photovoltaics, power electronics control, and power system dynamics and stability. He is currently an Associate Editor for the IEEE TRANSACTIONS ON SUSTAINABLE ENERGY.

ANTONIS KOLOKASIS (Member, IEEE) received the B.Eng. degree in electronic and electrical engineering from the University of Huddersfield, Huddersfield, England, and the M.Sc. degree in future power networks from Imperial College London, London, U.K., in 2020 and 2021, respectively. From 2021 to 2022, he was with Energy & Beyond LTD Electricity Supply Company of Green Energy Group, Limassol, Cyprus, as an Electricity Market Operator, working on solar power plant design and renewable energy trading. Since 2022, he has been

with the Cyprus Energy Regulatory Authority as an Energy Engineer, conducting research on the EU programs undertaken by the authority as part of its commitments for Research, Technological Development, and Innovation. The programs include development of emission reduction technologies, enabling smart grid technologies, and increasing penetration of RES and storage in Cyprus.