## **UNIVERSITY OF SOUTHAMPTON**

Faculty of Engineering and Physical Science Optoelectronics Research Center

# Memristor-based Spiking Neural Networks

by

Jinqi Huang

ORCiD: 0000-0003-3913-0067

A thesis for the degree of Doctor of Philosophy

November 2022

## **ABSTRACT**

Emerging non-volatile memory devices, known as memristors, have demonstrated remarkable perspective in neuromorphic hardware designs, particularly in spiking neural network (SNNs) hardware implementation. Memristor-based SNNs have been applied in solving tasks (e.g. image classification and pattern recognition) traditionally solved by conventional artificial neural networks (ANNs), and more attempts in varying disciplines are still being made to exploit the potential of this new research topic. To apply memristors in neuromorphic applications (strictly defined as applications using SNNs in this thesis), two pathways can be followed. One starts by characterising and controlling memristor devices by utilising hardware infrastructure, which is later mapped with the application's higher-level functions (e.g. matrix multiplications). Another embeds data-driven memristor models in software simulators to emulate the application with parameters extracted from real devices.

This thesis aims to build a cohesive pipeline for bringing memristor-based SNNs to practical use following these two pathways. To achieve this goal, three key designs have been developed. The first one is an FPGA-based digital interface that is part of a memristor characterisation and control system which enables 64-channel parallel read/write operations and high-speed data processing. The control system, developed by the author and two other researchers, not only acts as a testing tool for collecting memristor characteristics but also delivers higher-level functions with memristor arrays in neuromorphic designs. Whilst the thesis focuses on a usage scenario for memristors, this system includes more powerful, versatile testing functionality for other two-terminal emerging memory devices. The FPGA-based interface was developed by the author solely, and it achieves 64-channel level parallelism in the application aspect and complex digital system design and organisation in the engineering aspect. The digital interface is validated by resistor handling and current-voltage sweep experiments.

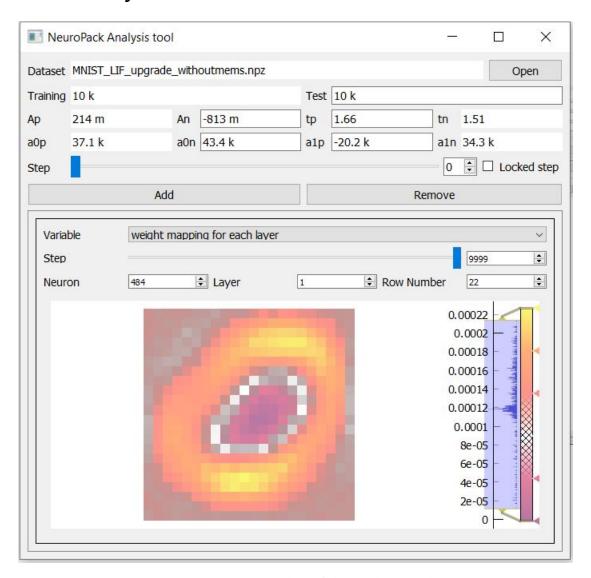

The second design is the first Python-based algorithm-level simulator, NeuroPack, for memristor-based SNNs with a data-driven memristor model. NeuroPack aims to allow users to quickly validate a neuromorphic concept in the pre-hardware design phase. This tool provides a wide range of optional neuron, plasticity, and device models for users to choose from and answers a fundamental question: is the design functional given the knowledge of the memristor switching dynamics, assuming that the rest of the design is functionally perfect? If yes, the design can move ahead towards the next step. Besides, NeuroPack stores internal variables, including membrane voltages, neuron firing history, and memristor states. With a built-in analysis tool, users can analyse and visualise inference results, observe the evolution of weights and membrane voltages and monitor memristor behaviours. A handwritten digit recognition task in the MNIST dataset showcased how NeuroPack assists users in confirming system validation and exploring sensitivity to critical design choices.

The third design tries to expand the usage of memristor-based SNNs to highdimensional large-scale applications. To do so, a bespoke simulation framework extended from the second design is developed. The first sentiment analysis task in the IMDB movie reviews dataset is exhibited with this framework. Two paths are taken to train spiking neural networks with memristor models: 1) by converting a pre-trained artificial neural network (ANN) to a memristorbased SNN, or 2) by directly training a memristor-based SNN. These two paths have two application scenarios: offline classification and online training. By converting a pre-trained ANN to a memristor-based SNN and training the mem ristor-based SNN directly, we achieve a classification accuracy of 85.88% and 84.86%, respectively, with the equivalent ANN achieving a baseline training accuracy of 86.02%. From ANNs to SNNs and from non-memristive synapses to data-driven memristive synapses, comparable classification accuracy can be achieved in simulation. In addition, investigations of the neural network sensitivity to global parameters such as spike train length, the read noise, and the weight updating stop conditions have also been given. These investigations further suggest that the simulation framework with statistic memristor models that use experimental data for statistical fitting taking the two paths presented in this chapter can help to exploit the potential of incorporating memristorbased SNNs in text classification tasks.

In summary, with the aid of the designs presented in this thesis, we envisage the two pathways now are complete to achieve neuromorphic applications with memristors, especially in performing text classification tasks. The thesis is

concluded with the achieved contributions and future perspectives toward AI hardware.

## **Contents**

| Li | st of 1 | Figures                                               |   |    |    |     |    | xi   |

|----|---------|-------------------------------------------------------|---|----|----|-----|----|------|

| Li | st of   | Tables                                                |   |    |    |     |    | xiii |

| Αı | uthor   | 's Publication List                                   |   |    |    |     |    | xv   |

| D  | eclara  | ation of Authorship                                   |   |    |    |     |    | xvii |

| A  | cknov   | vledgements                                           |   |    |    |     |    | xix  |

| A  | crony   | ms and Abbreviations                                  |   |    |    |     |    | xxi  |

| 1  | Intr    | oduction                                              |   |    |    |     |    | 1    |

|    | 1.1     | Context                                               |   |    |    |     |    | 1    |

|    | 1.2     | 0                                                     |   |    |    |     |    | 5    |

|    | 1.3     |                                                       |   |    |    |     |    | 7    |

|    | 1.4     | Thesis Outline                                        | • | •  | •  | •   | •  | 9    |

| 2  | Mer     | nristor-based Spiking Neural Networks: A Review in Th | e | or | et | tic | al |      |

|    |         | kground and Designs                                   |   |    |    |     |    | 13   |

|    | 2.1     |                                                       |   |    |    |     |    | 13   |

|    |         | 2.1.1 Spiking Neural Network Preliminaries            |   |    |    |     |    | 13   |

|    |         | 2.1.2 Memristor Preliminaries                         |   |    |    |     |    | 19   |

|    | 2.2     | Neuromorphic Designs at a Glance                      |   |    |    |     |    | 23   |

|    |         | 2.2.1 Hardware Frameworks                             |   |    |    |     |    | 23   |

|    |         | 2.2.2 Software Frameworks                             |   |    |    |     |    | 31   |

|    |         | 2.2.3 Applications                                    |   |    |    |     |    | 33   |

|    | 2.3     | Summary                                               |   |    |    |     |    | 35   |

| 3  | An l    | FPGA-based Digital Interface for Memristor Arrays     |   |    |    |     |    | 37   |

|    | 3.1     | Introduction                                          |   |    |    |     |    | 37   |

|    | 3.2     |                                                       |   |    |    |     |    | 39   |

|    | 3.3     | Design Implementation                                 |   |    |    |     |    | 41   |

|    | 0.0     | 3.3.1 Design Overview                                 |   |    |    |     |    | 41   |

|    |         | 3.3.2 Control Layer                                   |   |    |    |     |    | 42   |

|    |         | 3.3.3 Transmission Layer                              |   |    |    |     |    | 56   |

|    |         | 3.3.4 Clock Domain Crossing Synchronisation           |   |    |    |     |    | 57   |

|    | 3 4     | Experiments                                           | • | •  | •  | •   | •  | 58   |

viii *CONTENTS*

|    |      | 3.4.1           | Resistor Array handling                                     |            |

|----|------|-----------------|-------------------------------------------------------------|------------|

|    | 2 5  | 3.4.2<br>Discus | Memristor Current-Voltage Sweep                             |            |

|    | 3.5  | Discus          | ssion                                                       | 60         |

| 4  | Neu  | roPack          | : A Software Simulator for Memristor-based SNNs             | 63         |

|    | 4.1  | Introd          | uction                                                      | 63         |

|    | 4.2  | Metho           | ods                                                         | 65         |

|    |      | 4.2.1           | Design Overview                                             |            |

|    |      | 4.2.2           | Neuron Models and Learning Rules                            |            |

|    |      | 4.2.3           | Memristor Model                                             |            |

|    |      | 4.2.4           | Weight Mapping and Updating                                 |            |

|    |      | 4.2.5           | Customisation, usage scenarios and interface                |            |

|    | 4.3  |                 | ments                                                       | <b>7</b> 5 |

|    |      | 4.3.1           | Demonstration: NeuroPack Simulation of a Handwritten        |            |

|    |      |                 | Digit Recognition Task in the MNIST                         |            |

|    |      | 4.3.2           | R tolerance Sensitivity Exploration                         | 76         |

|    |      | 4.3.3           | Bias Method Comparison for Selector-based arrays and        |            |

|    |      | ъ.              | Selectorless Arrays                                         |            |

|    | 4.4  | Discus          | ssion                                                       | 80         |

| 5  | Text | Classif         | fication in Memristor-based SNNs                            | 83         |

| 0  | 5.1  |                 | uction                                                      |            |

|    | 5.2  | Metho           |                                                             |            |

|    | ·    | 5.2.1           | Methodology Overview                                        |            |

|    |      | 5.2.2           | Approach 1: Converting a Pre-trained ANN to an SNN          |            |

|    |      | 5.2.3           | Approach 2: Training an SNN directly                        |            |

|    |      | 5.2.4           | Adding Memristor Models                                     |            |

|    |      | 5.2.5           | Weight Updating Scheme                                      |            |

|    | 5.3  | Experi          | iments                                                      |            |

|    |      | 5.3.1           | Experiment Overview                                         |            |

|    |      | 5.3.2           | Results Analysis of Approach 1                              |            |

|    |      | 5.3.3           | Results Analysis of Approach 2                              |            |

|    | 5.4  |                 | usion                                                       |            |

|    | _    |                 |                                                             |            |

| 6  |      |                 | s and Future Perspectives                                   | 103        |

|    | 6.1  |                 | ary and Conclusions                                         |            |

|    | 6.2  | Future          | e Perspectives towards AI Hardware                          | 106        |

| Ar | pend | lix A           | Implementation Details of An FPGA-based Digital Inter       | r <b>-</b> |

| r  | _    |                 | emristor Arrays                                             | 107        |

|    |      |                 | A.1 DAC81416 registers reconfigurations                     |            |

|    |      |                 | A.2 Instruction Set                                         |            |

|    | 11   |                 |                                                             |            |

| Ap | _    |                 | Implementation Details of NeuroPack                         | 109        |

|    | App  |                 | 3.1 Derivation of back propagation for the leaky integrate- |            |

|    |      |                 | re neuron models (without winner-take-all)                  | 109        |

|    | App  |                 | 3.2 Derivation of back propagation for Leaky integrate-     |            |

|    |      | and-fi          | re neuron models (with winner-take-all)                     | 111        |

*CONTENTS* ix

| Appendix B.3   | Pseudo code for pulse parameter selection module         | 113        |

|----------------|----------------------------------------------------------|------------|

| Appendix B.4   | Main Panel GUI                                           | 114        |

| Appendix B.5   | Analysis Tool GUI                                        | 115        |

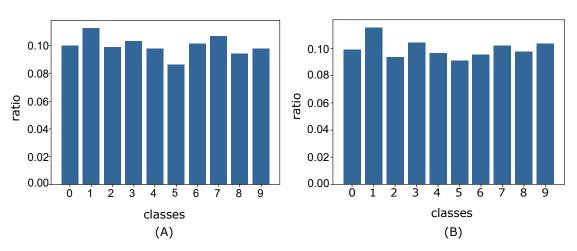

| Appendix B.6   | Dataset                                                  | 117        |

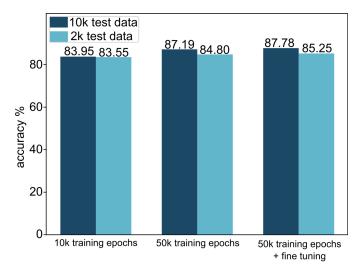

| Appendix B.7   | Accuracy improvement                                     | 118        |

| Appendix C Mat | hematical Derivation for Text Classification in Memristo | or-        |

| based Spiking  | Neural Networks                                          | <b>121</b> |

| Appendix C.1   | Relation between the memristor-based SNN firing rates    |            |

| and the e      | quivalent-ANN outputs                                    | 121        |

|                |                                                          |            |

# **List of Figures**

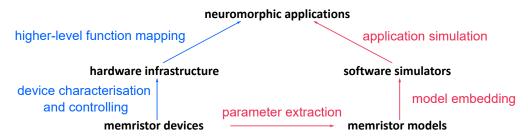

| 1.1  | Pathways for applying memristive technologies to applications .    | 5  |

|------|--------------------------------------------------------------------|----|

| 2.1  | Biology neural networks                                            | 13 |

| 2.2  | Membrane voltage changes when pre-synaptic spikes come             | 15 |

| 2.3  | Equivalent circuit of Hodgkin & Huxley model                       | 16 |

| 2.4  | Asymmetric STDP learning window                                    | 19 |

| 2.5  | Memristor crossbar                                                 | 20 |

| 2.6  | Memristors implement STDP                                          | 22 |

| 2.7  | Neuromorphic system designs in different scales                    | 24 |

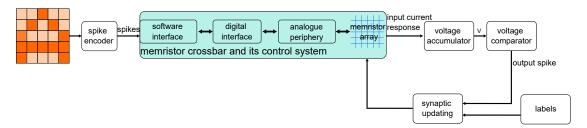

| 3.1  | Topology of a hybrid SNN with memristor arrays                     | 39 |

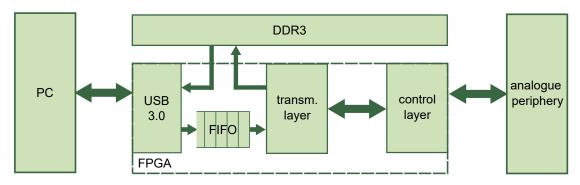

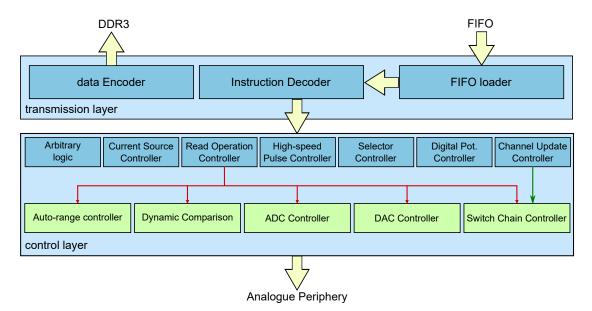

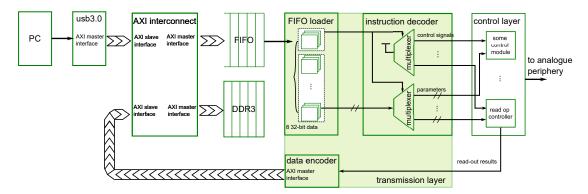

| 3.2  | Digital interface of memristor crossbar control system             | 41 |

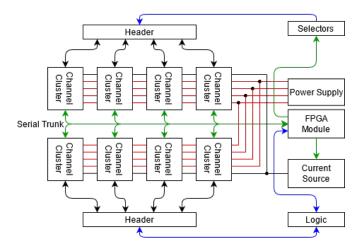

| 3.3  | Schematic of the analogue interface                                | 42 |

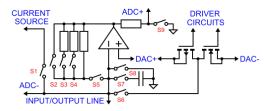

| 3.4  | Schematic of the channel circuit in the analogue interface         | 43 |

| 3.5  | Read and write operation in a selectorless memristor crossbar      | 43 |

| 3.6  | Hierarchy of the transmission layer and the control layer          | 44 |

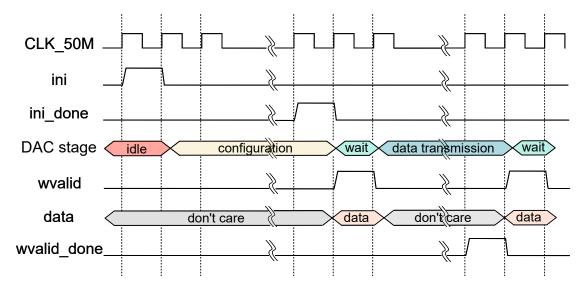

| 3.7  | DAC control module protocol                                        | 46 |

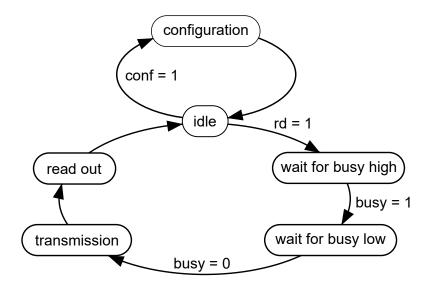

| 3.8  | ADC control module state machine                                   | 48 |

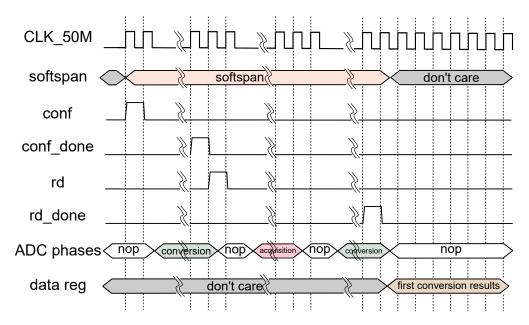

| 3.9  | ADC control module protocol                                        | 49 |

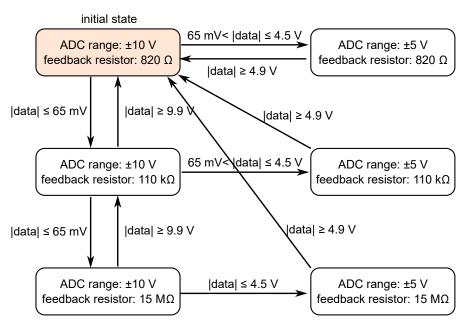

| 3.10 | Auto-range module state machine                                    | 51 |

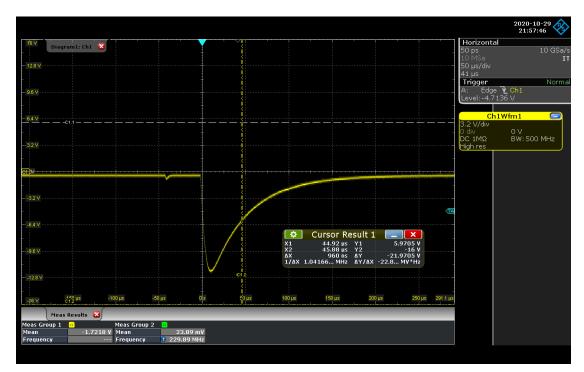

| 3.11 | Illustration of the large spike when changing states               | 53 |

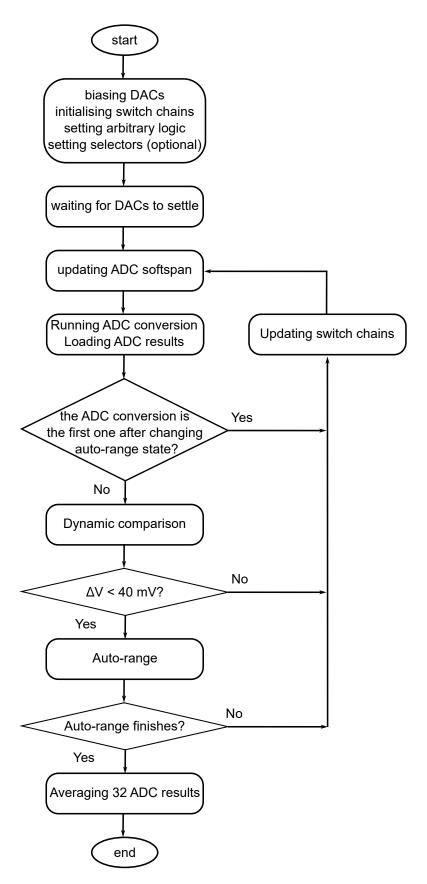

| 3.12 | Flowchart of the read operation                                    | 55 |

|      | Transmission layer                                                 | 56 |

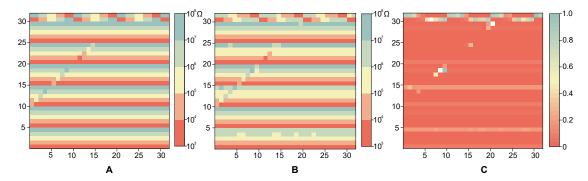

|      | Array read results for a $32 \times 32$ resistor array             | 58 |

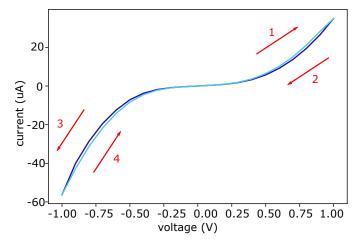

|      | IV sweep on a Pt (12 nm)/ TiOx (25 nm)/ AlOx (4 nm)/ Pt (15        |    |

|      | nm) memristor device                                               | 59 |

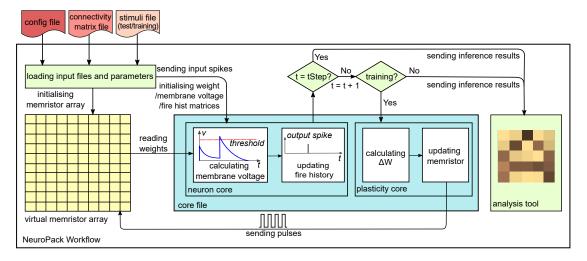

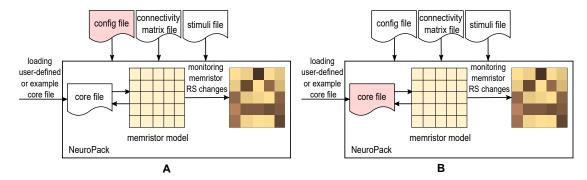

| 4.1  | NeuroPack workflow                                                 | 65 |

| 4.2  | Usage scenarios for NeuroPack                                      | 72 |

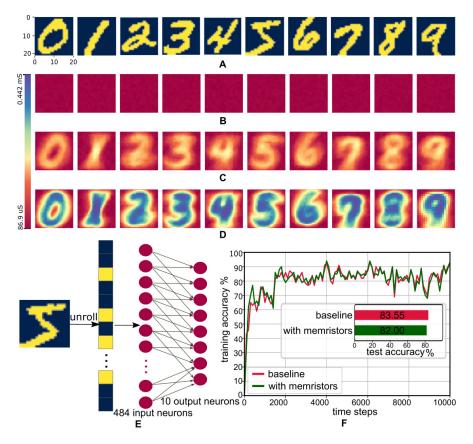

| 4.3  | Simulation of a handwritten digit recognition task with a TiOx     |    |

|      | memristor-based neural network in NeuroPack                        | 74 |

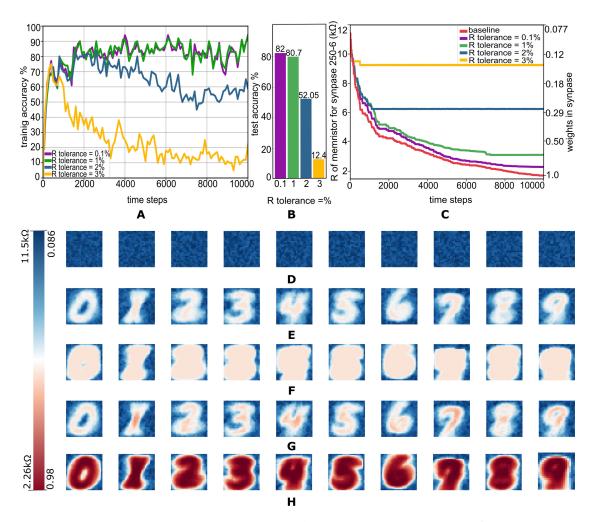

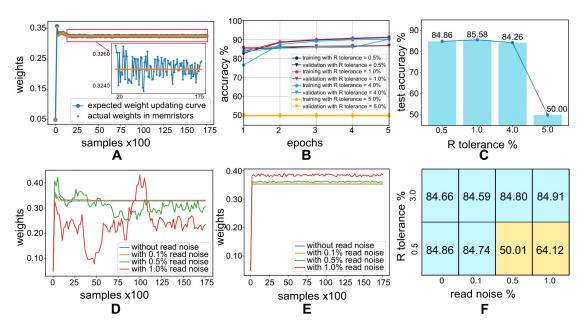

| 4.4  | Classification accuracy affected by <b>R tolerance</b>             | 77 |

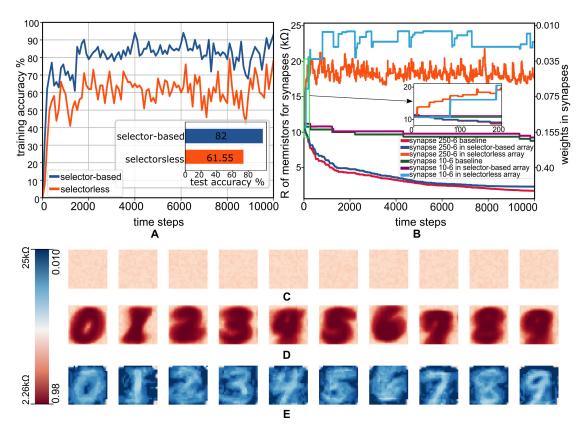

| 4.5  | Classification with versions using selector-based and selectorless |    |

|      | memristor arrays                                                   | 79 |

| 5.1  | Two approaches to obtain trained SNNs                              | 86 |

| 5.2  | Simulation framework workflow for performing the sentiment         |    |

|      | analysis task in the IMDR review dataset                           | 97 |

xii LIST OF FIGURES

| 5.3 Experime  | periments for the sentiment analysis task in the IMDB movie |  |  |  |  |  |

|---------------|-------------------------------------------------------------|--|--|--|--|--|

| reviews d     | ataset                                                      |  |  |  |  |  |

| 5.4 Result an | alysis for converting an ANN to a memristor-based SNN 99    |  |  |  |  |  |

| 5.5 Result an | alysis for directly training the memristor-based SNN $100$  |  |  |  |  |  |

| Appendix B.1  | Screenshot of the main panel                                |  |  |  |  |  |

| Appendix B.2  | Screenshot of the analysis tool                             |  |  |  |  |  |

| Appendix B.3  | Proportions of digits in the whole MINST training set       |  |  |  |  |  |

| and the cl    | hosen test set                                              |  |  |  |  |  |

| Appendix B.4  | Accuracy comparison between using 10k test data and         |  |  |  |  |  |

| 2k test da    | ta for different methods                                    |  |  |  |  |  |

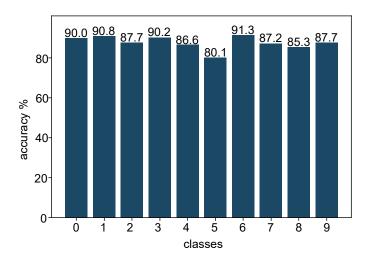

| Appendix B.5  | Test accuracy for each class                                |  |  |  |  |  |

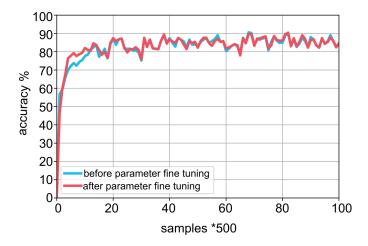

| Appendix B.6  | Training accuracy for running 50k epochs 119                |  |  |  |  |  |

## **List of Tables**

| 2.1 | Energy efficiency comparison of Von neumann machine, SRAM-     |    |

|-----|----------------------------------------------------------------|----|

|     | based in-memory computing design, and memristor-based in-      |    |

|     | memory computing designs                                       | 21 |

| 2.2 | A comparison among large-scale neuromorphic systems            | 25 |

| 2.3 | Comparison of four CMOS small-scale low-power designs          | 28 |

| 2.4 | FPGA-based small-scale neuromorphic designs                    | 29 |

| 2.5 | Comparison of memristor-based small-scale neuromorphic designs | 30 |

| 2.6 | Comparison of SNN and/or memristor-based NN Simulators         | 31 |

| 2.7 | Deep learning and Memristor-based SNN Applications             | 34 |

| 3.1 | DAC81416 control modules signals                               | 47 |

| 3.2 | LTC2358 control module signals                                 | 49 |

| 3.3 | Signals in auto range module                                   | 53 |

| 3.4 | Comparison between the instrument built with this work and     |    |

|     | similar systems                                                | 60 |

| 4.1 | Parameters used in NeuroPack for MNIST handwritten digit clas- |    |

| 1.1 | sification task                                                | 81 |

|     |                                                                |    |

| 5.1 | Test accuracy                                                  | 97 |

| 5.2 | Parameters used in the sentiment analysis task                 | 98 |

| Арр | endix A.1 DAC81416 configuration registers that need to be re- |    |

| 11  | configured                                                     | 07 |

| App | endix A.2 Instruction sets                                     |    |

#### **Author's Publication List**

- Jinqi Huang, Alexantrou Serb, Spyros Stathopoulos, and Themis Prodromakis: Text Classification in Memristor-based Spiking Neural Networks. *arXiv e-prints*, 2022, arXiv:2207.13729.

- Jinqi Huang, Spyros Stathopoulos, Alexantrou Serb and Themis Prodromakis: NeuroPack: An Algorithm-level Python-based Simulator for Memristor-empowered Neuro-inspired Computing. Frontiers in Nanotechnology, 2022, doi: 10.3389/fnano.2022.851856.

- Jinqi Huang, Spyros Stathopoulos, Alex Serb and Themis Prodromakis: A Tool for Emulating Neuromorphic Architectures with Memristive Models and Devices. 2022 IEEE International Symposium on Circuits and Systems, in proceeding, 2022

- Patrick Foster, Jinqi Huang, Alex Serb, Spyros Stathopoulos, Christos Papavassiliou, Themis Prodromakis: An FPGA-based System for Generalised Electron Devices Testing. Scientific Reports, 2022, doi: 10.1038/s41598-022-18100-3

- Patrick Foster, Jinqi Huang, Alex Serb, Themis Prodromakis, Christos Papavassiliou: An FPGA Based System for Interfacing with Crossbar Arrays. 2020 IEEE International Symposium on Circuits and Systems, 2020, pp. 1-4, doi: 10.1109/ISCAS45731.2020.9180671.

- Patrick Foster, Jinqi Huang, Alex Serb, Themis Prodromakis, Christos Papavassiliou: Live Demonstration: Electroforming of TiO2–x Memristor Devices using High Speed Pulses. 2020 IEEE International Symposium on Circuits and Systems, 2020, pp. 1-1, doi: 10.1109/ISCAS45731.2020.9180955.

### **Declaration of Authorship**

I declare that this thesis and the work presented in it is my own and has been generated by me as the result of my own original research.

#### I confirm that:

- 1. This work was done wholly or mainly while in candidature for a research degree at this University;

- 2. Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- 3. Where I have consulted the published work of others, this is always clearly attributed;

- 4. Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- 5. I have acknowledged all main sources of help;

- 6. Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- 7. None of this work has been published before submission

| Signed: | Date: |

|---------|-------|

### Acknowledgements

Firstly, I would like to thank my supervisors, Prof. Themis Prodromakis and Dr Alexander Serb, for leading me on the path toward becoming a qualified researcher. I would like to thank Prof. Michael Ng and Dr Nikitas Papasimakis as my administrative supervisors. I would also like to thank Prof. Geoff Merrett, Dr Adnan Mehonic, and Prof. Steve Gunn, my examiners in my final viva and during my PhD, for giving me helpful advice for conducting research and improving my technical writing. I would also like to thank my thesis committees for taking their precious time to organise the viva for me.

I would like to thank my lovely colleagues and friends, Dr Spyros Stathopoulos, Dr Firman Simanjuntak, Dr Shiwei Wang, Dr Sachin Maheshwari, Christos Giotis, Evangelos Moutoulas, Callum Aitchison, Patrick Foster, Jiaqi Wang, Yihan Pan, and Fan Yang for their professional and personal help and support.

On a personal note, I would like to thank my grandmother for letting me know she always has my back regardless of the situation. I would like to thank my friends Yi Yao, Qiang Gui, and Yitao Luo for giving me support and comfort even if with the distance.

Finally, I would like to thank myself for being courageous to move toward the direction I want without giving up, even with difficulties and challenges.

Jinqi

## **Acronyms and Abbreviations**

AI: artificial intelligence

AMBA: Advanced Microcontroller Bus Architecture

ANN: artificial neural network

BP: backpropagation

DRTP: direct random target projection

ECM: electrochemical metallisation memories

FIFO: first-in-first-out

**IMC:** In-memory computing

IP: intellectual property

LIF: Leaky Integrated-and-fired model

LRS/HRS: low/high resistive state

LTP/LTD: Long-Term Potentiation/Depression

MAC: multiplication-accumulation

MSE: mean-square-error

NIC: Neuro-inspired computing op-amp: operational amplifier PSP: postsynaptic potential

RS: resistive state

SNN: spiking neural network

STDP: spike-timing-dependent-plasticity

STE: straight through estimator

STP/STD: Short-Term Potentiation/Depression

TCM: thermochemical memories

TPU: tensor processing unit

VCM: valence change memories

WTA: winner-take-all

## Chapter 1

## Introduction

#### 1.1 Context

As a mainstream approach of artificial intelligence (AI), artificial neural networks (ANNs) have been widely employed in many disciplines, including pattern recognition [1, 2, 3], data mining [4, 5], system control [6], game playing [7], medical diagnosis [8, 9], financial data processing [10, 11], and machine translation [12], because of the generalisation ability and the computational power of deep neural networks. Loosely similar to biological neural networks, ANNs discard some biological properties to simplify the model. Spiking neural networks (SNNs), as new-generation ANNs [13], more closely mimic biological neural networks compared with their non-spiking predecessors [14]. Unlike traditional ANNs using continuous numerical values in computation, SNNs use spikes discrete in the time domain to encode information. In a time window, an SNN has one or more neurons firing and transmitting binary signals (all-or-nothing signals) called spikes through synapses. When a neuron receives spikes from neighbours, the membrane voltage increases or decreases depending on whether the synaptic potential is excitatory [15] or inhibitory [16]. The neuron then fires when the membrane voltage exceeds a certain threshold. After firing, the membrane voltage returns to a quiescent value, and the neuron cannot fire for a certain period.

There are some typical features of SNNs:

1. SNNs use binary spike trains to transmit information instead of continuous numerical values.

- 2. Temporal information, such as spike rates and the intervals between spikes, is applied in SNNs, to incorporate the binary spike coding method.

- 3. SNNs are highly event-driven because they only start calculation when spikes are received.

- 4. States of spiking neurons only depend on neurons' local information, such as firing states and spike timing.

- 5. Some SNNs involve recursion and recurrence, unlike the layer-to-layer propagation structure in ANNs. Therefore, the inference result is not given when propagated to the last layer as in ANNs, but when the first spike is generated.

These features bring SNNs great potential for lower energy consumption and better computational efficiency. Firstly, in traditional ANNs, the algorithm core is the dot product of input vectors and weight matrices. While in SNNs, a matrix multiplication turns into an addition because, in a single time step, each input can only be 1 or 0, resulting in less computational complexity [17]. Besides, conventional ANNs require computation for every input, while SNNs reduce the number of operations by only processing received spike events. The high sparsity of the spike trains not only further reduces energy consumption with fewer operations [17], but also increases robustness if the stochastic rate coding method is used [18]. To be more explicit, when using stochastic rate coding in SNNs, multiplication can be performed implicitly by using stochastic techniques. A typical case is where 2x stochastic bitstreams enter an AND gate. The statistics of computation dictate that the probability of a '1' at the output is the product of probabilities of '1' at the input streams, thus implementing multiplication in the probability domain. Naturally, the number of '1's within a time window along the output bitstream can be summed up to give an (approximate) reading of the probability number. In a similar manner, in SNNs, multiplication can be implemented implicitly, but more importantly, fault-tolerantly. Further, the scheme that neurons only process data from nearby splits the whole computation into smaller tasks, and each neuron only takes a small amount of workload. This operation scheme makes SNNs have higher fault tolerance because the work will be taken by nearby neurons if one is dead, though it requires re-training [19].

The typical way of implementing spiking neural networks in hardware is to process spikes and update neurons in discrete time steps. The simulation with 1.1. Context 3

a computing time step less than 1 ms can be regarded as meeting the real-time requirement because the biological time scale for cognition is 1 ms per inference. Some early works mapped spiking neural networks in parallel computers [20, 21, 22], clusters of multi-processor computer [23], hypercube supercomputer [24], or GPUs [25]. However, those designs hardly achieve the speed requirement of real-time simulation. Reference [25] is 1.5 times slower than real-time for a network with 100k neurons. Reference [21] can only run a realtime simulation in a network with less than 8k neurons. Reference [22] needs around 70 ms per time step to simulate an 8k-neuron network. Only reference [24] and reference [23] can achieve enough performance for real-time simulation of large scale spiking neural networks, with 0.1ms time step for running 64k and 100k neural network respectively [26]. For modern Von Neumann machines, given the limited computing resources, the network size and the speed need to be traded off. Therefore, the author predicts that for tasks that only require a small size of the network, the real-time requirement might be achieved. However, to scale up the network with a size similar to the brain, the runtime still overheads a lot.

When implementing SNNs, conventional computers have parallelism and memory bandwidth limits. From the system level, "neurons" are regarded as core computation units in SNNs, and neuron states need to be computed and updated concurrently within one time step [27]. The conventional sequential, centralised computation pattern can lead to long latency. From the architecture level, conventional Von Neumann architecture has separate computation units and memory. The bandwidth of communication between computation units and memory ('Von Neumann Bottleneck') [28] and the performance mismatch between them ('memory wall') [29, 30] are bottlenecks when frequent data movement is required. Compared with traditional ANNs, SNNs are based on a dynamic model, which requires storing both synaptic weights and internal potential. Since the SNNs model requires frequent data movement between memory and computation units, without sufficient memory bandwidth, large-scale SNNs implementation in conventional Von Neumann architectures is more communication-bounded than computation-bounded [26]. Von Neumann's bottleneck and memory wall also worsen the energy efficiency. For example, addition and multiplication of 32-bit floating-point operations take around 0.9pJ and 3.7pJ, respectively, in a 45nm technology with the power supply of 0.9 V, while accessing 64-bit data from DRAM takes 1.3-2.6nJ [30].

Some dedicated hardware designs have been delivered with a solution to place

computing units and memory closely. Those designs include TrueNorth from IBM [31], Loihi from Intel [32], Neurogrid from Stanford University [33], Brain-ScaleS from University of Heidelberg [34], SpiNNaker from University of Manchester [35]. Those designs apply distributed memory, place neurons and synapses closer to diminish the communication cost, and support massive parallelism. With the new architecture, they show promising performance in SNN implementation. TrueNorth, Loihi, Neurogrid and SpiNNaker all achieve real-time SNN simulation with 16M, 128k, 1M, and 460M neurons, respectively. Brain-ScaleS even speeds up 10000 times faster than real-time with the support of 3.6M neurons. Dedicated neuromorphic hardware outperformed general-purpose computers in both speed and energy efficiency, despite the lack of flexibility in choosing neuron models and on-chip learning rules (if implemented) and the inconvenience of accumulating weighted spikes. Besides, FPGAs are also used to speed up the neural networks, for both spiking [17, 36, 37, 38, 39, 40] and non-spiking [41, 42, 43, 44, 45, 46] versions, because of the programmability, the sufficient resources and fine-grain parallelism.

In-memory computing (IMC) is a solution to problems caused by Von Neumann architecture. In this thesis, IMC is strictly defined as the computing method based on a 2D crossbar array. The computing method that places computing units and memory closely to reduce communication costs is called 'nearmemory computing' instead. Instead of shifting data between memory and processing units, computations are performed where data are stored [47]. Based on a 2D array structure, efficient matrix multiplication is realised by storing one operand in a memory array while applying another operand to activate the rows of memory elements. The multiplication-accumulation (MAC) results are read from the array's columns. IMC is more efficient considering speed and energy than conventional Von Neumann hardware [48]. From the speed aspect, reference [49] shows that, in theory, the latency of accessing D bits data from a  $\sqrt{D} \times \sqrt{D}$  SRAM array in a conventional way is D times as long as that of in IMC way in the worst case. From the energy aspects, reference [50] estimates the energy consumption of 4-bit MACs and 1024 dimensional vectors with 1bit memory storage in 45nm technology. The total energy of memory accessing and computation is around 550fJ in the Non-IMC case, whilst the total energy is 50fJ in the IMC case. Design [51] also reports around 450 times better energy efficiency than Google TPU [52] ( $\sim$ 866 TOPS/W versus  $\sim$ 2 TOPS/W). References [53], [54], and [55] also successfully implement IMC in SNN hardware designs, showing IMC a promising approach to perform SNNs.

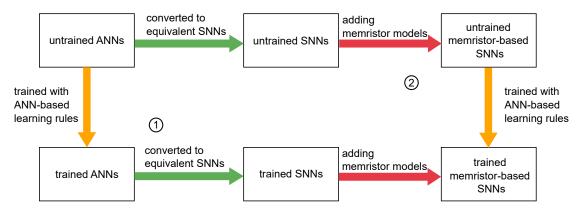

FIGURE 1.1: Pathways for applying memristive technologies to applications.

Memristors, firstly introduced by [56] as two-terminal circuit elements characterised by a relationship between the charge and the flux-linkage, are the fourth basic circuit element. Under this category, one important type is random-access memory devices (RRAM), cutting-edge memory that can be used for in-memory computing applications. Memristors are commonly organised in crossbar arrays, which can serve as matrix-vector multiplication accelerators [57, 58]. By setting one operand as input voltages from the rows and storing another operand as resistance in the array, the multiplication results can be easily calculated as currents along with the columns, directly following Ohm's law and Kirchhoff's current law. References [59], [60], [48], [61], [62], and [63] have performed matrix multiplication acceleration using memristor crossbar arrays in feedforward neural networks, convolutional neural networks, and long shortterm memory. Compared with SRAM, memristors are better memory devices for implementing IMC-style SNNs, because of multi-bit storage ( $\sim$ 6.5 bits [64]), high speed (85ps [65] vs. <10ns for SRAM [66]), low power consumption (10f] [67] vs 50fJ in SRAM [49] and non-volatility [68]. Multi-bit storage allows a single cell to store more information, while non-volatility can store trained parameters without external memory if on-chip training is planned. In the example of [69], memristors have been used to accelerate SNNs. Besides, the inherent physical characteristics of memristors show high similarity to biological synapses to support the spike-timing-dependent-plasticity (STDP) learning rule [70], which is a popular learning rule in SNNs. Having the ability to implement STDP in memristor arrays makes it possible to train memristive spiking neural networks. References [71], [72], and [73] have applied on-chip learning in memristor-based SNNs.

### 1.2 Motivations and Challenges

Figure 1.1 illustrates two pathways for applying memristive technologies to neuromorphic applications. In general, neuromorphic designs can both mean designs that target revealing the mystery of brain functions, or that use bioinspired architectures to perform AI tasks. In this thesis, neuromorphic applications are strictly defined as AI tasks, and neuromorphic designs are strictly

defined as designs that use SNNs to perform AI tasks, unless stated. With memristor devices ready, we can first utilise hardware infrastructure to characterise

and control devices, then map the higher-level functions in the hardware infrastructure to perform neuromorphic applications in hardware. Alternatively, we

can also extract memristor parameters to model devices and embed the device

models in software simulators to predict the outcomes of the applications before

hardware efforts are dedicated. This pathway is for functionality validation and

performance prediction mainly. The vast majority of works [71, 72, 73, 74, 75, 76]

that focus on hardware implementations of the memristor-based spiking neural networks follow the first path, whilst there is also a work [77] following

the second path to predicting the system functionality and performance in the

pre-hardware design phase.

Despite multiple works successfully performing neuromorphic applications by taking the two paths, some facilities are still missing to complete the pathways to become mature guides for researchers to follow. Hardware infrastructure in the first path has two primary functions: (1) it acts as a testing and control system to handle devices, and (2) it delivers higher-level functions such as matrix multiplications with the incorporation of a memristor array to perform a neuromorphic application. For one thing, memristors, usually simplified as two-terminal tuneable resistors with non-linear switching dynamics, require specified characterisation, such as current-voltage sweep and incremental pulsing, for researchers to gain more intuition about the intrinsic physical properties. For another, memristors arranged in array structure further request a control and testing system that can provide read/write parallelism and high-speed data acquisition to match the parallelism of a neuromorphic design. Existing memristor characterisation systems either stay in the conceptual stage without physical experiments [78, 79] or do not provide read/write parallelism [80].

In the software simulator aspect, the software simulators in the second path undertake the task of modelling memristor devices, validating neuromorphic concepts, and elaborating device- and weight updating protocol-related details. Existing simulators [81, 82] focus more on the circuit level to emulate the hardware module behaviours in neuromorphic designs and to predict the performance specifications in chip designs. A simulator that (1) incorporates statistic device models, (2) sits at the algorithm level to validate the functionality of the

1.3. Contributions 7

neuromorphic concept before committing efforts in hardware design, and (3) provides step-by-step details in performing a neuromorphic task for investigation of system sensitivity is still missing.

In the application aspect, a vast range of neuromorphic applications with memristors in different disciplines have been achieved, including pattern recognition and image classification [74, 75, 76, 83]. However, memristor-based SNNs' usage is now limited to low-dimensional small-scale applications. This is because there are three major issues for expanding memristor-based SNNs in performing high-dimensional large-scale applications: high-dimensional inputs, costly training, and memristor non-ideality. To be specific, high-dimensional inputs require large memory allocation, which is costly in implementing memristorbased SNNs. For example, text classification, a particular area in natural language processing, often requires more than 10k dimensional inputs. Dimension reduction technology such as word embeddings, (e.g. GloVe [84] and word2vec [85]), are commonly used to map high-dimensional inputs to dense lower-dimensional representation for better space efficiency. However, no historical work has revealed the theoretical foundation of training a dimension reduction model such as a word embedding layer in a spiking neural network. Besides, both local (e.g. e-prop [86]) and non-local [87] gradient-based learning rules require accumulating the errors over a spike train window that is used to represent a single numerical value. This computation has poor speed and space efficiencies, especially when the spike train window is large and memristors are involved. Lastly, memristors introduce non-idealities due to the read noise and the write variation. These issues make training a memristor-based spiking neural network for text classification challenging.

In conclusion, to complete the pathways to apply memristor devices in neuromorphic designs, more practical efforts must be committed to constructing hardware infrastructure, software simulators, and methodology for specific applications.

### 1.3 Contributions

To address the above-mentioned needs, this thesis presents three designs to complete the two pathways shown in Figure 1.1. The first one is an FPGA-based digital interface that can be used to build a memristor characterisation and control system with 64-channel parallel read/write operations and high-speed data

processing. The full control system not only acts as a testing tool for collecting memristor characteristics but also maps higher-level functions for device handling in neuromorphic designs. Furthermore, this system provides more powerful, versatile testing functionality for other two-terminal emerging memory devices beyond memristors. Resistor array handling and current-voltage sweep experiments are shown for functional validation of the digital interface.

The second design presented in this thesis is the first Python-based algorithmlevel simulator, called NeuroPack, for memristor-based neuromorphic designs with an empirical memristor model [88]. With a wide range of selectable neuron, plasticity, and device models and the compatibility with user-defined models, NeuroPack assists users to quickly validating memristor-based neuromorphic concepts and monitoring the devices' behaviours during the training or the inference phase before serious efforts are committed in hardware designs. Besides, NeuroPack also stores internal variables, including membrane voltages, firing history, and weights for every single time step during the simulation. With a built-in result analysis tool, these data can be further used for analysis and visualisation so that users can investigate how intimately global parameters and critical design choices affect system performance. A 'predict-writeverify' loop also is proposed as the weight updating protocol implemented in NeuroPack to find the suitable pulsing parameter sets to trigger memristor state changes. This approach solves the challenge of precise memristor resistance update control due to the non-linear switching dynamics. Finally, an MNIST handwritten digit recognition task performed in a single-layer spiking neural network with the leaky integrated-and-fire neuron model [89] and winner-takeall structure [90] is showcased as a usage example of NeuroPack. With the final classification accuracy of 82.00% given the parameter settings, the accuracy degrades 1.55% compared with the accuracy achieved by the equivalent structure without memristive synapses.

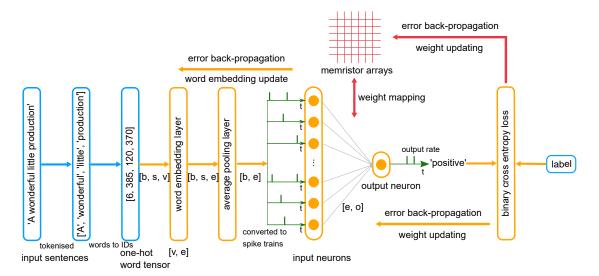

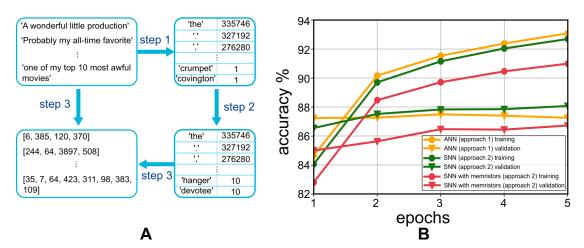

The third design solved the issues of high-dimensional inputs, costly training, and memristor non-ideality in expanding memristor-based SNNs in high-dimensional large-scale applications by extending NeuroPack for a bespoke simulation framework with [91] to enable GPU compatibility and taking two paths to obtain trained spiking neural networks with memristor models: 1) by converting a pre-trained artificial neural network (ANN) to a memristor-based SNN, or 2) by directly training a memristor-based SNN. These two paths have two application scenarios: offline classification and online training. The

1.4. Thesis Outline 9

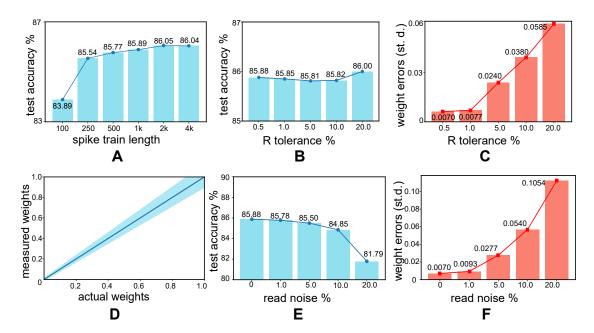

first demonstration of a text classification task has been executed in memristor-based spiking neural networks with a data-driven memristor model [88] using the developed simulation framework. The task is to perform sentiment analysis in the IMDB movie reviews dataset [92]. By converting a pre-trained ANN to a memristor-based SNN and training the memristor-based SNN directly, the classification accuracy of 85.88% and 84.86% are achieved, respectively, with the equivalent ANN achieving a baseline training accuracy of 86.02%. From ANNs to SNNs and from non-memristive synapses to data-driven memristive synapses, comparable classification accuracy is achievable in simulation. In addition, investigations of the neural network sensitivity to global parameters such as spike train length, the read noise, and the weight updating stop conditions have also been given.

The contributions of this work are summarised below:

- Developed and benchmarked an FPGA-based digital interface that allows channel-level parallelism and high-speed data processing for memristor array testing and control.

- 2. Designed the first algorithm-level simulator for memristor-powered neuro-inspired computing with selectable neuron, device and plasticity models, and elaborated the neural network sensitivity to device-related parameters with the demonstration of an MNIST handwritten digit recognition task performed in the presented simulator.

- 3. Demonstrated the first text classification task in the IMDB movie reviews dataset in spiking neural networks with a realistic memristor model by taking two different approaches to obtain trained neural networks, and explored system sensitivity to global parameters.

#### 1.4 Thesis Outline

The thesis has six major chapters: chapter 1 presents the context of SNNs, their main features, their advantages over traditional ANNs, and the promising potential of memristor-based SNNs. Next, the current obstacles to developing memristor-based SNNs are introduced. Later, the contributions of the works aiming at addressing the previously mentioned issues are listed. These works will be the focus of this thesis.

Chapter 2 presents the theoretical background and historical designs of memristor-based neuromorphic applications and their relatives. Starting from the basic concepts of SNNs and memristors, historical efforts of neuromorphic hardware designs, including large-scale frameworks and low-power systems in CMOS, FPGAs, and memristors, are described. Next, research in software simulators for both spiking neural networks and memristor-based neural networks is summarised. Finally, the applications of text classification are shown as examples. As there is no existing memristor-based solution for text classification, the thesis introduces the mainstream solutions of using deep learning for text classification and typical memristor-based SNN applications to find out the existing challenges of utilising memristor-based SNNs in text classification tasks that this thesis needs to address. The needs for conducting the research presented in this thesis are concluded from all mentioned historical designs.

In chapter 3, an FPGA-based digital interface for memristor arrays is introduced. This work addresses the need to build a control system that can provide read/write parallelism and high-speed data processing for device characterisation and functionality delivery in a board-level neuromorphic design. The chapter starts with the introduction of the background, motivations, contributions, and objectives, followed by the design implementations of the system, from the system overview to specified modules. A resistor array handling and a memristor current-voltage sweep experiments are delivered to validate the interface's functionality. Finally, the control system built with this digital interface is compared with other similar works, and the conclusion is given.

Chapter 4 presents a Python-based algorithm-level simulator for memristor-based SNNs. This work aims at acting as a flexible tool for users to quickly validate the neuromorphic concepts before efforts are made in hardware designs and assisting users in exploring system sensitivity to specified parameters in simulation. This work provides a range of device, neuron, and plasticity models for users to choose from. The background, motivations, and contributions are firstly introduced to start the chapter. Next, the design implementations are displayed with a top-down workflow. Critical parts of the design, including the neuron models, plasticity models, memristor models, and weight updating scheme, are described. After that, the experiments of an MNIST handwritten digit recognition are presented to validate the simulator, and the investigation is delivered to find out how the device- and updating protocol-related parameters affect system performance.

1.4. Thesis Outline

In chapter 5, the demonstration of a text classification task in the IMDB movie reviews dataset is performed in a memristor-based SNN with an empirical memristor model. This example takes two different paths to obtain a trained memristor-based spiking neural network: one is converting a trained ANN to its equivalent memristor-based SNN, and another is training a memristor-based SNN directly. To do so, a simulation framework using memristor models is developed. The chapter is started with the background, motivations and contributions. Next, the methodology used to perform this text classification task is given, with critical design details elaborated. Finally, the experimental results with standard configurations and varying parameter values are displayed, and the result analysis is given.

Lastly, in chapter 6, the thesis is summarised, the achieved contributions of this thesis are concluded, and future perspectives toward AI hardware are exhibited.

## **Chapter 2**

# Memristor-based Spiking Neural Networks: A Review in Theoretical Background and Designs

### 2.1 Memristor-based SNNs Theoretical Background

This section will introduce SNN and memristor basics to give a theoretical background of memristor-based SNNs.

### 2.1.1 Spiking Neural Network Preliminaries

When implementing an SNN, there are some aspects to think about: (1) structure of the networks, (2) coding schemes, (3) neuron models, and (4) learning rules. In this subsection, those aspects of SNN will be introduced.

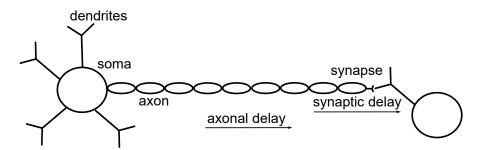

FIGURE 2.1: Biological neural network structure [17].

#### 2.1.1.1 Network Structure

Figure 2.1 shows the structure of biological neural networks. Biological neural networks consist of dendrites, soma, axon, and synapses. Dendrites receive presynaptic spikes, and the soma accumulates the voltage. If a spike is emitted, it transmits through the axon and synapses to other neurons. SNNs are artificial neural networks that mimic biological neural networks. Therefore, a complete SNN also consists of those four parts, though the axon and dendrites sometimes are omitted in simulation to simplify the design. At a network level, there are also some commonly used types of SNN architectures, including winner-take-all networks [93] and liquid state machine [94].

#### 2.1.1.2 Coding Schemes

Unlike ANNs using continuous numerical values in computation, SNNs deliver and process information through spike trains. Those discrete all-or-nothing binary signals with precise timing information allow SNNs to incorporate temporal information into the computation. That leads to the first question when implementing an SNN: which coding scheme to choose? There are two popular choices: rate coding and temporal coding. Rate coding is the coding method that only cares about the frequency of spike events, whilst temporal coding also conveys information through the timing of spikes. For example, spike sequences 0001100011 and 0101010101 deliver different information in temporal coding, whilst no difference is recognised in rate coding. Temporal coding can deliver more information, whereas rate coding is easier to implement. The vast majority of designs utilised rate coding because of its simplicity, whilst some designs insisted on temporal coding to provide more biological plausibility.

#### 2.1.1.3 Neuron Models

An SNN is formed by a group of neurons that serve as computation units in the network. Therefore, choosing neuron models becomes a fundamental question in implementing an SNN. Generally speaking, a spiking neuron model works by changing membrane voltage, also called postsynaptic potential (PSP), according to the weighted sum of the incoming spike train. Notice that the potential changes can be bidirectional: the PSP can either inhibit or excite future firing, and the corresponding PSPs in these cases are IPSP and EPSP, respectively. Usually, IPSP can be regarded as the case of a negative weight in traditional

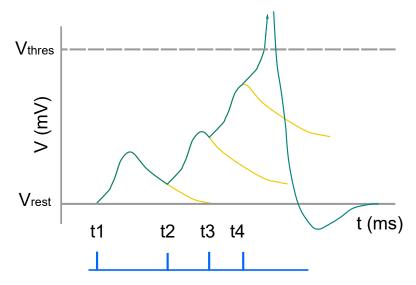

FIGURE 2.2: Membrane voltage changes when pre-synaptic spikes come. The image is from [95]. The x-axis is the time with the unit of ms, and y is the membrane voltage with the unit of mV. The blue spikes at the bottom show the incoming spike at time steps t1 to t4. When there is an incoming spike, the membrane starts accumulating, reaches the peak, and then decays. If the membrane voltage exceeds the threshold, a spike is generated, and the membrane voltage is reset.

ANNs. After the PSP exceeds the threshold, the neuron fires and the PSP is reset to zero. Figure 2.2 depicts the tendency of membrane voltage changes when spikes come.

Most spiking neuron models describe the relationship between input current response and output membrane voltage. The input current response expression is shown below:

$$u_i(t) = \sum_{j \neq i} w_{ij} x_{ij} + b_i \tag{2.1}$$

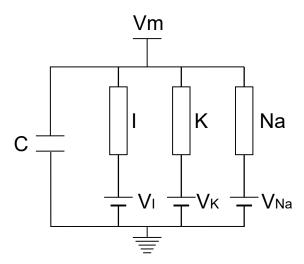

Where  $u_i$  is the synaptic response current,  $w_{ij}$  is the synaptic weight from neuron j to i,  $x_{ij}$  is the spike input,  $b_i$  is the constant bias. Among these types of neuron models, the most biological-like one is Hodgkin & Huxley model [96], which is based on a circuit model with resistors and capacitors shown in Figure 2.3, to mimic the effect of neurotransmitters between neurons. This model has a very complex form, shown below:

$$I_m = C\frac{dV_m}{dt} + G_l(V_m - V_l) + G_K(V_m - V_K) + G_{Na}(V_m - V_{Na})$$

(2.2)

Where  $V_m$ , and  $I_m$  are the membrane voltage and current, respectively, C is the capacitance,  $G_K$ ,  $G_{Na}$  are the potassium and sodium conductance,  $V_K$ ,  $V_{Na}$

FIGURE 2.3: Equivalent circuit of Hodgkin & Huxley model [95].  $V_m$  is the membrane potential. C represents the lipid bilayer. Voltage-gated potassium and sodium ion channels are represented by resistance  $R_K$  and  $R_{Na}$ , respectively.  $V_k$  and  $V_{Na}$  are potassium and sodium reversal potentials.  $R_I$  and  $V_I$  are leaky resistance and leaky reversal potential.

are reversal potentials <sup>1</sup> of potassium and sodium, and  $G_l$  and  $V_l$  are leak conductance and leak reversal potential. Here,  $G_K$ ,  $G_{Na}$  are time and voltage-dependent with more internal variables.

Hodgkin & Huxley model successfully model the biophysical property of ionchannel-based neuron membrane voltage changes. However, due to the complex form, it is computationally expensive to apply Hodgkin & Huxley model in SNN simulation. A neuron in Hodgkin & Huxley model takes 1200 floating points operations per time step (typically 1 ms for real-time), and four internal variables are required to store in memory [97, 98].

The Leaky Integrated-and-fired model (LIF) is a simple neuron model that is computationally efficient. The mechanism of LIF can be represented as equations below [99]:

$$\dot{v}_i(t) = \begin{cases} -\frac{1}{\tau}(v_i(t) - v_{rest}) + u_i(t) & \text{if not firing} \\ 0 & \text{otherwise} \end{cases}$$

(2.3)

Where  $u_i$  is the synaptic response current,  $v_i$  is the membrane potential,  $v_{rest}$  is the rest voltage usually assumed to be zero, and  $\tau$  is the leaky time constant. The incoming spikes change the membrane voltage with the amounts according to the synaptic weights, and the neuron fires a spike if the voltage

<sup>&</sup>lt;sup>1</sup>Reversal potential: the membrane potential when the ion channel is open

passes the threshold. After firing a spike, the membrane voltage resets to 0. Notice that the integration is leaky, given by the leaky term for membrane voltage. If there is no incoming spike, the membrane voltage will reduce gradually with the time constant  $\tau$ . The integrated-and-fire neuron model is the simplified version of the Hodgkin & Huxley model, with the spikes' shape neglected. Spikes for the integrated-and-fire neuron model are always uniform so that only the time of appearance matters. The LIF neuron model only takes 4-5 FLOPs for one time step, and only one internal variable, the membrane voltage, is needed to store in memory [97, 98]. Some variants of IF or LIF can exhibit more biological attributes while keeping the computational efficiency. Those variants includes adaptive integrated-and-fire model [100], fractional-order leaky integrated-and-fire model [101, 102], exponential integrated-and-fire model [104], etc.

Izhikevich neuron model is another neuron model that is a good compromise between the biological plausibility of the Hodgkin & Huxley model and the computational efficiency of the integrated-and-fire neuron model [105]. It is also a simplified version of the Hodgkin & Huxley model while still keeping the shape of spikes to produce the spiking and bursting dynamics. The equation of the model gives below:

$$v' = 0.04v^2 + 5v + 140 - u + I$$

$u' = a(bv - u)$  (2.4)

Where v is the membrane potential, u is the membrane recovery variable which represents  $K^+$  and  $Na^+$  ionic currents in the Hodgkin & Huxley neuron model. The term  $0.04v^2 + 5v + 140$  was attained by fitting the observation of neuron dynamics. a and b are internal parameters for recovery variable u. It takes 14 FLOPs per time step, and only two variables are required to store in memory [97, 98]. Apart from these classic models, some are based on IF with stochasticity, such as the spike response model [106]. In general, if the design targets precise simulation of biological neural networks, Hodgkin & Huxley model should be applied; if the design focuses on computational efficiency, IF or LIF neurons should be applied; if the design trades off between computational efficiency and biological plausibility, Izhikevich neuron model, SRM, and IF variants can be utilised [97].

# 2.1.1.4 Learning Rules

Efficient adaptation and accurate inference of a learning system depend mainly on effective learning rules. For ANNs, the most common updating rule is gradient descent [87] with error backpropagation [107]. However, spiking neurons have internal state variables related to the sum-up of the input spikes, making the cost function non-differentiable. Therefore, the traditional supervised learning updating rules cannot be directly used in SNNs. SNNs updating rules are more inspired by natural neural processes and are more similar to Hebb's rule <sup>2</sup>[108], which attempted to explain synaptic plasticity. Synaptic plasticity refers to the ability to adjust synaptic connections between neurons. This adjustment can be Long-Term Potentiation (LTP)/ Long-Term Depression (LTD) if effects last for hours or Short-Term Potentiation (STP)/ Short-Term Depression (STD) if effects only last for seconds or minutes. One of the most popular updating rules for SNNs is Spike-Timing Dependent Plasticity (STDP) [70], discovered in biological research. STDP tells us that synaptic plasticity is highly sensitive to the precise timing of the post-synaptic spikes related to pre-synaptic spikes. In other words, if the pre-synaptic spike comes earlier than the post-synaptic one, it will cause LTP; otherwise, LTD. The precise effect was given in [109] as below:

$$\Delta W_j = \sum_{f=1}^{N} \sum_{n=1}^{N} W(t_i^n - t_j^f)$$

(2.5)

Here  $\Delta W_j$  is the weight change of a synapse from pre-synaptic neuron j.  $t_i^n$  and  $t_j^f$  give the timing of post-synaptic and pre-synaptic spikes respectively, where n, f = 1, 2, 3 ...counts post/pre-synaptic spikes. W(x) is an STDP learning window, of which a common choice is as below [109]:

$$W(x) = \begin{cases} A_{+}exp(-x/\tau_{+}) & \text{for } x > 0\\ -A_{-}exp(-x/\tau_{-}) & \text{otherwise} \end{cases}$$

(2.6)

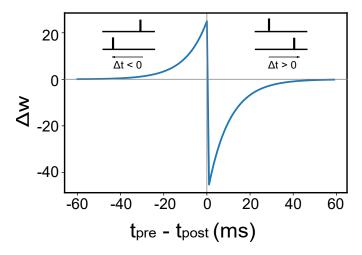

Parameters  $A_+$ ,  $A_-$  are scaling factors, and  $\tau_+$ ,  $\tau_-$  are time constants which are usually  $\pm 10ms$ . Figure 2.4 shows this common choice of STDP window for induction of potentiation and depression characteristics with pre- and post-synaptic spiking timing.

STDP appears as a possible updating rule to underpin temporal Hebb's rule in SNNs. However, STDP is a timing-sensitive algorithm, and having timing as a

<sup>&</sup>lt;sup>2</sup>Hebb's rule: A neuroscientific theory that synaptic efficacy increases when receiving persistent and repeated input stimuli.

FIGURE 2.4: Asymmetric STDP learning window [70]. The plot is generated with  $A_+ = 50$  and  $A_- = 25$ .

variable also needs precise control in hardware. Besides, STDP as an unsupervised learning rule requires adaptation to be explored to empower supervised learning tasks. Insufficiently development in learning algorithms underlies the main obstacle for making most of SNNs. It is believed that SNNs, compared with DNNs, are more of a long-term goal for researchers in neuromorphic area [95].

## 2.1.1.5 SNNs vs. ANNs

Here is a brief comparison in terms of energy consumption and speed between ANNs and SNNs: [110] showed the estimated energy consumption ratio between ANNs and SNNs is 1.72. When running ANNs and SNNs in the same digital platform, an inference in ANNs requires 2 FLOPs, and an inference in LIF-based SNNs requires 4-5 FLOPs. Given the limited computing resources, ANNs can be up to 2.5 faster than SNNs.

# 2.1.2 Memristor Preliminaries

#### 2.1.2.1 Memristor Features

One critical point to emulate biologic neural networks is to use suitable devices to represent synapses. Non-volatility [68], multi-bits storage capability [64], low power consumption, and fast access time [111] make memristors good candidates [48]. First of all, the change of electric stimuli can switch the devices between low resistive (ON state) and high resistive (OFF state) [112], while

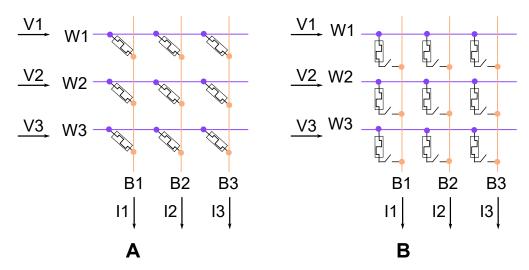

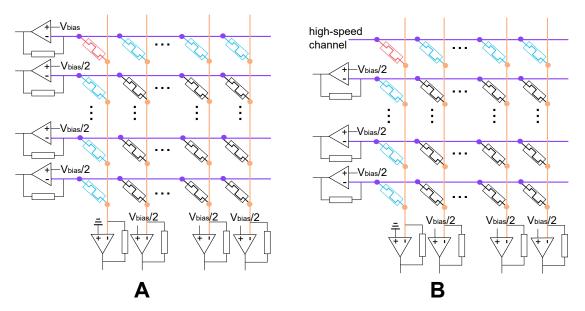

FIGURE 2.5: Memristor array without selectors **(A)** and with selectors **(B)**. Wordlines and bitlines are coloured in purple and orange, respectively. Notably, the crosspoints between wordlines and bitlines are not connected. When running in-memory computing in a memristor array with selectors, switches for selected devices are closed.

the resistive state will be retained after the voltage removes. Memristors' nonvolatility can store weights with no extra power consumption, especially in a scenario of mapping and retaining pre-trained weights. Besides, a single memristor can store more than one bit with low power consumption. Reference [64] has reported 92 distinguishable states, which are equivalent to 6.5 bits when using digital memory, with energy consumption in the pJ - nJ range. Reference [67] mentioned  $\sim$ 10f]/operation for IMC in memristors, comparsed to 50fJ/operation estimated by reference [49]. Reference [113] further reported 115fJ for on-switching and 13pJ for off-switching for tantalum oxide memristors. Moreover, memristors also provide high-speed property, with switch time as fast as 85ps for nitride memristors [111], compared to <10ns read access time for SRAM [66]. Memristors are further specified into several categories: electrochemical metallisation memories (ECM), valence change memories (VCM), and thermochemical memories (TCM), based on working principles [114]: the bipolar ECM relies on the drift of the highly mobile ions conducting, the bipolar VCM switching is induced by voltage pulses, and the unipolar TCM relies on thermochemical mechanism, the change of the stoichiometry caused by a current-induced temperature increase. This thesis will only discuss VCM memristors.

# 2.1.2.2 Memristors and In-memory Computing

As two-terminal devices, memristors are suitable for matrix integration. With Directly applying Ohm's law and Kirchoff's current law, memristor crossbars are widely used to perform dot product [58], which is the core of an SNN algorithm. Figure 2.5 explains how a selectorless memristor crossbar forms a crucial part of a spiking neural network: rows (wordlines) and columns (bitlines) represent pre-synapse and post-synapse, respectively. Incoming voltage spikes, as one vector operand, are sent to wordlines, with synaptic weights stored as resistive states in memristors. The result of the weighted sum can be attained in bitlines as currents. Memristors are more commonly integrated into crossbars with selectors in series, as shown in the right figure of Figure 2.5 to get rid of the sneak path current, though increasing the difficulty in integrating crossbar in high density. With a crossbar structure, memristors can be used in in-memory computing with good energy efficiency. Table 2.1 displays the comparison of energy efficiency remarked by numbers of Tera-operations per Watt among Google's tensor processing unit (TPU) [115], a SRAM-based IMC design [116], and two memristor-based IMC designs [117, 118].

TABLE 2.1: Energy efficiency comparison of Von neumann machine, SRAM-based in-memory computing design, and memristor-based in-memory computing designs

| Designs                    | Google's TPU[115] | [116]    | [117]         | [118]         |

|----------------------------|-------------------|----------|---------------|---------------|

| Categories                 | Von Neuman        | SRAM IMC | memristor IMC | memristor IMC |

| Energy efficiency (TOPS/W) | 0.24-0.31         | 3.12     | 11            | 28            |

#### 2.1.2.3 Memristors and STDP

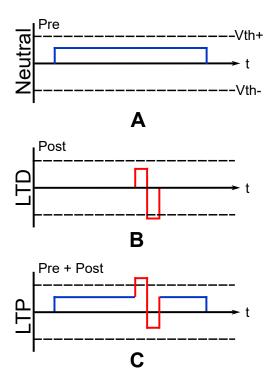

As mentioned in Section 2.1.1.4, STDP is a popular learning rule for SNNs, especially for unsupervised learning tasks. However, due to the complex mathematics form, this learning rule is not hardware friendly. Reference [119] has given a CMOS-based STDP implementation with 30 transistors per plastic synapse. Previous research has shown that memristors can implement classic STDP learning rules as memristors have intrinsic characteristics that are highly similar to STDP [120]. Reference [71] proposed an effective approach to applying weight-dependent STDP in neuromorphic applications. This approach uses a low-voltage pulse below the threshold as a pre-synaptic spike (Figure 2.6 (A)). A bipolar pulse whose negative part exceeds the threshold is applied as a post-synaptic spike (Figure 2.6 (B)). In this way, a single pre-synaptic spike will not switch the state of memristors, while a single post-synaptic will cause long-term

FIGURE 2.6: Memristors implement STDP [71]. This approach has been presented by [71]. Neutral (A), LTD (B), and LTP (C) are represented by a long, low-voltage under-threshold pre-synaptic pulse, a short bipolar post-synaptic pulse with the negative part exceeding the threshold, and the superposition of pre- and post-synaptic pulses, respectively.

depression (LTD). Suppose concurrent pre- and post-synaptic spikes are applied to the same memristor. In that case, the superposition will make the voltage exceed the positive threshold (Figure 2.6 (C)), which is equivalent to long-term potentiation (LTP). In other words, there are three possible spiking events to a single memristor: a pre-synaptic event, a post-synaptic event, and a combined pre-and post-synaptic event. They will lead to three outcomes respectively: neutral, LTD and LTP. The paper further looked into how the resistance state changed depending on the memristor's current state, which clearly shows an exponential tendency aligned with STDP. Based on this weight-dependent STDP characteristic, a general equation is summarized below:

$$\frac{\Delta g}{g} = POST \cdot [PRE \cdot f^{LTP}(g) - (1 - PRE) \cdot f^{LTD}(g)]$$

This approach enables memristor synapses to encode conditional probability so that inference and updating weight can be merged into one phase while training memristor-based SNNs, further empowering memristors to perform as plastic synapses in neuromorphic designs.

In summary, memristors bring great potential in implementing SNN designs by serving as synapses thanks to the low-power multi-bit storage capacity, cross-bar structure, high-speed dynamics, non-volatility, and inherent physical characteristics similar to biological synapses. Despite great potential, larger sizes of memristor systems are still limited by device variability [67]. Besides, computing accuracy is also affected by device variations. So far, memristor-based in-computing ANN or SNN designs hardly achieve the same classification accuracy as their software equivalence [72, 74, 121, 122]. More efforts and exploration are still needed to make memristor-based neuromorphic become mainstream.

# 2.2 Neuromorphic Designs at a Glance

#### 2.2.1 Hardware Frameworks

## 2.2.1.1 General Neuromorphic Design Strategies

The main goals of developing neuromorphic systems are performing AI tasks with the biological time scale and the power consumption, or understanding how brains work. These designs can either be potentially used in robotics [123], biomedical field [33, 124] and real-time online learning [125], or benefit from fast and low-power-cost information processing [31, 32]. In Section 2.1, a basic structure of biological neural networks has been given in Figure 2.1, with soma, dendrites, synapses, and axon. Inspired by biological neural networks, SNNs can choose to keep some of the biological attributes to balance design complexity and performance. In most SNN implementations, soma and synapses must be included, while dendrites and axons are optionally implemented. Hodgkin-Huxley neuron model [96] and Izhikevich's neuron model [105] use relatively complex mathematical expressions to model biological neural networks accurately, while they both require more hardware complexity. Leaky-integrate-and-fire neuron model [99] is more computational friendly, therefore LIF is a popular choice as the neuron model in SNN system designs [17, 38, 40, 53, 54, 71, 72, 126, 127]. Synapses are commonly represented as memory devices [53, 54, 71, 72, 73, 74, 75, 76].

In SNNs, information is encoded as spike rates together with the precise timing of arrival. The typical way to realise the temporal property of SNNs is to calculate and update neuron states in each time step, though this method brings the trade-off between precision and latency. Some designs [17, 31, 32, 38, 128, 129]

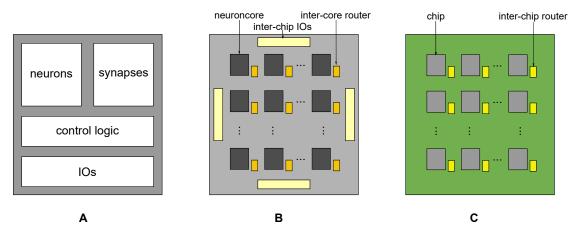

FIGURE 2.7: Neuromorphic system designs in different scales. **(A)** Neurocore. Neurons and synapses are placed closely to reduce communication costs. Each core has separate control logic so that multi-cores can work concurrently. **(B)** Chip. Multiple cores are integrated in this scale. Each neuroncore has an individual router, and a global NoC is used for cross-core communication. **(C)** Board. The image is inspired by [130].

also support fixed-axon and/or synapse delays to reduce information loss, despite the increased system complexity.

Neurons are regarded as the processing units in SNNs. In an SNN, a large number of neurons work separately and concurrently. Therefore, massive parallelism is the main challenge and the design goal when demonstrating an SNN regardless of the platform used. Memory utilisation and bandwidth are other issues that need carefully considered due to the large number of parameters used as synaptic weights. Some designs [53, 54, 71, 72, 73, 74, 75, 76] merge the computational units and the memory so that the data are processed in an in-situ manner to reduce the cost of accessing data to and from memory.

Figure 2.7 illustrates neuromorphic systems in different scale. This design hierarchy shows the same methodology for neuromorphic systems: distributing the memory storage and computation. Each neurocore contains part of neurons and synapses, so multiple neurocores can cooperate to speed up and save energy. Multiple neurocores in a chip and multiple chips on a board show parallelism at the chip and the board level, respectively.

Different targeted applications lead to different design choices. Large-scale neuromorphic systems aim at enabling and accelerating large-scale high-power datacentric computing tasks, whereas embedded processors are designed for mobile devices prioritising power consumption. Therefore, it is not fair to compare their performance directly. In the following subsections, typical designs

for both large-scale neuromorphic systems and small-scale low-power designs are discussed separately.

# 2.2.1.2 Large-scale Neuromorphic Systems

Large-scale neuromorphic systems to be introduced in this subsection include application-specific integrated-circuits (ASICs) and application-specific instruction set processors (ASIPs) designs: TrueNorth [31] from IBM, Neurogrid [33] from Stanford University, Loihi [32] from Intel, SpiNNaker [35, 128] from University of Manchester, BrainScaleS [131] from Heidelberg University, multi-FPGA-based design BlueHive [129], and multi memristor crossbars based design INXS [132]. Table 2.2 gives the key characteristics of those seven designs.

TABLE 2.2: A comparison among large-scale neuromorphic systems. The table is inspired by [130, 133]

| Platform               | Neurogrid[33]            | BrainScaleS[34, 131]       | TrueNorth[31]      | SpiNNaker[35]        | Loihi [32]         | BlueHive [129]             | INXS[132]                      |

|------------------------|--------------------------|----------------------------|--------------------|----------------------|--------------------|----------------------------|--------------------------------|

|                        |                          | , ,                        |                    | 1                    |                    |                            |                                |

| Technology             | analog                   | analog                     | digital            | digital              | digital            | digital                    | mix-signal                     |

| Processor              | Neurocore                | HICANN[34]                 | 4096 cores         | 18 ARM cores         | 128 cores          | FPGA                       | 512 memristor<br>32k crossbars |

| # Neurons              | 65k                      | 512                        | 1M                 | 16k                  | 128k               | 64k                        | 128k                           |

| # Synapses             | 100M                     | 100k                       | 256B               | 16M                  | 2M                 | 64M                        | ∼ 226k                         |

| Power                  | 150mW                    | 1.3W                       | 72mW               | 1W                   | N/A                | N/A                        | 2W                             |

| Power/neuron/Hz        | 2.3nW/Hz                 | 0.25nW/Hz                  | 72pW/Hz            | 62.5nW/Hz            | N/A                | N/A                        | N/A                            |

| Board                  | PCB                      | Wafer                      | PCB                | PCB                  |                    | Rack box                   |                                |

| # Processor            | 16                       | 352                        | 16                 | 48                   |                    | Up to 64                   |                                |

| Power                  | 3W                       | 500W                       | 1W                 | 80W                  |                    | $N/A^a$                    |                                |

| System                 |                          | 20 Wafers                  |                    | 600 PCBs             |                    |                            |                                |

| Power                  |                          | 10kW                       |                    | 50kW                 |                    |                            |                                |

| Speed                  | 1kHz                     | 10MHz                      | 1kHz               | 1kHz                 | N/A                | 1kHz                       | N/A                            |

| Chip Network           | Tree<br>multicast        | Hierarchy                  | 2D-mesh<br>Unicast | 2D-mesh<br>Multicast | 2D-mesh<br>Unicast | High Speed<br>Serial Links | 2D-mesh<br>Unicast             |