UNIVERSITY OF SOUTHAMPTON

**Tunable spin and charge transport using

CMOS-compatible silicon quantum dots

for quantum information applications**

by

Joseph William Hillier

A thesis submitted in partial fulfilment for the

degree of Doctor of Philosophy

in the

Faculty of Engineering and Physical Sciences

School of Electronics and Computer Science

April 2022

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF ENGINEERING, SCIENCE AND MATHEMATICS

SCHOOL OF ELECTRONICS AND COMPUTER SCIENCE

Doctor of Philosophy

by Joseph William Hillier

Scaling in commercially available silicon (Si) complementary-metal-oxide-semiconductor (CMOS) devices has inevitably led to single carrier behaviour exhibited at low temperatures owing to the strong orbital quantization of disorder based quantum dots (QDs). As a consequence, p-type Si metal-oxide-semiconductor-field-effect-transistors (MOSFETs) fabricated and supplied by Hitachi provide an excellent platform to evaluate and explore a plethora of rich phenomena that arise from the interplay of single hole transport and spin interactions. Through the use of the well terminal acting as a pseudo-gate in a MOSFET, I discover the formation of a double-QD system exhibiting Pauli spin-blockade and investigate the magnetic field dependence of the leakage current. This enables attributes that are key to hole spin state control to be determined, where I calculate a tunnel coupling  $t_c$  of  $57 \mu\text{eV}$  and a short spin-orbit length  $l_{SO}$  of 250 nm. The outcome of a strong spin-orbit interaction at the interface when using disorder based QDs demonstrates support for electric-field mediated control.

In addition, I experimentally investigate the impact of electrical stress on the tunability of single hole transport properties in a MOSFET device. This is achieved by monitoring Coulomb-blockade from three disorder based QDs at the channel-oxide interface, which are known to lack tunability as a result of their stochastic origin. My findings indicate that when applying gate biases between -4 V to -4.6 V, nearby charge trapping enhances Coulomb-blockade leading to a stronger QD confinement that can be reversed to the initial device condition after performing a thermal cycle reset. Re-applying stress then gives rise to a predictable response from reproducible changes in the QD charging characteristics with consistent charging energy increases of up to  $\approx 50\%$  being observed. A threshold is reached above gate biases of -4.6 V, where the performance and stability become reduced due to device degradation occurring as a product of large-scale trap generation. These results not only suggest stress as an effective technique to enhance and reset charging properties, but also offer insight on how industry compatible Si devices can be harnessed for single charge transport applications by investigating interactions which are useful for quantum information processing.

# Contents

|                                                                                                                       |           |

|-----------------------------------------------------------------------------------------------------------------------|-----------|

| <b>Acknowledgements</b>                                                                                               | <b>xv</b> |

| <b>1 Introduction</b>                                                                                                 | <b>1</b>  |

| <b>2 Literature review and theory</b>                                                                                 | <b>5</b>  |

| 2.1 Advancements in Si quantum information technology . . . . .                                                       | 5         |

| 2.1.1 Single carrier transport devices . . . . .                                                                      | 5         |

| 2.1.2 Single spin sensing and manipulation . . . . .                                                                  | 7         |

| 2.1.3 Unclonable charging characteristics . . . . .                                                                   | 9         |

| 2.2 Fundamentals in silicon technology and physics . . . . .                                                          | 9         |

| 2.2.1 MOSFET operation . . . . .                                                                                      | 9         |

| 2.2.2 QD transport and properties . . . . .                                                                           | 14        |

| 2.2.3 Pauli spin-blockade and spin-orbit interaction . . . . .                                                        | 17        |

| 2.2.4 Basics of refrigeration and Joule-Thomson expansion . . . . .                                                   | 22        |

| <b>3 Preparations and methodology</b>                                                                                 | <b>25</b> |

| 3.1 Introduction . . . . .                                                                                            | 25        |

| 3.2 Probe-station measurement system . . . . .                                                                        | 25        |

| 3.3 Low temperature measurement systems . . . . .                                                                     | 28        |

| 3.3.1 RIKEN Oxford Instruments LHe cryostat . . . . .                                                                 | 28        |

| 3.3.2 Southampton Cryogenic CFMS . . . . .                                                                            | 30        |

| 3.3.3 CFMS repair . . . . .                                                                                           | 32        |

| 3.4 Sample preparation . . . . .                                                                                      | 36        |

| 3.4.1 Wire-bonding . . . . .                                                                                          | 36        |

| 3.4.2 Sample loading . . . . .                                                                                        | 39        |

| <b>4 Probing hole spin transport of disorder quantum dots via Pauli spin-blockade in standard silicon transistors</b> | <b>41</b> |

| 4.1 Introduction . . . . .                                                                                            | 41        |

| 4.2 Device and methodology . . . . .                                                                                  | 42        |

| 4.3 Investigating spin interactions of disorder states . . . . .                                                      | 43        |

| 4.3.1 Pauli spin-blockade via tuning the well . . . . .                                                               | 43        |

| 4.3.2 Enhanced triplet leakage due to magnetic-fields . . . . .                                                       | 47        |

| 4.3.3 CSDs at fixed magnetic-fields . . . . .                                                                         | 51        |

| 4.3.4 Spin-orbit strength and tunnel coupling determination . . . . .                                                 | 53        |

| <b>5 Tunable quantum dot transport in Si MOSFETs via electrical stress</b>                                            | <b>55</b> |

| 5.1 Introduction . . . . .                                                                                            | 55        |

---

|                     |                                                                                  |            |

|---------------------|----------------------------------------------------------------------------------|------------|

| 5.2                 | Device specification and stress procedure . . . . .                              | 56         |

| 5.3                 | Impact of stress on device operation . . . . .                                   | 58         |

| 5.3.1               | Charging energy and single hole transport enhancement . . . . .                  | 58         |

| 5.3.2               | Reversible and repeatable changes to Coulomb-blockade . . . . .                  | 60         |

| 5.3.3               | Large-scale trapping and device degradation . . . . .                            | 63         |

| 5.3.4               | Quantifying activation energy and QD coupling when subjected to stress . . . . . | 66         |

| 5.4                 | Discussion on changes to single hole transport and trapping model . . . . .      | 67         |

| 5.5                 | Outlook and applications . . . . .                                               | 69         |

| <b>6</b>            | <b>Silicon nanowire devices - design, fabrication and measurement</b>            | <b>73</b>  |

| 6.1                 | Project aim and overview . . . . .                                               | 73         |

| 6.2                 | Fabrication process flow . . . . .                                               | 74         |

| 6.2.1               | Nanowire definition . . . . .                                                    | 77         |

| 6.2.2               | Dopant diffusion . . . . .                                                       | 78         |

| 6.2.3               | Patterning Finger gates . . . . .                                                | 79         |

| 6.2.4               | Patterning Top gate . . . . .                                                    | 80         |

| 6.2.5               | Contact and metallisation . . . . .                                              | 80         |

| 6.2.6               | TiN/Ti/Al metal stack investigation . . . . .                                    | 82         |

| 6.3                 | Device yield check . . . . .                                                     | 84         |

| 6.4                 | Back-end processing . . . . .                                                    | 86         |

| 6.4.1               | Laser cutting and cleaning . . . . .                                             | 86         |

| 6.4.2               | Wire-bonding . . . . .                                                           | 88         |

| 6.5                 | Low temperature characterisation . . . . .                                       | 90         |

| 6.5.1               | Single-QD transport . . . . .                                                    | 90         |

| 6.5.2               | Double-QD formation . . . . .                                                    | 92         |

| 6.5.3               | Difficulties when characterising SET57 . . . . .                                 | 95         |

| 6.6                 | Summary . . . . .                                                                | 95         |

| <b>7</b>            | <b>Conclusions</b>                                                               | <b>97</b>  |

| <b>A</b>            | <b>LabVIEW program creation for HP4142 source-meter</b>                          | <b>99</b>  |

| <b>B</b>            | <b>Janis cryostat development for single electron pumps</b>                      | <b>101</b> |

| <b>C</b>            | <b>List of publications</b>                                                      | <b>103</b> |

| C.1                 | Publications as first-author . . . . .                                           | 103        |

| C.2                 | Publications as co-author . . . . .                                              | 104        |

| <b>Bibliography</b> |                                                                                  | <b>105</b> |

# List of Figures

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

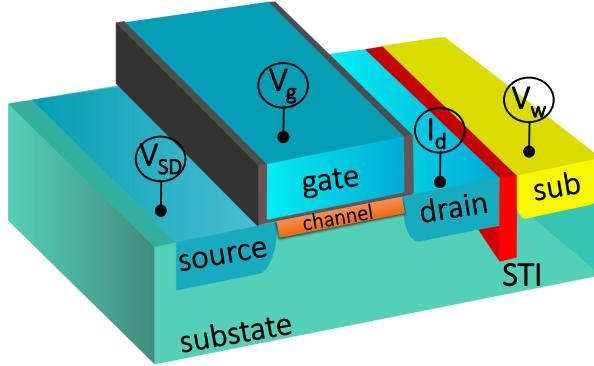

| 2.1  | Basic structure of a MOSFET. Typical oxides include $\text{SiO}_2$ or $\text{SiON}$ , with the gate usually consisting of heavily doped poly-Si and shallow trench isolation (STI) separates the substrate terminal. . . . .                                                                                                                                                                                                                     | 10 |

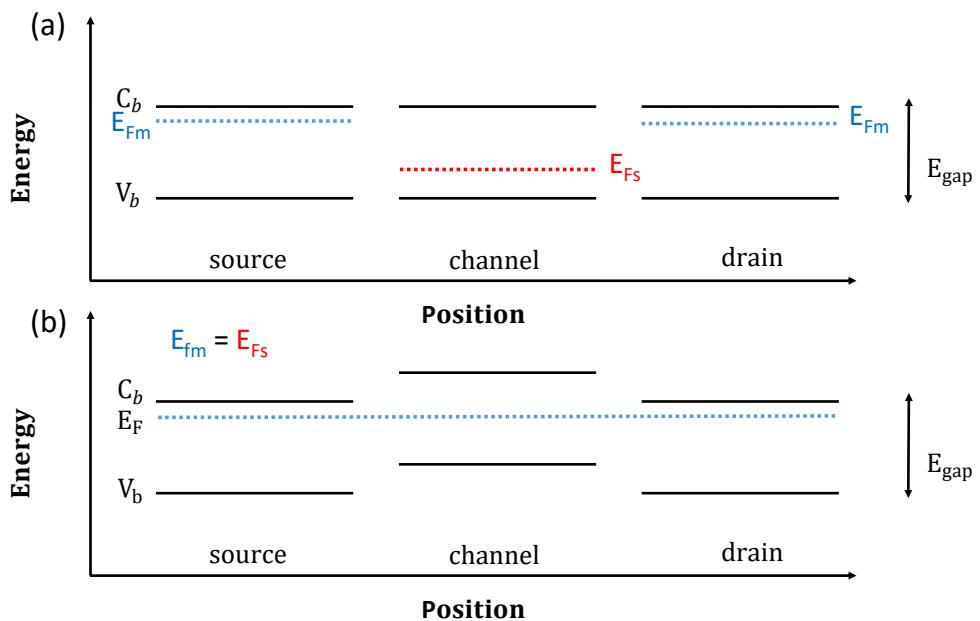

| 2.2  | (a) Fermi-levels of the highly doped n-type source/drain ( $E_{Fm}$ ) and p-type Si channel ( $E_{Fs}$ ) together with the conduction ( $C_b$ ) and valence ( $V_b$ ) bands, when all three are separated. (b) Shows the $E_f$ alignment after joining the three materials together, since $E_{Fs}$ is lower in the channel both $C_b$ and $V_b$ both shift upwards. . . . .                                                                     | 11 |

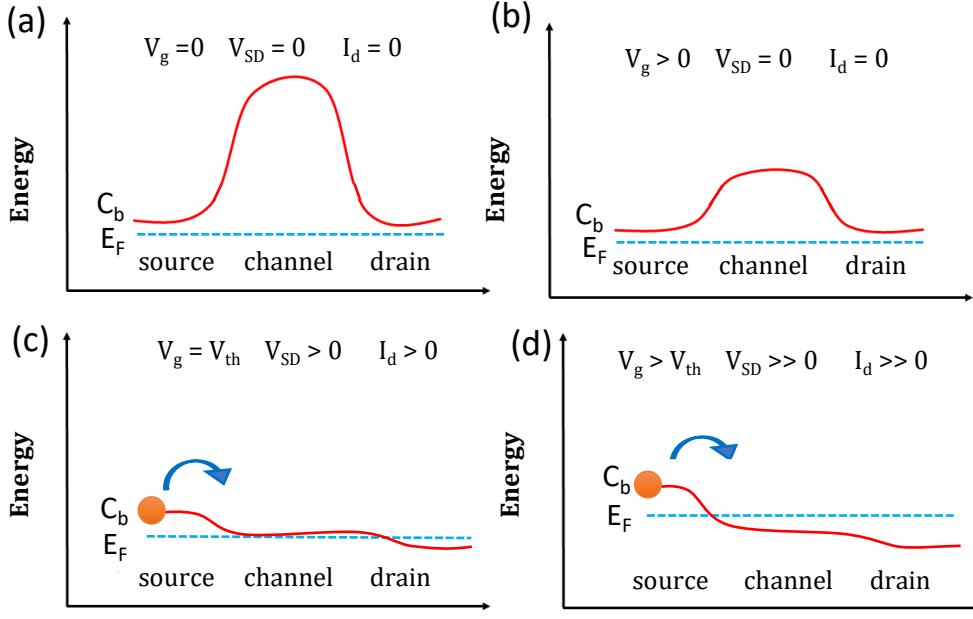

| 2.3  | (a) $V_g$ is below threshold voltage ( $V_{th}$ ) therefore the conduction band is energetically out of reach within the channel. (b) $V_g$ is approaching $V_{th}$ , but no drain current ( $I_d$ ) flows. (c), $V_g$ is at $V_{th}$ and has a small $V_{SD}$ bias, $I_d$ flows through the channel. (d) $V_g$ is above $V_{th}$ and $V_{SD}$ is large, and a large $I_d$ flows. . . . .                                                        | 12 |

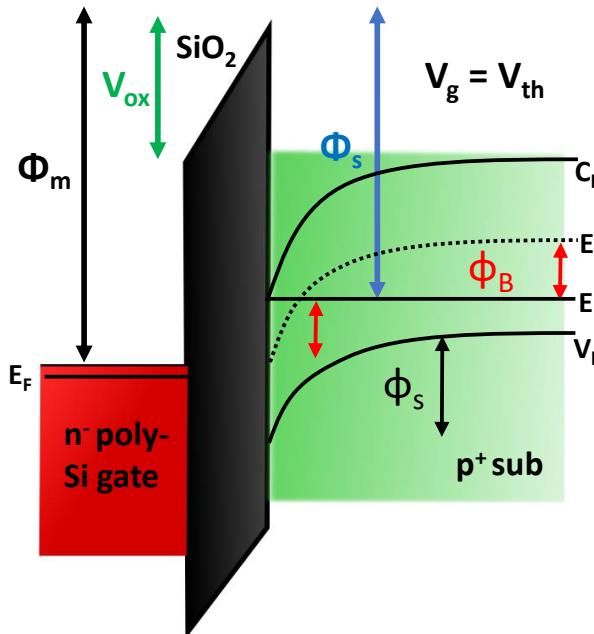

| 2.4  | Energy band diagram at the MOS interface with $V_g=V_{th}$ . Here, $V_{ox}$ is the voltage across the oxide, $\Phi_m$ , $\Phi_s$ , $\phi_B$ and $\phi_s$ are the work functions for the poly-Si and substrate, and the Fermi potential of the bulk and surface potential respectively. . . . .                                                                                                                                                   | 12 |

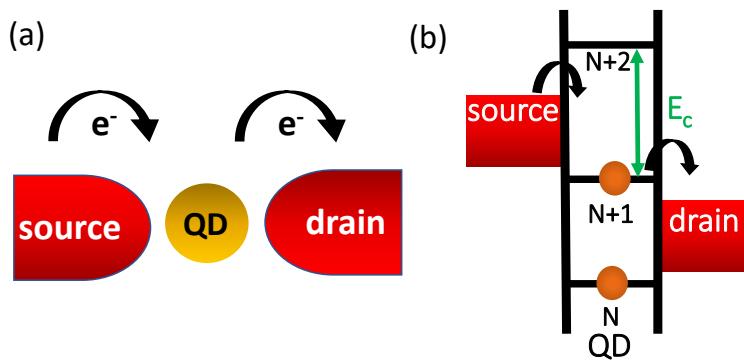

| 2.5  | (a) Illustration showing how carriers quantum tunnel from source to drain via a QD. (b) Energy level diagram with the relative source/drain potentials as well a quantum levels between barriers for carriers to tunnel through in the QD, where $N$ refers to carrier occupation. . . . .                                                                                                                                                       | 14 |

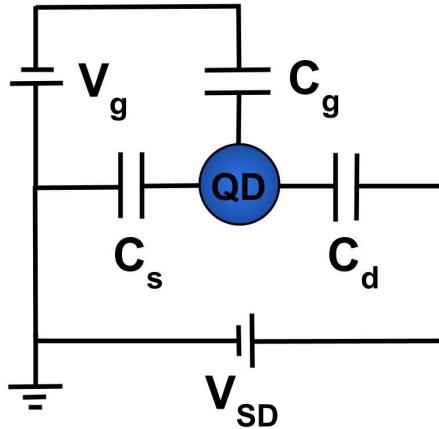

| 2.6  | A circuit diagram showing how a QD in the channel is capacitively coupled to the gate ( $C_g$ ), source ( $C_s$ ) and drain ( $C_d$ ). . . . .                                                                                                                                                                                                                                                                                                   | 15 |

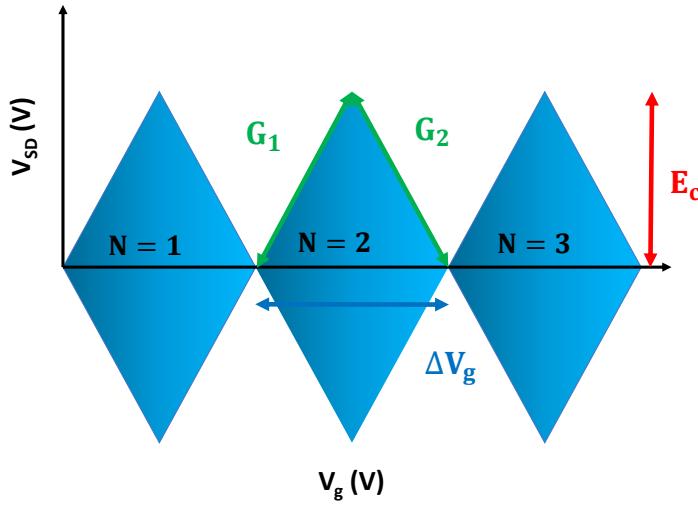

| 2.7  | A simplified charge stability diagram (CSD) showing ideal Coulomb-diamonds from QD charging characteristics. Parameters such as the charging energy $E_c$ , gradients $G_1$ and $G_2$ as well as $\Delta V_g$ for reference. . . . .                                                                                                                                                                                                             | 16 |

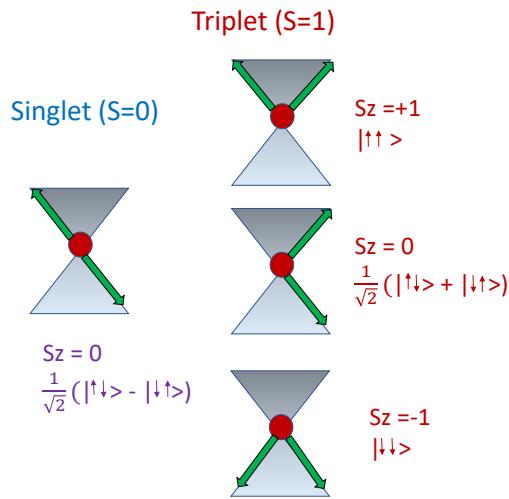

| 2.8  | Summary of four different electron/hole spin configurations which are dependant on the spin orientation (up or down). The charge carrier is given in red at the centre and the precession axis is marked by the green arrow. This leads to a spin singlet when two opposing spins pair, or a spin triplet when two spins pair with the same orientation (note that the $S_z=0$ triplet state is a linear combination of singlet states). . . . . | 18 |

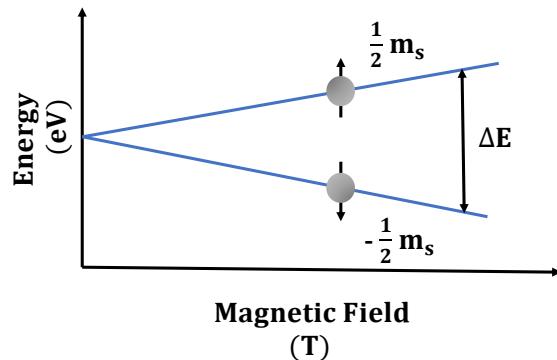

| 2.9  | A single energy level is split depending on the spin being $\uparrow$ or $\downarrow$ , where the spin quantum number is represented by $m_s$ . At 0 T both spin states are degenerate in energy, while after applying an external field the zeeman splitting increases according to equation 2.14. . . . .                                                                                                                                      | 19 |

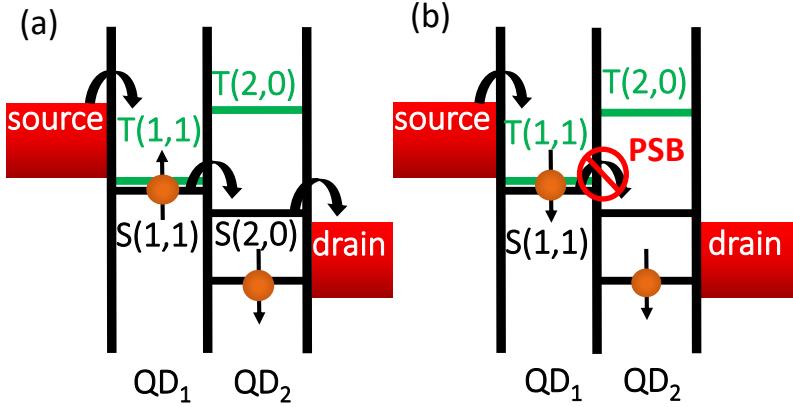

| 2.10 | Energy level diagrams for PSB occurring in a double QD, where the path through to $S(0,2)$ is allowed in (a) from the $S(1,1)$ state, but blocked in (b) due to parallel spins in each QD as a result of $T(1,1)$ . . . . .                                                                                                                                                                                                                      | 20 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

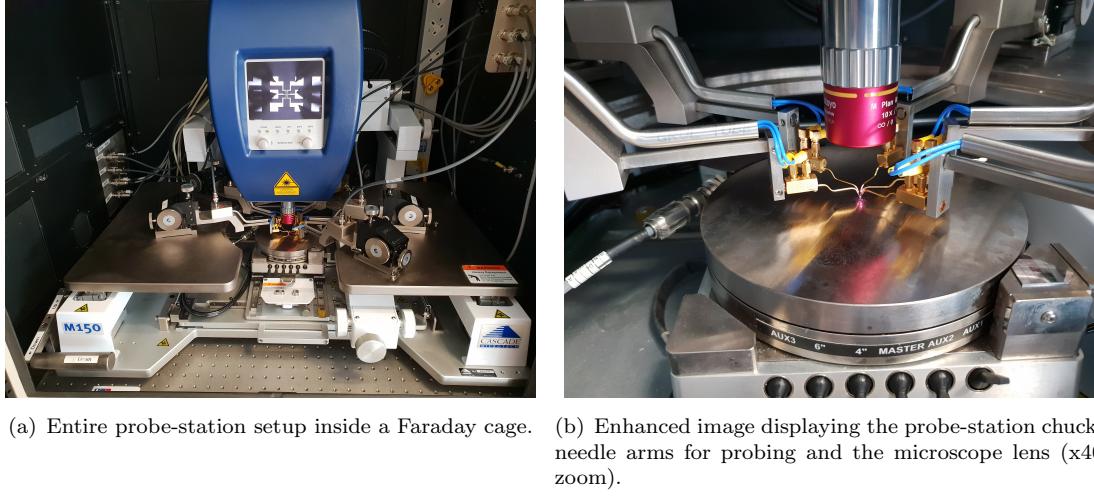

| 3.1  | Cascade M150 probe-station for room temperature measurement. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 26 |

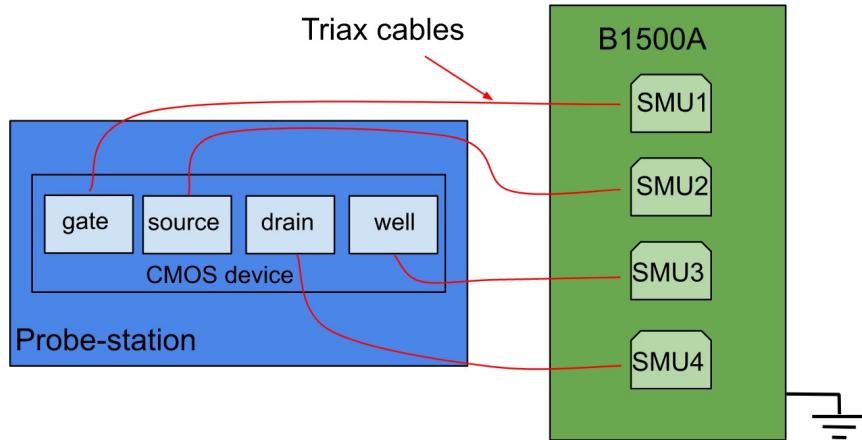

| 3.2  | Diagram displaying SMU connections to device pads . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 26 |

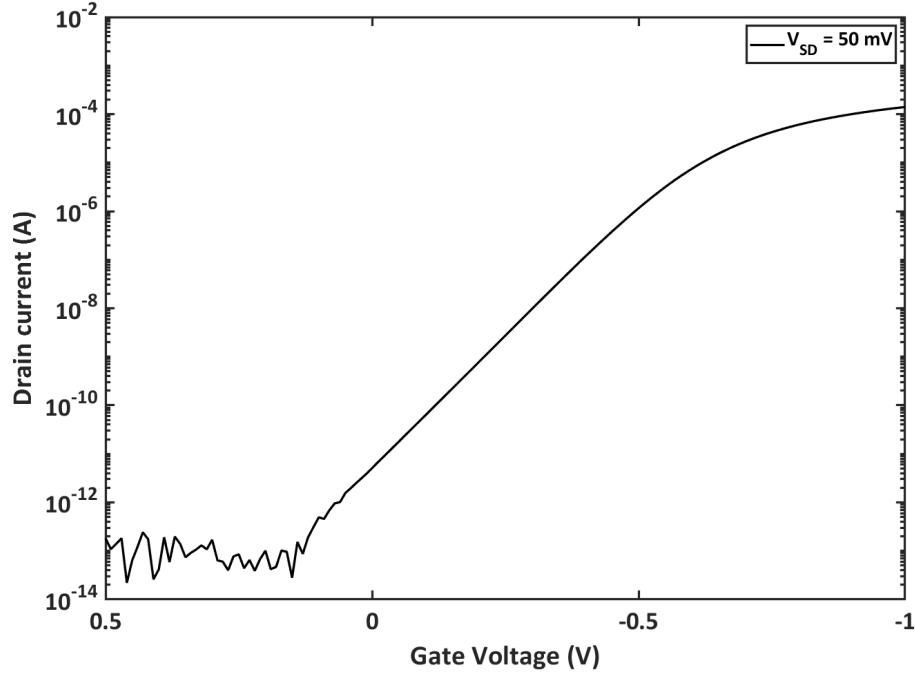

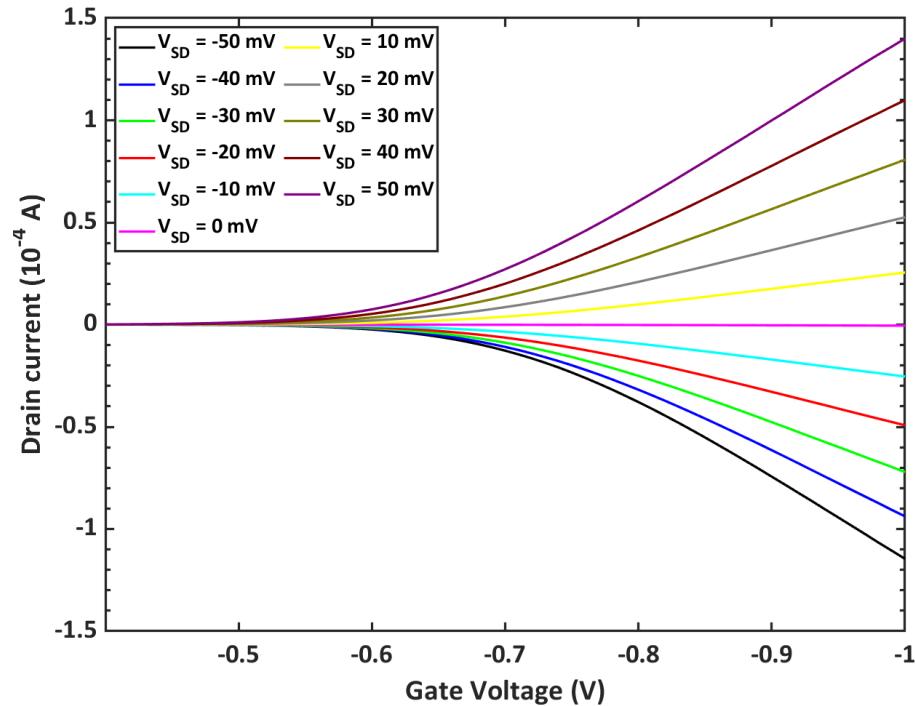

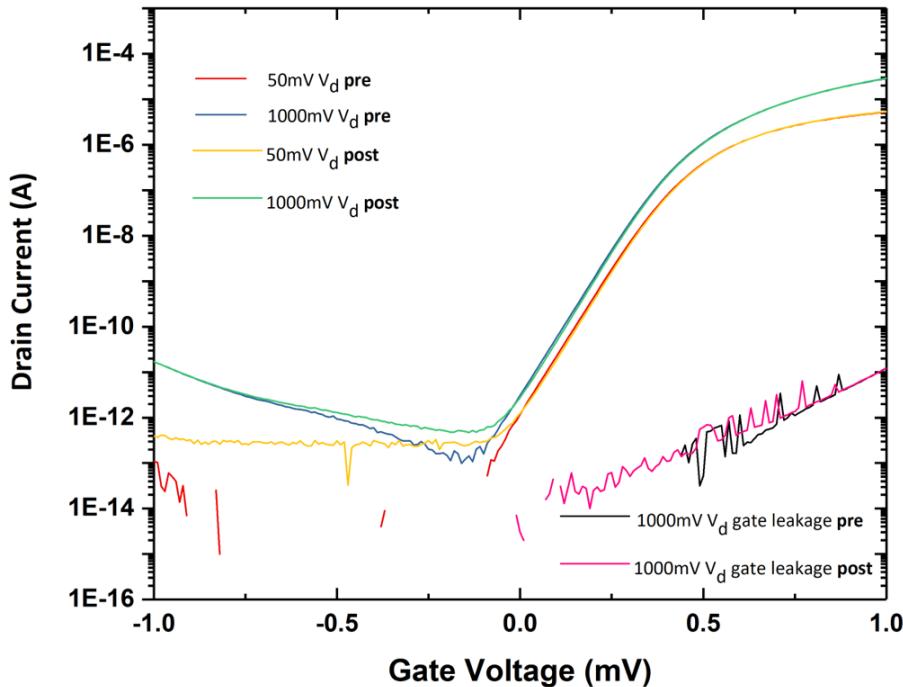

| 3.3  | Room temperature PMOS $I_d$ - $V_g$ measurements using Cascade probe station. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 27 |

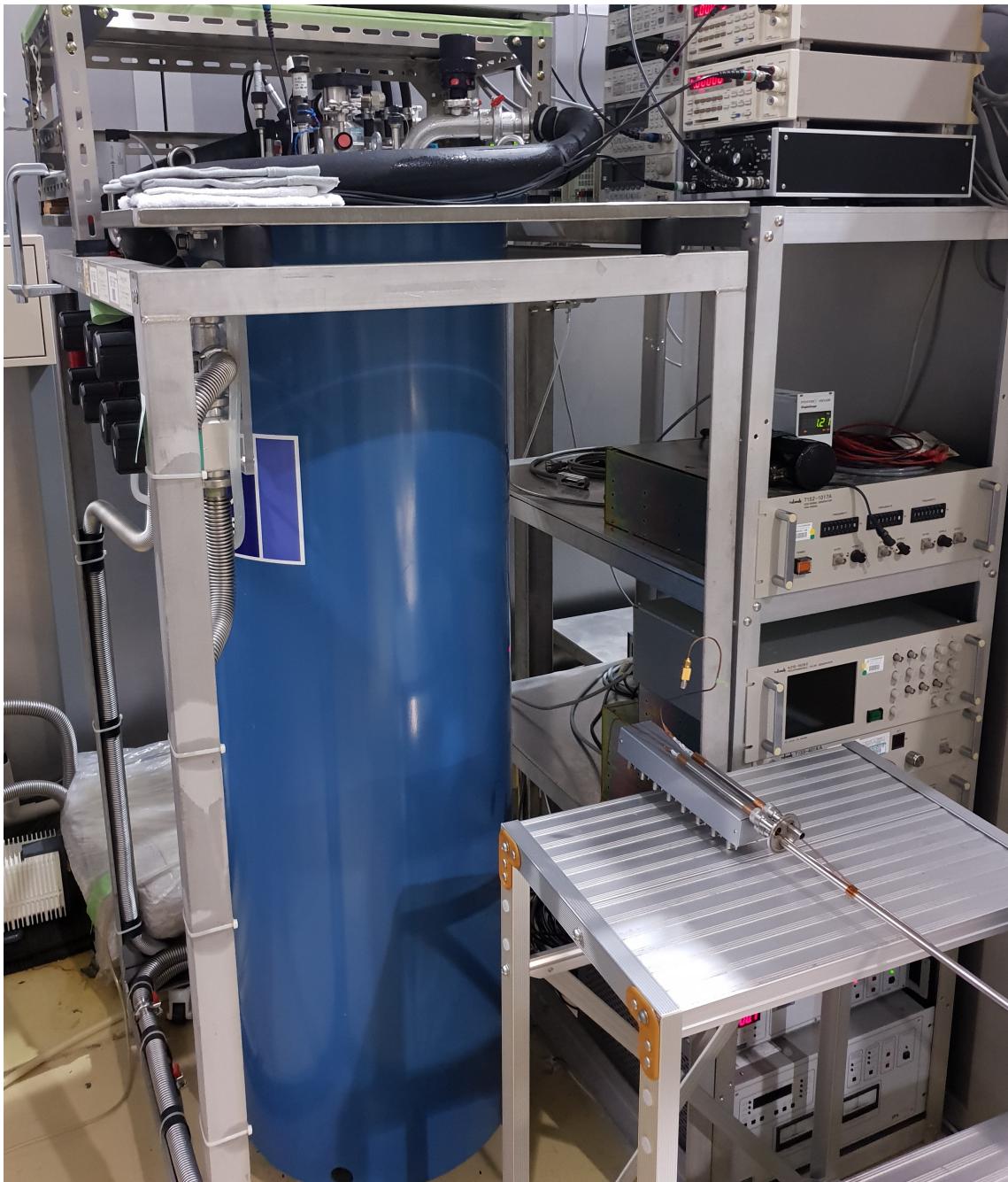

| 3.4  | Oxford instruments LHe cryostat for low temperature measurements based at The RIKEN Institute. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 29 |

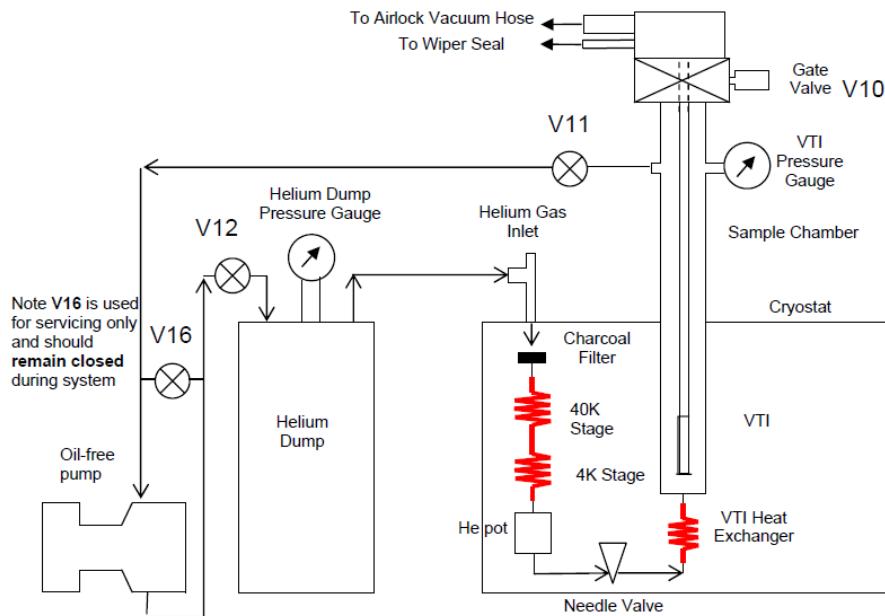

| 3.5  | Schematic diagram showing the helium flow as well as the VTI cooling circuit within the Cryogenic cryostat [60]. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32 |

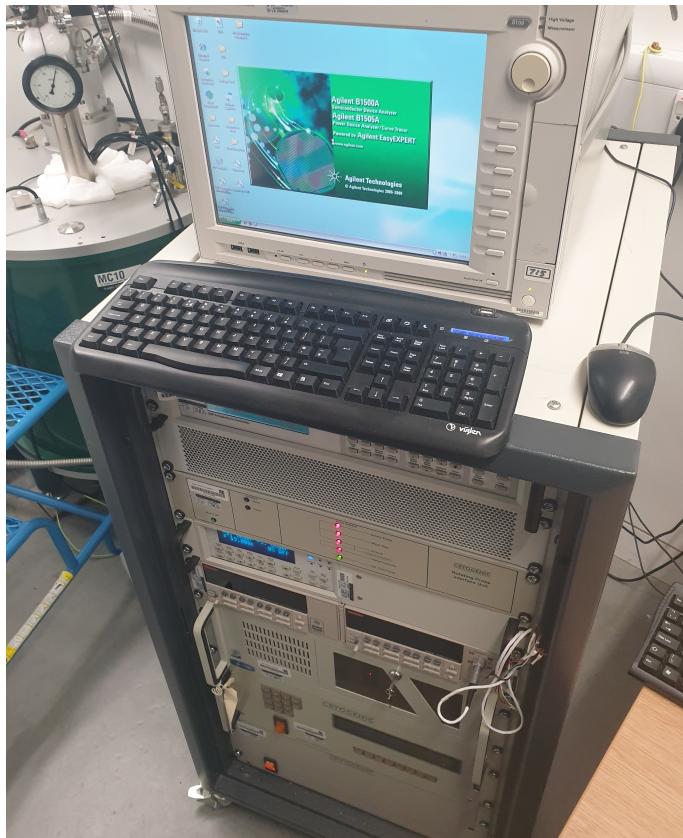

| 3.6  | B1500 (top) and Cryogenic control system (rack). . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 33 |

| 3.7  | Modifications and component repair required in order to operate the Cryogenic cryostat. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 35 |

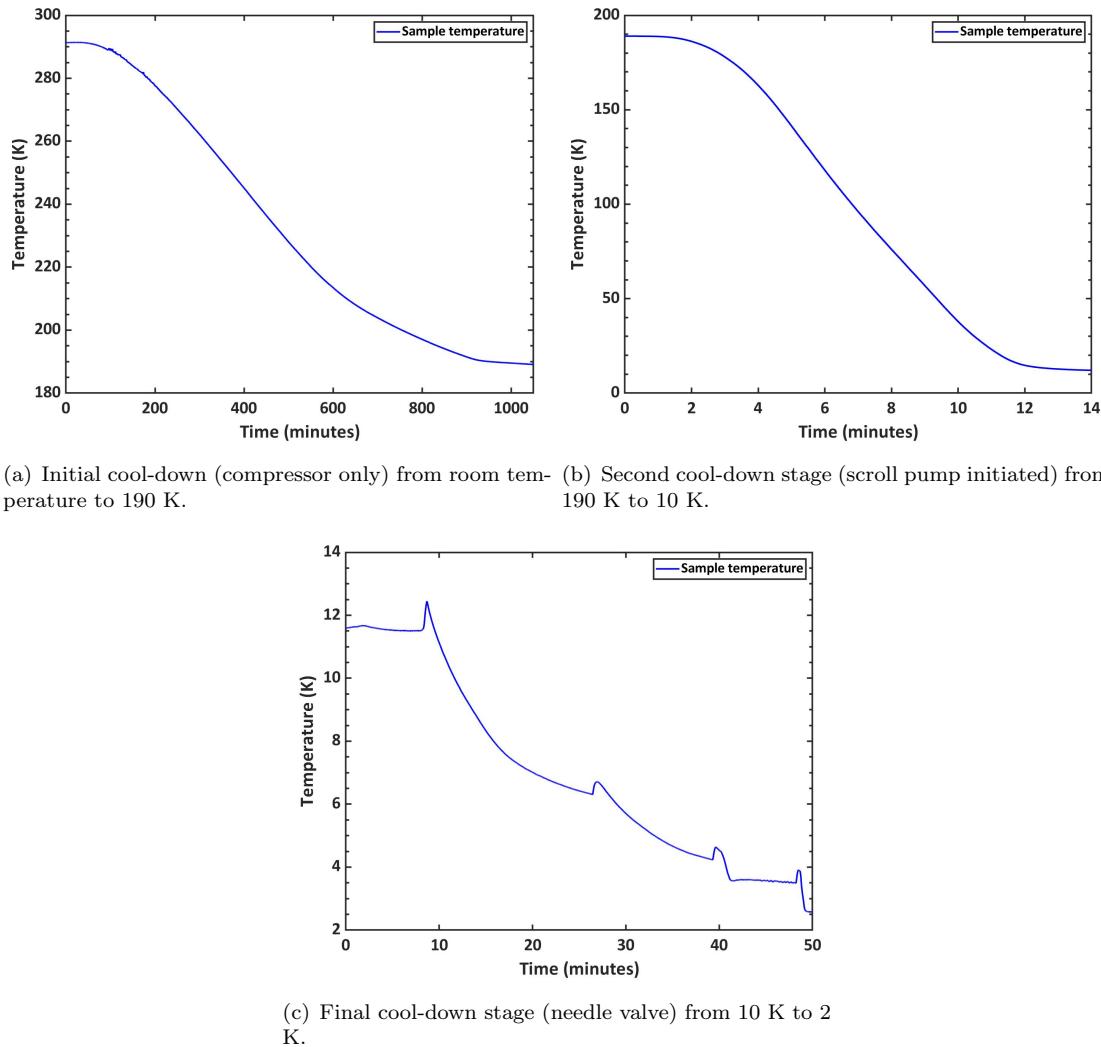

| 3.8  | Cryogenic cryostat cool-down stages. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 36 |

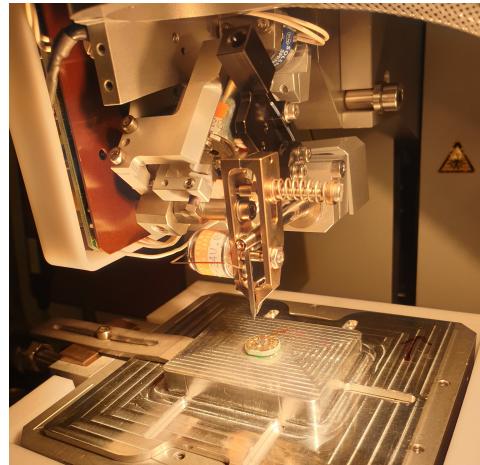

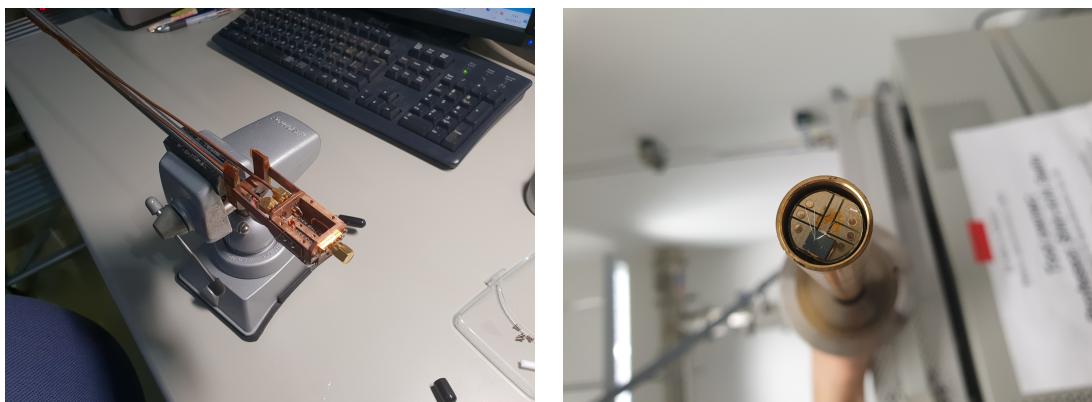

| 3.9  | Wire-bonding systems used for sample preparation at low temperatures. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37 |

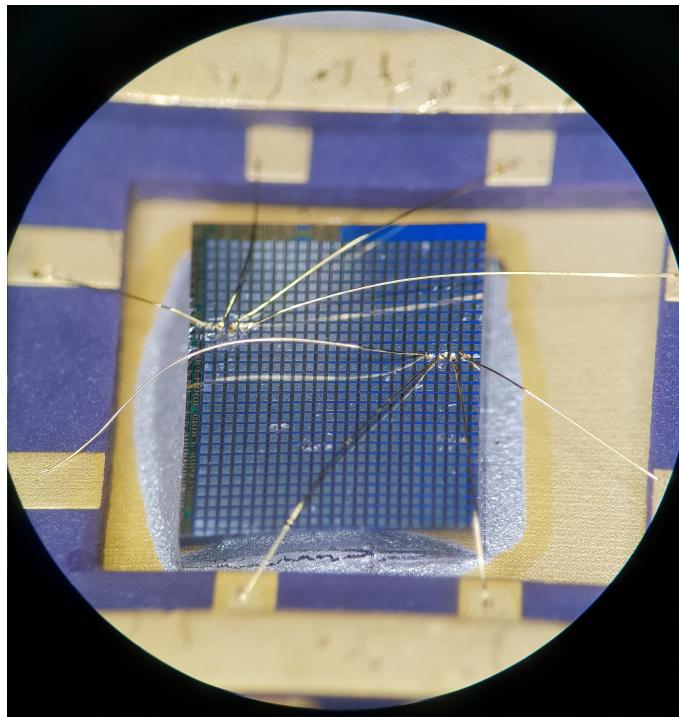

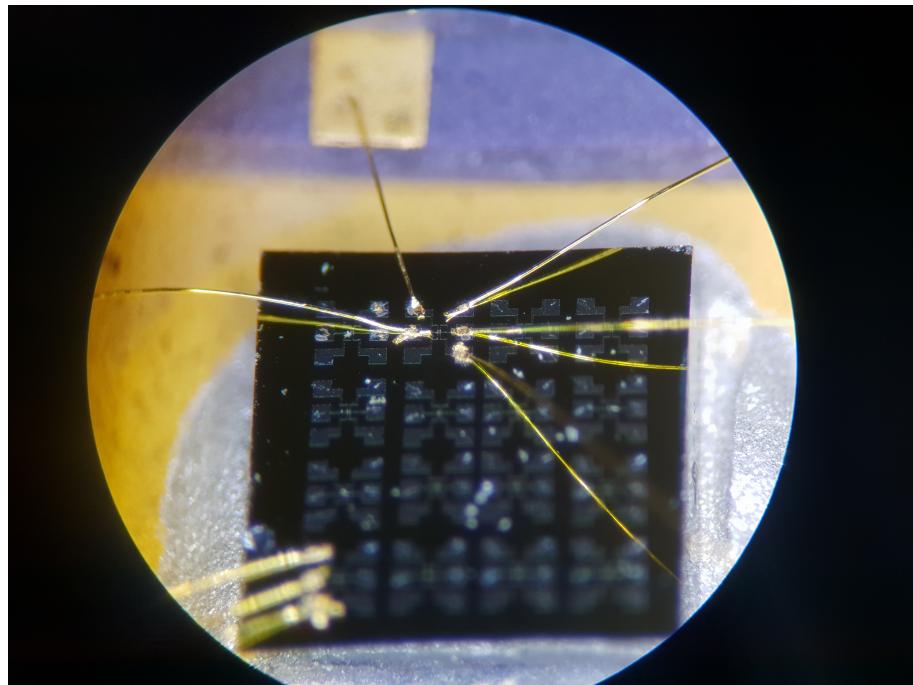

| 3.10 | Microscope image (20x zoom) of two CMOS devices wire-bonded. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 38 |

| 3.11 | A comparison of pre and post wire-bonded samples to compare $I_d$ - $V_g$ characteristics. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 38 |

| 3.12 | Comparison between different sample inserts for low temperature measurements. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 39 |

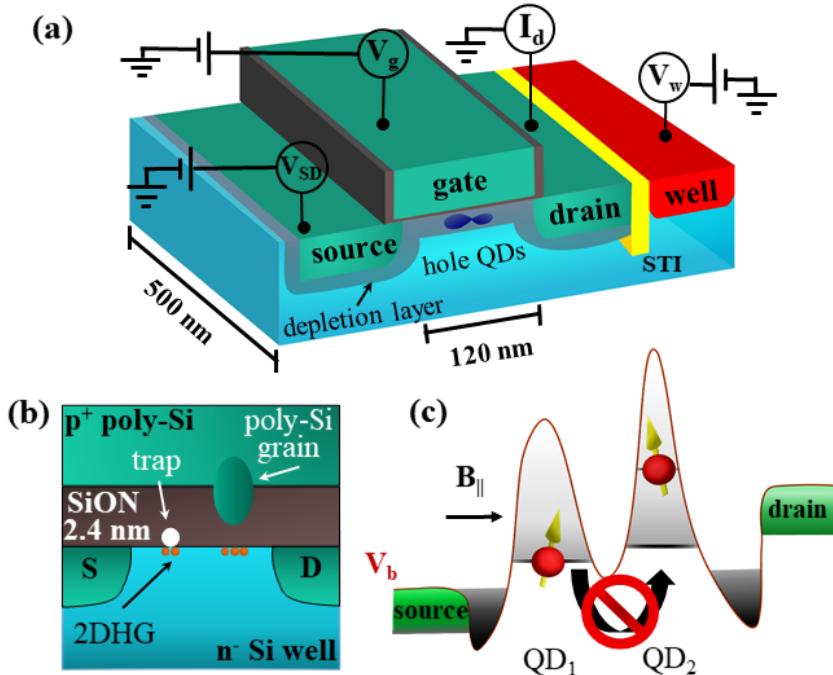

| 4.1  | (a) Schematic of p-type Si MOSFET sample with channel dimensions 500 nm width and 120 nm length. (b) Cross-section of device displaying disorder at the Si-oxide interface leading to a 2DHG forming below defects. (c) Energy band diagram showing valance band bending which leads to double-QD formation and the conditions for PSB. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 42 |

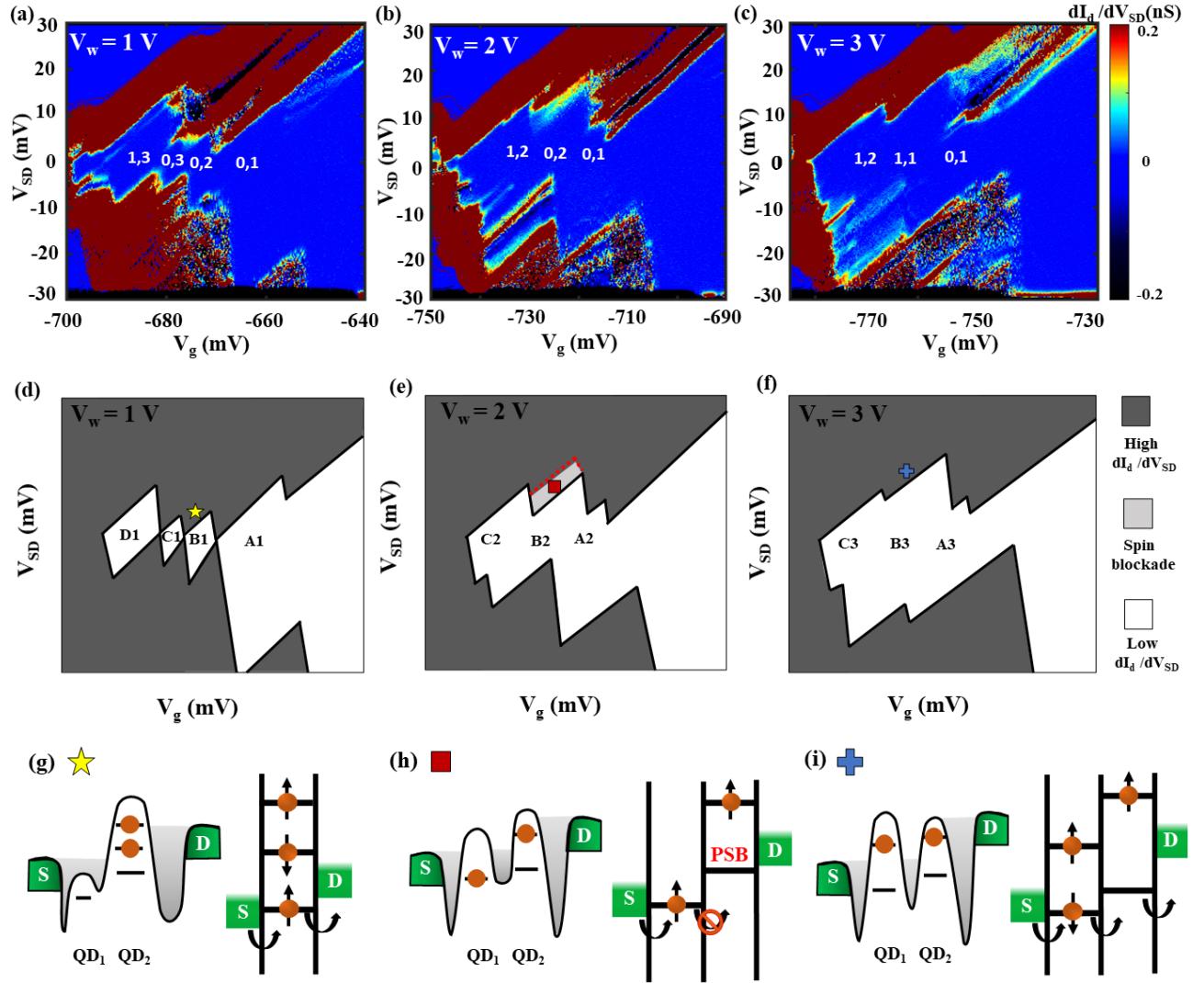

| 4.2  | CSDs for $V_{SD} = -30$ to 30 mV over a 60 mV gate voltage ( $V_g$ ) range at different well voltages ( $V_w$ ). Within the Coulomb-diamonds the number of confined holes in each QD (QD <sub>1</sub> , QD <sub>2</sub> ) are labelled. (a) $V_w = 1$ V, a row of single Coulomb-diamonds appear with various charging energies. (b) $V_w = 2$ V, the alignment of the QD energy levels change, resulting in overlapping of the Coulomb-diamonds which strongly suggests double-QD transport. (c) $V_w = 3$ V, the alignment of the Coulomb-diamonds is further altered, leading to regions of extended Coulomb blockade. The confinement of an additional hole within the dominant transport path is marked by letters A, B, C and D in simplified CSDs (d)-(f), where the number refers to the $V_w$ magnitude, however the same letter does not necessarily denote the same QD energy level in each CSD. The appearance of a PSB like low $dI_d/dV_{SD}$ region at the edge of B2 for positive $V_{SD}$ is annotated in (e), where the absence is noted at the edge of B3 in (f) from a change in coupling between the confined levels. (g)-(i) show energy band diagrams marked by the star, square and cross in (d)-(f) respectively. At $V_w = 1$ V the transport is assumed to occur largely through a single QD, upon increasing $V_w$ to 2 V the confinement changes (from larger Coulomb-diamonds), together with the QDs becoming weakly coupled and form a double QD exhibiting PSB. When $V_w = 3$ V the energy level alignment shifts between the double QD, removing PSB and allowing transport to occur. . . . . | 44 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

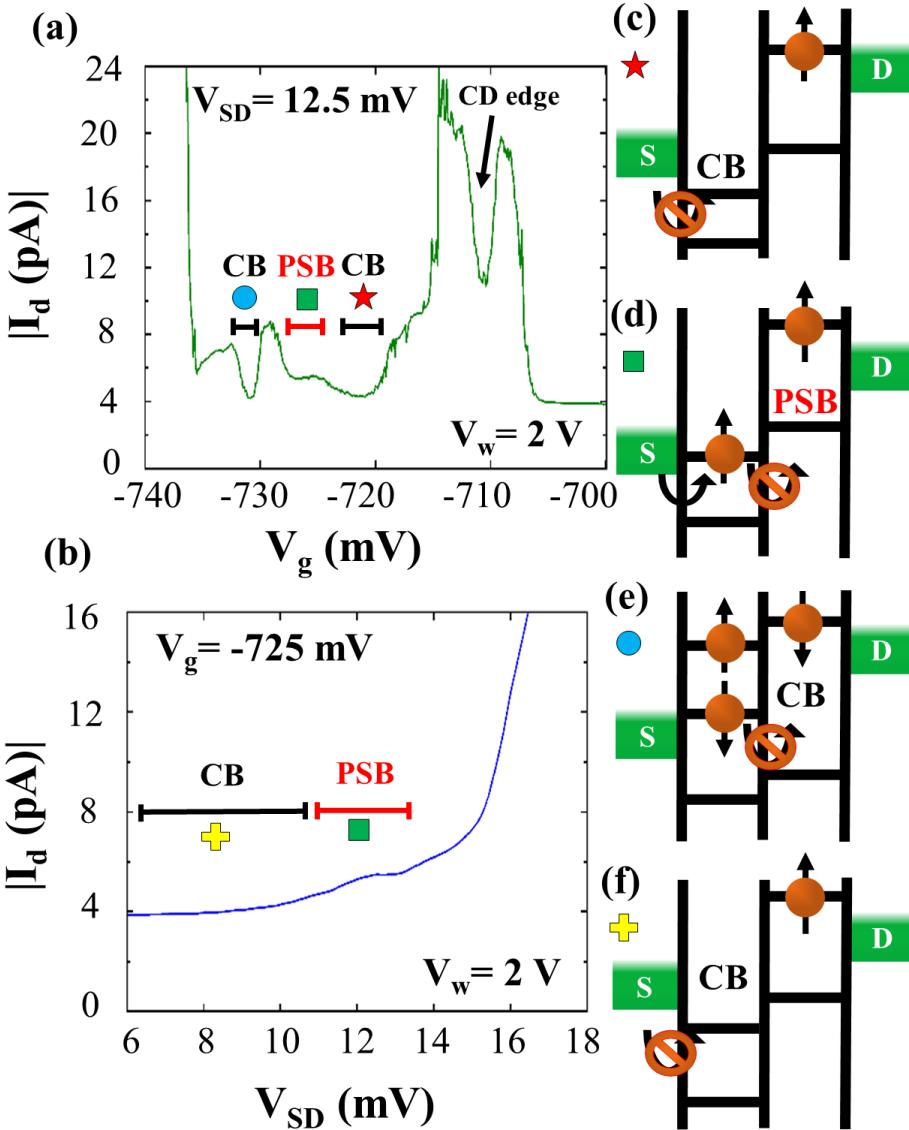

| 4.3 | For $V_w$ fixed at 2 V, a gate sweep with $V_{SD} = 12.5$ mV is shown in (a), and a source sweep with $V_g = -725$ mV is displayed in (b). Coulomb-blockade, as well as the suspected PSB region from low $dI_d/dV_{SD}$ are labelled. (c)-(e) show energy band diagrams marked by the star, square and circle in (a), for the Coulomb-blockade regions as well as PSB. In (f), an energy band diagram for Coulomb-blockade conditions marked by the cross in (b) is displayed, where PSB then occurs at higher $V_{SD}$ . . . . .                                                                                                                                                                                                        | 46 |

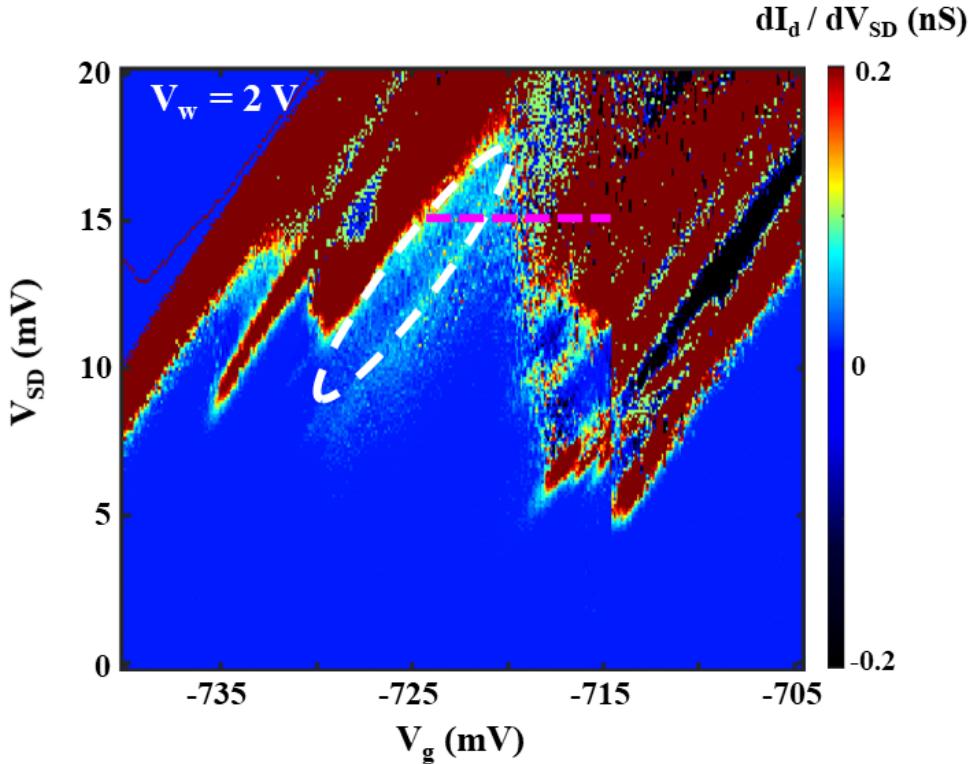

| 4.4 | CSD for $V_{SD} = 0$ to 20 mV and $V_g = -705$ to -740 mV with $V_w = 2$ V at the edge of a Coulomb diamond (white dash semi-circle), where a reduction in current is observed due to blockaded transport through a double-QDs. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 48 |

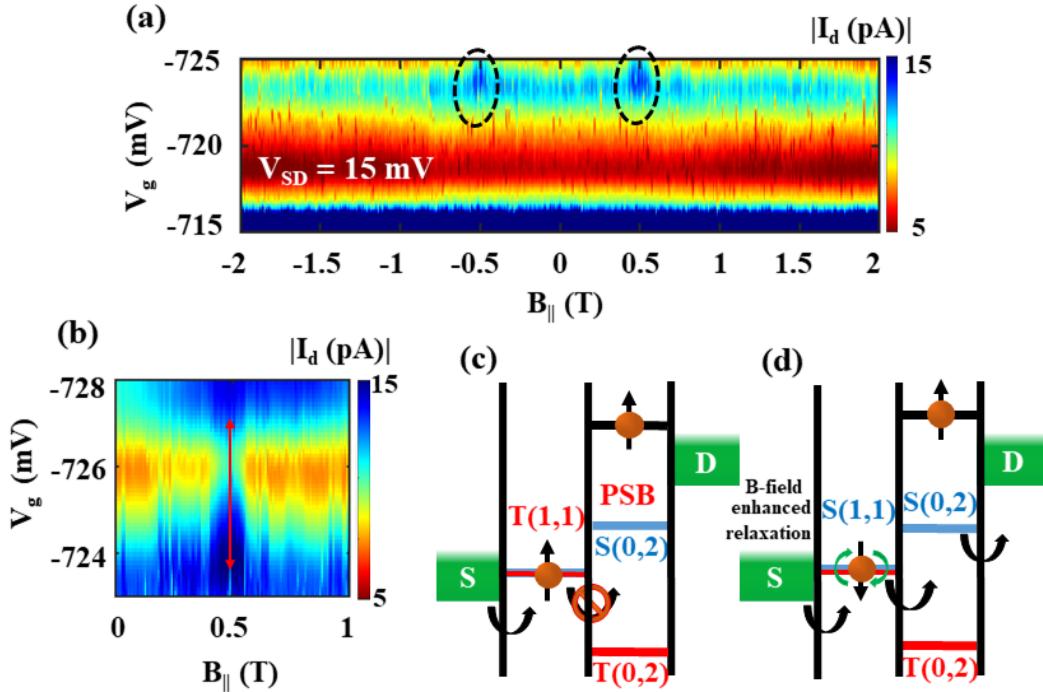

| 4.5 | (a) Current as a function of magnetic field in the PSB region at fixed $V_{SD} = 15$ mV between $V_g = -715$ to -725 mV (pink dashed line in (a)), two peaks are present due to an increase in the PSB leakage current at 0.5 T. (b) High resolution magnetic field spectroscopy scan with a clearly identifiable peak, where the extent of the maximum magnetic field enhanced spin relaxation current with respect to $V_g$ is indicated by the red arrow. (c) Energy level diagrams for PSB occurring in a double QD, where the path to S(0,2) is blocked due to parallel spins in each QD, and (d) where the blockade is partially lifted due to enhanced relaxation from S-T mixing when a finite magnetic field is applied. . . . . | 49 |

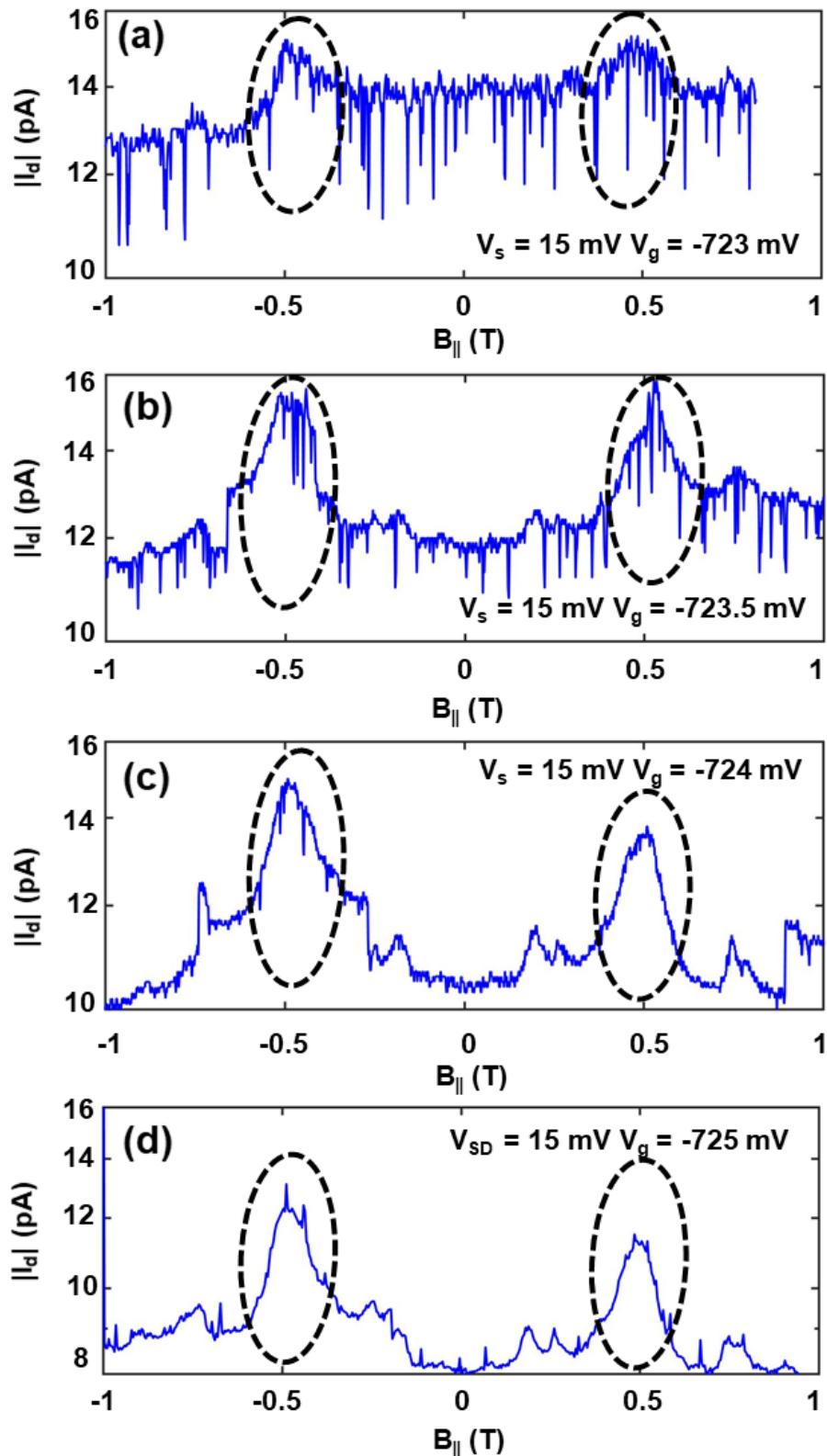

| 4.6 | (a)-(d) Profile plots showing the magnetic field dependant leakage current (blue) of a single point centered within the PSB region at a $V_{SD}$ of 15 mV and $V_g = -723$ mV, -723.5 mV, -724 mV and -725 mV. Peaks begin to appear at $\pm 0.5$ T where a total leakage current of around 15 pA is observed. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                    | 50 |

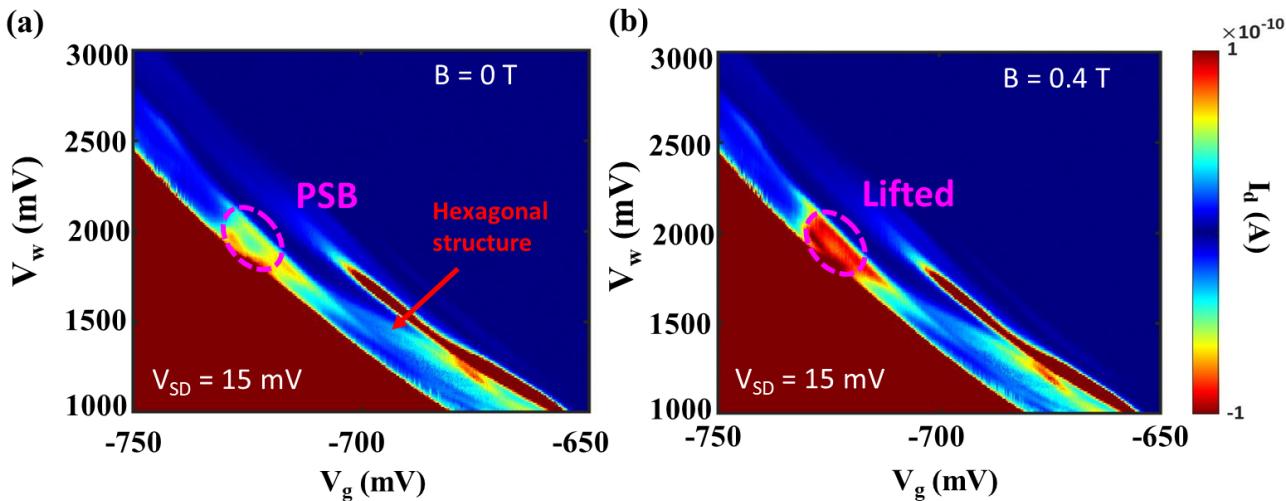

| 4.7 | (a) CSDs generated by sweeping the $V_w$ and $V_g$ to identify coupled QD transport. (b) Identical parameters to (a) but with a static $B = 0.4$ T applied, where triplet leakage is maximized when $T = 2$ K. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 51 |

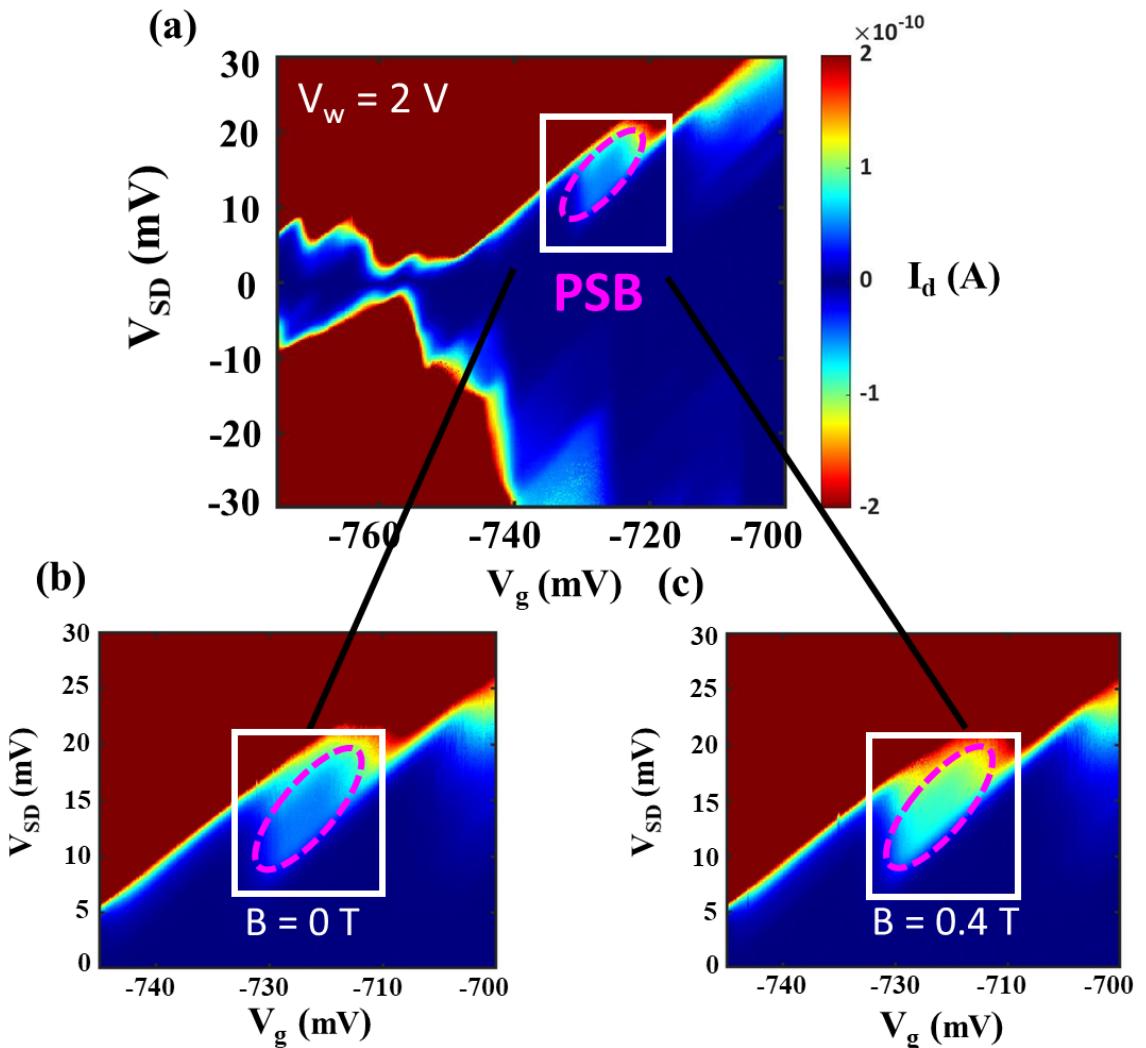

| 4.8 | (a) CSDs with $V_w$ fixed at 2 V to observe PSB double QD conditions from Figure 4.7. An enhanced image is shown of PSB at $B = 0$ T (b) and $B = 0.4$ T (c) where it is partially lifted at $T = 2$ K. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 52 |

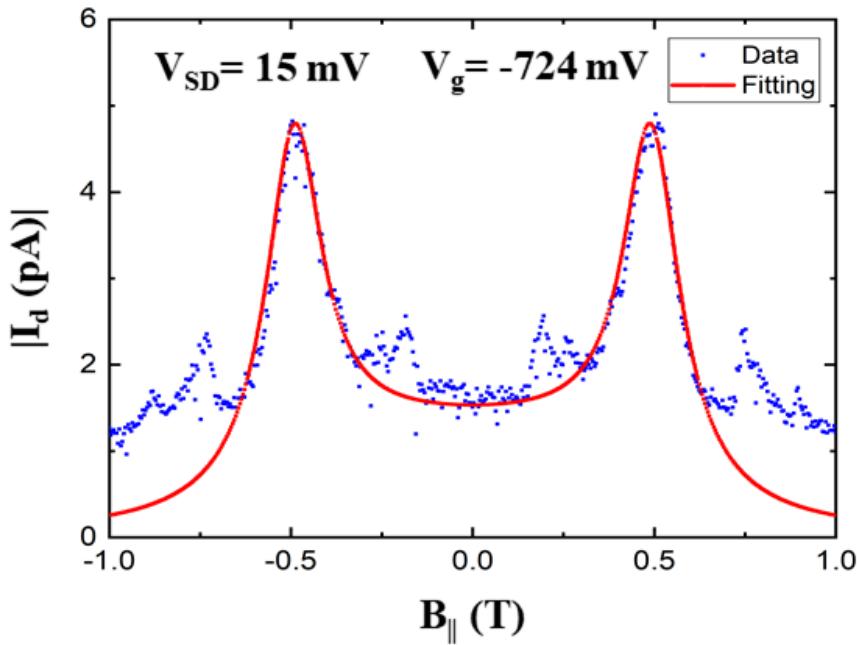

| 4.9 | A profile plot showing the magnetic field dependant leakage current (blue) of a single point centered within the PSB region at a $V_{SD}$ of 15 mV and $V_g = -724$ mV. Peaks begin to appear at $\pm 0.5$ T where a leakage current of around 5 pA is observed. Using equation 4.1 a fitting is applied to the peaks (red) to extract a $t_c$ of 57 $\mu$ eV and an $l_{SO}$ of 250 nm. . . . .                                                                                                                                                                                                                                                                                                                                          | 54 |

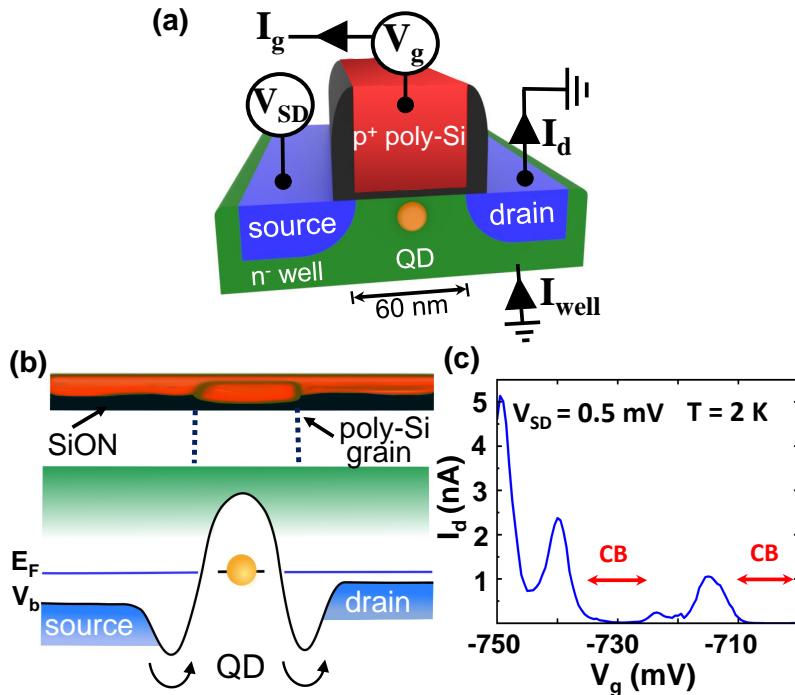

| 5.1 | (a) A schematic of the p-type MOSFET structure with an illustration of a QD in the channel. (b) A QD can be created by Si dangling bonds, poly-Si grains (depicted) or dopants at the gate-oxide interface which results in valance band bending and quantized energy levels for single hole transport. (c) An $I_d$ - $V_g$ plot displaying Coulomb-oscillations and Coulomb-blockade as a result of QD formation in the channel at a temperature of $T = 2$ K. . . . .                                                                                                                                                                                                                                                                  | 56 |

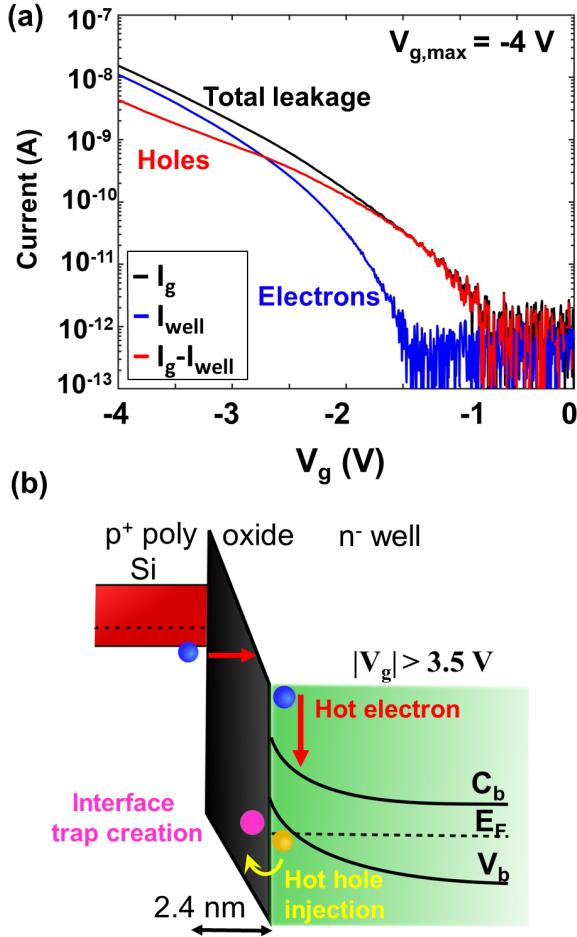

5.2 (a)  $I_g$ - $V_g$  stress sweep for  $V_{g,\max} = -4$  V. The total  $I_g$  (black) is separated into the respective carriers, with electrons tunnelling from the gate (blue) and holes from the channel (red). For each stress sweep  $V_{SD}$  is set to 10 mV and the well is grounded. (b) A band diagram illustration displaying the leakage mechanisms as a result of anode-hole injection for  $|V_g| > 3.5$  V, where hot electrons tunnelling across the oxide lead to the generation of hot holes, which are injected back into the oxide and create interface traps. . . . . 57

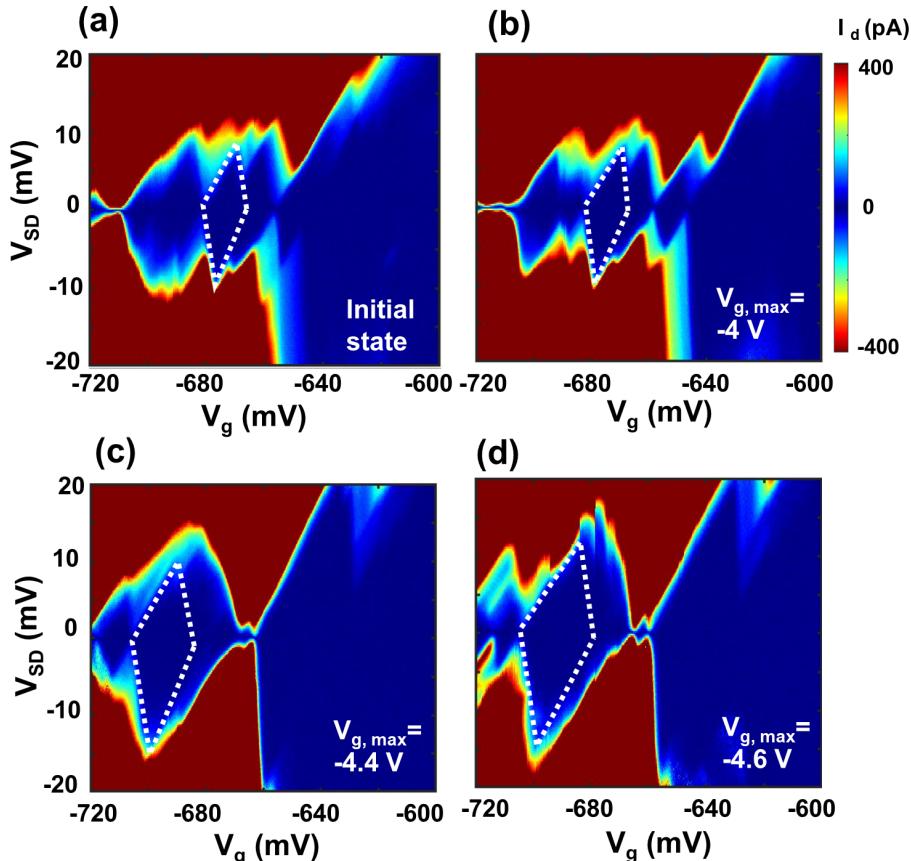

5.3 CSDs generated by biasing the source and gate, whilst measuring drain current in the sub-threshold region for device 1. (a)-(d) Current CSDs with the initial state,  $V_{g,\max} = -4$  V, -4.4 V and -4.6 V. Coulomb-diamonds are overlaid by a white dotted line in (a)-(d) to monitor the QD changes during stress. . . . . 59

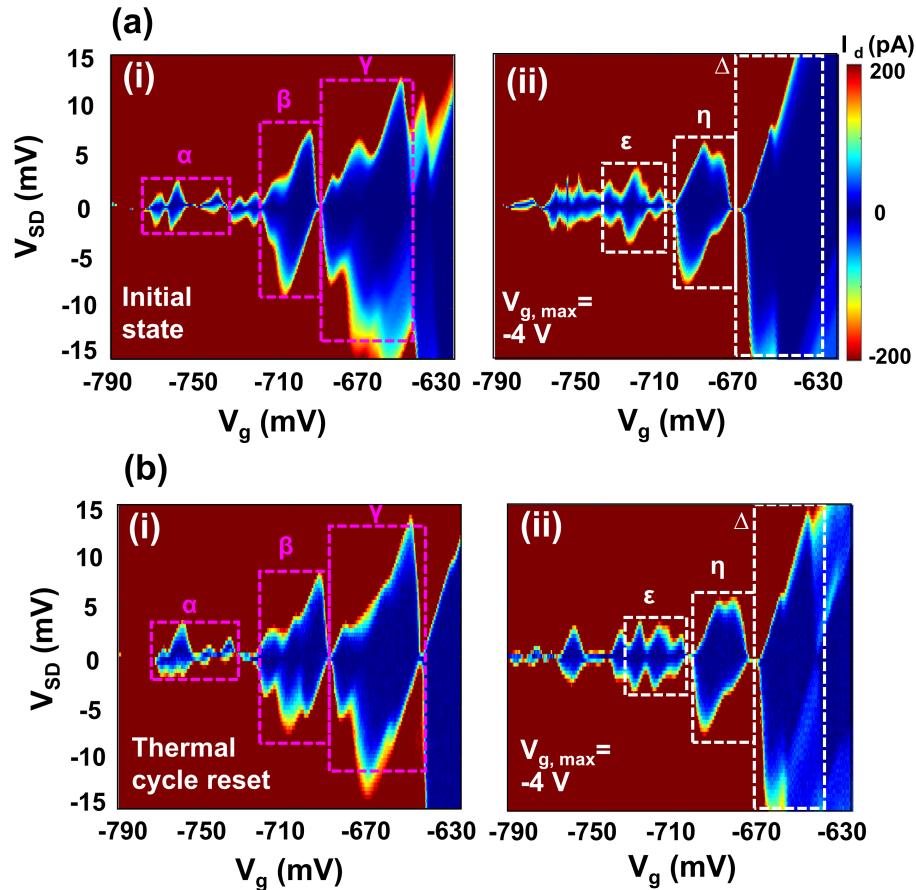

5.4 CSDs generated by biasing the source and gate, whilst measuring the drain current in the sub-threshold region for device 2. (a) Current CSDs with the initial pre-stressed state (a)(i) and moderate stress,  $V_{g,\max} = -4$  V (a)(ii). After a thermal cycle, from 2 K to 295 K and back to 2 K, another CSD is taken (b)(i) as well as after applying a second stress of -4 V (b)(ii). The rectangles outlined in dashed pink highlight Coulomb-diamonds which closely match in (a)(i) and (b)(i). The white dashed rectangles in (a)(ii) and (b)(ii) highlight similarities in regions after applying the first and second -4 V stress. . . . . 61

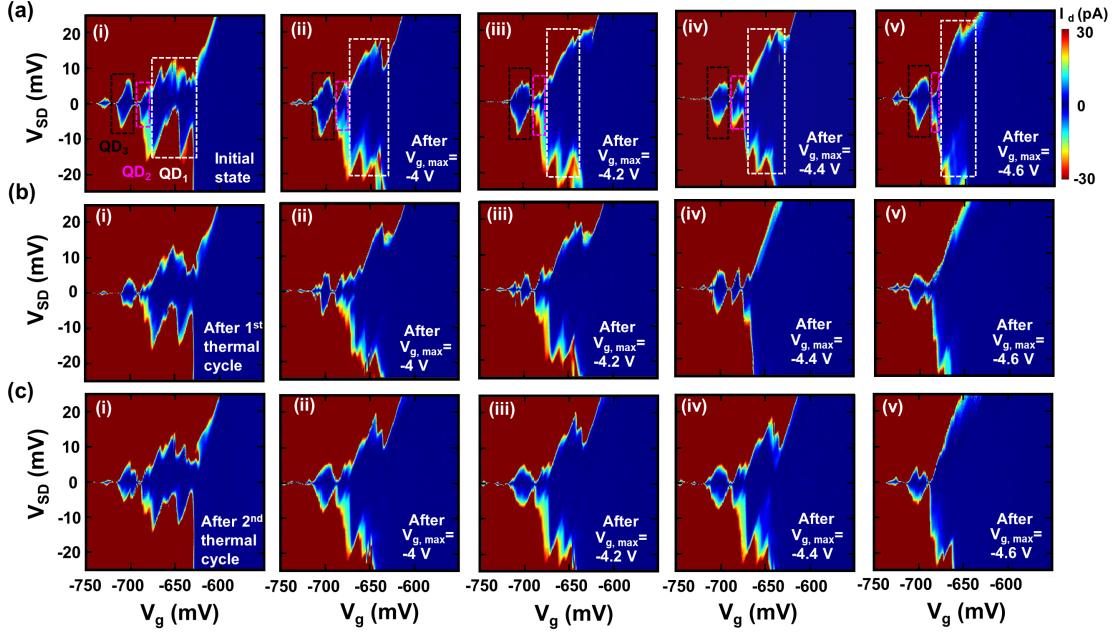

5.5 CSDs generated from experimental data from device 3 by biasing the source ( $V_{SD}$ ) and gate ( $V_g$ ), whilst measuring drain current ( $I_d$ ) in the sub-threshold region. (a) CSDs taken of the initial state and immediately after  $V_{g,\max} = -4$  V, -4.2 V, -4.4 V and -4.6 V stress sweeps in (i)-(v) respectively. The white, pink and black dashed rectangles highlight the changes to the Coulomb-diamond pattern from  $QD_1$ ,  $QD_2$  and  $QD_3$  respectively, as a result of stress-induced changes at the interface. (b) After performing one thermal cycle from 2 K to 295 K and back to 2 K, the CSDs are remeasured with identical parameters in (i)-(v). (c) A second thermal cycle is performed and the CSDs are retaken again in (i)-(v) to verify a consistent response. . . . . 62

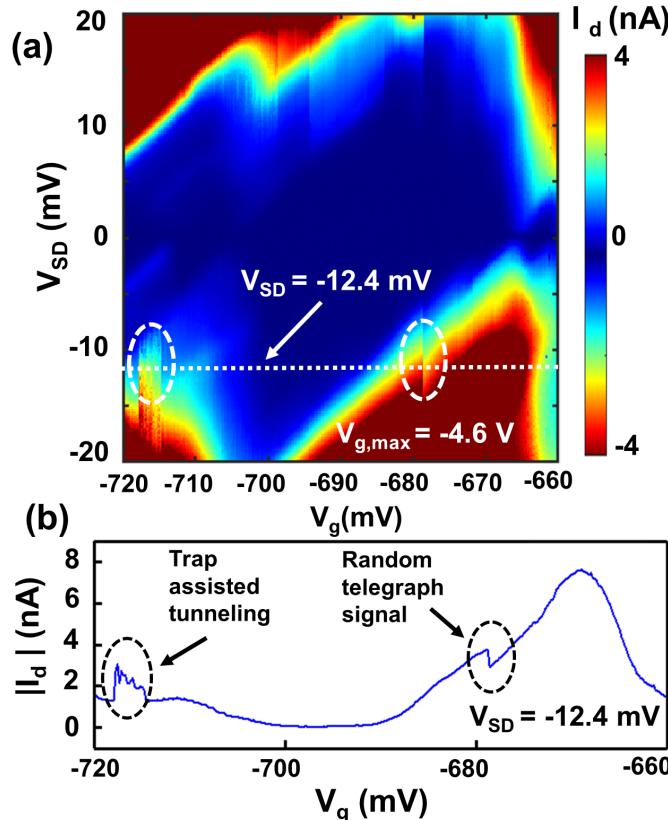

5.6 (a) Enlargement of unstable region of device 1 at the edge of a Coulomb-diamond after  $V_{g,\max} = -4.6$  V, showing discrete switching from a trap in the highlighted areas. (b)  $I_d - V_g$  sweep with  $V_{SD} = -12.4$  mV. A significant random telegraph signal event can be identified at -678 mV  $V_g$  as well as trap assisted tunneling at -715 mV  $V_g$ . . . . . 64

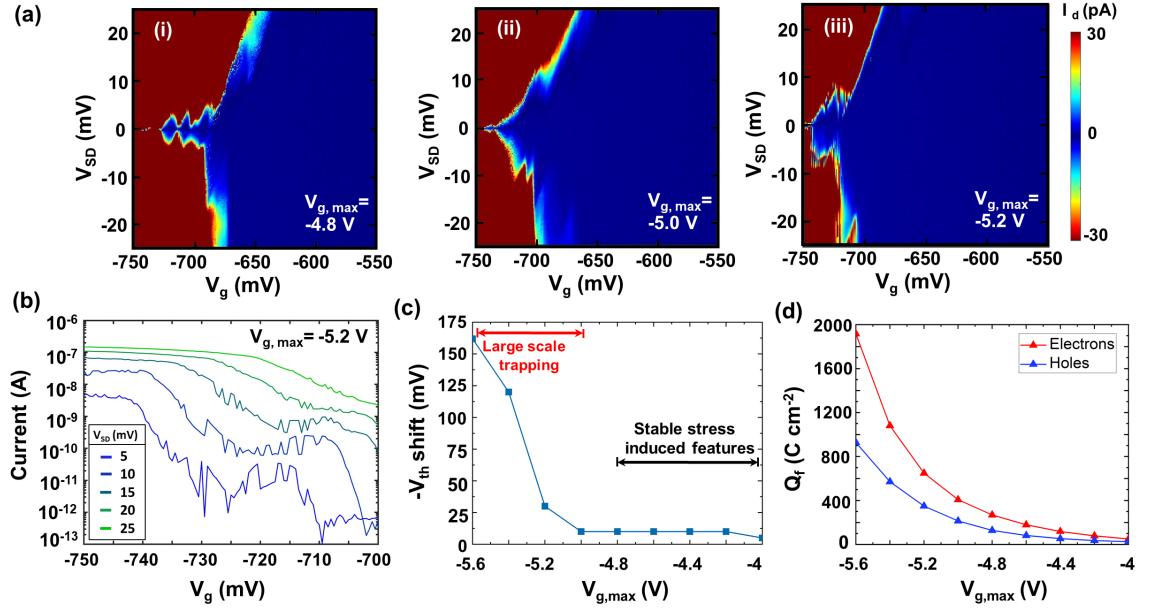

5.7 For  $V_{g,\max} = -4.8$  V and beyond, the experimental data of device 3 suggests that the device stability is compromised from large-scale trapping. (a)(i)-(iii) CSDs at elevated  $V_{g,\max}$  values of -4.8 V, -5 V and -5.2 V respectively. The Coulomb diamonds appear unstable in (i) with RTS becoming more prominent in (ii) and (iii). (b)  $I_d - V_g$  sweeps after  $V_{g,\max} = -5.2$  V for  $V_{SD} = 5-25$  mV, the RTS becomes very prominent and greatly affects device performance. (c) The respective change in threshold voltage ( $V_{th}$ ) shift as the maximum applied stress voltage,  $V_{g,\max}$ , increased from -4 V to -5.6 V. A significant shift can be noted above  $V_{g,\max} = -5$  V. (d) Charge fluence ( $Q_f$ ) for both electrons and holes through the oxide at each  $V_{g,\max}$ . . . . . 65

---

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

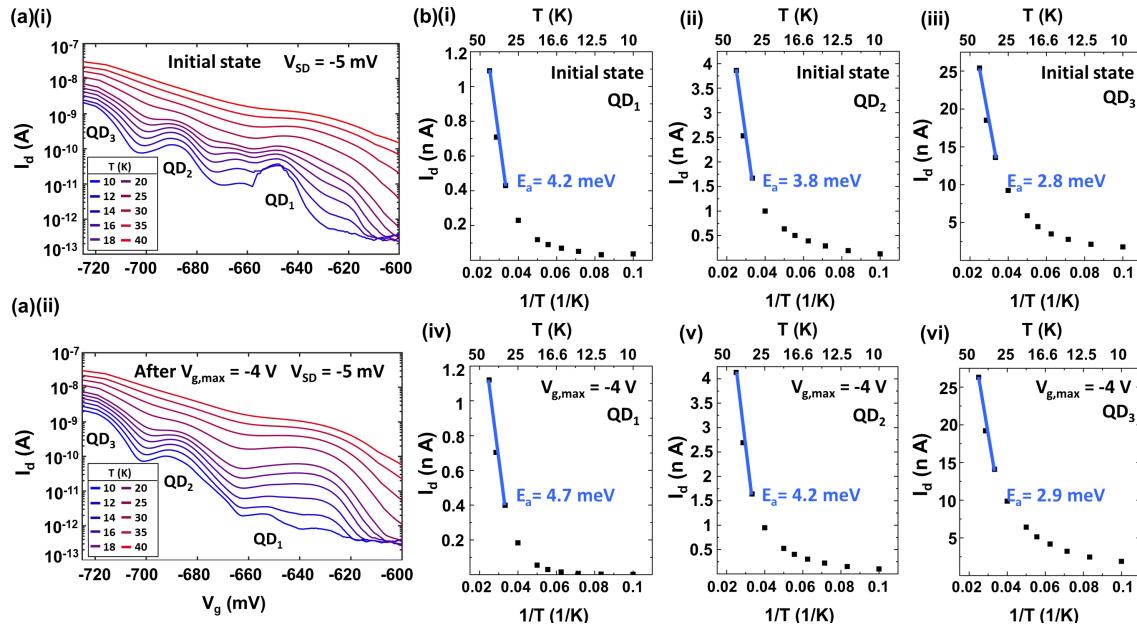

| 5.8  | Estimating changes to the $E_a$ after stress by using the QD temperature dependence of device 3. (a)(i) Coulomb oscillation peaks at 10-40 K for QD <sub>1</sub> , QD <sub>2</sub> and QD <sub>3</sub> in the initial pre-stressed state and after applying $V_{g,\max} = -4$ V in (a)(ii). (b)(i)-(iii) Arrhenius plots over a 10-40 K temperature range to extract $E_a$ from the Coulomb oscillation peaks of each QD during the initial state and after applying $V_{g,\max} = -4$ V in (b)(iv)-(vi). | 66 |

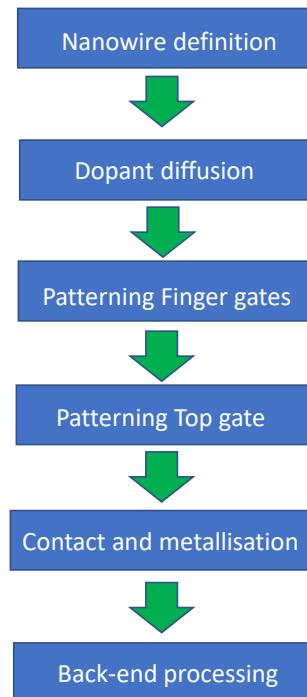

| 6.1  | The process flow for the fabricating Si nano-wires . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                              | 74 |

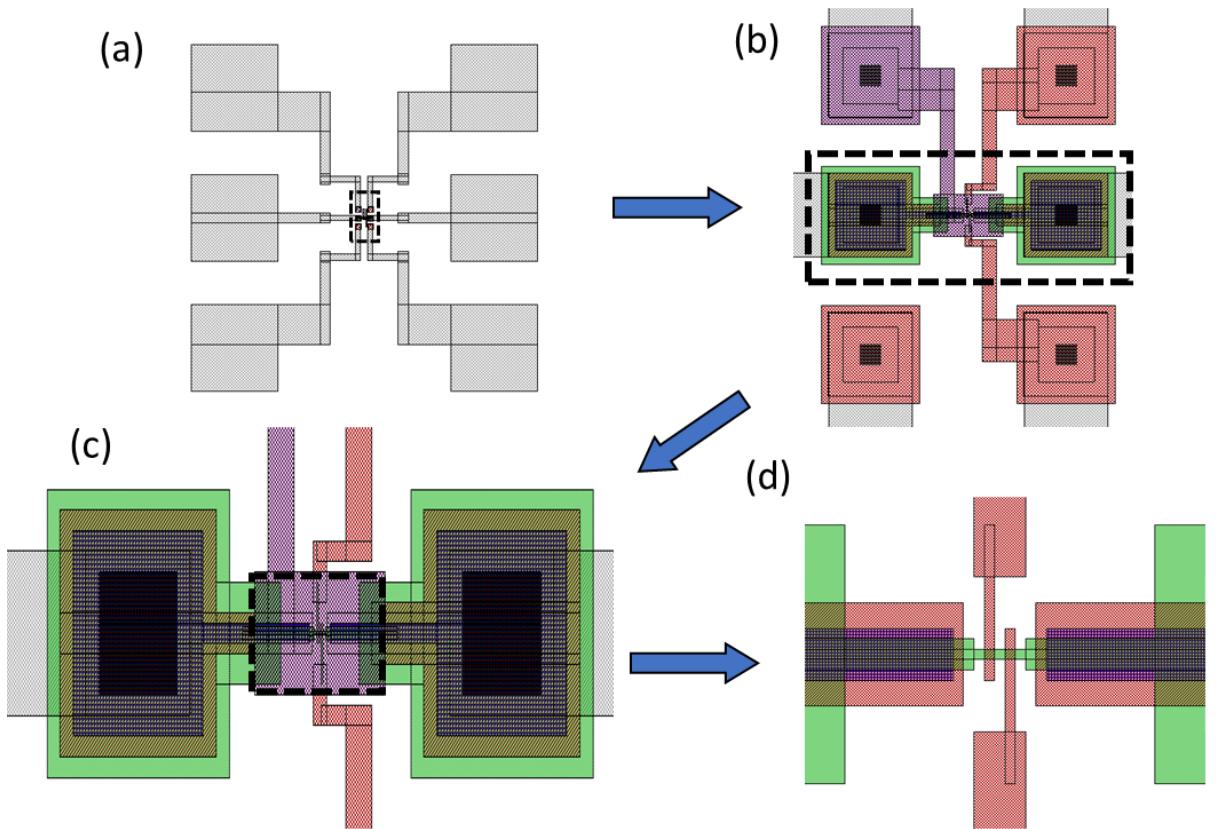

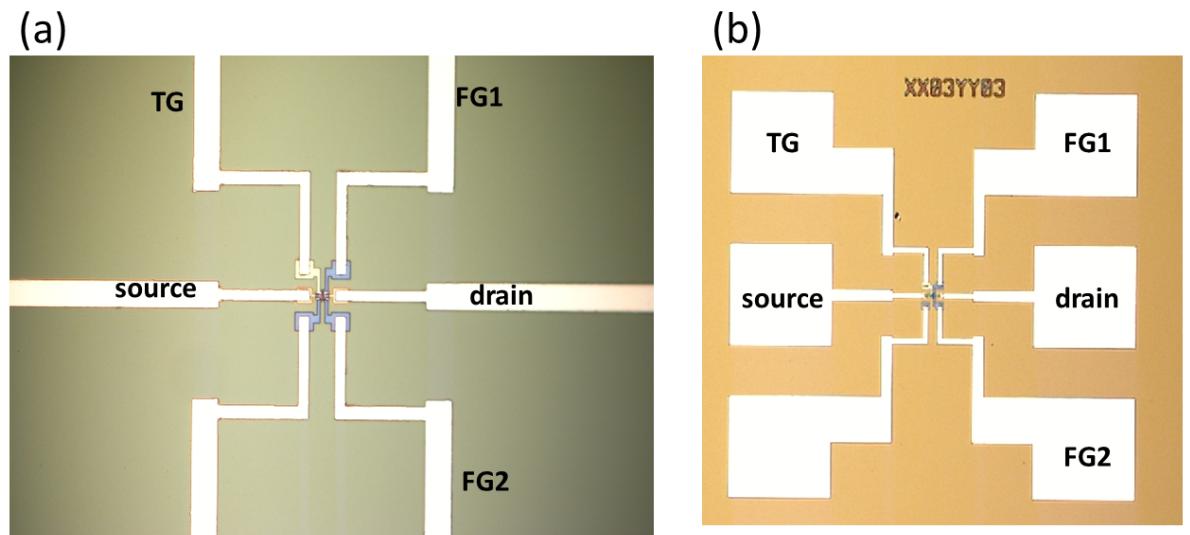

| 6.2  | Device images at various levels within the L-edit design software (a) Entire device overview with metal layer and pads visible. (b) Zoomed in image of device contact level. (c) Higher magnification from highlighted region in (b) with gate structures becoming visible. (d) Enhanced image from highlighted area in (c), showing the device core with nanowire and FG <sub>1</sub> and FG <sub>2</sub> . TG is omitted for clarity which would cover the entire area in (d). . . . .                  | 75 |

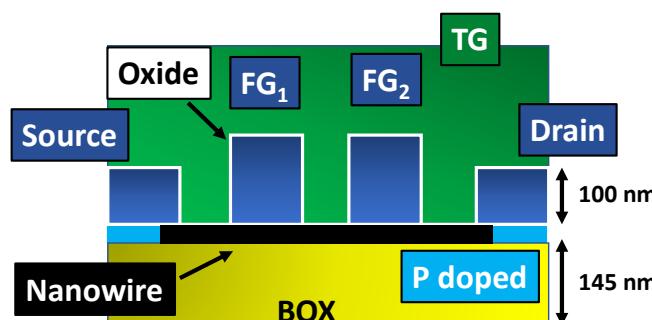

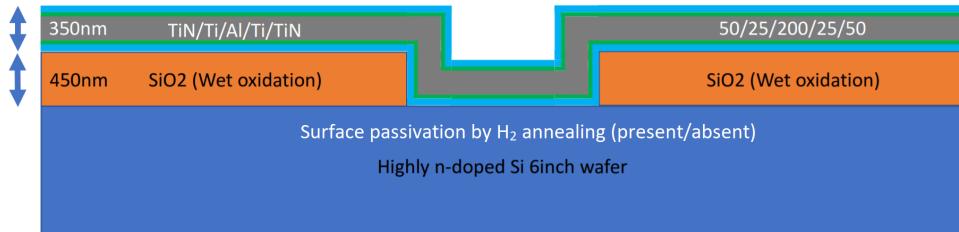

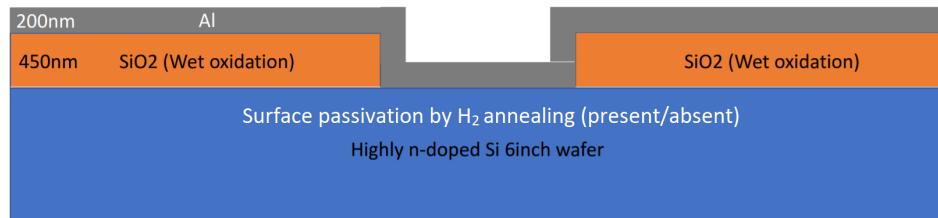

| 6.3  | Device cross-section with gate stack, source/drain and oxide visible. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                             | 76 |

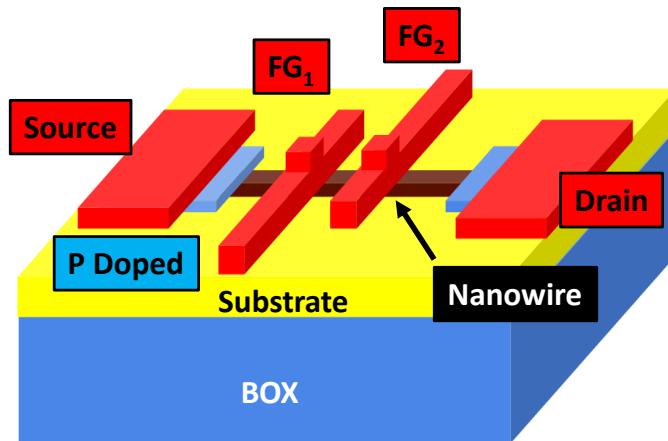

| 6.4  | 3D schematic of a standard device design with the nanowire, source/drain and FG <sub>1</sub> and FG <sub>2</sub> shown (TG removed for display purposes). . . . .                                                                                                                                                                                                                                                                                                                                         | 77 |

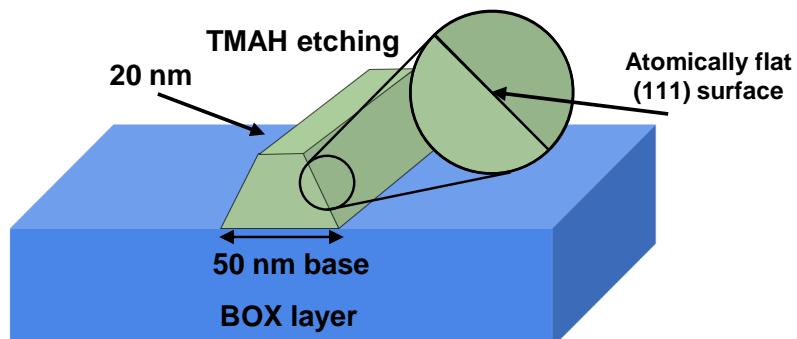

| 6.5  | A diagram displaying the nanowire trapezoidal shape after tetramethylammonium hydroxide (TMAH) wet etching and removing the hard mask. . . . .                                                                                                                                                                                                                                                                                                                                                            | 77 |

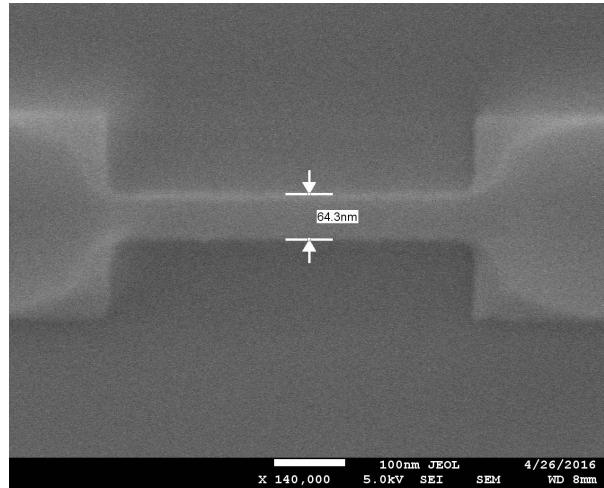

| 6.6  | SEM image showing nanowire definition after Tetramethylammonium Hydroxide (TMAH), with a measured width of 64.3 nm for a nanowire with a designed width of 75 nm before an overetch was applied. . . . .                                                                                                                                                                                                                                                                                                  | 78 |

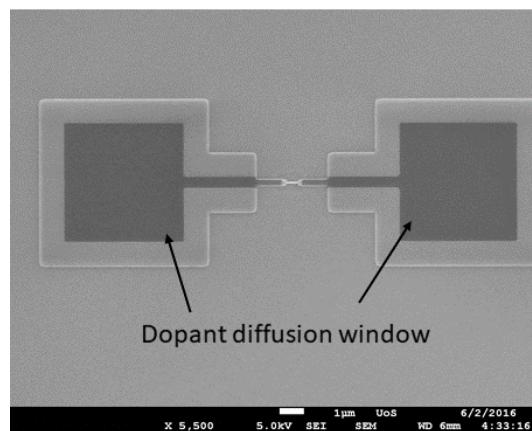

| 6.7  | SEM image showing the dopant diffusion window for the source/drain. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                               | 78 |

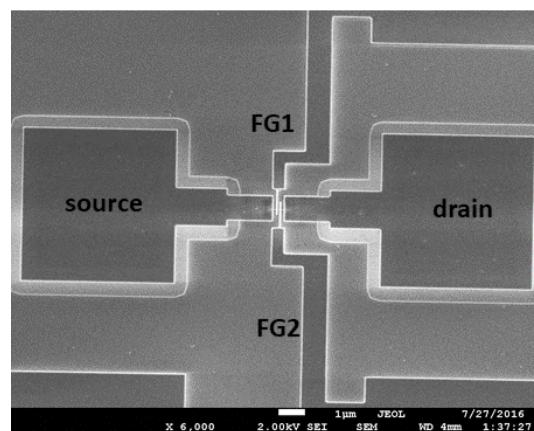

| 6.8  | SEM image of nanowire device after FG and source/drain patterning. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                | 79 |

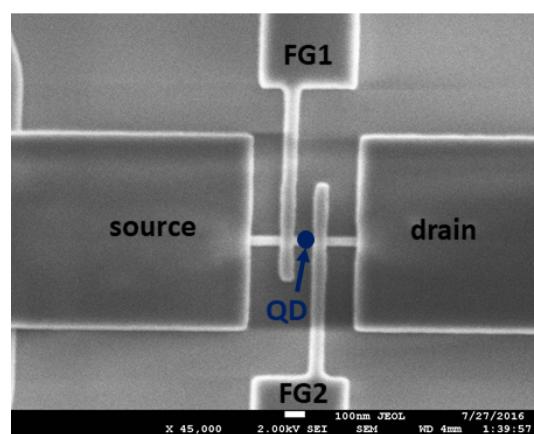

| 6.9  | Higher magnification SEM image of nanowire device after FG patterning with the area of QD formation indicated. . . . .                                                                                                                                                                                                                                                                                                                                                                                    | 79 |

| 6.10 | Optical image after TG patterning, where TG cover the entire device core area. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                    | 80 |

| 6.11 | Optical image after contact holes are made in the device pads before metallisation. . . . .                                                                                                                                                                                                                                                                                                                                                                                                               | 81 |

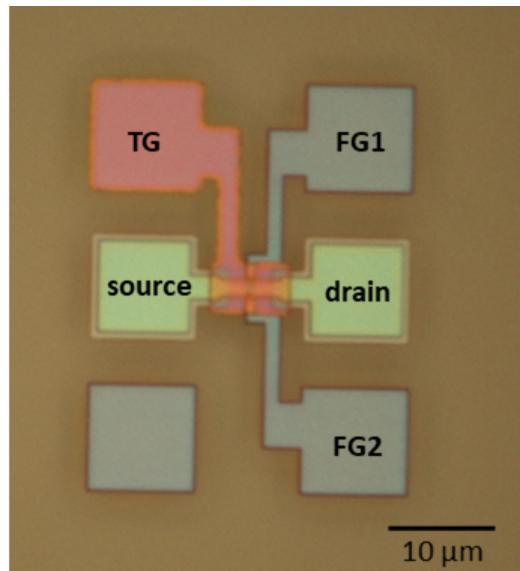

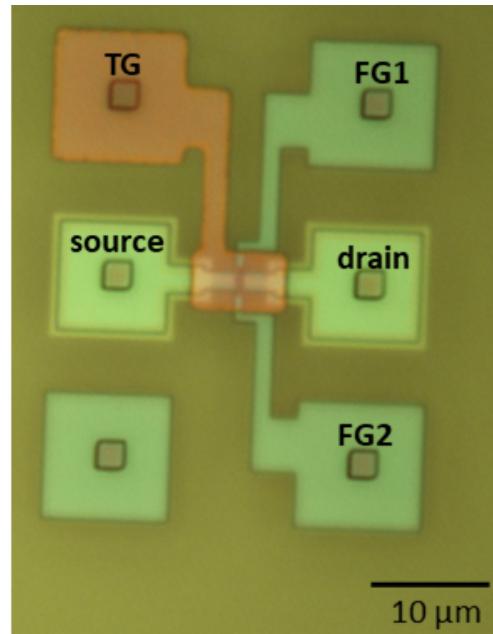

| 6.12 | (a) Optical image after metallisation. (b) Optical image of an entire completed device with aluminium pads visible . . . . .                                                                                                                                                                                                                                                                                                                                                                              | 81 |

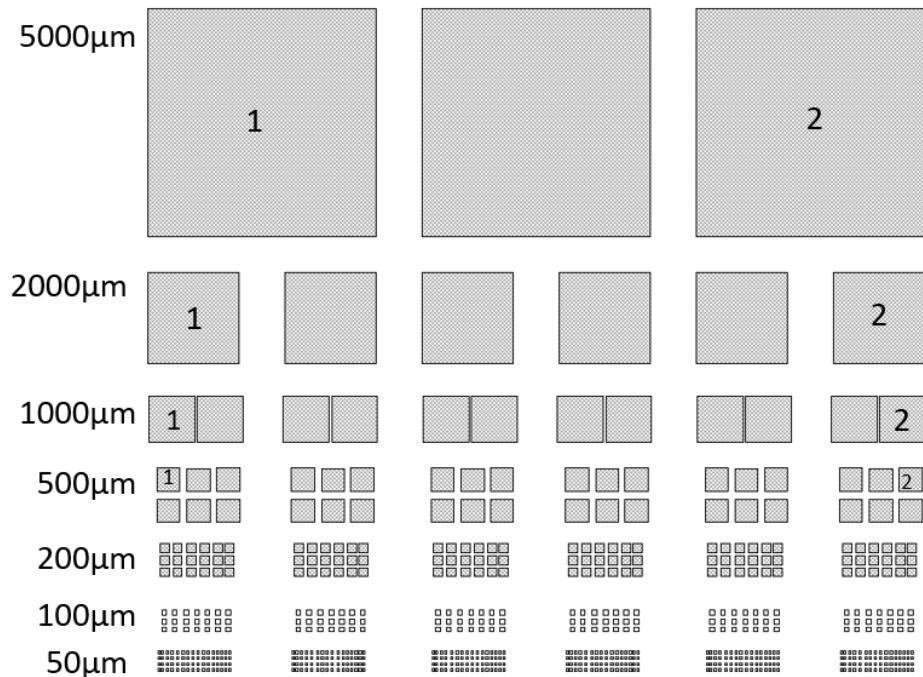

| 6.13 | Schematics for the metal stack structures of the four wafers as well as the pad layout and sizes for electrical measurements. . . . .                                                                                                                                                                                                                                                                                                                                                                     | 83 |

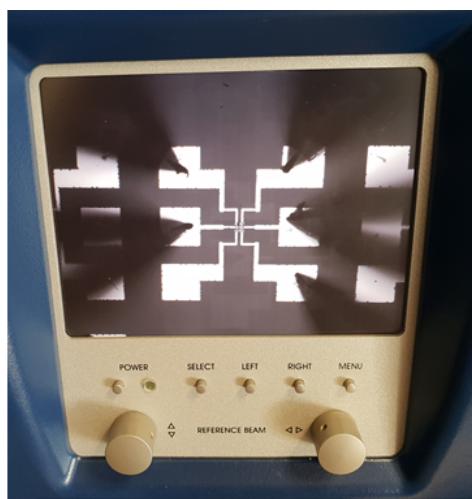

| 6.14 | Probe-station microscope image of nanowire device during the validation process . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                 | 84 |

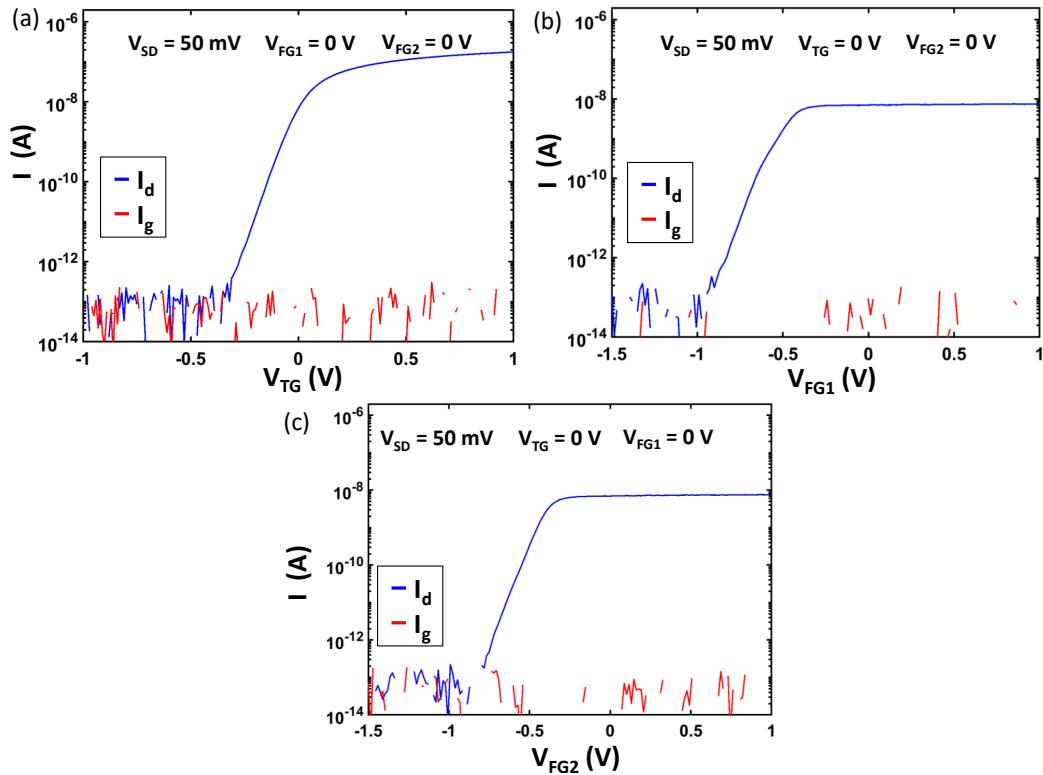

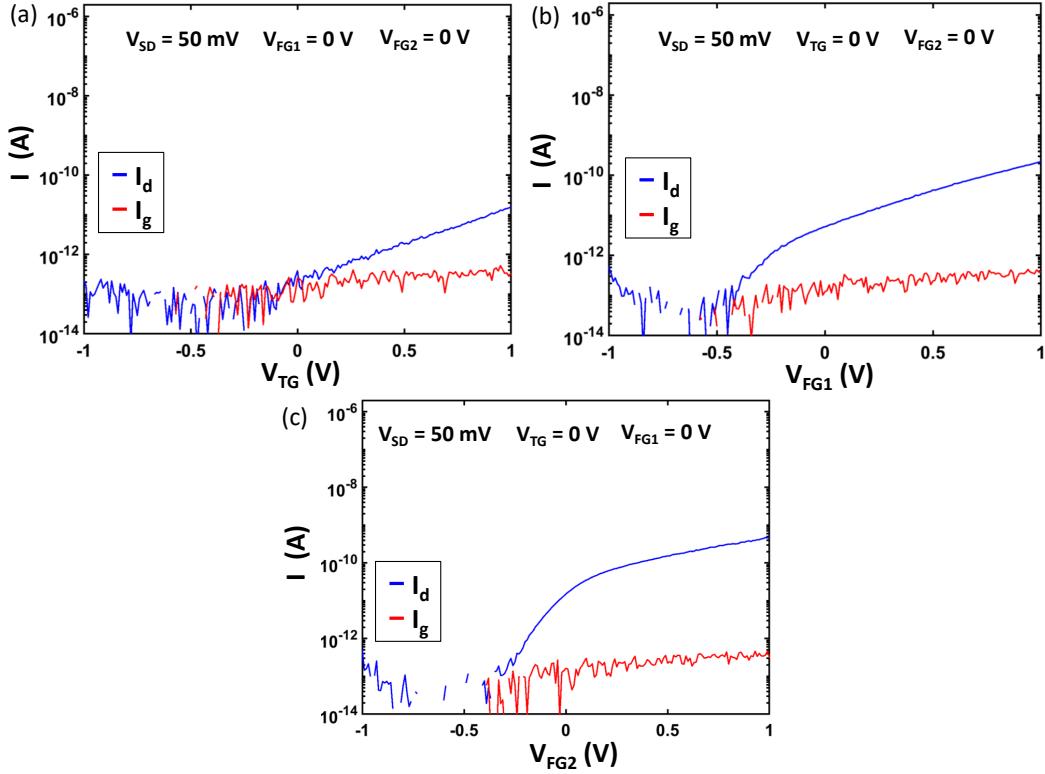

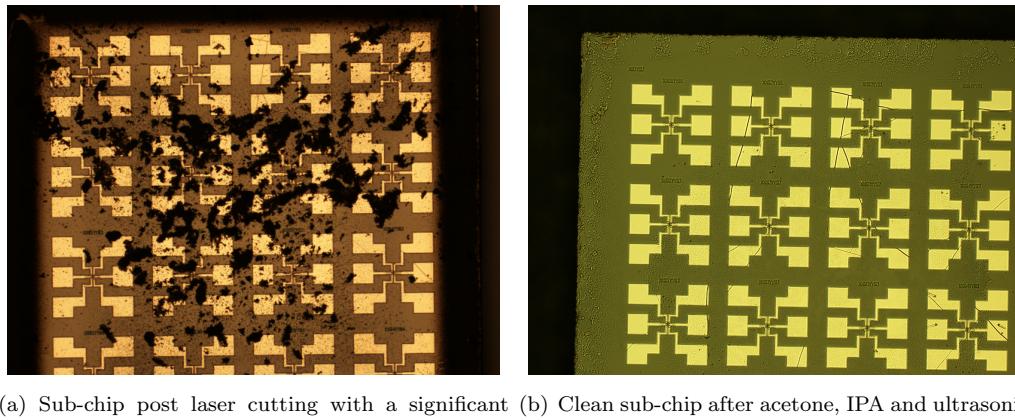

| 6.15 | $I - V$ characteristics for a SET48 device with a nanowire diameter of 50 nm together with FG width and spacing equal to 100 nm. (a) displays a TG sweep, while (b) and (c) show FG <sub>1</sub> and FG <sub>2</sub> sweeps respectively at $V_{SD} = 50$ mV. . . . .                                                                                                                                                                                                                                     | 85 |

| 6.16 | $I - V$ characteristics for a SET57 device with a nanowire diameter of 40 nm together with FG width and spacing equal to 100 nm. (a) displays a TG sweep, while (b) and (c) show FG <sub>1</sub> and FG <sub>2</sub> sweeps respectively at $V_{SD} = 50$ mV. . . . .                                                                                                                                                                                                                                     | 86 |

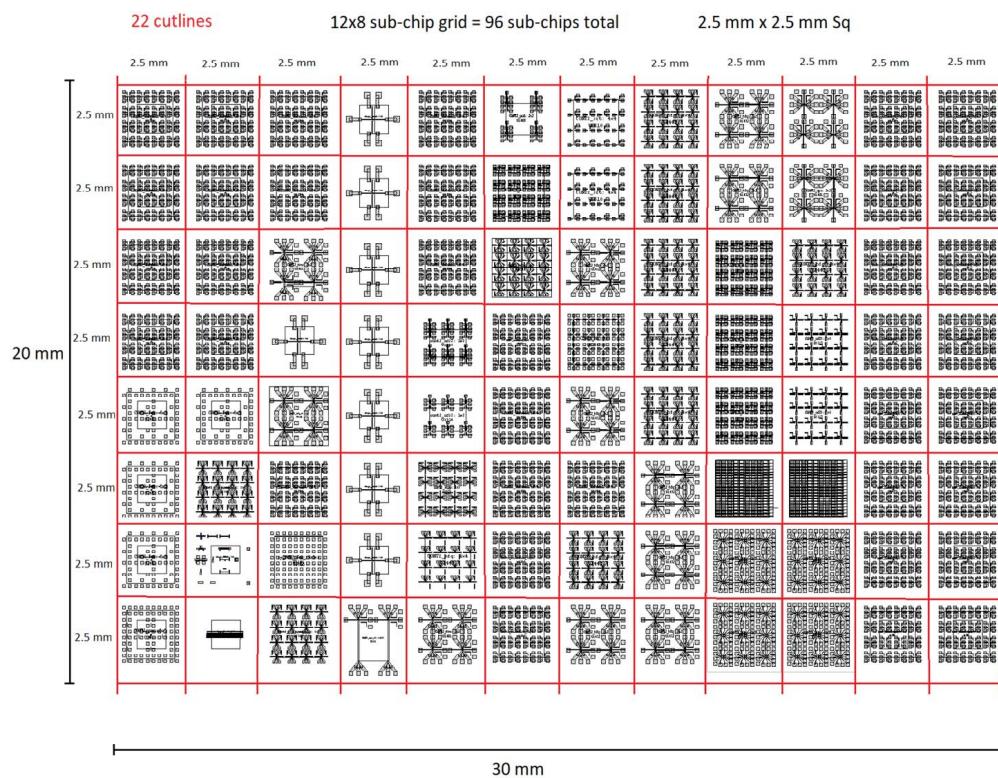

| 6.17 | SET57 chip with lines added for laser cutting into 2.5 mm sub-chips . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                             | 87 |

| 6.18 | Dicing and laser cutting samples from SET57 . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 87 |

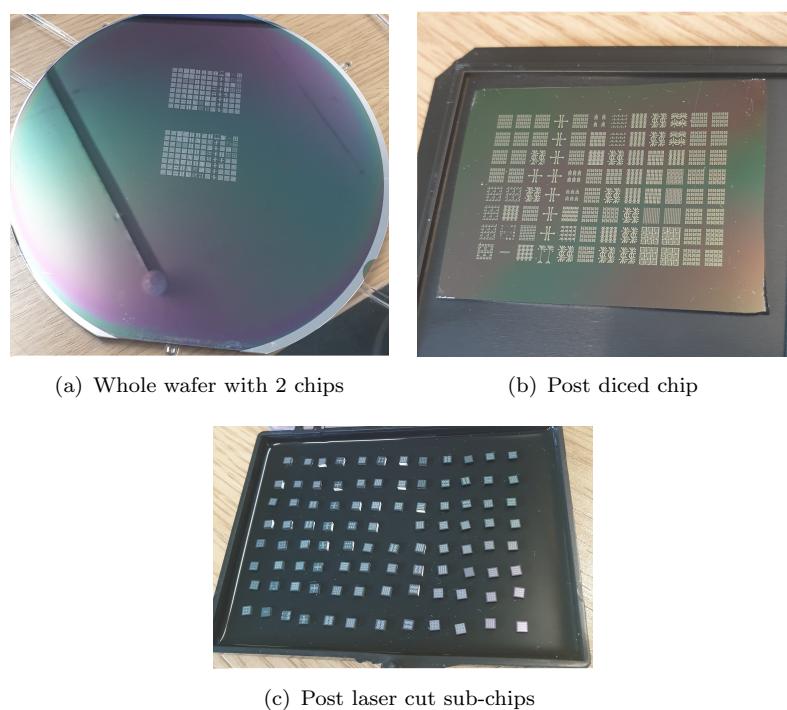

| 6.19 | Clean debris from device terminals after laser cutting . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                          | 88 |

---

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.20 | Wire-bonded SET48 device onto the cryostat sample holder viewed through a x20 zoom optical microscope lens . . . . .                                                                                                                                                                                                                                                                                                                 | 89  |

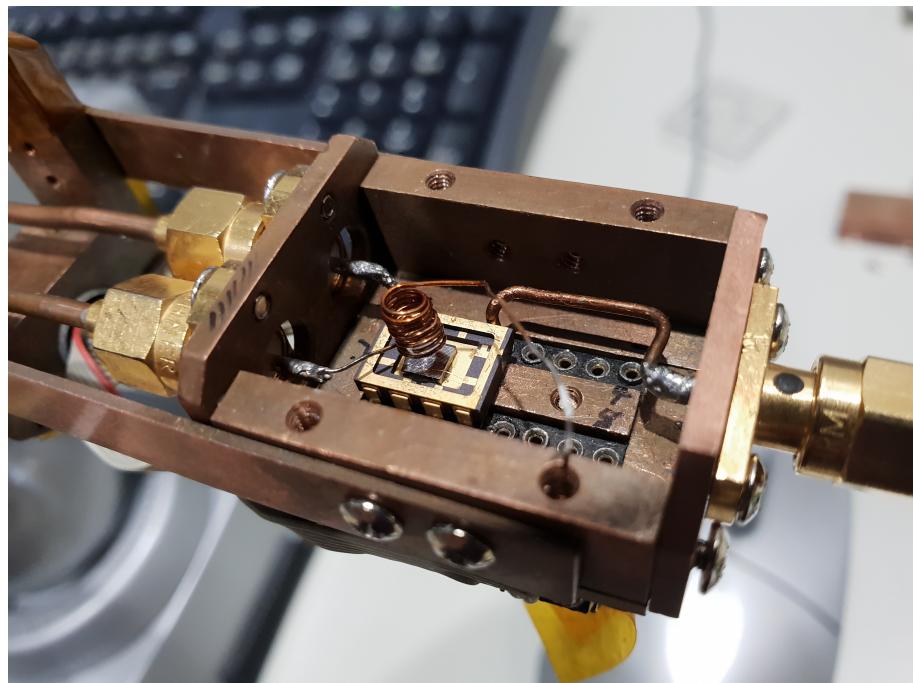

| 6.21 | Nanowire device after loading into the probe insert for low temperature characterisation at The Riken Institute. . . . .                                                                                                                                                                                                                                                                                                             | 89  |

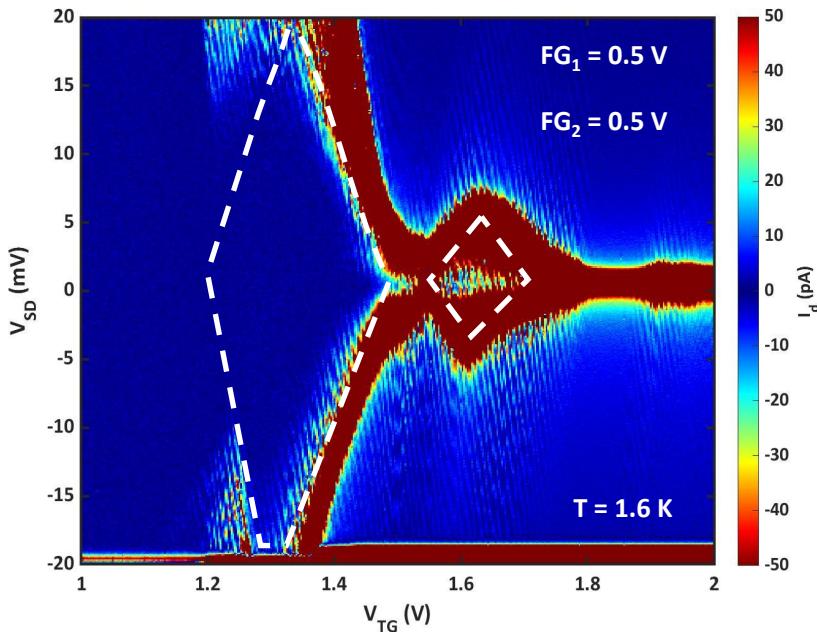

| 6.22 | CSD 1, showing single QD transport observed for device 1 from an SET48 sample with a nanowire and FG width/spacing of 100 nm/100 nm/150 nm at T = 1.6 K. $V_{FG1}$ and $V_{FG2}$ are both fixed at 0.5 V, while $V_{SD}$ and $V_{TG}$ are swept from -20 mV to 20 mV and 1 V to 2 V respectively. . . . .                                                                                                                            | 90  |

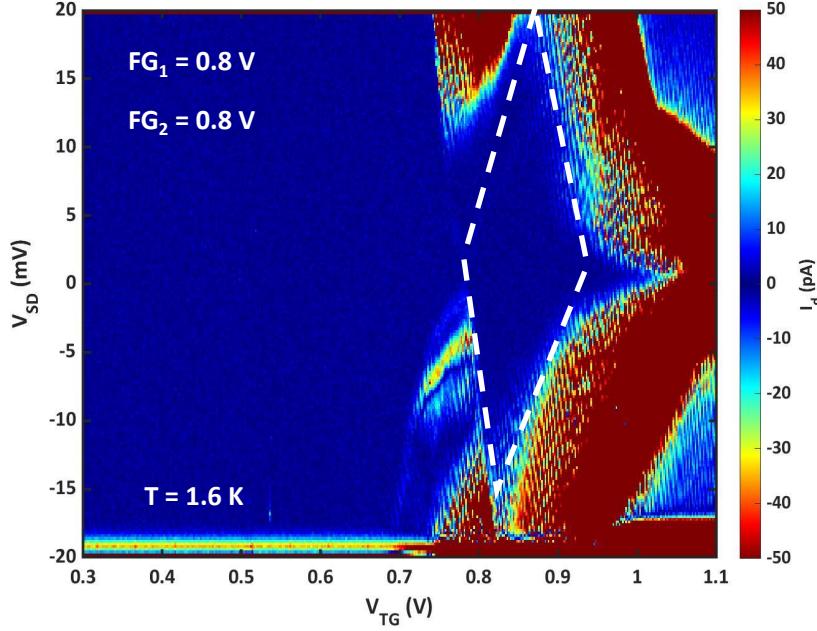

| 6.23 | CSD 2, showing single QD transport for device 1, observed from an SET48 sample with a nanowire and FG width/spacing of 100 nm/ 100 nm/150 nm at T = 1.6 K. $V_{FG1}$ and $V_{FG2}$ are both fixed at 0.8 V, while $V_{SD}$ and $V_{TG}$ are swept from -20 mV to 20 mV and 0.3 V to 1.1 V respectively. . . . .                                                                                                                      | 91  |

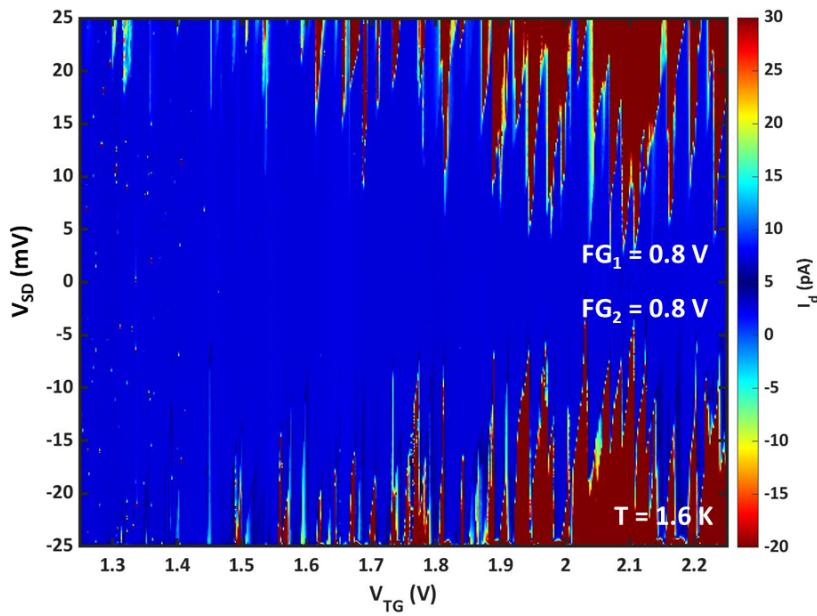

| 6.24 | CSD displaying single electron transport for device 2 through a series Coulomb-diamonds from an SET48 sample with nanowire and FG width/spacing of 50 nm/150 nm/150 nm respectively at T = 1.6 K. $V_{FG1}$ and $V_{FG2}$ are both fixed at 0.8 V, while $V_{SD}$ and $V_{TG}$ are swept from -25 mV to 25 mV and 1.25 V to 2.25 V respectively. It is estimated that the QDs contain more than 30 electrons when $V_{TG}$ . . . . . | 93  |

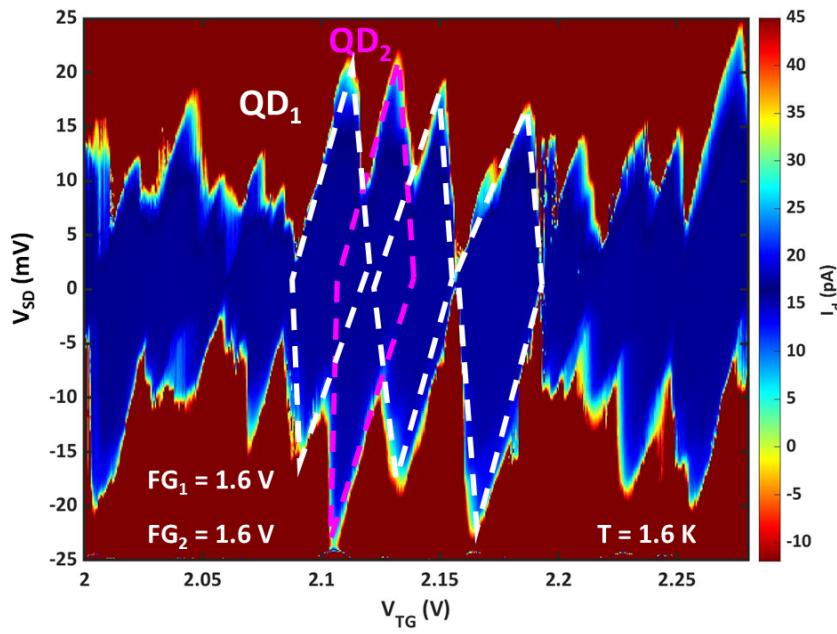

| 6.25 | CSD showing double-QD transport observed for device 2 from an SET48 sample with nanowire and FG width/spacing of 50 nm/150 nm/150 nm respectively at T = 1.6 K. $V_{FG1}$ and $V_{FG2}$ are both fixed at 1.6 V, while $V_{SD}$ and $V_{TG}$ are swept from -25 mV to 25 mV and 2 V to 2.3 V respectively. The overlapping of the highlighted Coulomb-diamonds suggests two QD are present, and are of a similar size. . . . .       | 94  |

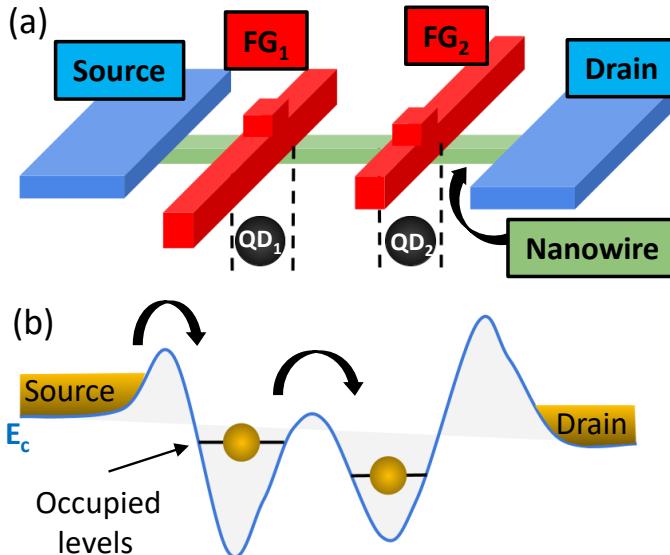

| 6.26 | (a) Device schematic showing the formation of two QDs below FG <sub>1</sub> and FG <sub>2</sub> . (b) Energy level diagram of how conduction band bending enables discrete levels to form as a product of quantum confinement. . . . .                                                                                                                                                                                               | 94  |

| A.1  | HP4142 measurement system after installation of new SMUs. . . . .                                                                                                                                                                                                                                                                                                                                                                    | 99  |

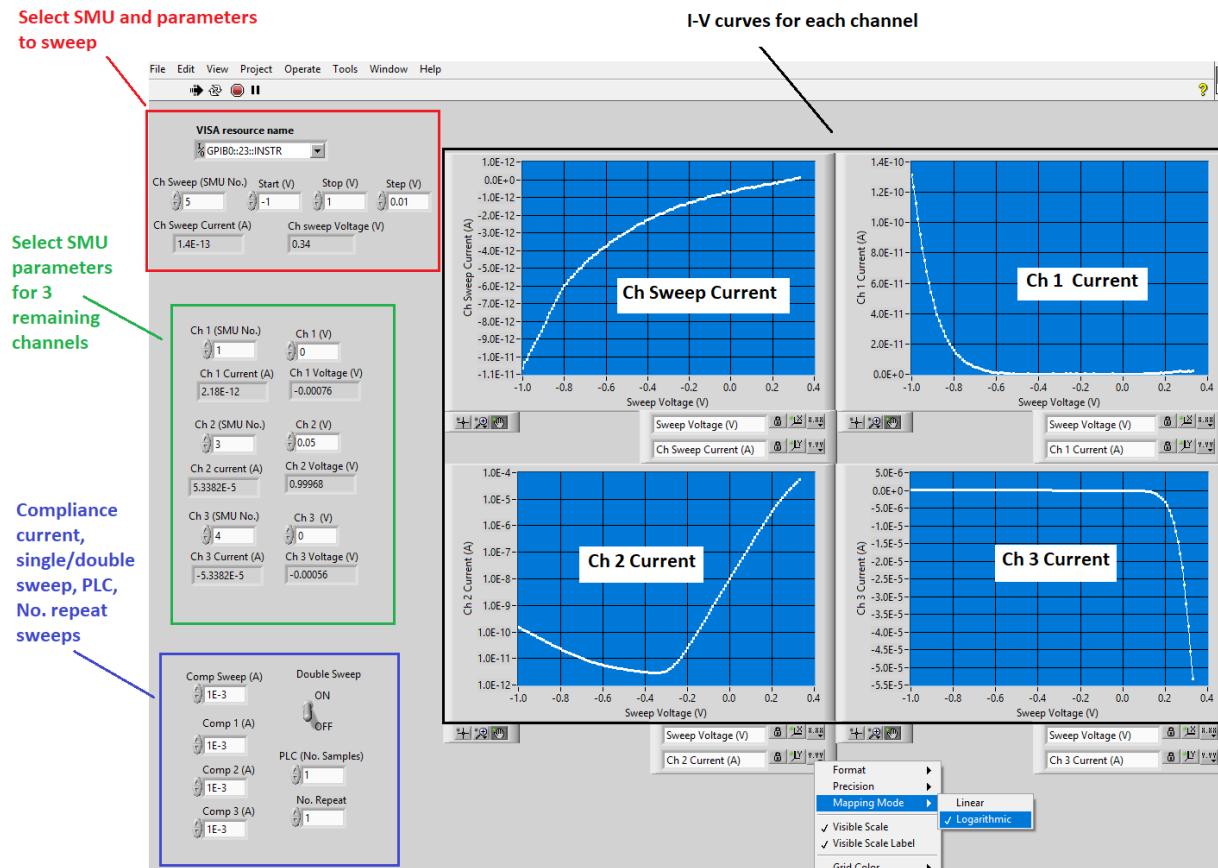

| A.2  | LabVIEW program created to operate a HP4142 system for CMOS characterisation. . . . .                                                                                                                                                                                                                                                                                                                                                | 100 |

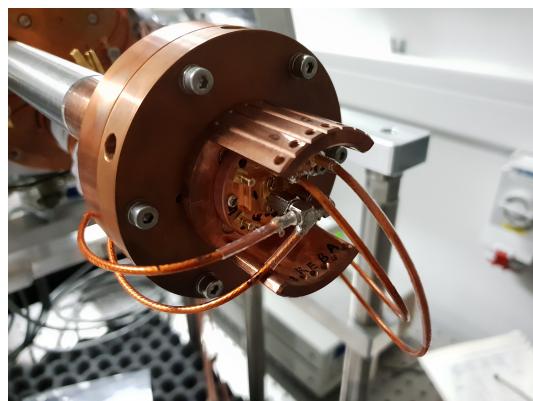

| B.1  | Image taken of the Janis cryostat after re-wiring with SMA cables with new sample holder mounted. . . . .                                                                                                                                                                                                                                                                                                                            | 101 |

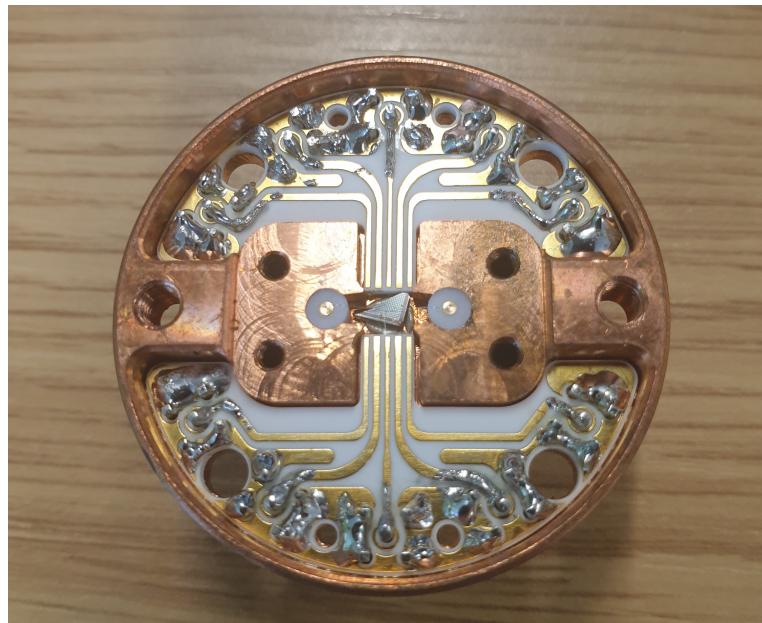

| B.2  | Custom made HF sample holder designed for SEP operation using the Janis cryostat . . . . .                                                                                                                                                                                                                                                                                                                                           | 102 |

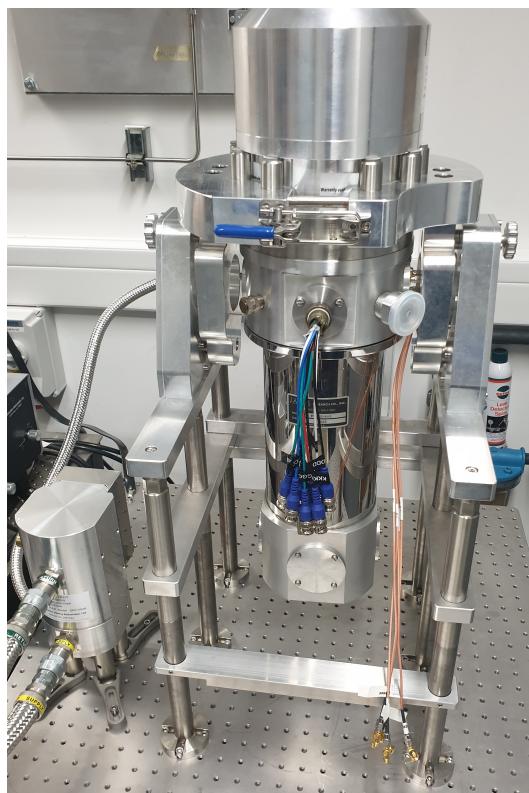

| B.3  | Image of the entire Janis cryostat system with radiation shield and vacuum cover fitted, ready for the cool-down process. . . . .                                                                                                                                                                                                                                                                                                    | 102 |

**University of Southampton Thesis Licence**

Copyright © and Moral Rights for this thesis and, where applicable, any accompanying data are retained by Joseph William Hillier (the copyright holder). A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis and the accompanying data cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder. The content of the thesis and accompanying research data (where applicable) must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holder. When referring to this thesis and any accompanying data, full bibliographic details must be given, e.g.

Thesis: Joseph William Hillier (2022) "Tunable spin and charge transport using CMOS-compatible silicon quantum dots for quantum information applications", School of Electronics and Computer Science, University of Southampton, Southampton, United Kingdom, PhD Thesis

Data: Joseph William Hillier (2022) Dataset for Doctoral thesis 'Tunable spin and charge transport using CMOS-compatible silicon quantum dots for quantum information applications'. DOI: <https://doi.org/10.5258/SOTON/D2068>

## Declaration of Authorship

I, Joseph W. Hillier, declare that this thesis and the work presented in it is my own and has been generated by me as the result of my own original research.

I confirm that:

1. This work was done wholly or mainly while in candidature for a research degree at this University;

2. Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

3. Where I have consulted the published work of others, this is always clearly attributed;

4. Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

5. I have acknowledged all main sources of help;

6. Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

7. Parts of this work have been published as:

**J. Hillier**, K. Ono, K. Ibukuro, F. Liu , Z. Li , M. K. Husain, H. N. Rutt, I. Tomita, Y. Tsuchiya, K. Ishibashi and S. Saito. Probing hole spin transport of disorder quantum dots via Pauli spin-blockade in standard silicon transistors. *Nanotechnology*, 32, 260001, 2021.

**J. Hillier**, K. Ibukuro, F. Liu, M. K. Husain, J. Byers, I. Tomita, H. N. Rutt, Y. Tsuchiya, and S. Saito. Investigating stability and tunability of quantum dot transport in silicon MOSFETs via the application of electrical stress. *J. Phys. D: Appl. Phys.* 55, 105107, 2022.

**J. Hillier**, K. Ono, K. Ibukuro, F. Liu , Z. Li , M. K. Husain, H. N. Rutt, I. Tomita, Y. Tsuchiya, K. Ishibashi and S. Saito. Single spin sensing in silicon p-type Metal-Oxide-Semiconductor Field-Effect Transistors. *International conference for the quantum science and technology community*, 3193, 2020.

**J. Hillier**, K. Ono, K. Ibukuro, F. Liu , Z. Li , M. K. Husain, H. N. Rutt, I. Tomita, Y. Tsuchiya, K. Ishibashi and S. Saito. Atomically flat trapezoidal silicon nanowires for tunable gate defined quantum dots. *Silicon Quantum Information Processing Workshop*, 2021.

Signature:

Date:

# Acknowledgements

Firstly, I wish to give my sincere thanks and admiration to my supervisors Prof. Shinichi Saito and Dr. Yoshishige Tsuchiya who gave me the opportunity to pursue this project at The University of Southampton. Their leadership, guidance and global contacts enabled me to develop the necessary tools to thrive in a research environment, including an unforgettable 3-month collaboration at The Riken Institute under Dr. Keiji Ono in Tokyo, Japan, who it was an honour to work under.

I would also like to thank the other members of my research group for their continued support, post-doctoral researcher Dr. Muhammad Khaled Husain and fellow PhD students Dr. Li Zuo, Dr. Fayong Liu, and Dr. Kouta Ibukuro - who I worked closely with. All of whom shared their extensive knowledge and experience throughout my four years. In addition, I'd like to recognise Dr. Kapil Debnath, Dr Moise Sotto, Dr. Daniel Burt and Dr James Byers who provided valuable feedback during the initial stages of my project.

Finally, I feel that the successful completion of my PhD would have not been possible without the immense support of my parents, William and Jayne, and of course my wife Jessica.

# Chapter 1

## Introduction

Silicon (Si) based devices have become the cornerstone of modern technology, and are now a leading candidate for quantum information processing architectures [1, 2, 3, 4]. Promising alternatives to traditional metal-oxide-semiconductor field-effect transistors (MOSFETs) take the form of quantum dots (QDs) acting as quantum bits (qubits) in single electron devices through the use of charge and spin as the fundamental building blocks [5, 6, 7]. The use of multi-gate device architectures in particular has led to many breakthroughs by tuning the potential profiles defining QDs as well as the inter-dot tunneling barriers for precise control, where development is undertaken by academia and large pre-industrial fabrication facilities [8, 9, 10, 11, 12, 13, 14].

Various methods to observe and control spin phenomena have been also proposed [15, 16, 17]. Spin based quantum information devices through multi-gate QD systems in particular have led to many breakthroughs by tuning the potential profiles defining the QD as well as the inter-dot tunneling barriers for precise control [18, 19, 20]. However, although employing many gates certainly adds flexibility, it is a fabrication intensive process. One alternative is to use devices which are Si VLSI (very-large-scale integration) compatible. Efforts have been made to take advantage of features already present at the single electron level in Si VLSI technology. The use of trap states within Si quantum devices can complement and even enhance single charge transport, with applications ranging from quantum information and quantum metrology, to bio-sensing and hardware security [21, 22, 23, 24].

One technological obstacle to overcome is that of electric-field mediated control for spin-based quantum information processing schemes, which relies on a strong spin-orbit (SO) interaction. This has led to investigations of spin transport schemes with an enhanced SO interaction through the use of holes, valley states and inversion layer asymmetry at the oxide interface [25, 26, 27, 28, 29]. Pauli spin-blockade (PSB), a double-QD phenomenon and common measurement tool used in spin transport systems, can also be

harnessed to study the SO interaction strength given that a device can be tuned into a PSB configuration.