17.02.2016

(21) Application No: 1414376.2

(22) Date of Filing: 13.08.2014

(71) Applicant(s):

**University of Southampton** Highfield, SOUTHAMPTON, Hampshire, SO17 1BJ, **United Kingdom**

(72) Inventor(s):

**Robert Geoffrey Maunder**

(74) Agent and/or Address for Service:

D Young & Co LLP 120 Holborn, LONDON, EC1N 2DY, United Kingdom (51) INT CL:

H04L 1/00 (2006.01)

H03M 13/27 (2006.01)

(56) Documents Cited:

EP 2429085 A

EP 1564893 A

(58) Field of Search:

INT CL H03M, H04L

Other: ONLINE: WPI, EPODOC, TXTE, INSPEC

- (54) Title of the Invention: Detection circuit, receiver, communications device and method of detecting Abstract Title: Turbo detection circuit and process

- (57) A detection circuit performs a turbo detection process to recover a frame of data symbols from a received signal, the symbols having been effected, by a Markov process with the effect that symbols in the received signal are dependent on one or more preceding symbols which can be represented as a trellis having plural stages. The detection circuit comprises a plurality of processing elements 706,708, each element is associated with one of the trellis stages. Each element receives soft decision values corresponding to symbols associated with the trellis stage, and each processing element is configured, in one clock cycle to receive fixed point data representing apriori forward slate metrics, a-priori backward state metrics, and a-priori soft decision values for the symbols for the trellis stage. For each cycle, the circuit processes, for each processing element, the a-priori information for symbols detected for the stage associated with the processing element, and t provides extrinsic soft decision values corresponding to the symbols for a next clock cycle of the detection process.

FIG. 8

FIG. 5

FIG. 6

FIG. 10

FIG. 10 (continued)

FIG. 11

FIG. 11 (continued)

FIG. 12 (continued)

FIG. 13

# 11 09 15

|                                                     | Log-BCJR LTE N E | Log-BCJR WIMAX N & | State-of-art LTE | State-of-art WiMAX |

|-----------------------------------------------------|------------------|--------------------|------------------|--------------------|

| Characteristic                                      | [40, 6144]       | [24, 2400]         | N ε [40, 6144]   | N E [40, 6144]     |

| Time periods per decoding iteration T               | 2N TtotP         | 2N TtotP           | N/64 TtotP       | N/32 TtotP         |

| Time period duration D                              | 1,13 TtotP       | 1.22 TtotP         | 0.43 TtotP       | 0.33 TtotP         |

| Complexity per decoding iteration C                 | 1.10 TtotP       | 1.25 TtotP         | 1.77 TtotP       | 1.58 TfotP         |

| Decoding iterations required /                      | 1/6 TtotP        | 1/4 TtotP          | ·. 1/6 TtotP     | 1/4 TtotP          |

| Overall throughput $\alpha 1/(T \times D \times I)$ | 2,65/N TtotP     | 1.64/N TtotP       | 893/N TtotP      | 388/N TtotP        |

| Overall latency Tx D x /                            | N/2.65 TtotP     | N/1.64 TtotP       | N/893 TtotP      | N/388 TfotP        |

| Overall complexity C x /                            | 0.18 TtotP       | 0.31 TtotP         | 0.30 TtotP       | 0.40 TtotP         |

| Memory required                                     | 9.33 TtotP       | 8.00 TtotP         | 1.25 TtotP       | 1.67 TtotP         |

|                                                     |                  |                    |                  |                    |

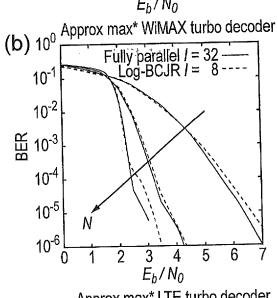

16/19

with an equivalent Log-BCJR Turbo Decoder and a State-of-the-Art Turbo Decoder, wherein TtotP = times that of the proposed fully-parallel Table 1 providing a performance comparison with a Fully-Parallel Turbo Decoder according to an embodiment of the present technique turbo decoder.

FIG. 14

| Log - BCJR                          | Forward recursion | (4) (5) (6) |  | 5 {5} 1.5 12 12 {1} 28 {2} 2 {2} 25.5 {5} |  | 0 8 .8{1} 0 14{3} | 94 (5) 12 30 30 (1) 62 (2) 4 (2) 138 (5) |             |   | $\{4\}$ 0 24 $24\{2\}$ 0 $32\{4\}$ 80 $\{6\}$ |

|-------------------------------------|-------------------|-------------|--|-------------------------------------------|--|-------------------|------------------------------------------|-------------|---|-----------------------------------------------|

| Fully-parallel of Present Technique |                   | (10) Tc     |  | 2 {2}   47.5 {5}                          |  | 14 {3}   30 {3}   |                                          | *********** |   | 32 (4) 80 (4)                                 |

| lot of Dro                          |                   | (6)         |  | ∞                                         |  | ∞                 | ·                                        |             |   | 24                                            |

|                                     | <u>a</u>          | 1           |  | ∞<br><u>~</u>                             |  | ∞                 | 000                                      |             | _ | 24                                            |

| P. P. P.                            |                   | (8) (2)     |  | 29.5 {3} 8                                |  | 0                 | 74 (3) 8                                 | <u> </u>    |   | 0                                             |

| Operation                           |                   |             |  | + 0L -                                    |  | max*              |                                          | + OL -      |   | max*                                          |

| Turbo Code Operation                |                   |             |  | LTE                                       |  |                   |                                          | WiMAX       |   |                                               |

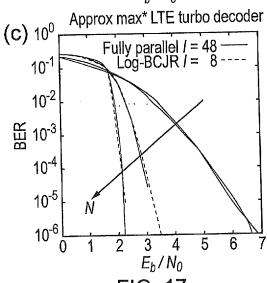

Table 2 providing an indication of numbers of calculations required for a Fully-parallel Turbo Decoder according to the present technique with an equivalent Log-BCJR Turbo Decoder.

FIG. 15

FIG. 17

# DETECTION CIRCUIT, RECEIVER, COMMUNICATIONS DEVICE AND METHOD OF DETECTING

# TECHNICAL FIELD OF THE DISCLOSURE

5

10

15

20

25

30

The present disclosure relates to detection circuits for performing a turbo detection process to recover a frame of data symbols from a received signal, the data symbols of the frame having been affected, during the process of transmission, by a Markov process with the effect that the data symbols of the frame in the received signal are dependent on one or more preceding data symbols which can be represented as a trellis having a plurality of trellis states. In some examples the detection circuit forms part of a receiver and operates in cooperation with another detection circuit to perform the turbo detection process.

Embodiments of the present disclosure may provide therefore receivers configured to recover the frame of data symbols using a turbo decoder and methods for decoding turbo encoded data. In one example the data symbols are bits.

# BACKGROUND OF THE DISCLOSURE

Over the past two decades, wireless communication has been revolutionized by channel codes that benefit from iterative decoding algorithms. For example, the Long Term Evolution (LTE) [1] and WiMAX [2] cellular telephony standards employ turbo codes [3], which comprise a concatenation of two convolutional codes. Conventionally, the Logarithmic Bahl-Cocke-Jelinek-Raviv (Log-BCJR) algorithm [4] is employed for the iterative decoding of the Markov chains that are imposed upon the encoded bits by these convolutional codes. Meanwhile, the WiFi standard for Wireless Local Area Networks (WLANs) [5] has adopted Low Density Parity Check (LDPC) codes [6], which may operate on the basis of the min-sum algorithm [7]. Owing to their strong error correction capability, these sophisticated channel codes have facilitated reliable communication at transmission throughputs that closely approach the capacity of the wireless channel. However, the achievable transmission throughput is limited by the processing throughput of the iterative decoding algorithm, if realtime operation is required. Furthermore, the iterative decoding algorithm's processing latency imposes a limit upon the end-to-end latency. This is particularly relevant, since multi-gigabit transmission throughputs and ultra-low end-to-end latencies can be expected to be targets for next-generation wireless communication standards [8]. Therefore, there is a demand for iterative decoding algorithms having improved processing throughputs and lower processing latencies. Owing to the inherent parallelism of the min-sum algorithm, it may be operated in a fully-parallel manner, facilitating LDPC decoders having processing throughputs of up to 16.2 Gbit/s [9]. By contrast, the processing throughput of state-of-the-art turbo decoders [10] is limited to 2.15 Gbit/s. This may be attributed to the inherently serial nature of the Log-BCJR algorithm, which is imposed by the data dependencies of its forward and backward recursions [4]. More specifically, the turbo-encoded bits generated by each of typically two convolutional encoders must be processed serially, spread over numerous consecutive time periods, which are clock cycles in a practical integrated circuit implementation. Furthermore, the Log-BCJR algorithm is typically applied to the two convolutional codes alternately, until a sufficient number of decoding iterations have been performed. As a result, thousands of time periods are required to complete the iterative decoding process of the state-of-the-art turbo decoder.

Accordingly, providing an alternative to the Log-BCJR decoder, which has fewer data dependencies and which enables fully parallel processing represents a technical problem.

# SUMMARY OF THE DISCLOSURE

5

10

15

20

25

30

According to a first example embodiment of the present technique there is provided a detection circuit for performing a turbo detection process to recover a frame of data symbols or bits from a received signal comprising fixed point data representing one or more soft decision values for each data symbol of the frame. The data symbols or bits of the frame have been affected, during transmission, by a Markov process with the effect that the data symbols of the frame in the received signal are dependent on one or more preceding data symbols which can be represented as a trellis having a plurality of trellis states. The detection circuit comprises a plurality of processing elements. Each of the processing elements is associated with one of the trellis stages representing the dependency of the data symbols of the frame according to the Markov process and each of the processing elements is configured to receive one or more soft decision values corresponding to one or more data symbols associated with the trellis stage. Each of one or more of the processing elements is configured, in one clock cycle, to receive fixed point data representing a priori forward state metrics from a first neighboring processing element, to receive fixed point data representing a priori backward state metrics from a second neighboring processing element, and to receive fixed point data representing a priori soft decision values for the one or more data symbols being detected for the trellis stage. The processing element combines the a priori forward state metrics, the a priori backward state metrics and the a priori soft decision values relating to the one or more data symbols to determine fixed point extrinsic forward state metrics, fixed point extrinsic backward metrics and extrinsic soft decision values corresponding to the one or more data symbols for the trellis stage associated with the processing element, and communicates the extrinsic forward state metrics to the second neighboring processing element, which becomes the *a priori* forward state metrics for a next clock cycle, communicates the extrinsic backward state metrics to the first neighboring processing element, which becomes the *a priori* backward state metrics for the next clock cycle, and provides the extrinsic soft decision values, which becomes the *a priori* soft decision values relating to the data symbol for the next clock cycle. In one example the extrinsic soft decision values are provided to a second detection circuit for processing as part of the turbo detection process. In other example the extrinsic soft decision values are provided for storing in memory so that the detection circuit can use these for a subsequent iteration of the turbo detection process. For one or more of a plurality of consecutive clock cycles of the turbo detection process, the processing elements of the detection circuit are configured to operate simultaneously.

Embodiments of the present technique can provide a receiver for detecting and recovering a frame of data symbols or bits from a received signal. The data symbols of the frame as present in the received signals have during the process of transmission been affected by a Markov process to the effect that data symbols of the frame in the received signal are dependent on one or more preceding data symbols which can be represented as a trellis having a plurality of trellis states.

As will be appreciated by those skilled in the art this description of the frame of data symbols as represented by the received signal could be manifested as transmitting the frame of data symbols through a channel which suffers from inter-symbol interference. Therefore a received symbol of the frame may be detected or represented within the received signal as a combination of a received symbols and one or more preceding symbols so that the channel introduces inter-symbol interference and therefore introduces some memory corresponding to a Markov process. In other embodiments the data symbols may be encoded with a turbo code with the effect that the data symbols in the received signal are represented by one or more different encoded data symbols which may be systematic data symbols representing the original data symbols as input to the turbo encoder or parity data symbols which are produced by the turbo encoder. Furthermore, in accordance with turbo encoding, the encoder may be provided with a plurality of convolutional encoders each of which may output a plurality data symbols for each input data symbol.

In some examples, for each of a plurality of clock cycles of the turbo detection process, the detection circuit may be configured to co-operate with at least one other detection circuit to process, for each of the processing elements representing the trellis stages, the *a priori* information for the one or more data symbols being detected for the trellis stage associated with the processing element, and to exchange the extrinsic soft decision values corresponding to the one or more data symbols generated by the processing element with the at least one other processing element. In some example the processing elements of each of the detection circuit and the at least one other detection circuit may operate in each clock cycle and after each clock cycle the first detection circuit and the at least one other detection circuit exchange the extrinsic soft decision values to the other.

5

10

15

20

25

30

According to the present technique a receiver comprises a demodulator for detecting and demodulating a received signal to recover an estimate of a frame of data symbols represented as soft decision values, a soft decision value representing the probability of each of the data symbols of the frame adopting each of its possible values. For the example of a turbo encoded frame of data symbols or bits the demodulator generates for each encoded data symbol or bit a soft decision value. The receiver further comprises a first detection processor configured to receive the soft decision values representing the frame of data symbols and a second detection processor which is configured to cooperate with the first detection processor to perform a turbo detection process to generate an estimate of the frame of data symbols. The first detection processor comprises a plurality of processing elements, each of the processing elements being associated with one of the trellis stages representing the dependency of the data symbols of the frame according to the Markov process. Each of the processing elements is configured to receive the soft decision value corresponding to one or more data symbols associated with the trellis stage and each of the plurality of processing elements is configured to receive data representing a priori forward state metrics from one neighbouring processing element, to receive data representing a priori backward state metrics from another neighbouring processing element and to receive data representing a priori information for the data symbols being detected for the trellis stage associated with the processing element from the second detection processor and from the demodulator. Each processing element is configured to combine the a priori forward state metrics, the a priori backward state metrics and the a priori information relating to the data symbols to produce extrinsic forward metrics, and extrinsic backward metrics and extrinsic data information and to communicate the extrinsic forward state metrics to the second neighbouring processing element which becomes the *a priori* forward state metrics for a next iteration, to communicate the extrinsic backward state metrics to the first neighbouring processing element which becomes the *a priori* backward state metrics for the next iteration and to communicate the extrinsic data information to the second detection processor for which becomes the *a priori* information for a next iteration of the turbo detection process. The first detection processor and the second detection processor are configured to exchange for each of the processing elements representing the trellis stages, the *a priori* information for the data symbol being detected for the trellis stage associated with the processing element and the corresponding extrinsic data information generated by the processing element for each of a plurality of iterations of the turbo detection process. In each clock cycle, processing elements from both decoders are being activated. This is in contrast to conventional decoders, where one decoder remains inactive whenever the other is activated.

5

10

15

20

25

30

Embodiments of the present technique can provide an improved turbo detection processor which modifies conventional algorithms such as the Log-BCJR also known as Log-MAP algorithm so that processing elements which are associated with each of the trellis stages describing a Markov process to which the data symbols have been subjected during the process of transmission, with the effect that each of the processing elements can operate autonomously and therefore in parallel thereby providing an improvement in the processing rate of the turbo detection processor and reducing a latency in recovering a data frame from a received signal. The improved turbo detector as mentioned above can be applied to decode a turbo encoded data frame or used as a turbo equaliser where a received data frame has suffered inter-symbol interference during transmission or other applications such as turbo synchronisation and Low Density Parity Check (LDPC) decoding. The present technique can therefore facilitate turbo decoders with similar processing throughputs and latencies as fully parallel LDPC decoders. Furthermore, this solution would bring similar benefits to the recovery of Markov chains of data in other applications that are typically decoded using the Log-BCJR algorithm, such as equalisation, synchronisation, channel estimation and source decoding.

In order to achieve the fully parallel processing architecture for the turbo detector the present technique removes the data dependencies which are associated with a conventional turbo detector such as the Log-BCJR or Log-MAP algorithm by not requiring that a previous stage in the turbo decoder completes before executing operations of the turbo decoder for a current iteration. That is to say, a conventional turbo decoder would require that all stages in the forward direction ripple through in a serial manner to calculate the forward state metrics

and correspondingly ripple through in the backward direction to generate the backward state metrics. Accordingly, the detection processor according to the present technique does not wait for the turbo detector to ripple forward the state metrics in the forward or backward directions but accepts a current value of the forward or backward state metrics at the output of the neighbouring processing elements and *a priori* information relating to the data symbol from another detection processor in the form that they currently are. This represents something of an approximation with respect to the Log-BCJR algorithm and accordingly the inventor has found that a greater number of iterations is required for the turbo detector according to the present technique to achieve the same decoding performance compared to the Log-BCJR algorithm. However, as will be explained in the following paragraphs, the inventor has discovered that an equivalent performance can be produced albeit with a greater number of iterations but with a faster detection process because the number of clock cycles in order to produce an equivalent performance of turbo detection/decoding is smaller than that produced by the conventional Log-BCJR algorithm.

5

10

15

20

25

30

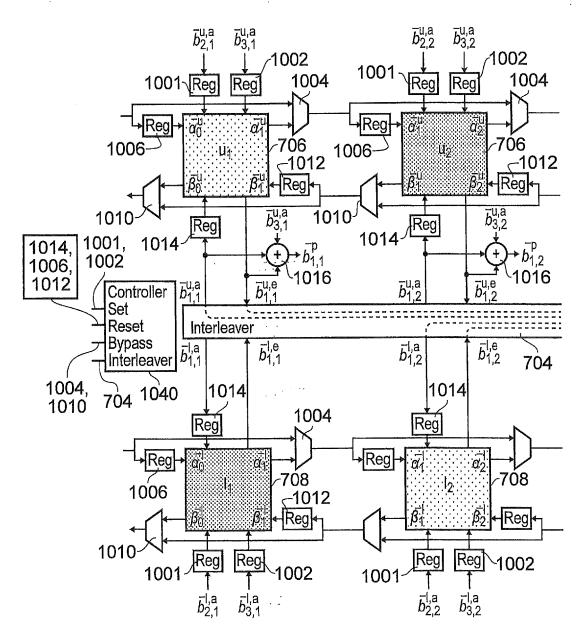

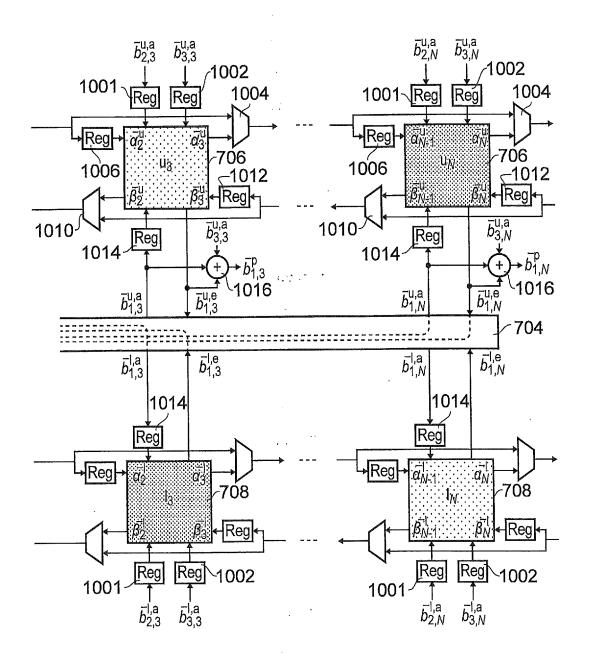

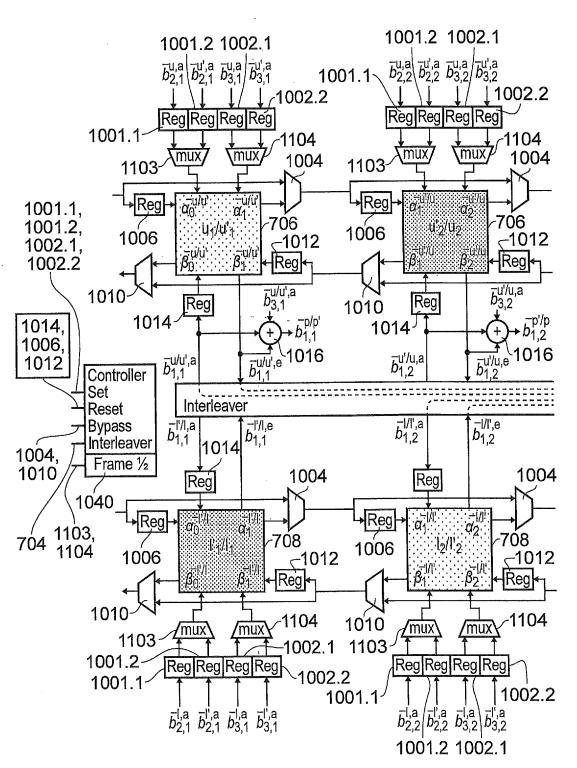

For the example in which the receiver in accordance with the present technique is arranged to detect data symbols of a frame which have been encoded with a turbo encoder then the receiver may further include an interleaver which is configured between the first and second detection processors to convey a priori information relating to the data symbol between the first detector and the second detection processor whereby the processing elements of the first detection processor receive and transmit extrinsic information relating to the data symbol and receive a priori information relating to the data symbol from different processing elements of the second detection processor in accordance with an interleaving pattern. Accordingly, for the example where interleaving has been applied to a second convolutional encoder forming the turbo encoding process in accordance with odd-even interleaving, then the data information relating to the data symbol is communicated between processing elements of the first and the second detection processors which are odd-indexed or even-indexed depending on the interleaving applied by the turbo encoder. Accordingly, where odd-even interleaving has been applied the odd-indexed processing elements in the first detection processor and the even-indexed processing elements in the second detection processor may be executed alternatively between each clock cycle with the even-indexed processing elements in the first detection processor and the odd-indexed processing elements in the second detection processor, thereby providing a 50% saving on processing.

According to the present technique the processing elements may include a by-pass circuit which allows for selected processing elements to be switched off to reflect a shorter

frame length and corresponding interleaver pattern. Accordingly, a corresponding saving in energy consumption can be achieved. The by-pass circuit may comprise a multiplexer, which is configured to select either an output from a current trellis stage or a previous trellis stage to by-pass the processing element. In some examples the interleaver is hardwired according to a predetermined interlever pattern and by-passes allow a sub-set of the interleaver pattern to be selected. In some examples the interleaver may be configurable to accommodate different interleaver patterns, which may be set in accordance with a particular turbo encoder. In another example the interleaver is re-configurable to route extrinsic information to different processing elements, which can therefore configure the turbo decoder in accordance with a particular turbo encoder. In one example the interleaver is implemented as a Beneš-network, which can be configured as desired.

The processing elements may also include one or more registers which are used to store the *a priori* forward state metrics or *a priori* backward state metrics or *a priori* information relating to the data symbol between time periods or clock cycles.

Various further aspects and features of the present disclosure are defined in the appended claims and include a communications device, a method of communicating using a communications device.

# BRIEF DESCRIPTION OF DRAWINGS

5

10

15

20

25

30

Embodiments of the present disclosure will now be described by way of example only with reference to the accompanying drawings wherein like parts are provided with corresponding reference numerals and in which:

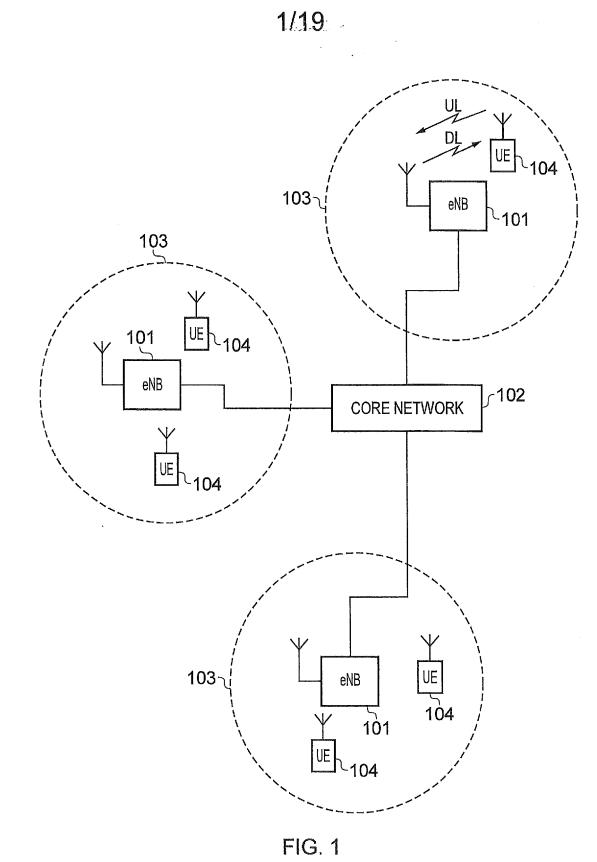

Figure 1 is a schematic diagram of a mobile communications system operating in accordance with the LTE standard;

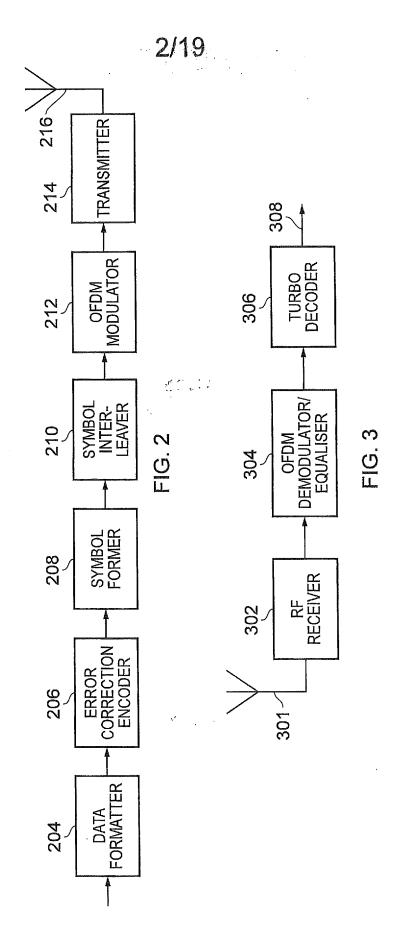

Figure 2 is a schematic block diagram of an example transmitter for the LTE system shown in Figure 1;

Figure 3 is a schematic block diagram of an example receiver for the LTE system shown in Figure 1;

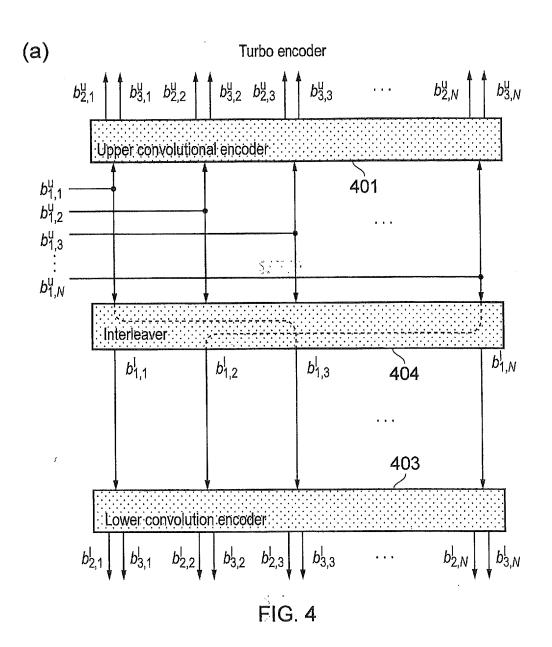

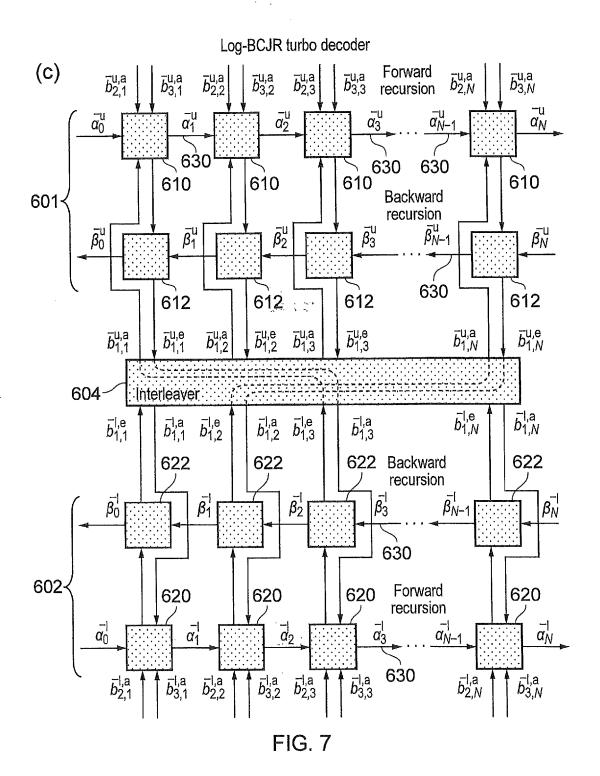

Figure 4 is a schematic block diagram of a simplified turbo encoder for an LTE standard or a WiMAX standard;

Figures 5 is a schematic block diagram showing a more detailed example of an LTE turbo encoder;

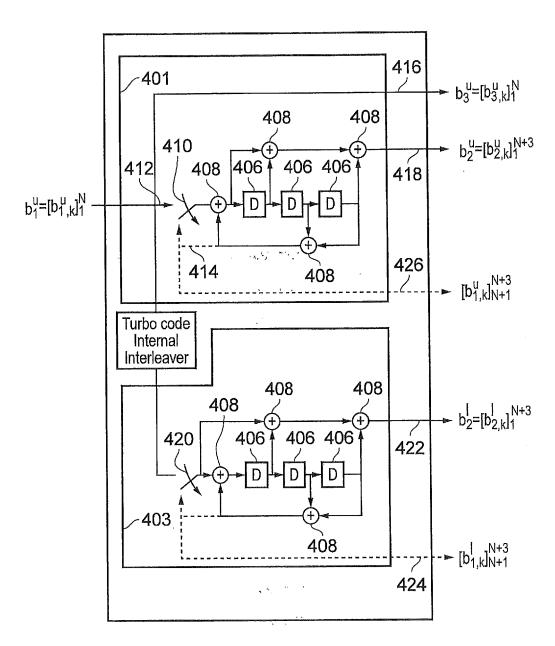

Figure 6 is an illustration of state and state transitions representing encoding using a convolutional encoder forming part of the turbo encoder of Figure 5;

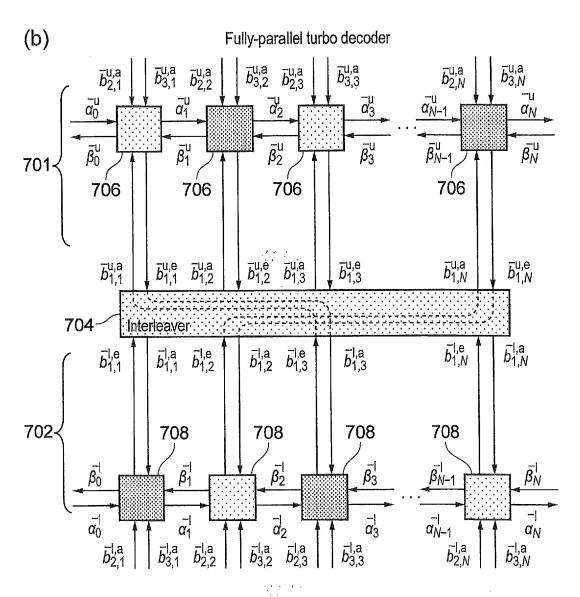

Figure 7 is a schematic block diagram of an example turbo decoder according to a Log-BCJR algorithm;

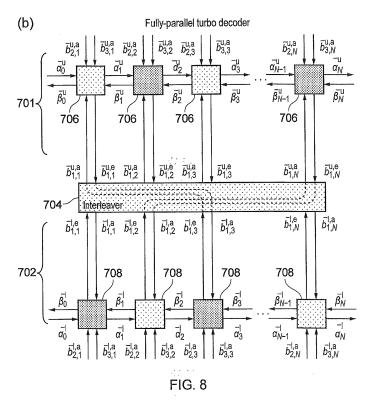

Figure 8 is a schematic block diagram of a fully-parallel turbo decoder according to an example embodiment of the present technique;

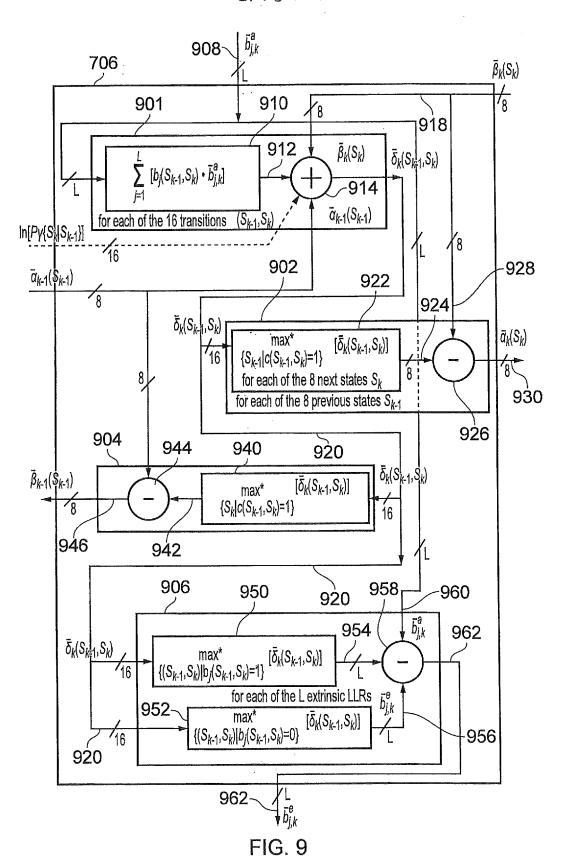

Figure 9 is a schematic block diagram showing a more detailed implementation of a processing element forming part of the fully-parallel turbo decoder of Figure 8;

5

10

15

20

25

30

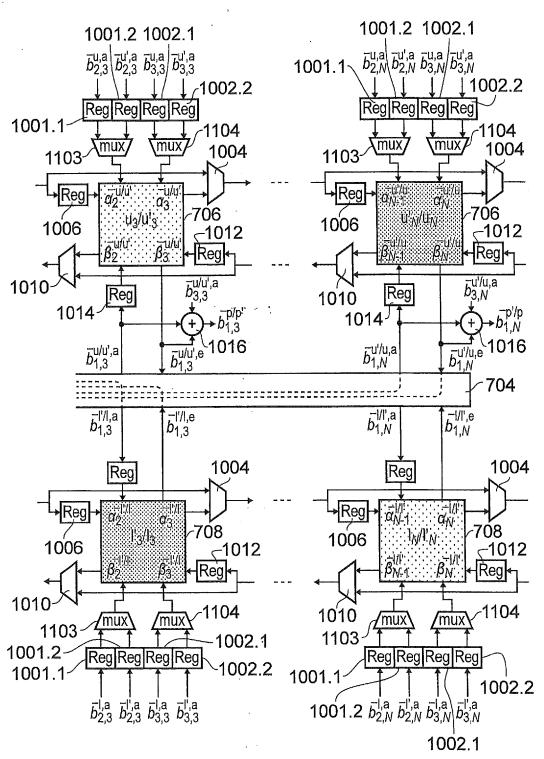

Figure 10 is a schematic functional block layout of a fully-parallel turbo decoder according to an example embodiment of the present technique;

Figure 11 is a schematic functional block layout of a fully-parallel turbo decoder according to a further example embodiment of the present technique;

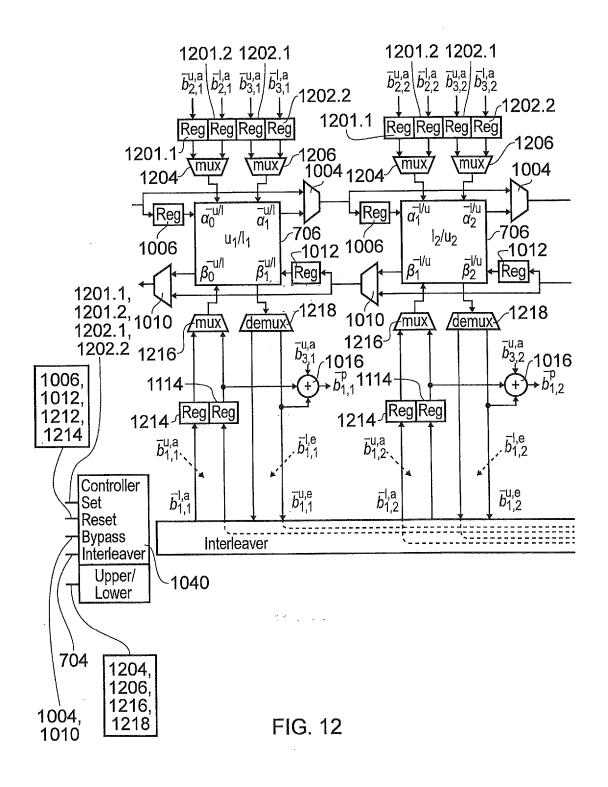

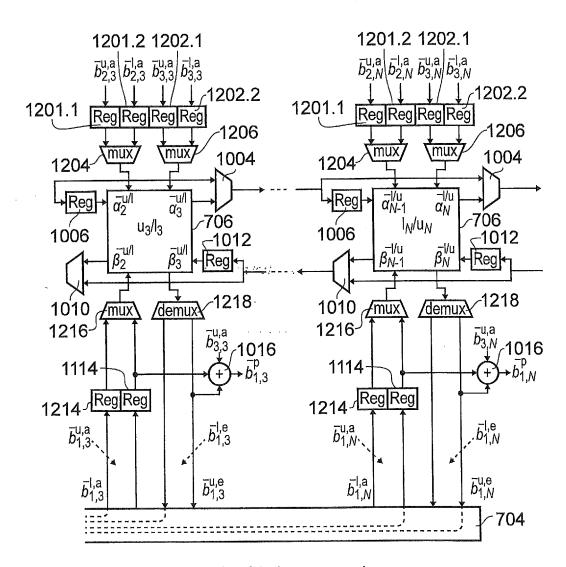

Figure 12 is a schematic functional block layout of a fully-parallel turbo decoder according to a further example embodiment of the present technique;

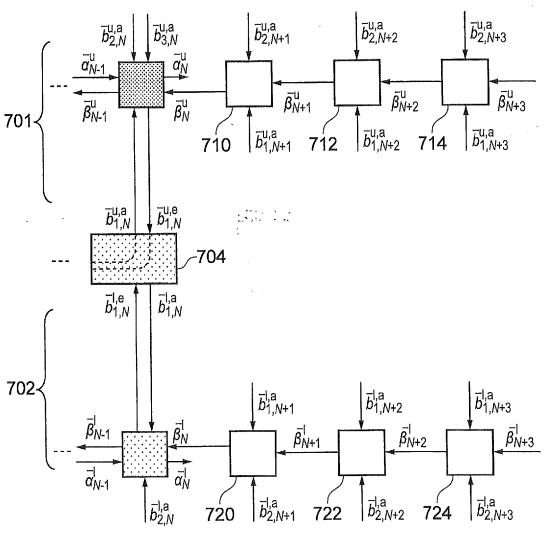

Figure 13 is a schematic block layout of processing elements forming part of the fully-parallel turbo decoder of Figure 8, which are responsible for terminating a frame of data being decoded;

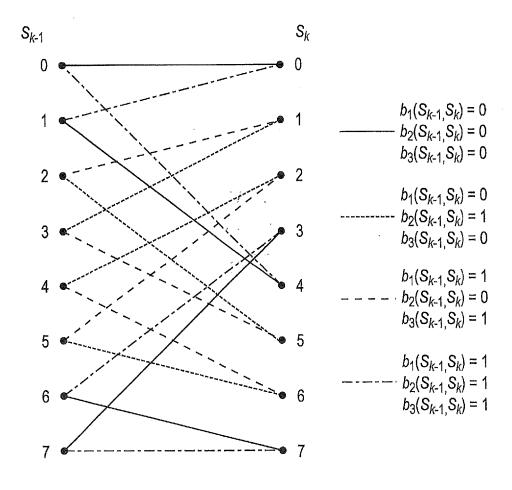

Figure 14 presents a table 1, showing a performance comparison between a Fully-Parallel Turbo Decoder according to an embodiment of the present technique with an equivalent Log-BCJR Turbo Decoder and a State-of-the-Art Turbo Decoder [10], in which the abbreviation TtotP is used to mean "times that of the proposed fully-parallel turbo decoder";

Figure 15 presents a table 2, showing an indication of numbers of calculations required for a Fully-parallel Turbo Decoder according to the present technique with an equivalent Log-BCJR Turbo Decoder, and in curly brackets number of calculations in the critical path length;

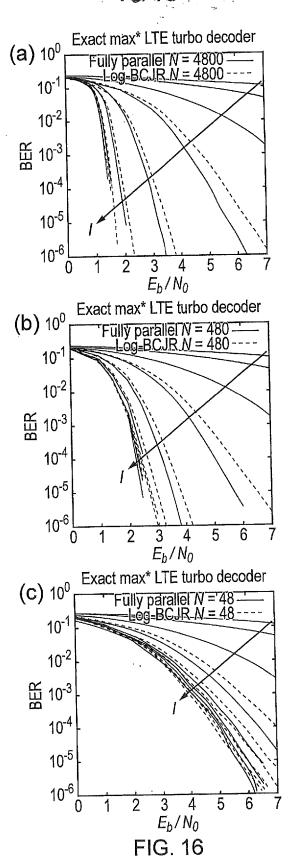

Figure 16a, 16b and 16c provide graphical plots of bit error rate with respect to signal to noise ratio representing the error correction performance of an LTE turbo decoder when decoding frames comprising (a) N=4800, (b) N=480 and (c) N=48 bits; and

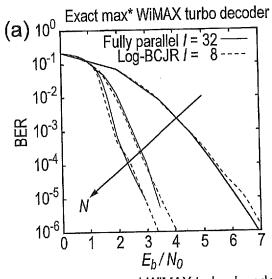

Figures 17a, 17b and 17c graphical plots of bit error rate with respect to signal to noise ratio representing the error correction performance of a WiMAX turbo decoder when using the exact max\* operator, Figure 17b the WiMAX turbo decoder when using the approximate max\* operator; and Figure 17c the LTE turbo decoder when using the approximate max\* operator.

#### DESCRIPTION OF EXAMPLE EMBODIMENTS

#### **Example Communications System**

5

10

15

20

25

30

Figure 1 provides a schematic diagram of a conventional mobile telecommunications system 100, where the system includes mobile communications devices 101, infrastructure equipment 102 and a core network 103. The infrastructure equipment may also be referred to as a base station, network element, enhanced Node B (eNodeB) or a coordinating entity for example, and provides a wireless access interface to the one or more communications devices within a coverage area or cell. The one or more mobile communications devices may communicate data via the transmission and reception of signals representing data using the wireless access interface. The network entity 102 is communicatively linked to the core network 103 where the core network may be connected to one or more other communications systems or networks which have a similar structure to that formed from communications devices 101 and infrastructure equipment 102. The core network may also provide functionality including authentication, mobility management, charging and so on for the communications devices served by the network entity. The mobile communications devices of Figure 1 may also be referred to as communications terminals, user equipment (UE), terminal devices and so forth, and are configured to communicate with one or more other communications devices served by the same or a different coverage area via the network entity. These communications may be performed by transmitting and receiving signals representing data using the wireless access interface over the two way communications links represented by lines 104 to 109, where 104, 106 and 108 represent downlink communications from the network entity to the communications devices and 105, 107 and 109 represent the uplink communications from the communications devices to the network entity. The communications system 100 may operate in accordance with any known protocol, for instance in some examples the system 100 may operate in accordance with the 3GPP Long Term Evolution (LTE) standard where the network entity and communications devices are commonly referred to as eNodeB and UEs, respectively.

As will be appreciated from the operation explained above at the physical layer the UEs and the eNodeBs are configured to transmit and receive signals representing data. As such a typical transmitter/receiver chain is shown in Figures 2 and 3.

Figure 2 provides a schematic block diagram illustrating components which make up a transmitter which may form part of the e-NodeB 101 or a communications device 104 of the physical layer transmission via the wireless access interface of the LTE system as illustrated in Figure 1. In Figure 2, data is received via an input 201 at a data formatter 204

and formed into frames or sub frames for transmission. Frames of data are then encoded with an error correction code by an error correction encoder 206 and fed to a symbol former 208 which forms the error correction encoded bits into groups of bits for mapping on to symbols for modulation. The data symbols are then interleaved by a symbol interleaver 210 and fed to an OFDM modulator 212 which modulates the subcarriers of an OFDM symbol with the data symbols which have been received from the interleaver 210. The OFDM symbols are then converted to an RF frequency and transmitted by a transmitter 214 via an antenna 216.

Correspondingly, a receiver operating to receive data transmitted via the physical layer for either the communications device 104 or an eNodeB 101 via an LTE wireless access interface includes a receiver antenna 301, which detects the radio frequency signal transmitted via the wireless access interface to a radio frequency receiver 302. Figure 3 represents a simplified version of a receiver and several blocks will make up an OFDM demodulator/equaliser 304 which converts the time domain OFDM symbol into the frequency domain and demodulates the subcarriers of the OFDM symbol to recover the data symbols and performs deinterleaving etc. However an output of the OFDM demodulator/equaliser 304 is to feed the encoded soft decision values representing the data bits to a turbo decoder 306. The turbo decoder performs a turbo decoding algorithm to detect and recover an estimate of the transmitted data bits which are output as a stream of data bits on an output 308 corresponding to the input 201.

It will be appreciated that Figures 2 and 3 have been drawn in order to illustrate an example embodiment of the present technique in which a fully parallel turbo decoder performs detection of the data bits encoded by the error correction encoder 206. However, it will be appreciated that the generalisation of the turbo detection process in accordance with the embodiments of the present invention can be provided to other parts of the receiver chain, notably for some systems which suffer from Inter-Symbol-Interference as a turbo equaliser and so the term detector is used generally to refer to both equalisation, demodulation and error correction decoding in which fully parallel turbo decoding algorithm in accordance with the present technique can be applied. As mentioned above, other applications of the fully parallel turbo algorithm include recovery of Markov chains of data in other applications that are typically decoded using the Log-BCJR algorithm, such as equalisation, synchronisation, channel estimation, LDPC decoding and source decoding.

For the example of LTE as mentioned above, an example embodiment of an error correction encoder 206 shown in Figure 2 is shown in Figure 4. Figure 4 provides an example representation illustrating a simplified turbo encoder, which encodes a message

frame  $\mathbf{b}_{1}^{\mathrm{u}} = \left[b_{1,k}^{\mathrm{u}}\right]_{k=1}^{N}$  comprising N number of bits, each having a binary value  $b_{1,k}^{\mathrm{u}} \in \{0, 1\}$ . This message frame is provided to an upper convolutional encoder 401, and a lower convolutional encoder 403, as shown in Figure 4. The upper convolutional encoder 401 performs a convolutional encoding process such as the examples provided below to generate two N-bit encoded frames, namely a parity frame  $\mathbf{b}_2^{\mathrm{u}} = \left[b_{2,k}^{\mathrm{u}}\right]_{k=1}^N$  and a systematic frame  $\mathbf{b}_3^{\mathrm{u}} = \left[b_{3,k}^{\mathrm{u}}\right]_{k=1}^N$ . Meanwhile, the message frame  $\mathbf{b}_1^{\mathrm{u}}$  is interleaved, by an internal turbo encoding interleaver 404, in order to obtain the N-bit interleaved message frame  $\mathbf{b}_1^1 =$  $\left[b_{1,k}^{1}\right]_{k=1}^{N}$  which, as shown in Figure 4 is provided to a lower convolutional encoder 403, which also applies a convolutional encoder to generate two more N-bit encoded frames, namely a parity frame  $\mathbf{b}_2^l = \left[b_{2,k}^l\right]_{k=1}^N$  and a systematic frame  $\mathbf{b}_3^l = \left[b_{3,k}^l\right]_{k=1}^N$ . Here, the superscripts 'u' and 'l' indicate relevance to the upper and lower convolutional encoders 401, 403, respectively. However, in the following, these superscripts are only used when necessary to explicitly distinguish between the two convolutional encoders 401, 403 of the turbo encoder and are omitted when the discussion applies equally to both. Note that the turbo encoder represents the N-bits of the message frame  $b_1^u$  using four encoded frames, comprising a total of 4N-bits and resulting in a turbo coding rate of R=N/(4N)=1/4.

As explained above with reference to Figure 2, following turbo encoding, the encoded frames may be modulated onto a wireless channel and transmitted to a receiver, such as the example provided in Figure 3.

#### 20 LTE turbo encoder

5

10

15

25

30

A more specific example of a turbo encoder is provided in Figure 5. Figure 5 provides an example of a turbo encoder, which corresponds to an example which has been proposed for the LTE standard [1]. For the example shown in Figure 5 the turbo encoder is a 1/3 rate code in which data bits received from a data formatter 204 as shown in Figure 2 are fed to an upper convolutional encoding processor 401. As can be seen in Figure 5 the received *N*-bits of the message frame  $\mathbf{b}_1^{\mathbf{u}} = \begin{bmatrix} b_{1,k}^{\mathbf{u}} \end{bmatrix}_{k=1}^{N}$  are also fed to a lower convolutional encoding processor 403 via a turbo code internal interleaver 404. In accordance with a known arrangement the *N*-bits of the message frame  $\mathbf{b}_1^{\mathbf{u}} = \begin{bmatrix} b_{1,k}^{\mathbf{u}} \end{bmatrix}_{k=1}^{N}$  are fed to memory elements 406 which are connected to other memory elements 406 to form a shift register type arrangement. An output of the memory elements 406 is used to form an input to XOR units 408, which form at their output a bit from a logical XOR of their inputs, which forms either

an encoded output bit or a bit which is fed back as an input to one of the memory elements 406. A switch in the upper convolutional encoder 410 switches the input bits between an input 412 and an output of the upper convolutional encoder 414 to form respectively, on a first output 416, a systematic frame  $\mathbf{b}_3^{\mathrm{u}} = \begin{bmatrix} b_{3,k}^{\mathrm{u}} \end{bmatrix}_{k=1}^{N}$ , and on a third output 426, three message termination bits  $\begin{bmatrix} b_{1,k}^{\mathrm{u}} \end{bmatrix}_{k=N+1}^{N+3}$ . A second output 418 of the upper convolutional encoder 401 provides a parity frame  $\mathbf{b}_2^{\mathrm{u}} = \begin{bmatrix} b_{2,k}^{\mathrm{u}} \end{bmatrix}_{k=1}^{N+3}$ . In Figure 5 the three message termination bits  $\begin{bmatrix} b_{1,k}^{\mathrm{u}} \end{bmatrix}_{k=N+1}^{N+3}$  are used to terminate the upper convolutional encoder 401 in a known state, which is not shown in Figure 4 for simplicity.

In the lower convolutional encoder 403 a switch 420 switches between the received bits from the internal interleaver 404 and corresponds to the switch 410 for the upper convolutional encoder. In a similar manner to the upper convolutional encoder, output channels 422, 424 of the lower convolutional encoder provide respectively a parity frame  $\mathbf{b}_2^1 = \begin{bmatrix} b_{2,k}^1 \end{bmatrix}_{k=1}^{N+3}$  and three message termination bits  $\begin{bmatrix} b_{1,k}^1 \end{bmatrix}_{k=N+1}^{N+3}$ . The systematic data bits of the lower convolutional encoder  $\mathbf{b}_3^1 = \begin{bmatrix} b_{3,k}^1 \end{bmatrix}_{k=1}^{N}$  are not output from the lower convolutional encoder because these are already present on the first output 416. Accordingly, with the first output 416 providing the input bits as a systematic code the second and fourth outputs 418, 422 providing respective parity bits, the turbo encoder provides a 1/3 rate code. As with the upper convolutional encoder, three message termination bits  $\begin{bmatrix} b_{1,k}^1 \end{bmatrix}_{k=N+1}^{N+3}$  are used to terminate the lower convolutional encoder 403 in a known state, which is not shown in Figure 4 for simplicity.

In summary, the LTE turbo encoder [1] of Figure 5 employs twelve additional termination bits to force each convolutional encoder into the final state  $S_{N+3} = 0$ . More specifically, the upper convolutional encoder 401 generates the three message termination bits  $b_{1,N+1}^u$ ,  $b_{1,N+2}^u$ ,  $b_{1,N+3}^u$  as well as the three parity termination bits frame  $b_{2,N+1}^u$ ,  $b_{2,N+2}^u$ ,  $b_{2,N+3}^u$ . The lower convolutional encoder 403 operates in a similar manner, generating corresponding sets of three message termination bits  $b_{1,N+1}^l$ ,  $b_{1,N+2}^l$ ,  $b_{1,N+3}^l$  as well as the three parity termination bits  $b_{2,N+1}^l$ ,  $b_{2,N+2}^l$ ,  $b_{2,N+3}^l$ . In contrast to the systematic frame  $\mathbf{b}_3^u$  that is produced by the upper convolutional encoder, that of the lower convolutional encoder  $\mathbf{b}_3^l$  is not output by the LTE turbo encoder. Owing to this, the LTE turbo encoder uses a total of (3N+12) bits to represent the N bits of the message frame  $\mathbf{b}_1^u$ , giving a coding rate of R = N / (3N+12).

The example of the turbo encoder presented in Figure 5 provides upper and lower convolutional encoders 401, 403, which each have three memory elements 406. As will be known by those acquainted with convolutional encoders, the binary content of the memory elements 406 can be interpreted as a state, so that the convolutional encoding process can be synthesised as transitions through a trellis comprising the possible states of the convolutional encoder. As such, a convolutional encoder or a turbo encoder can be described as a Markov process and therefore represented as a trellis diagram. An example of state transition diagram for a convolutional encoder is shown in Figure 6. The state transition diagram of Figure 6 represents one stage of a trellis having M=8 states and K=2transitions per state, and can therefore provide an example corresponding to the upper and lower convolutional encoders 401, 403, which operate in the same manner. For the upper convolutional encoder 401 begins from an initial state of  $S_0 = 0$  and successively transitions into each subsequent state  $S_k \in \{0, 1, 2, \dots, M-1\}$  by considering the corresponding message bit  $b_{1,k}$ . Since there are two possible values for the message bit  $b_{1,k} \in \{0,1\}$  there are K=2 possible values for the state  $S_k$  that can be reached by transitioning from the previous state  $S_k-1$ . In Figure 6 for example, a previous state of  $S_k-1=0$  implies that the subsequent state is selected from  $S_k \in \{0,4\}$ . This example can also be expressed using the notation c(0, 0) = 1 and c(0, 4) = 1, where  $c(S_{k-1}, S_k) = 1$  indicates that it is possible for the convolutional encoder to transition from  $S_{k-1}$  into  $S_k$ , whereas  $c(S_{k-1}, S_k) = 0$  indicates that this transition is impossible. Of the K=2 options, the value for the state  $S_k$  is selected such that  $b_1(S_{k-1}, S_k) = b_{1,k}$ . For example,  $S_{k-1} = 0$  and  $b_{1,k} = 0$  gives  $S_k = 0$ , while  $S_{k-1} = 0$ and  $b_{1,k} = 1$  gives  $S_k = 4$  in Figure 6. In turn, binary values are selected for the corresponding bit in the parity frame  $\mathbf{b}_2$  and the systematic frame  $\mathbf{b}_3$ , according to  $b_{2,k}=b_2$  $(S_{k-1}, S_k)$  and  $b_{3,k} = b_3(S_{k-1}, S_k)$ . In the example of Figure 6,  $S_{k-1} = 0$  and  $S_k = 0$  gives  $b_{2,k} = 0$  and  $b_{3,k} = 0$ , while  $S_{k-1} = 0$  and  $S_k = 4$  gives  $b_{2,k} = 1$  and  $b_{3,k} = 1$ .

Turbo Encoder Internal Bit Interleaver

5

10

15

20

25

30

As explained above, turbo encoders typically include an internal bit interleaver 404, which interleaves the data bits from the order in which they are encoded between the upper and the lower convolutional encoders 401, 403. For example, the LTE turbo encoder shown in Figure 5, employs an odd-even interleaver [14] that supports various frame lengths N in the range 40 to 6144 bits.

Example WiMAX Turbo Encoder

Like the example of an LTE turbo encoder, a turbo encoder which operates in accordance with the WiMAX standard [2] employs an odd-even interleaver, supporting various frame lengths N in the range 24 to 2400 bits. However, in contrast to the LTE turbo encoder, the WiMAX turbo encoder is duobinary [2]. More specifically, the upper WiMAX convolutional encoder encodes two N-bit message frames at once  $\mathbf{b}_1^{\mathrm{u}}$  and  $\mathbf{b}_2^{\mathrm{u}}$ . In response, a turbo encoder which operates in accordance with the WiMAX standards produces four N-bit encoded frames, namely two parity frames  $\boldsymbol{b}_3^u$  and  $\boldsymbol{b}_4^u$ , as well as two systematic frames  $\boldsymbol{b}_5^u$ and  $\mathbf{b}_{6}^{\mathrm{u}}$ . Meanwhile, the message frames  $\mathbf{b}_{1}^{\mathrm{u}}$  and  $\mathbf{b}_{2}^{\mathrm{u}}$  are interleaved, in order to obtain two Nbit interleaved message frames  $\mathbf{b}_1^l$  and  $\mathbf{b}_2^l$ . These two N-bit interleaved message frames  $\mathbf{b}_1^l$ and  $\boldsymbol{b}_2^l$  are encoded by a lower convolutional encoder 403, in order to generate two parity frames  $\mathbf{b}_3^1$  and  $\mathbf{b}_4^1$ . As for the example of the LTE turbo encoder however, the lower encoder's N-bit systematic frames  $\mathbf{b}_5^l$  and  $\mathbf{b}_6^l$  are not output by a WiMAX turbo encoder. Therefore, a WiMAX turbo encoder represents the 2N bits of the message frames  $\mathbf{b}_1^{\mathrm{u}}$  and  $\mathbf{b}_2^{\mathrm{u}}$ using six encoded frames, comprising a total of 6N bits and resulting in a coding rate of R =(2N)/(6N) = 1/3. In a WiMAX turbo encoder, the upper and lower convolutional encoders 401, 403 operate on the basis of a state transition diagram having K = 4 transitions from each of M = 8 states, in correspondence to the four possible combinations of the two message bits. Rather than employing termination bits, WiMAX employs tail-biting to ensure that  $S_N = S_0$ , which may require  $S_N$  and  $S_0$  to have non-zero values.

#### 20 Turbo Decoder Using Log BCJR-Algorithm

5

10

15

25

30

The section above has described a turbo encoder as shown in Figure 2 with reference to Figures 4, 5 and 6. Embodiments of the present technique can provide a fully-parallel turbo decoder, which has an improved rate of decoding, a smaller memory requirements and a reduced number of arithmetic calculations to implement in comparison to conventional algorithms. In order better appreciate the improvement provided by the present technique with respect to conventional turbo decoders or detectors, a conventional turbo decoder which operates in accordance with the conventional log BCJR algorithm will first be described, which is configured to decode a turbo encoded frame of data bits which has been turbo encoded in accordance with an example of turbo encoder as explained above with reference to Figures 4, 5 and 6 according to the LTE standard.

Following their transmission over a wireless channel, the four encoded frames  $\mathbf{b}_2^{\mathrm{u}}$ ,  $\mathbf{b}_3^{\mathrm{u}}$ ,  $\mathbf{b}_2^{\mathrm{l}}$  and  $\mathbf{b}_3^{\mathrm{l}}$ , generated by the turbo encoder as illustrated in Figure 4, may be demodulated and provided to the turbo decoder of Figure 7. However, owing to the effect of noise in the

wireless channel, the demodulator will be uncertain of the bit values in these encoded frames. Therefore, instead of providing frames comprising N hard-valued bits, the demodulator provides four frames each comprising N soft-valued a priori Logarithmic Likelihood Ratios (LLRs)  $\bar{\mathbf{b}}_{2}^{\mathrm{u,a}} = [\bar{b}_{2,k}^{\mathrm{u,a}}]_{k=1}^{N}$ ,  $\bar{\mathbf{b}}_{3}^{\mathrm{u,a}} = [\bar{b}_{3,k}^{\mathrm{u,a}}]_{k=1}^{N}$ ,  $\bar{\mathbf{b}}_{2}^{\mathrm{l,a}} = [\bar{b}_{2,k}^{\mathrm{l,a}}]_{k=1}^{N}$ , and  $\bar{\mathbf{b}}_{3}^{\mathrm{l,a}} = [\bar{b}_{3,k}^{\mathrm{l,a}}]_{k=1}^{N}$ . Here, an

5 LLR pertaining to bit  $b_{j,k}$  is defined by

$$\bar{b}_{j,k} = \ln \frac{\Pr(b_{j,k}=1)}{\Pr(b_{j,k}=0)},\tag{1}$$

where the superscripts 'a', 'e' or 'p' may be appended to indicate an *a priori*, extrinsic or *a posteriori* LLR, respectively.

The Log-BCJR algorithm generally forms a decoding or detection process which performs a forward recursion process and a backward recursion process through a trellis representing the connection of each of the states of a Markov process, such as a convolutional encoder. For the turbo encoded data, a decoder which performs a Log-BCJR decoding process comprises a upper decoder and a lower decoder. Each of the upper and lower decoders each perform a forward recursion process and a backward recursion process and generate for each iteration extrinsic LLRs which are fed to other of the upper and lower decoders.

Figure 7 provides a schematic block diagram illustrating an example implementation of a simplified turbo decoder for the Log-BCJR algorithm, which corresponds to the simplified turbo encoder of Figure 4. The Log-BCJR turbo decoder is operated iteratively, where each of the I iterations comprises the operation of all processing elements or algorithmic blocks shown. During the forward and backward recursions of the Log-BCJR algorithm, the  $k^{\rm th}$  pair of algorithmic blocks in the upper and lower rows perform calculations relating to one stage of the trellis according to Equations (2) – (6) [4]:

25

20

10

15

$$\bar{\gamma}_k(S_{k-1}, S_k) = \left[ \sum_{j=1}^L \left[ b_j(S_{k-1}, S_k) \cdot \bar{b}_{j,k}^a \right] \right] + \ln[Pr\{S_k | S_{k-1}\}]$$

(2)

$$\bar{\alpha}_k(S_k) = \max^* \{S_{k-1} | c(S_{k-1}, S_k) = 1\} [\bar{\gamma}_k(S_{k-1}, S_k) + \bar{\alpha}_{k-1}(S_{k-1})]$$

(3)

$$\bar{\beta}_{k-1}(S_{k-1}) = \max^* \{ S_k | c(S_{k-1}, S_k) = 1 \} \left[ \bar{\gamma}_k(S_{k-1}, S_k) + \bar{\beta}_k(S_k) \right]$$

(4)

$$\bar{\delta}_k(S_{k-1}, S_k) = \bar{\gamma}_k(S_{k-1}, S_k) + \bar{\alpha}_{k-1}(S_{k-1}) + \bar{\beta}_k(S_k)$$

(5)

$\overline{b}_{j,k}^{\mathrm{e}}$

$$\left[\max^*_{\{(S_{k-1},S_k)|b_j(S_{k-1},S_k)=1\}} \left[\bar{\delta}_k(S_{k-1},S_k)\right]\right] - \left[\max^*_{\{(S_{k-1},S_k)|b_j(S_{k-1},S_k)=0\}} \left[\bar{\delta}_k(S_{k-1},S_k)\right]\right] - \bar{b}_{j,k}^{a}$$

(6)

The term  $\ln[Pr\{S_k|S_{k-1}\}]$  in equation (2) has been included to increase the generality of the Log-BCJR algorithm, so as to illustrate that the present technique can be applied to applications beyond channel decoding. This term facilitates the exploitation any additional a priori knowledge that the receiver has for the probability  $Pr\{S_k|S_{k-1}\}$  of entering the state  $S_k$  given that the previous state  $S_{k-1}$  has been entered. This could source from knowledge of the channel characteristics and from information received over the channel, for coded demodulation or turbo equalization. When used for source decoding, this could source from knowledge of the source probability distribution. Similarly, this additional term provides for numerous other applications, including turbo synchronization and turbo channel estimation. In applications such as turbo decoding where no additional a priori knowledge is available, then this term can be omitted or set to a constant value and so in the following discussion can be ignored.

As shown in Figure 7, a first set of 2N processing elements or algorithmic blocks 601 are devoted to performing a first part of the turbo decoding algorithm on the turbo encoded data produced by an upper convolutional encoder 401. A first row of N processing elements 610 of the upper decoder 601 are devoted to performing a forward recursion process through a trellis of possible states, whereas a second row of N processing elements 612 are devoted to performing backward recursion through the trellis stages according to the Log-BCJR algorithm. Each processing element corresponds to one of the N stages in the trellis, which comprises a set of transitions between a set of previous states and a set of next states. A second set of 2N processing elements or algorithmic blocks 602 are devoted to performing a second part of the turbo decoding algorithm on the turbo encoded data produced by the lower convolutional encoder 403. As for the upper decoder 601, the lower decoder includes a first row of N processing elements 620 of the lower decoder 602, which are devoted to performing a forward recursion process through a trellis of possible states, whereas a second row of N processing elements 622 are devoted to performing backward recursion through the trellis states according to the Log-BCJR algorithm.

The  $k^{th}$  processing element 610, of the N processing elements 610 of the upper decoder 601 which are devoted to performing the forward recursion part of the Log-BCJR algorithm 610, is arranged to receive the  $k^{th}$  LLR values  $\bar{b}_{2,k}^{u,a}$ ,  $\bar{b}_{3,k}^{u,a}$ , from the demodulator which were estimated for the frames of encoded bits  $\mathbf{b}_{2}^{u}$ ,  $\mathbf{b}_{3}^{u}$ , generated by the upper encoder 401. Correspondingly, the  $k^{th}$  processing element 620 of the N processing elements 620 of the lower decoder 602, which are devoted to performing the forward recursion part of the

Log-BCJR algorithm, is arranged to receive the  $k^{\text{th}}$  LLR values  $\overline{b}_{2,k}^{1,a}$ ,  $\overline{b}_{3,k}^{1,a}$ , from the demodulator which were estimated for the frames of encoded bits  $\mathbf{b}_2^1$ ,  $\mathbf{b}_3^1$ , generated by the lower encoder 402.

The  $k^{th}$  processing element 610, 620, which each in turn are arranged to perform the forward recursion, in the upper detection processor 601 and the lower detection processor 602, one after the other serially employs equation (2) (without the term  $\ln[Pr\{S_k|S_{k-1}\}]$  for the present example) to combine the L=3 a priori LLRs  $\bar{b}_{1,k}^a$ ,  $\bar{b}_{2,k}^a$ , and  $\bar{b}_{3,k}^a$ , in order to obtain an a priori metric  $\bar{\gamma}_k(S_{k-1},S_k)$  for each transition in the state transition diagram (as illustrated for example in Figure 6). Following this calculation, each of the  $k^{th}$  processing elements 610, 620 performing the forward recursion, combines these a priori transition metrics with the a priori forward state metrics of  $\bar{\alpha}_{k-1}(S_{k-1})$  according to equation (3), in order to obtain the extrinsic forward state metrics of  $\bar{\alpha}_k(S_k)$ . These extrinsic state metrics are then passed to the  $k+1^{th}$  processing element 610, 620, to be employed as a priori state metrics in the next time period. However as will be appreciated by those familiar with the Log-BCJR algorithm the upper and lower decoders of the turbo decoder work alternately, so that when one is active the other is idle.

The  $k^{th}$  processing element 612, 622, which are performing the backward recursion, in the upper turbo decoder 601 and the lower turbo decoder 602 employs equation (4) to combine the *a priori* metric  $\bar{\gamma}_k(S_{k-1}, S_k)$  for each transition with the *a priori* backward state metrics  $\bar{\beta}_k(S_k)$ . This produces an extrinsic backward state metric  $\bar{\beta}_{k-1}(S_{k-1})$ , which may be passed to the k-1<sup>th</sup> processing element, to be employed as *a priori* state metrics in the next time period. Furthermore, the k<sup>th</sup> processing element 612, 622, which are performing the backward recursion, in the upper turbo decoder 601 and the lower turbo decoder 602 employs equation (5) to obtain an *a posteriori* metric  $\bar{\delta}_k(S_{k-1}, S_k)$  for each transition in the state transition diagram (as for example illustrated in Figure 5). Finally, the k<sup>th</sup> processing element 612, 622, which are performing the backward recursion, in the upper turbo decoder 401 and the lower turbo decoder employs equation (6) to generate an extrinsic message LLR  $\bar{b}_{j,k}^e$  for the k<sup>th</sup> bit. These LLR values are swapped between the upper and lower decoders 601, 602.

The upper decoder 601 and the lower decoder 602 exchange extrinsic LLRs for each of the data bits of the frame, which become an estimate of the systematic bits of the encoded data frame. More specifically, an interleaver 604 performs deinterleaving of the LLR values of data bits passed between an upper decoder 601 and the lower decoder 602, to reverse the

interleaving of the data bits which are used by the upper convolutional encoder 401 and the lower convolutional encoder 402 of a turbo encoder.

The interleaver 604 exchanges extrinsic information with the other decoder 601, 602, which uses it as *a priori* information. More specifically, as shown in Figure 7 the  $k^{th}$  algorithmic block 612 which is performing the backward recursion in the upper decoder 601 provides as an output an extrinsic estimate of the LLR value for the message data bit  $\bar{b}_{1,k}^{u,e}$  to the interleaver 604, which after interleaving forms the *a priori* LLR value  $\bar{b}_{1,k}^{l,a}$  as input to the  $k^{th}$  processing element 620, which is performing the forward recursion in the lower decoder 602.

For a first decoding iteration of the Log-BCJR turbo decoder, zero-values are employed for the *a priori* message LLRs. The simplified example decoder of Figure 7 can be applied to the example turbo encoders for the LTE standard and the WiMAX standard, using the Log-BCJR algorithm of (2) – (6) decoder having L=3 and L=2 a priori LLRs for the LTE encoder, as well as the blocks of the WiMAX turbo code having L=6 and L=4. Depending on whether termination or tailbiting is employed, values for  $\overline{\alpha}_0$  and  $\overline{\beta}_N$  can be selected for the Log-BCJR turbo decoder.

# **Disadvantages of Conventional Turbo Decoders**

5

10

15

20

25

30

As will be appreciated in the explanation of the turbo decoder according to a conventional arrangement of the Log-BCJR decoding process above, each of the respective detection processors must wait until the forward recursion has been completed and the backward recursion has been completed before outputting the extrinsic LLR information to corresponding processing elements in the other of the upper and lower detection processor, via the interleaver 604. Furthermore, a Log-BCJR turbo decoder is operated iteratively, where each of the I iterations comprises the operation of all processing elements or algorithmic blocks shown in Figure 7. As such, T = 4N consecutive time periods are required to complete each decoding iteration, so that the 4N algorithmic blocks are operated sequentially, in the order indicated by the bold arrows 630 of Figure 7. These arrows 630 indicate the data dependencies of the Log-BCJR algorithm, which impose the forward and backward recursions shown in Figure 7. Therefore, as explained below, when implementing the LTE or WiMAX turbo decoders, the number of time periods required by the Log-BCJR algorithm is 2N Times that of the Proposed (TtotP) fully-parallel turbo decoder embodying the present technique, which requires T = 1 or T = 2 time periods as discussed below.

#### Fully Parallel Turbo Decoder

In contrast to the Log-BCJR algorithm, a detector which operates in accordance with an embodiment of the present technique is configured to remove as far as possible data dependencies, thereby facilitating fully-parallel turbo decoding. More specifically, the proposed fully-parallel algorithm can process all turbo-encoded bits in both components of the turbo code at the same time. This process is repeated iteratively, until a sufficient number of decoding iterations have been performed. Owing to this, the iterative decoding process can be completed using just tens of time periods, which is significantly lower than the number required by the state-of-the-art turbo decoder of [10]. Note that a number of fully-parallel turbo decoders have been previously proposed, although these suffer from significant disadvantages that are not manifested in detectors/decoders embodying the present technique. In [11], the min-sum algorithm is employed to perform turbo decoding. However, this approach only works for a very limited set of turbo code designs, which does not include those employed by any standards, such as LTE and WiMAX. A fully-parallel turbo decoder implementation that represents the soft information using analogue currents was proposed in [12], however it only supports very short message lengths N. Similarly, [13] proposes a fullyparallel turbo decoder algorithm that operates on the basis of stochastic bit sequences. However, this algorithm requires significantly more time periods than the Log-BCJR algorithm, therefore having a significantly lower processing throughput.

5

10

15

20

25

30

Other proposals have been made to improve a rate of performing turbo detection. For example, CN 102611464 [17], CN 102723958 [18], WO 2011/082509 [19] and a published article entitled "A 122Mb/s Turbo decoder using a mid-range GPU" by Xianjun J., et al [20] there are disclosed turbo decoders with improved processing performance and reduced complexity. The article entitled "A 122Mb/s Turbo decoder using a mid-range GPU" by Xianjun J., et al [20] discloses using a plurality of processing elements referred to as sub-decoder, each processing element being assigned to one bit of a code block. As such there is an improvement in the parallel processing which is possible. However in contract with embodiments of the present technique the decoder referred to in the above mentioned article does not operate the decoders at the same time.

Embodiments of the present technique can provide a fully parallel arrangement of processing to perform a turbo decoding process which is based on the Log-BCJR turbo decoding algorithm but simplified in order to allow all of the processing elements to operate in parallel. Figure 8 provides an example but simplified arrangement of a fully parallel decoding technique. In Figure 8, the respective upper and lower turbo decoding parts 701, 702 correspond to the upper and lower turbo decoding parts of the Log-BCJR algorithm 601,

602, but are replaced with N parallel processing elements or algorithmic blocks 706, 708. Thus the upper decoder 701 is comprised of N processing elements 706 whereas the lower decoder 702 is comprised of N processing elements 708.

5

10

15

20

30

As shown in Figure 8 and in correspondence with the operation of the Log-BCJR algorithm, the demodulator in the receiver of Figure 3, provides the a priori LLRs to the turbo decoder's 2N processing elements 708, 706 (algorithmic blocks), which as shown in Figure 8 are arranged in two rows. More specifically, following their transmission over a wireless channel, the four encoded frames  $b_2^u$ ,  $b_3^u$ ,  $b_2^l$  and  $b_3^l$  are demodulated and provided to the turbo decoder of Figure 8. The demodulator provides four frames each comprising N soft-valued a priori Logarithmic Likelihood Ratios (LLRs)  $\bar{\mathbf{b}}_{2}^{\mathrm{u,a}} = \left[\bar{b}_{2,k}^{\mathrm{u,a}}\right]_{k=1}^{N}$ ,  $\bar{\mathbf{b}}_{3}^{\mathrm{u,a}} = \left[\bar{b}_{2,k}^{\mathrm{u,a}}\right]_{k=1}^{N}$  $\left[\bar{b}_{3,k}^{\mathrm{u,a}}\right]_{\nu=1}^{N},\ \bar{\mathbf{b}}_{2}^{\mathrm{l,a}}=\left[\bar{b}_{2,k}^{\mathrm{l,a}}\right]_{\nu=1}^{N}\ ,\ \mathrm{and}\ \bar{\mathbf{b}}_{3}^{\mathrm{l,a}}=\left[\bar{b}_{3,k}^{\mathrm{l,a}}\right]_{k=1}^{N}\ \, \mathrm{to}\ \, \mathrm{the}\ \, \mathrm{fully-parallel}\ \, \mathrm{turbo}\ \, \mathrm{decoder's}\ \, 2N$ processing elements or algorithmic blocks, with the *a priori* parity LLR  $\bar{b}_{2,k}^{\text{u,a}}$  and the *a priori* systematic LLR  $\bar{b}_{3,k}^{\text{u,a}}$  being provided to the  $k^{\text{th}}$  algorithmic block 706 in the upper decoder 701 shown in Figure 8. Furthermore, the interleaver 704 provides the  $k^{th}$  algorithmic block in the upper decoder 701 with the *a priori* message LLR  $\bar{b}_{1,k}^{u,a}$ , as will be detailed below. Meanwhile, the  $k^{th}$  algorithmic block in the lower decoder 702 is correspondingly provided with the a priori LLR values  $\bar{b}_{1,k}^{l,a}$ ,  $\bar{b}_{2,k}^{l,a}$  and  $\bar{b}_{3,k}^{l,a}$ . In addition to this, the  $k^{th}$  algorithmic block 706, 708 in each of the upper and lower decoders 701, 702 is also provided with a vector of a priori forward state metrics  $\overline{\alpha}_{k-1} = [\overline{\alpha}_{k-1}(S_{k-1})]_{S_{k-1}=0}^{M-1}$  and a vector of *a priori* backward state metrics  $\overline{\beta}_k = \left[\overline{\beta}_k(S_k)\right]_{S_k=0}^{M-1}$ , as will be detailed below. Unlike a conventional turbo decoder operating in accordance with the BCJR algorithm described above with reference to Figure 7, each of the processing elements 706, 708 of the upper and lower decoders 701, 702 operates in an identical manner to receive the soft decision a priori LLR values of  $\bar{\mathbf{b}}_{2}^{\mathrm{u,a}} = \left[\bar{b}_{2,k}^{\mathrm{u,a}}\right]_{k=1}^{N}$ ,  $\bar{\mathbf{b}}_{3}^{\text{u,a}} = \left[\bar{b}_{3,k}^{\text{u,a}}\right]_{k=1}^{N} \text{ for a processing element 706 of the upper decoder 701, or } \bar{\mathbf{b}}_{2}^{\text{l,a}} = \left[\bar{b}_{2,k}^{\text{l,a}}\right]_{k=1}^{N}, \text{ and } \bar{\mathbf{b}}_{3}^{\text{u,a}} = \left[\bar{b}_{2,k}^{\text{l,a}}\right]_{k=1}^{N}, \bar{\mathbf{b}}_{3}^{\text{u,a}} = \left[\bar{b}_{2,k}^{\text{u,a}}\right]_{k=1}^{N}, \bar$  $\bar{\mathbf{b}}_{3}^{l,a} = \left[\bar{b}_{3,k}^{l,a}\right]_{k=1}^{N}$  for a processing element 708 in the lower decoder 702, corresponding to one or more data symbols associated with the trellis stage and to receive a priori forward state metrics  $\bar{a}_{k-1}$  from one neighbouring processing element, to receive a priori backward statement metrics  $\overline{\beta}_k$  from a second neighbouring processing element and to receive a priori LLR value  $\bar{b}_{1,k}^{\rm a}$  for the data symbol being detected for the trellis stage associated with the  $k^{\rm th}$ processing element from the second detection processor. Each processing element performs calculations associated with one trellis stage, comprising a set of transitions between a set of previous states and a set of next states. Each processing element is configured to combine the a priori forward state metrics  $\bar{\boldsymbol{\alpha}}_{k-1} = [\bar{\alpha}_{k-1}(S_{k-1})]_{S_{k-1}=0}^{M-1}$ , the a priori backward state metrics  $\bar{\boldsymbol{\beta}}_k = [\bar{\beta}_k(S_k)]_{S_k=0}^{M-1}$  and the a priori LLR value  $\bar{b}_{1,k}^a$  relating to the data symbol, according to the following equations (7) to (10).

$$\bar{\delta}_k(S_{k-1}, S_k) = \left[ \sum_{j=1}^L \left[ b_j(S_{k-1}, S_k) \cdot \bar{b}_{j,k}^a \right] \right] + \ln[Pr\{S_k | S_{k-1}\}] + \bar{\alpha}_{k-1}(S_{k-1}) + \bar{\beta}_k(S_k)$$

(7)

$$\bar{\alpha}_k(S_k) = \left[ \max^*_{\{S_{k-1} \mid c(S_{k-1}, S_k) = 1\}} \left[ \bar{\delta}_k(S_{k-1}, S_k) \right] \right] - \bar{\beta}_k(S_k)$$

(8)

$$\bar{\beta}_{k-1}(S_{k-1}) = \left[ \max^*_{\{S_k \mid c(S_{k-1}, S_k) = 1\}} \left[ \bar{\delta}_k(S_{k-1}, S_k) \right] \right] - \bar{\alpha}_{k-1}(S_{k-1})$$

(9)

$b_{j,k}^{

m e}$  :

$$\left[\max^*_{\{(S_{k-1},S_k)|b_j(S_{k-1},S_k)=1\}} \left[\bar{\delta}_k(S_{k-1},S_k)\right]\right] - \left[\max^*_{\{(S_{k-1},S_k)|b_j(S_{k-1},S_k)=0\}} \left[\bar{\delta}_k(S_{k-1},S_k)\right]\right] - \left[\bar{b}_{j,k}^a(10)\right] - \left[\min^*_{\{(S_{k-1},S_k)|b_j(S_{k-1},S_k)=0\}} \left[\bar{\delta}_k(S_{k-1},S_k)\right]\right] - \left[\min^*_{\{(S_{k-1},S_k)|b_j(S_k)=0\}} \left[\bar{\delta}_k(S_{k-1},S_k)\right]\right] - \left[\min^*_{\{(S_{k-1},S_k)|b_j(S_k)=0\}} \left[\bar{\delta}_k(S_{k-1},S_k)\right]\right] - \left[\min^*_{\{(S_{k-1},S_k)|b_j(S_k)=0\}} \left[\bar{\delta}_k(S_{k-1},S_k)\right]\right] - \left[\min^*_{\{(S_{k-1},S_k)|b_j(S_k)=0\}} \left[\bar{\delta}_k(S_k,S_k)\right]\right] - \left[\min^*_{\{(S_{k-1},S_k)|b_j(S_k)=0\}} \left[\bar{\delta}_k(S_k,S_k)\right]\right] - \left[\min^*_{\{(S_{k-1},S_k)|b_j(S_k)=0\}} \left[\bar{\delta}_k(S_k,S_k)\right]\right] - \left[\min^*_{\{(S_{k-1},S_k)|b_j(S_k)=0\}} \left[\bar{\delta}_k(S_k,S_k)\right]\right]$$

Each processing element 706, 708 therefore produces the extrinsic forward state metrics  $\overline{\alpha}_k = [\overline{\alpha}_k(S_k)]_{S_k=0}^{M-1}$ , and the extrinsic backward state metrics  $\overline{\beta}_{k-1} = [\overline{\beta}_{k-1}(S_{k-1})]_{S_{k-1}=0}^{M-1}$  and one or more extrinsic LLR values  $\overline{b}_{j,k}^e$  in accordance with the above equations (7) to (10). The processing element 706, 708 then communicates the extrinsic forward state metric  $\overline{\alpha}_k$  to the second neighbouring processing element which becomes the *a priori* forward state metrics for a next iteration, the extrinsic backwards state metrics  $\overline{\beta}_{k-1}$  to the first neighbouring processing element which becomes the *a priori* backward state metric for the next iteration and communicates the one or more extrinsic LLR values  $\overline{b}_{j,k}^e$  for the data information to the other detection processor which become *a priori* LLR values for a next iteration of the turbo detection process.

As will be appreciated therefore, each of the upper and lower turbo decoders 701, 702 uses equation (7) to (10) to combine the L=3 a priori LLR values  $\bar{b}_{1,k}^a$ ,  $\bar{b}_{2,k}^a$  and  $\bar{b}_{3,k}^a$ , as well as the a priori forward state metrics  $\bar{\alpha}_{k-1}$ , the a priori backward state metrics  $\bar{\beta}_k$ . This produces an a posteriori transition metric  $\bar{\delta}_k(S_{k-1}, S_k)$  for each of the possible transitions in the state transition diagram of the  $k^{th}$  stage, namely for each pair of previous state  $S_{k-1}$  and next state  $S_k$  for which  $c(S_{k-1}, S_k) = 1$ . These a posteriori transition metrics are then combined by (8), (9) and (10), in order to produce the vector of extrinsic forward state metrics  $\bar{\alpha}_{k-1} = [\bar{\alpha}_{k-1}(S_{k-1})]_{S_{k-1}=0}^{M-1}$  and the vector of extrinsic backward state metrics  $\bar{\beta}_k = [\bar{\beta}_k(S_k)]_{S_k=0}^{M-1}$  and the extrinsic message LLR  $\bar{b}_{1,k}^e$ , respectively. These equations employ the Jacobian logarithm, which is defined for two operands as

$$\max^*(\overline{\delta}_1, \overline{\delta}_2) = \max(\overline{\delta}_1, \overline{\delta}_2) + \ln(1 + e^{-|(\overline{\delta}_1 - \overline{\delta}_2)|})$$

(11)

and may be extended to more operands by exploiting its associativity property. Alternatively, the exact max\* operator of (11) may be optionally and advantageously replaced with one of the following approximations [4]:

$$\max^*(\overline{\delta}_1, \overline{\delta}_2) \approx \max(\overline{\delta}_1, \overline{\delta}_2) \tag{12}$$

5

10

15

20

25

30

$$\max^*(\overline{\delta}_1, \overline{\delta}_2) \approx A \cdot \max(\overline{\delta}_1, \overline{\delta}_2) + B \tag{13}$$

$$\max^*(\overline{\delta}_1, \overline{\delta}_2) \approx A(\overline{\delta}_1, \overline{\delta}_2) \cdot \max(\overline{\delta}_1, \overline{\delta}_2) + B(\overline{\delta}_1, \overline{\delta}_2) \tag{14}$$

in order to reduce the complexity of the proposed fully-parallel turbo decoder, at the cost of slightly degrading its error correction performance. Note that A and B are constants in equation (12), whereas  $A(\overline{\delta}_1, \overline{\delta}_2)$  and  $B(\overline{\delta}_1, \overline{\delta}_2)$  are simple functions of  $(\overline{\delta}_1, \overline{\delta}_2)$  in equation (14).

The proposed fully-parallel turbo decoder is operated iteratively, where each of the Iiterations comprises the operation of all processing elements or algorithmic blocks shown in Figure 8. The turbo decoder may be considered to be fully-parallel, since each iteration is completed within just T = 1 time period, by operating all 2N of the algorithmic blocks simultaneously. In general, the extrinsic information produced by each algorithmic block in Figure 7 is exchanged with those provided by the connected algorithmic blocks, to be used as a priori information in the next decoding iteration. More specifically, the  $k^{th}$  algorithmic block 706, 708 in each of the upper and lower decoders 701, 702 passes the extrinsic message LLR  $\bar{b}_{1,k}^{e}$  through the interleaver 704, to be used as an *a priori* LLR by the connected block or processing element 706, 708 in the other of the upper and lower decoders 701, 702 during the next decoding iteration. Meanwhile, this processing element or algorithmic block 706, 708 in the other of the upper and the lower decoder 701, 702 provides an extrinsic message LLR which is used as the a priori message LLR  $\bar{b}_{1,k}^a$  during the next decoding iteration. This exchange of the extrinsic LLR message information between the upper and lower decoders 701, 702, which becomes the a priori message LLR  $\bar{b}_{1,k}^a$  for the iteration in the other of the upper and lower decoders 701, 702, via the interleaver 704 corresponds substantially to the operation of the conventional Log-BCJR turbo decoder as explained above with reference to Figure 7. However as explained below, to achieve a fully parallel turbo decoder, the  $k^{th}$  processing element or algorithmic block 706, 708 in each of the upper and lower decoders provides the vectors of extrinsic forward state metrics  $\overline{\alpha}_k$  $[\bar{\alpha}_k(S_k)]_{S_k=0}^{M-1}$  and extrinsic backward state metrics  $\bar{\beta}_{k-1} = [\bar{\beta}_{k-1}(S_{k-1})]_{S_{k-1}=0}^{M-1}$  for the neighbouring algorithmic blocks to employ in the next decoding iteration.

As will be appreciated from the above explanation, embodiments of the present technique can provide a fully parallel implementation for a turbo detector or decoder. To this end, data dependencies, which are present in the Log-BCJR algorithm (illustrated by the bold arrows 630 in Figure 7) are reduced by substituting equation (2) into (5). As a result each of the processing elements or algorithmic blocks 706, 708 is arranged to determine the state transition metric  $\bar{\delta}_k(S_{k-1}, S_k)$  for each of the possible transitions in the state transition diagram of the  $k^{\text{th}}$  stage, namely for each pair of previous state  $S_{k-1}$  and next state  $S_k$  for which  $c(S_{k-1}, S_k) = 1$  by combining the *a priori* forward state metrics and the *a priori* backward state metrics, which were provided as inputs for the present iteration to form the extrinsic forward state metrics and backward state metrics respectively. Furthermore using the identity  $\max^*(\bar{\delta}_1 - \bar{\delta}_3, \bar{\delta}_2 - \bar{\delta}_3) = \max^*(\bar{\delta}_1, \bar{\delta}_2) - \bar{\delta}_3$ , (8) and (9) can be derived by rearranging (5) and substituting it into (3) and (4), respectively.

According to the above explanation, each of the processing elements considers one trellis stage as exemplified in Figure 6 and is arranged to receive both *a priori* forward and backward state metrics in a clock cycle or time period and output the extrinsic forward and backward state metrics. These are provided to the neighbouring processing elements to be used in the next clock cycle or time period. In a single clock cycle in some examples, a plurality of the processing elements from at least two of the decoders can operate in parallel. Furthermore the *a priori* / extrinsic forward state metrics, the *a priori* / extrinsic backward state metrics, the *a priori* message LLRs and the extrinsic message information are represented using a fixed point representation.

Following the completion of the final decoding iteration, an *a posteriori* LLR pertaining to the  $k^{\text{th}}$  message bit  $b_k$  may be obtained as  $\overline{b}_{1,k}^{\text{p}} = \overline{b}_{1,k}^{\text{u,a}} + \overline{b}_{1,k}^{\text{u,e}}$  and may also be combined with systematic information  $\overline{b}_{3,k}^{\text{u,a}}$ . An estimation of the message bit  $b_k$  may then be obtained as the result of the binary test  $\overline{b}_{1,k}^{\text{p}} > 0$ .

A schematic block diagram illustrating one implementation of a processing element 706, 708 shown in Figure 8 is provided in Figure 9. Figure 9 effectively forms the calculations for the  $k^{th}$  trellis stage according to equations (7), (8), (9) and (10). The annotations of Figure 9 indicate the data path widths for the example of the LTE turbo code, which employs sixteen transitions between eight states. As shown in Figure 9 processing element 706 is comprised of four sub processing elements 901, 902, 904, 906 which respectively perform the calculations according to equations (7), (8), (9) and (10). A first sub-processing element 901 receives an *a priori* LLR for each of the *L* message, systematic