# University of Southampton Research Repository

Copyright © and Moral Rights for this thesis and, where applicable, any accompanying data are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis and the accompanying data cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content of the thesis and accompanying research data (where applicable) must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holder/s.

When referring to this thesis and any accompanying data, full bibliographic details must be given, e.g.

Thesis: Author (Year of Submission) "Full thesis title", University of Southampton, name of the University Faculty or School or Department, PhD Thesis, pagination.

Data: Author (Year) Title. URI [dataset]

#### **UNIVERSITY OF SOUTHAMPTON**

Faculty of Engineering and Physical Sciences School of Electronics and Computer Science Smart Electronic Materials and Systems

# **Checkpointing Strategies for Efficient Reactive Intermittent Computing Systems**

by

Timothy S. Daulby

**BEng Electronic Engineering**

ORCiD: 0000-0002-7047-6181

A thesis for the degree of Doctor of Philosophy

January 2023

#### University of Southampton

#### Abstract

Faculty of Engineering and Physical Sciences School of Electronics and Computer Science

#### Doctor of Philosophy

#### **Checkpointing Strategies for Efficient Reactive Intermittent Computing Systems**

by Timothy S. Daulby

The Internet of Things is a growing field, with 1 trillion devices forecast to be collecting, sending and showing information. These devices exist on a scale from the ultra-power constrained to large, data-rich, mains connected devices. Powering the ultra-constrained devices is challenging, particularly when mass, size and cost must be minimised.

Energy harvesting presents a way of increasing the lifetime of battery powered devices. A more sustainable approach is removing any form of energy storage, significantly reducing the mass, size and cost. Unfortunately, energy harvesters have low power density, temporal variation and unpredictability, making running directly from the supply difficult with traditional computing schemes.

A new paradigm, intermittent computing, overcomes intermittency by storing information in non-volatile memory ahead of power-failure. Reactive checkpointing is one such approach that monitors the supply voltage, and interrupts execution to store volatile data before the supply voltage drops below the minimum operating voltage of the processor.

As intermittent computing matures from proof-of-concept to deploy-able systems, adaptation for system-on-chip implementation is crucial to understand the limitations of existing schemes and application agnostic strategies. By profiling power and memory accesses in RTL and gate-level simulations, as well as analysing memory-usage across benchmarks, design criteria can be established.

All intermittent computing schemes suffer performance from the added time and energy overheads of saving state. Two methods for reducing these overheads for any benchmarks and conditions are presented: PowerNapping and Expedit. These give improvements of up to 46.8% and 84.4% in completion time across a range of benchmarks.

# **Contents**

| Li | st of 1 | Figures                                 | ix   |

|----|---------|-----------------------------------------|------|

| Li | st of   | Tables                                  | хi   |

| D  | eclar   | ration of Authorship                    | xiii |

| Ac | knov    | wledgements                             | xv   |

| Ał | brev    | viations                                | xix  |

| No | omen    | nclature                                | xxi  |

| 1  | Intr    | roduction                               | 1    |

|    | 1.1     | Intermittent Computing Systems          | 3    |

|    | 1.2     | Research Justification                  | 4    |

|    | 1.3     | Research Questions                      | 5    |

|    | 1.4     | Contributions                           | 6    |

|    | 1.5     | Publications                            | 7    |

|    | 1.6     | Thesis Structure                        | 7    |

| 2  | A Re    | eview of Intermittent Computing Systems | 9    |

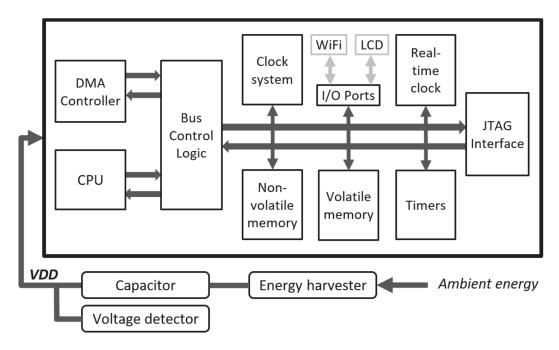

|    | 2.1     | EH-IoT Sensor Architecture              | 9    |

|    |         | 2.1.1 Microcontroller                   | 9    |

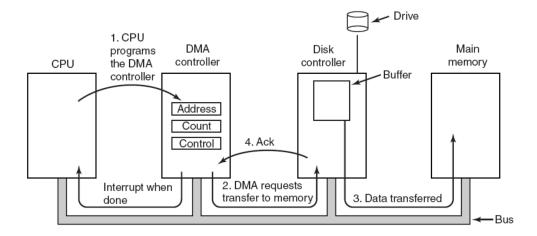

|    |         | 2.1.2 DMA Controller                    | 11   |

|    |         | 2.1.3 Sensors                           | 12   |

|    |         | 2.1.4 Transceiver                       | 12   |

|    | 2.2     | Energy Harvesting                       | 14   |

|    |         | 2.2.1 Photovoltaic Energy Harvesting    | 14   |

|    |         | 2.2.2 Thermo-Electric Energy Harvesting | 15   |

|    |         | 2.2.3 RF Harvesting                     | 16   |

|    |         | 2.2.4 Kinetic Energy Harvesting         | 16   |

|    |         | 2.2.5 Ambient vs External               | 17   |

|    |         | 2.2.6 Summary                           | 17   |

|    |         | 2.2.7 Energy Management                 | 18   |

|    |         | 2.2.7.1 Energy Storage                  | 19   |

|    |         | 2.2.7.2 Input Power Conditioning        | 19   |

|    |         | 2.2.7.3 Output Power Conditioning       | 20   |

|    | 2.3     | EH Sensor Approaches                    | 20   |

|    |         | 2.3.1 Event-Driven                      | 20   |

vi *CONTENTS*

|   |     | 2.3.2 Energy-Neutral                                              | <br>21 |

|---|-----|-------------------------------------------------------------------|--------|

|   | 2.4 | Intermittent Computing                                            | <br>21 |

|   |     | 2.4.1 Checkpointing Approaches                                    | <br>22 |

|   |     | 2.4.2 Task-Based Approaches                                       | 28     |

|   |     | 2.4.3 Non-Volatile Processors                                     | <br>30 |

|   |     | 2.4.4 Predictive Approaches                                       | 31     |

|   |     | 2.4.5 Physical Deployment                                         | 32     |

|   |     | 2.4.6 Summary                                                     | 32     |

|   | 2.5 |                                                                   | 34     |

|   |     | 2.5.1 MATLAB Mathematical Simulation                              | 35     |

|   |     | 2.5.2 Fused Simulation                                            | 37     |

|   |     | 2.5.3 RTL and Gate-level Simulation                               | 37     |

|   | 2.6 |                                                                   | 38     |

|   |     |                                                                   |        |

| 3 | The | e Impact of Memory in Targeting Reactive Intermittent SoC Designs | 41     |

|   | 3.1 |                                                                   | 41     |

|   | 3.2 |                                                                   | 42     |

|   |     | 3.2.1 Intermittent RTL Design                                     | 44     |

|   | 3.3 | Volatile and Non-Volatile Memory in Intermittent Devices          | <br>45 |

|   |     | 3.3.1 NVM vs VM in Design                                         | 46     |

|   |     | 3.3.2 Trading Runtime Performance for Checkpointing Efficiency .  | <br>48 |

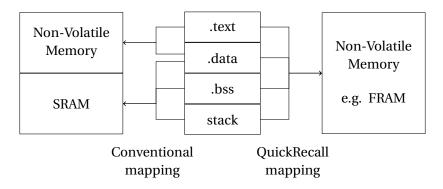

|   |     | 3.3.3 Static Contents of Volatile Memory                          | <br>49 |

|   |     | 3.3.4 Volatile Memory Variation During Execution                  | <br>52 |

|   |     | 3.3.4.1 Stack                                                     | <br>52 |

|   |     | 3.3.4.2 Heap                                                      | <br>54 |

|   |     | 3.3.5 Conclusion                                                  | <br>54 |

|   | 3.4 | Further Application Analysis                                      | <br>54 |

|   |     | 3.4.1 Applications used in existing schemes                       | <br>55 |

|   |     | 3.4.2 Reactive Overheads Compared with Task Completion            | <br>56 |

|   | 3.5 | , 1                                                               | 59     |

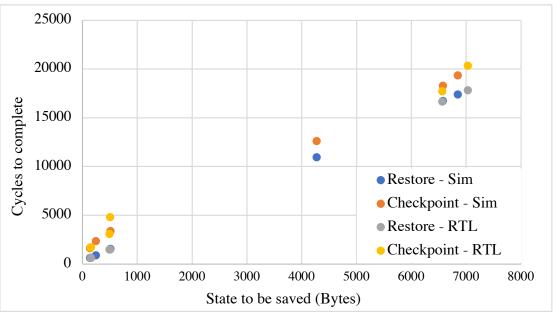

|   |     | 3.5.1 RTL Implementation Error                                    | <br>59 |

|   |     | 3.5.2 Selecting the Correct Non-Volatile Memory                   | <br>61 |

|   |     | 3.5.3 Energy Consumption                                          | <br>62 |

|   |     | 3.5.4 Latency                                                     | <br>62 |

|   |     | 3.5.5 Endurance                                                   | <br>64 |

|   |     | 3.5.6 Comparison                                                  | <br>65 |

|   | 3.6 | S Summary and Discussion                                          | <br>65 |

| 4 | Enh | hanced Checkpointing for Intermittent High-Power Sources          | 67     |

| • | 4.1 |                                                                   | 67     |

|   | 4.2 |                                                                   | 67     |

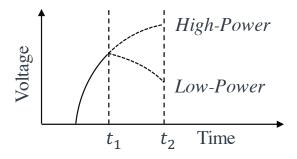

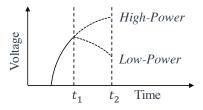

|   | 1.2 | 4.2.1 Low-Power and High-Power Sources                            | 70     |

|   | 4.3 |                                                                   | 72     |

|   | 1.0 | 4.3.1 The Benefit of Design Time Energy Awareness                 | 72     |

|   |     | 4.3.2 The Benefit of Runtime Energy Awareness                     | 73     |

|   |     | 4.3.3 Energy Consumption During Checkpointing                     | 74     |

|   | 4.4 |                                                                   | 75     |

|   | 7.7 | Discounting oystem resources for enforcing chickpointing          | <br>13 |

*CONTENTS* vii

| n. | c          | ncas                                                           | 120      |

|----|------------|----------------------------------------------------------------|----------|

| Аp | pen        | dix A Published Papers                                         | 117      |

|    | 6.2        | Future Work                                                    | 114      |

|    | 6.1        | Conclusions                                                    | 113      |

| 6  | Con        | nclusions                                                      | 113      |

|    | 5.8        | Summary and Discussion                                         | 111      |

|    | <b>5</b> 0 |                                                                | 108      |

|    |            |                                                                | 106      |

|    |            | 1                                                              | 105      |

|    | 5.7        | 1                                                              | 105      |

|    | 5.6        |                                                                | 104      |

|    | 5.5        |                                                                | 102      |

|    | _          |                                                                | 101      |

|    |            |                                                                | 100      |

|    | 5.4        | PowerNapping Design                                            | 96       |

|    | 5.3        | PowerNapping                                                   | 94       |

|    |            | 5.2.3 Increased Complexity                                     | 93       |

|    |            | 5.2.2 Checkpoint Optimisation by Reducing Stack                | 93       |

|    |            | 5.2.1 Task Completion                                          | 92       |

|    | 5.2        | Push-Through                                                   | 92       |

|    | 5.1        | Introduction                                                   | 91       |

| 5  | Inte       | ermittent Computing with Consistent, but Scarce Energy Sources | 91       |

|    |            | ·                                                              | 55       |

|    | 4.6        | Summary and Discussion                                         | 89       |

|    |            | 4.5.4.2 Results                                                | 83       |

|    |            | 4.5.4.1 Experimental Method                                    | 83       |

|    |            | 4.5.4 Practical Validation                                     | 82       |

|    |            | 4.5.3 Simulation                                               | 80       |

|    |            | 4.5.1 Expedit - Reducing State Save Overneads                  | 78<br>79 |

|    | 4.3        | 4.5.1 Expedit - Reducing State Save Overheads                  | 77<br>78 |

|    | 4.5        | Disabling the CPU During Checkpointing                         | 77       |

|    |            | 4.4.3 Low Power Modes                                          | 70<br>77 |

|    |            | <ul><li>4.4.1 Isolating Peripherals</li></ul>                  | 76<br>76 |

|    |            | 4.4.1 Isolating Peripherals                                    | 76       |

# **List of Figures**

| 1.1  | Example of a wireless IoT sensor device                                                                  | 1  |

|------|----------------------------------------------------------------------------------------------------------|----|

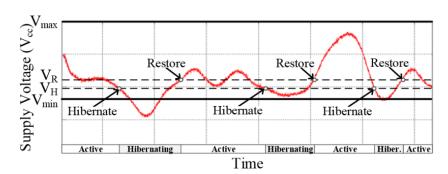

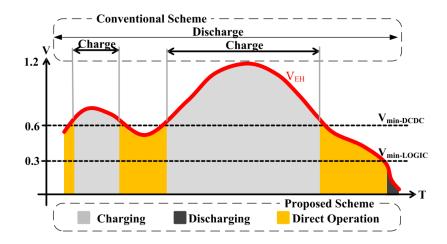

| 1.2  | Operation of Hibernus in response to intermittent supply voltage                                         | 5  |

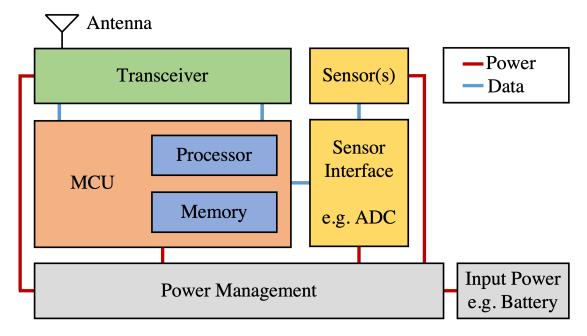

| 2.1  | Perpetually powered sensor architecture                                                                  | 10 |

| 2.2  | Operation of a DMA transfer                                                                              | 12 |

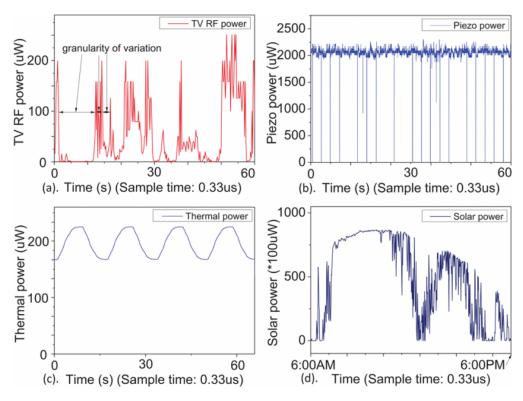

| 2.3  | Power traces a)TV RF b) Piezo c) Thermal d) Solar                                                        | 14 |

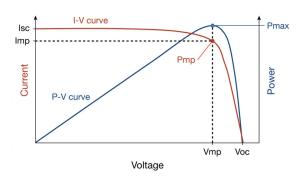

| 2.4  | Graph showing IV and PV characteristics of a PV cell                                                     | 15 |

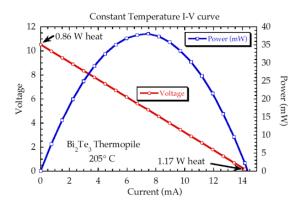

| 2.5  | I-V and P-V characteristic of a thermoelectric generator                                                 | 16 |

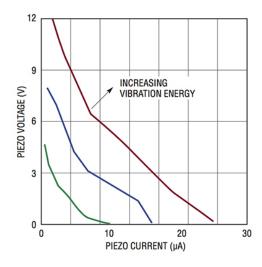

| 2.6  | IV curve for a piezoelectric harvester                                                                   | 17 |

| 2.7  | Conceptual representation of reciprocal conversion                                                       | 20 |

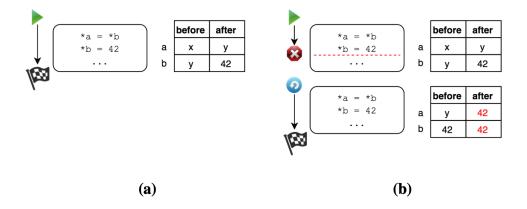

| 2.8  | The same code executed with and without power failure to demonstrate idem-                               |    |

|      | potence violations                                                                                       | 23 |

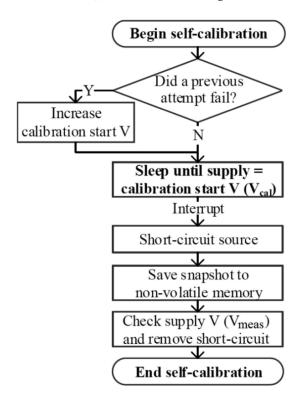

| 2.9  | Calibration routine for setting thresholds in Hibernus++                                                 | 25 |

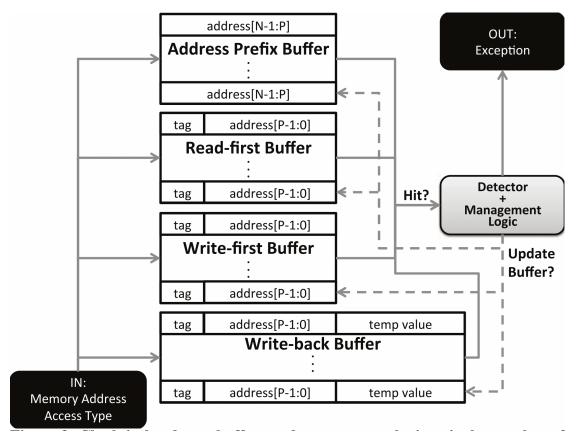

| 2.10 | Clank in-hardware buffers and management logic                                                           | 27 |

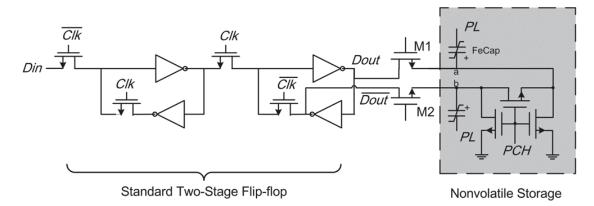

| 2.11 | Non-volatile flip flop design                                                                            | 31 |

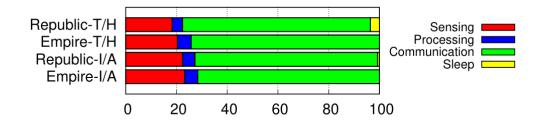

| 2.12 | Breakdown of percentage energy consumption depending on functionality                                    | 33 |

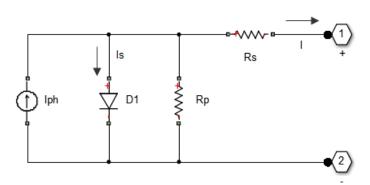

| 2.13 | Equivalent circuit of a photovoltaic (PV) cell using a single diode model                                | 35 |

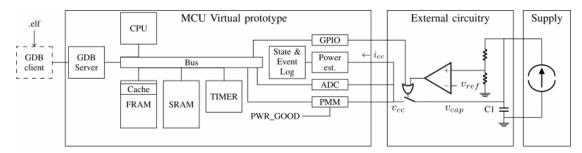

| 2.14 | Model architecture of fused                                                                              | 37 |

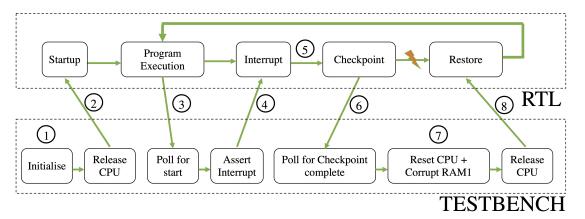

| 3.1  | Register transfer level (RTL) implementation                                                             | 44 |

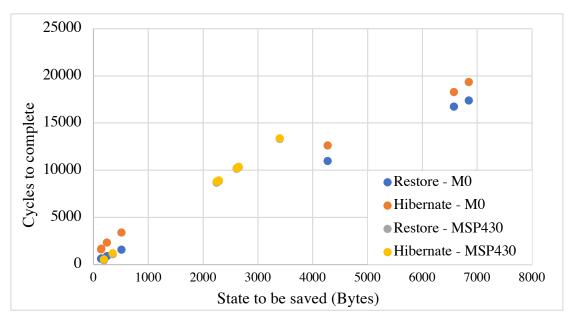

| 3.2  | Comparison of state transfer cycles for a number of benchmarks of differing                              |    |

|      | size                                                                                                     | 47 |

| 3.3  | QuickRecall linker map compared to conventional system                                                   | 48 |

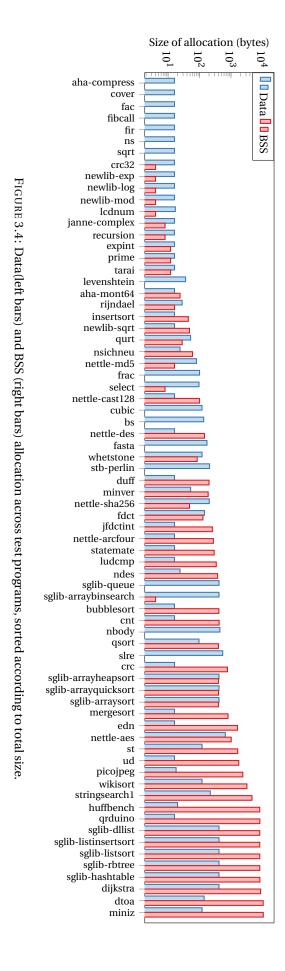

| 3.4  | Data(left bars) and BSS (right bars) allocation across test programs, sorted ac-                         |    |

|      | cording to total size                                                                                    | 50 |

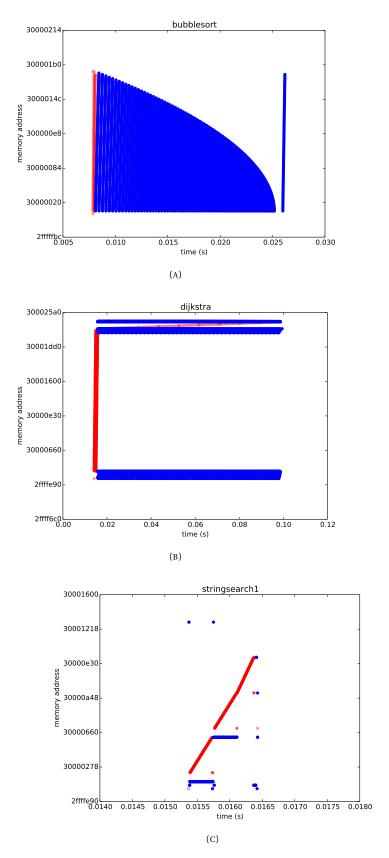

| 3.5  | $\label{eq:continuous} A plot of memory reads and writes against time during execution of test programs$ | 51 |

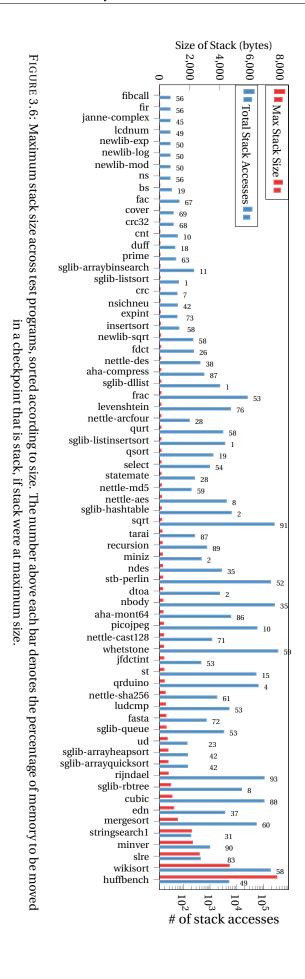

| 3.6  | Maximum stack size across test programs, sorted according to size                                        | 53 |

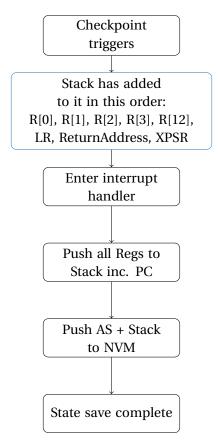

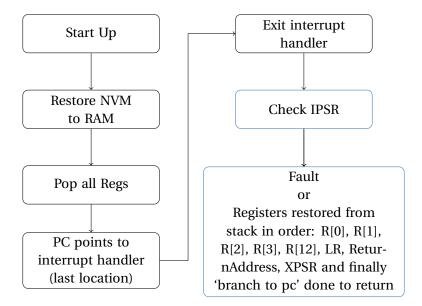

| 3.7  | Checkpoint routine used in RTL implementation                                                            | 60 |

| 3.8  | •                                                                                                        | 61 |

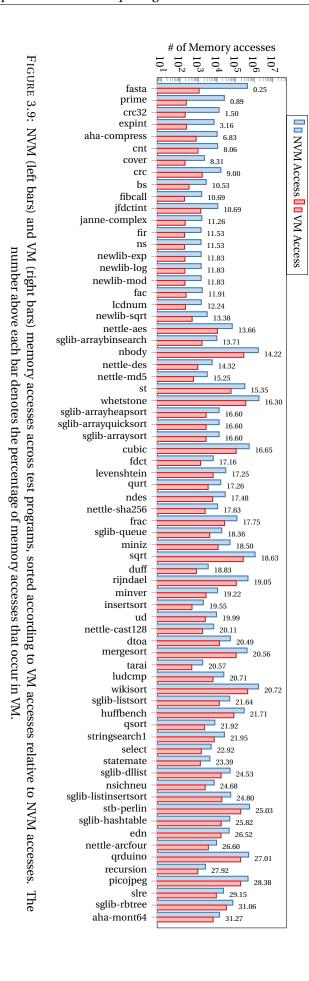

| 3.9  | Non-volatile memory (NVM) and volatile memory (VM) memory accesses across                                |    |

|      |                                                                                                          | 63 |

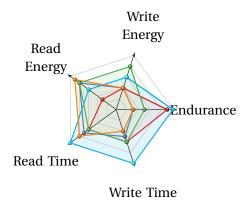

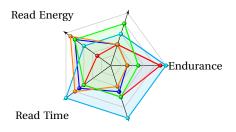

| 3.10 | Radar plot of NVM characteristics                                                                        | 64 |

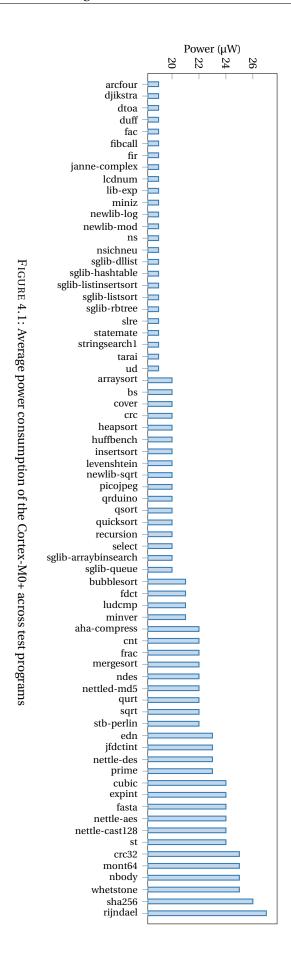

| 4.1  |                                                                                                          | 69 |

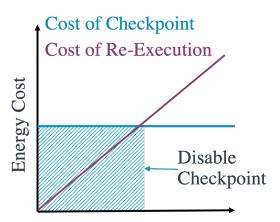

| 4.2  | Dynamically disabling checkpointing                                                                      | 74 |

| 4.3  | Representation of the difference in time available for active computation with                           |    |

|      | three different current consumption's during checkpointing                                               | 75 |

| 4.4  | Predicted improvement in forward progress according to MATLAB simulation                                 |    |

|      | for an interrupted high-power source                                                                     | 81 |

X LIST OF FIGURES

| 4.5  | Predicted improvement in forward progress according to MATLAB simulation .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 81  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

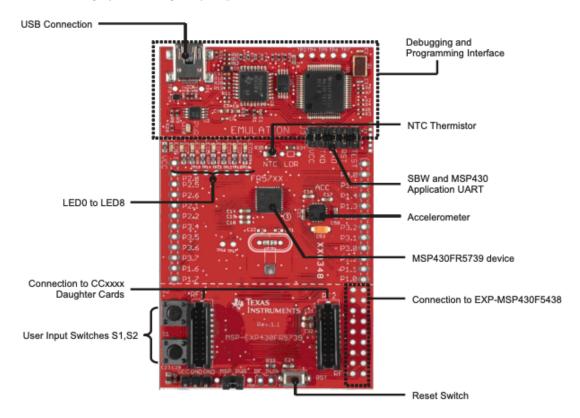

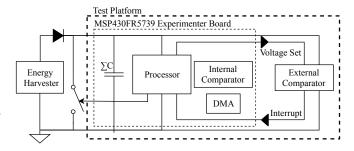

| 4.6  | MSP-EXP430FR5739 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 82  |

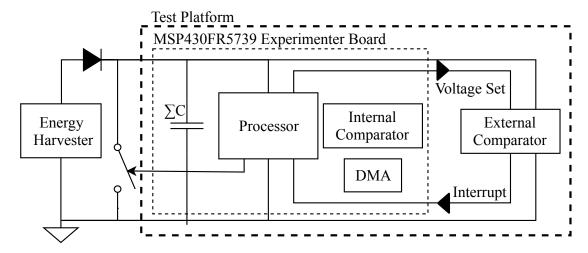

| 4.7  | Schematic of the test platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 83  |

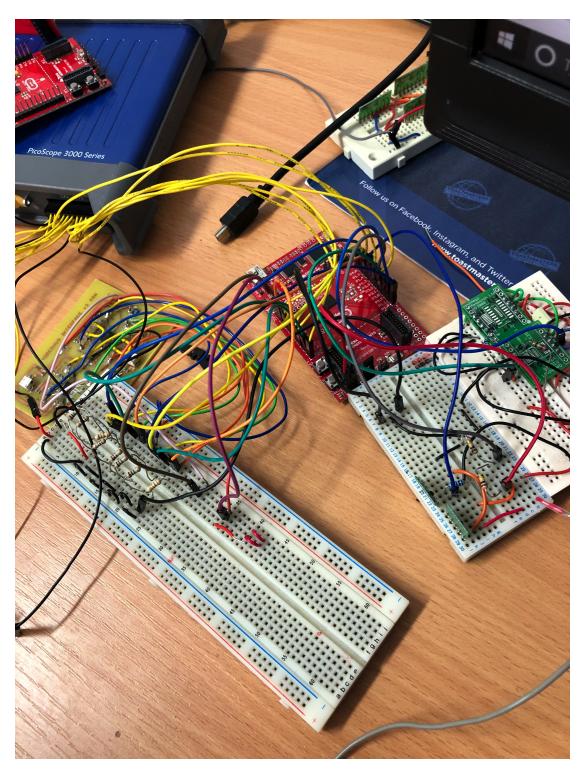

| 4.8  | Experimental Test Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 84  |

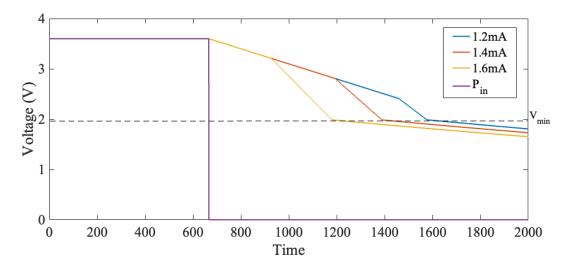

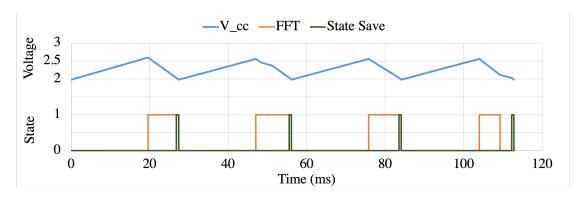

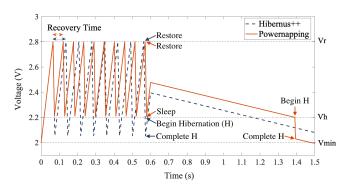

| 4.9  | Voltage over time for fast-fourier transform (FFT) benchmark running Expedit,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|      | including digital signals for active computation and state saving                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 85  |

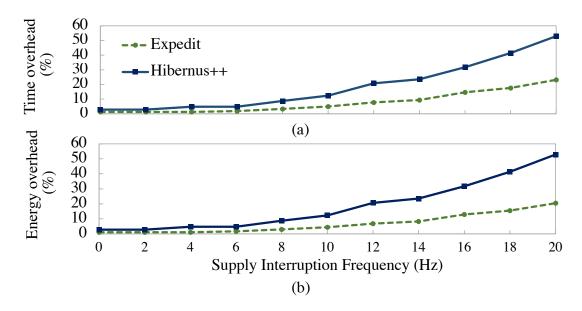

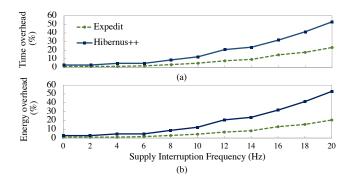

| 4.10 | Overhead comparisons for Expedit and Hibernus++                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 86  |

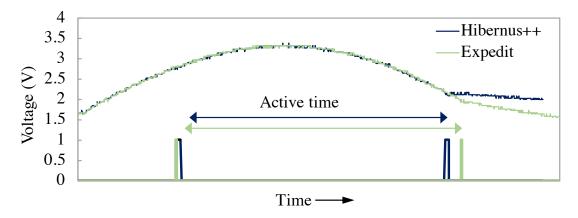

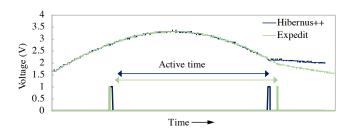

| 4.11 | Expedit increase in active time with sinusoidal voltage input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 86  |

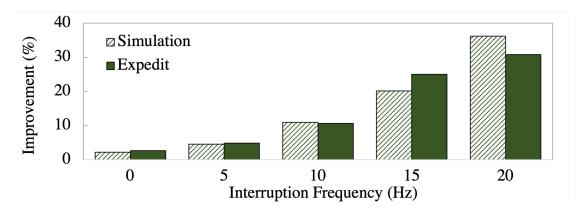

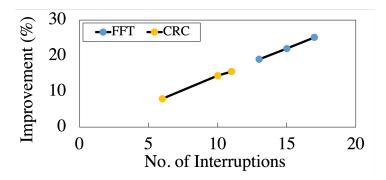

| 4.12 | Improvement in FFT complete time for Expedit over Hibernus++ including sim-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|      | ulation for a representative high-power source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 87  |

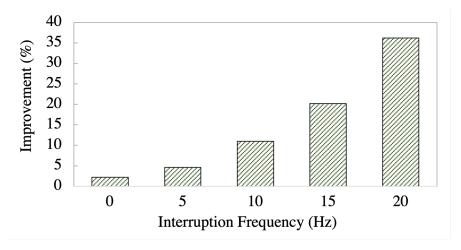

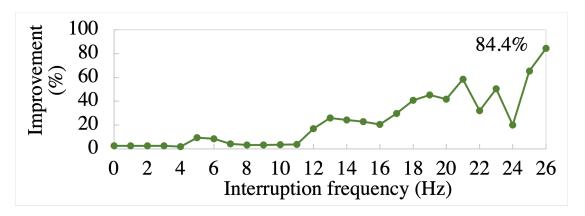

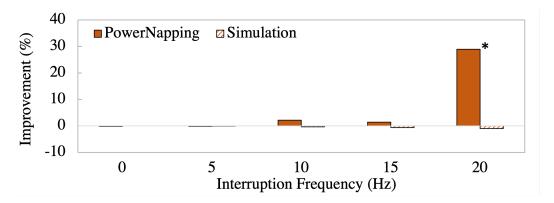

| 4.13 | Improvement in FFT complete time for Expedit over Hibernus++ for 0-26Hz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|      | interrupted source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 87  |

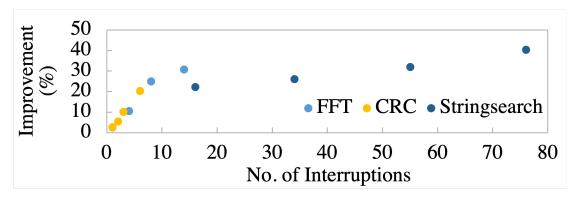

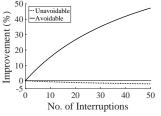

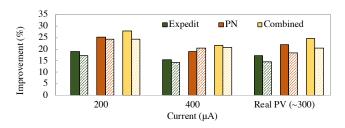

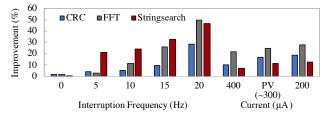

| 4.14 | Improvement in benchmark complete time for Expedit over Hibernus++                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

|      | compared with number of interruptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 88  |

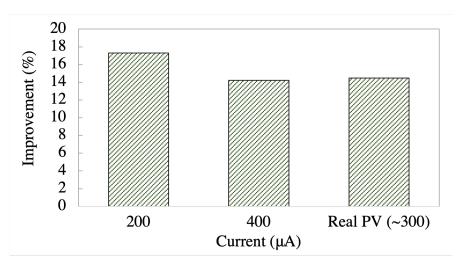

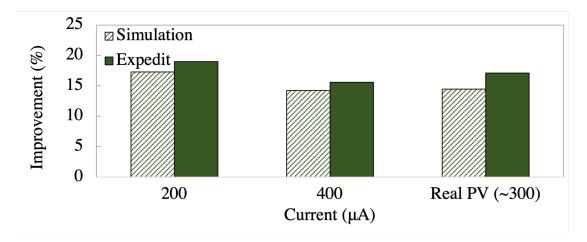

| 4.15 | Improvement in FFT complete time for Expedit over Hibernus++ including Sim-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|      | ulation for low-power sources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 88  |

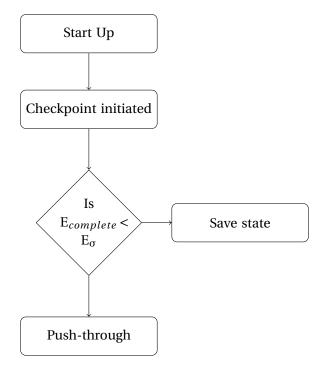

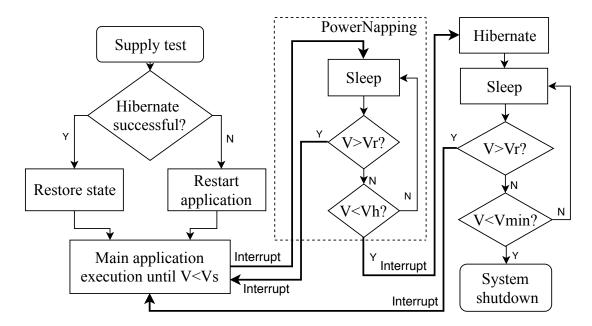

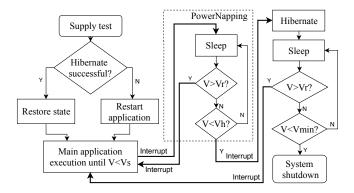

| 5.1  | Decision flowchart for push-through mechanism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 93  |

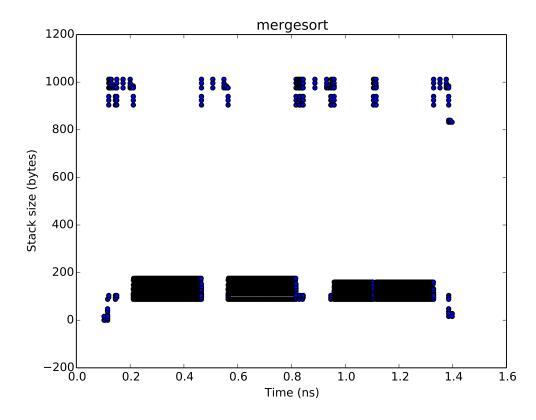

| 5.2  | Stack variation over time for mergesort                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 94  |

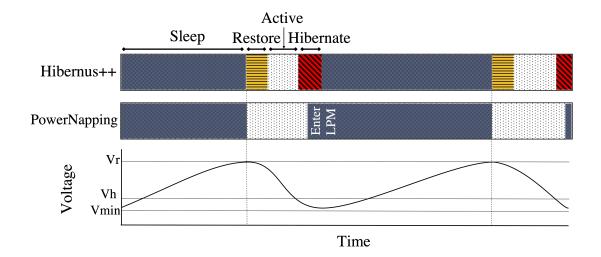

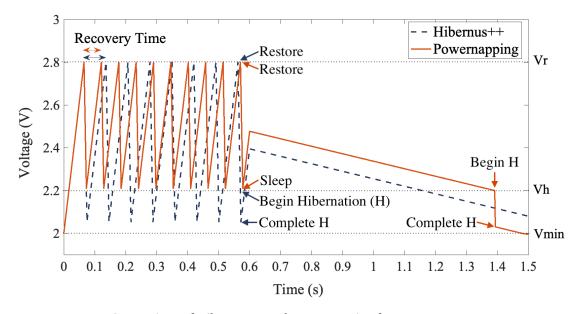

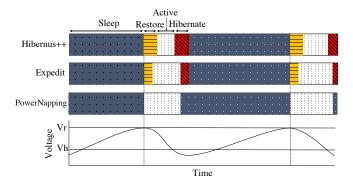

| 5.3  | Illustration of system operation for a given supply with PowerNapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 97  |

| 5.4  | State diagram of PowerNapping approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 99  |

| 5.5  | Illustration of high/low power is determined using an ADC during startup routine.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

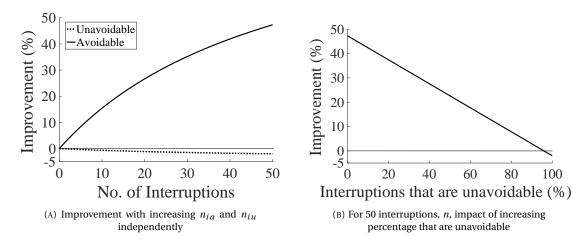

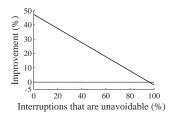

| 5.6  | Improvement of PowerNapping with changing $n_{ia}$ and $n_{iu}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 33  |

| 3.0  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 103 |

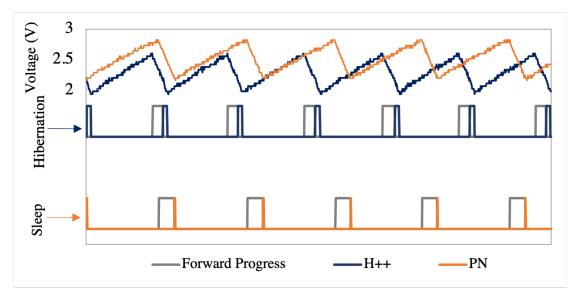

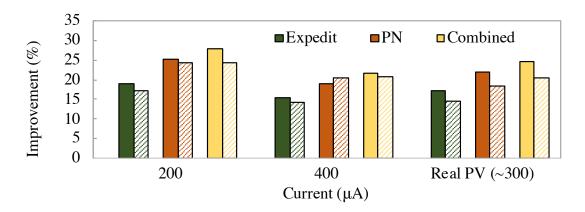

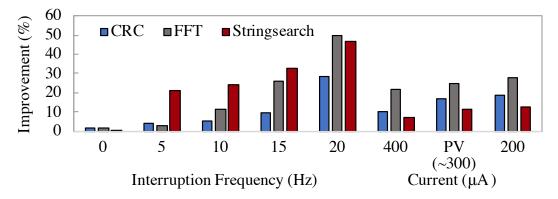

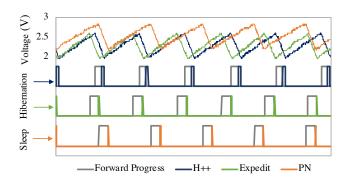

| 5.7  | Comparison of Hibernus++ and PowerNapping for a constant current source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 100 |

| 5.1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 104 |

| 5.8  | Comparison of PowerNapping and Hibernus++ with PV cell input energy source,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| 0.0  | 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 107 |

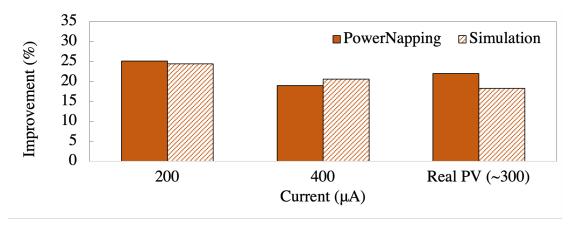

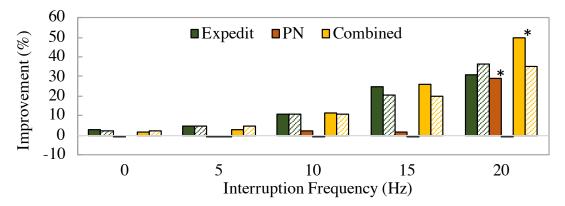

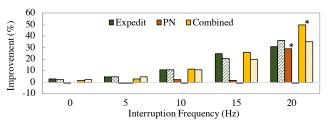

| 5.9  | Improvement in FFT complete time for PowerNapping over Hibernus++ includ-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |