Copyright © and Moral Rights for this thesis and, where applicable, any accompanying data are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis and the accompanying data cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content of the thesis and accompanying research data (where applicable) must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holder/s. When referring to this thesis and any accompanying data, full bibliographic details must be given, e.g.

Thesis: Sivert T. Sliper (2022) "Off and On Again: Modeling and Optimizing Intermittent Computing Systems", University of Southampton, Faculty of Engineering and Physical Sciences, PhD Thesis, 102 pages.

#### Data:

Sivert T. Sliper (2019) Dataset supporting "Efficient State Retention through Paged Memory Management for Reactive Transient Computing". https://eprints.soton.ac.uk/428696/ [dataset]

Sivert T. Sliper (2020) Dataset supporting "Fused: Closed-Loop Performance and Energy Simulation of Embedded Systems". https://eprints.soton.ac.uk/437156/[dataset]

Sivert T. Sliper (2022) Dataset supporting the journal article "Pragmatic Memory-System Support for Intermittent Computing using Emerging Non-Volatile Memory". https://eprints.soton.ac.uk/456087/[dataset]

## University of Southampton

Faculty of Engineering and Physical Sciences School of Electronics and Computer Science

# Off and On Again: Modeling and Optimizing Intermittent Computing Systems

by

Sivert T. Sliper

ORCiD: 0000-0002-8991-3783

A thesis for the degree of Doctor of Philosophy

November 2022

#### University of Southampton

#### Abstract

Faculty of Engineering and Physical Sciences School of Electronics and Computer Science

#### Doctor of Philosophy

#### Off and On Again: Modeling and Optimizing Intermittent Computing Systems

by Sivert T. Sliper

Intermittent computing (IC) is a vital technology for realizing IoT at a vast scale. By harvesting energy from the environment, and leveraging non-volatile memory (NVM) to retain computational progress through power cycles, IC enables untethered and battery-free devices that perform incremental computation whenever ambient energy is available. The backbone of IC is NVM, and recent advances in energy-efficient byte-addressable NVM have the potential to expand the application domain of IC substantially. The tight interaction between energy and execution does, however, cause complexities that require specialized modeling, hardware design, and software design; complexities that hamper adoption. This thesis is focused on optimizing IC using software and hardware support leveraging energy-efficient NVM, and also on system-level modeling of IC systems to enable such research.

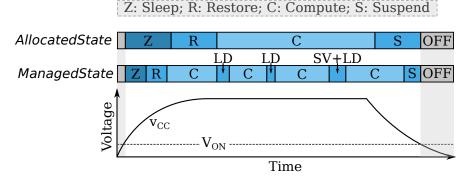

Supporting IC on commercially available microcontrollers is important to lower the barrier to entry, and for adoption of IC in real-world applications. However, current methods suffer from inefficient state retention. To address this issue, this thesis proposes Managed State, a new page-based memory manager that tracks used and modified regions of memory to reduce the overhead of state retention by 26-87 %. To make IC as efficient, robust and useful as possible, however, software support alone is insufficient. Hardware support for IC is needed; and to research system-level hardware support for IC, electronic system-level modeling is the most reasonable approach. However, modeling IC presents unique challenges that current modeling tools do not support, most prominent of which is the tight interactions between energy and execution. To model IC systems, this thesis proposes a new full-system simulator, named Fused, that specifically models the interplay between energy and execution in IC devices. Using Fused, this thesis then explores new hardware support for IC that leverages energy-efficient and byte-addressable NVMs. The result is MEMIC, a memory architecture with hardware support that improves performance by 13-39 % compared to the state-of-art, and furthermore allows systems to operate under harsher conditions. MEMIC strives to combine volatile- and non-volatile memory in such a way that the operations of IC are as efficient as possible, while also maximizing computational performance per joule.

# **Contents**

| Li | st of  | Figures  | 5                                                             | ix   |

|----|--------|----------|---------------------------------------------------------------|------|

| Li | st of  | Tables   |                                                               | xiii |

| D  | efinit | ions an  | nd Abbreviations                                              | xv   |

| D  | eclara | ation of | f Authorship                                                  | xvi  |

| 1  | Intr   | oductio  | on                                                            | 1    |

|    | 1.1    | Resea    | rch justification                                             | 3    |

|    | 1.2    | Resea    | rch questions                                                 | 6    |

|    | 1.3    | Resea    | rch contributions                                             | 7    |

|    |        | 1.3.1    | Taxonomy of IC methods for COTS microcontrollers              | 7    |

|    |        | 1.3.2    | Paged memory management for efficient state retention on COTS |      |

|    |        |          | microcontrollers                                              | 8    |

|    |        | 1.3.3    | Full-system simulator for IC research                         | 8    |

|    |        | 1.3.4    | Memory system support for efficient IC                        | 9    |

|    | 1.4    | Orgar    | nization                                                      | 9    |

| 2  | Inte   | rmitte   | nt computing                                                  | 11   |

|    | 2.1    | Challe   | enges of intermittent computing (IC)                          | 11   |

|    | 2.2    | Appli    | cation constraints for intermittent operation                 | 15   |

|    | 2.3    | Re-ex    | ecution bugs                                                  | 16   |

|    | 2.4    | Corre    | ctness requirements, performance goals and scalability goals  | 18   |

|    | 2.5    | Taxon    | nomy                                                          | 20   |

|    |        | 2.5.1    | Static IC                                                     | 21   |

|    |        | 2.5.2    | Task-based IC                                                 | 22   |

|    |        | 2.5.3    | Reactive IC                                                   | 24   |

|    | 2.6    | Suppo    | orting failure-atomic section (FASE) execution                | 26   |

|    | 2.7    | Proto    | typing and evaluating IC devices                              | 27   |

|    |        | 2.7.1    | Hardware prototyping                                          | 27   |

|    |        | 2.7.2    | Analytical modelling                                          | 28   |

|    |        | 2.7.3    | Simulation of IC hardware and software                        | 29   |

|    | 2.8    | Lever    | aging emerging NVM for IC                                     | 31   |

|    |        | 2.8.1    | Non-volatile processors                                       | 33   |

|    |        | 2.8.2    | Hardware support                                              | 34   |

|    | 29     | Summ     | nary and discussion                                           | 35   |

vi CONTENTS

| 3 |            | cient int<br>crollers | termittent computing on commercial off-the-shelf (COTS) micro- |

|---|------------|-----------------------|----------------------------------------------------------------|

|   |            |                       |                                                                |

|   | 3.1        |                       |                                                                |

|   | 3.2        |                       | 8                                                              |

|   | 3.3        | 0                     | 41                                                             |

|   | 3.4        | -                     | nic suspend and restore thresholds                             |

|   | 3.5        |                       | tion                                                           |

|   |            | 3.5.1                 | Experimental setup                                             |

|   |            | 3.5.2                 | Memory tracking                                                |

|   |            | 3.5.3                 | Suspend and restore time                                       |

|   |            | 3.5.4                 | Suspend threshold                                              |

|   | 2 (        | 3.5.5                 | Application performance                                        |

|   | 3.6        | Discus                | sion                                                           |

| 4 | Mod        | deling i              | ntermittent computing systems 55                               |

|   | 4.1        | Introdu               | uction                                                         |

|   | 4.2        | Experi                | mental Setup                                                   |

|   | 4.3        | Model                 | overview                                                       |

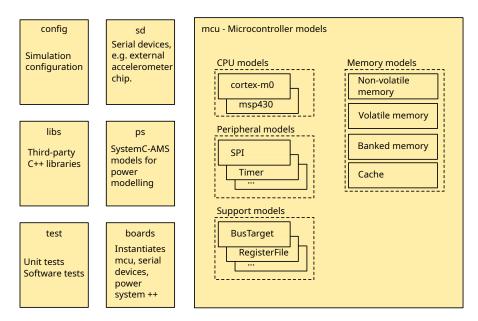

|   |            | 4.3.1                 | Implementation                                                 |

|   |            | 4.3.2                 | Simulation target 61                                           |

|   |            | 4.3.3                 | Software interface                                             |

|   |            | 4.3.4                 | CPU 62                                                         |

|   |            | 4.3.5                 | Bus                                                            |

|   |            | 4.3.6                 | Peripherals                                                    |

|   |            | 4.3.7                 | Power management module                                        |

|   |            | 4.3.8                 | Memory                                                         |

|   |            | 4.3.9                 | Event & state logging                                          |

|   |            | 4.3.10                | Power estimator                                                |

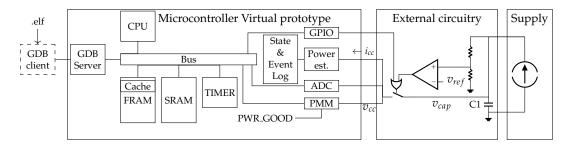

|   |            | 4.3.11                | External circuitry and power supply 64                         |

|   | 4.4        |                       | modeling methodology                                           |

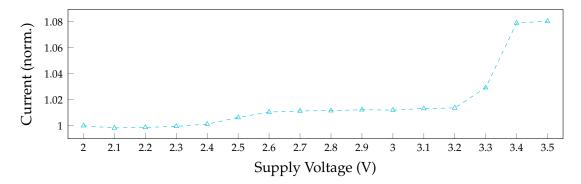

|   |            | 4.4.1                 | Power profiling                                                |

|   |            |                       | Selecting explanatory variables for linear regression          |

|   |            | 4.4.3                 | Hardware boot                                                  |

|   | 4.5        | Experi                | mental Validation                                              |

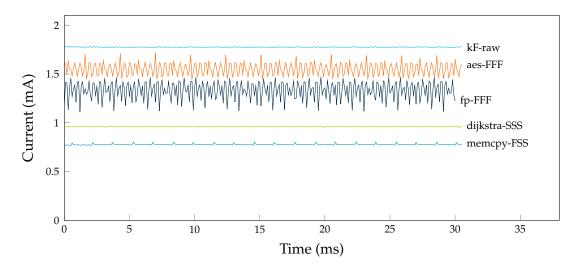

|   |            | 4.5.1                 | Computational kernels & benchmarks                             |

|   |            | 4.5.2                 | Execution time                                                 |

|   |            | 4.5.3                 | Cache model                                                    |

|   |            | 4.5.4                 | Power estimation                                               |

|   | 4.6        | Case st               | tudy: Simulating intermittent computing systems                |

|   |            | 4.6.1                 | Experimental setup                                             |

|   |            | 4.6.2                 | Results & analysis                                             |

|   | 4.7        | Discus                | sion                                                           |

| 5 | Mor        | n <i>or</i> v-er      | stem support for intermittent computing 79                     |

| J | 5.1        |                       | uction                                                         |

|   | 5.2        |                       | ry-System Support for Reactive Intermittent Computing          |

|   | <b>∪.∠</b> |                       | Objectives                                                     |

*CONTENTS* vii

|   |     | 5.2.2   | Target technology                                           | 81  |

|---|-----|---------|-------------------------------------------------------------|-----|

|   |     | 5.2.3   | Top-level architecture                                      | 82  |

|   |     | 5.2.4   | Minimizing writes to non-volatile memory (NVM) and limiting |     |

|   |     |         | volatile state                                              | 84  |

|   |     | 5.2.5   | Suspend and restore during normal execution                 | 86  |

|   |     | 5.2.6   | Suspend and restore during failure-atomic sections          | 86  |

|   |     | 5.2.7   | Undo logging module                                         | 86  |

|   |     | 5.2.8   | The unsafe zone                                             | 87  |

|   | 5.3 | Evalua  | ation                                                       | 88  |

|   |     | 5.3.1   | Experimental setup                                          | 89  |

|   |     | 5.3.2   | Workloads                                                   | 91  |

|   |     | 5.3.3   | Baseline                                                    | 91  |

|   |     | 5.3.4   | Cache configuration                                         | 92  |

|   |     | 5.3.5   | Instruction Cache                                           | 93  |

|   |     | 5.3.6   | Data Cache                                                  | 96  |

|   |     | 5.3.7   | Operating conditions                                        | 97  |

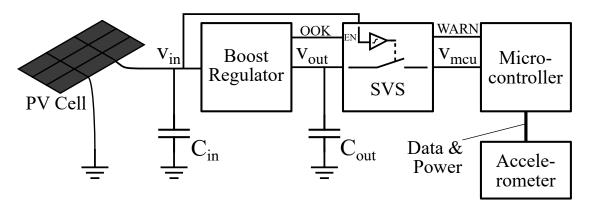

|   |     | 5.3.8   | Case study: Solar-powered sensor node                       | 99  |

|   |     | 5.3.9   | Endurance                                                   | 100 |

|   | 5.4 | Discus  | ssion                                                       | 101 |

| 6 | Con | clusior | ns and future work                                          | 103 |

|   | 6.1 | Concl   | usions                                                      | 103 |

|   | 6.2 | Future  | e work                                                      | 105 |

# **List of Figures**

| 1.1 | controller, some power management circuitry, and an energy harvester.                                                                                                                                                                                                                                                                                                                                                                       | ,   |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.2 | Illustration of intermittent operation. The device operates during brief on-periods (typically in the order of milliseconds), until its stored energy is depleted. It then remains off until the supply voltage recovers                                                                                                                                                                                                                    | 3   |

| 2.1 | Pseudo code illustrating three possible faults when re-executing arbitrary sections of code                                                                                                                                                                                                                                                                                                                                                 | 17  |

| 2.2 | State machine representation of (a) static, (b) task-based and (c) reactive IC. Reactive IC has simpler state transitions, most importantly avoiding power-off edges (red) from any states where idempotency violations can occur.                                                                                                                                                                                                          | 21  |

| 2.3 | Behavior of the three classes of IC strategies with regards to $v_{cc}$                                                                                                                                                                                                                                                                                                                                                                     | 21  |

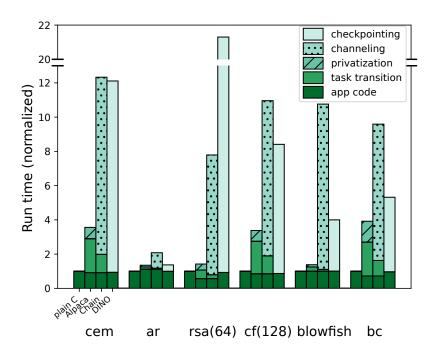

| 2.4 | Run-time overhead of task-based methods while continuously powered (no reboots). Reprinted from [96], 10a                                                                                                                                                                                                                                                                                                                                   | 23  |

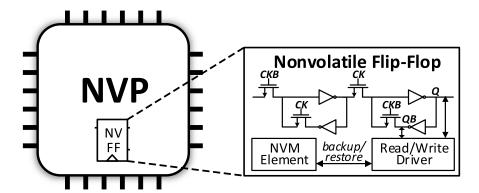

| 2.5 | Example NVM-backed flipflop used as registers in [87]. The figure is re-arranged and reprinted from [87]                                                                                                                                                                                                                                                                                                                                    | 33  |

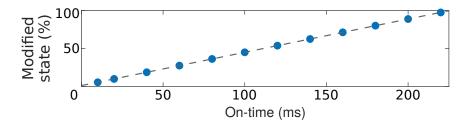

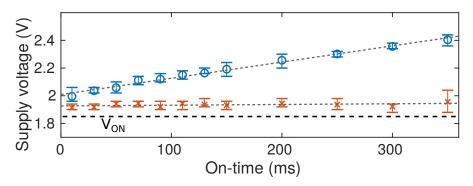

| 3.1 | Percentage of allocated memory that is modified at the end of an on-<br>period in relation to its duration (on-time)                                                                                                                                                                                                                                                                                                                        | 37  |

| 3.2 | Conceptual comparison between <i>AllocatedState</i> , and <i>ManagedState</i> , in response to a power supply trace                                                                                                                                                                                                                                                                                                                         | 39  |

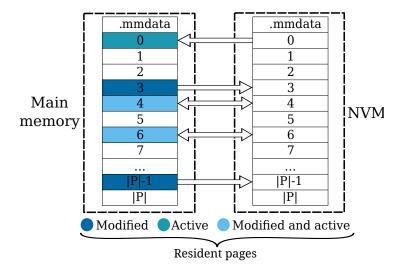

| 3.3 | Illustration of the memory operations of <i>ManagedState</i>                                                                                                                                                                                                                                                                                                                                                                                | 4(  |

| 3.4 | A code snippet that encrypts a 2kB string using advanced encryption standard (AES). For clarity, this example is somewhat simplified compared to the AES workload used in the evaluation section (cipher block                                                                                                                                                                                                                              |     |

|     | chaining is ommitted).                                                                                                                                                                                                                                                                                                                                                                                                                      | 42  |

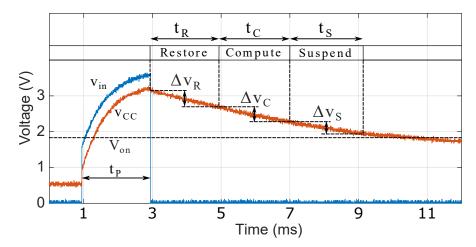

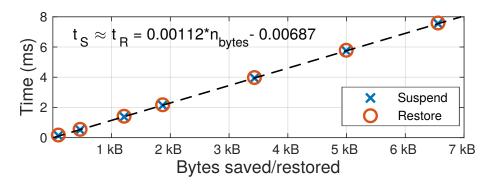

| 3.5 | Safe restore and suspend thresholds                                                                                                                                                                                                                                                                                                                                                                                                         | 45  |

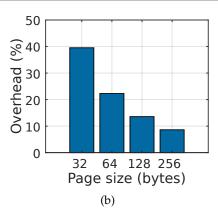

| 3.6 | Execution time of suspend and restore operations                                                                                                                                                                                                                                                                                                                                                                                            | 45  |

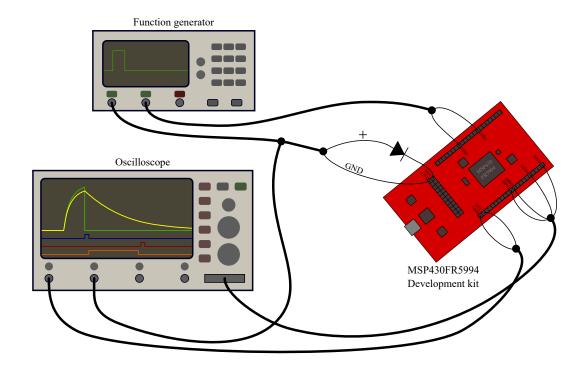

| 3.7 | Experimental setup. The first channel from the function generator is used as a configurable power supply, and the second channel is used (in some experiments) to generate general purpose input/output (GPIO) interrupts. An oscilloscope is used to measure the input voltage, supply voltage, and GPIO pins that indicate activity. The rectifying diode prevents current backflow from the development board to the function generator. | 42  |

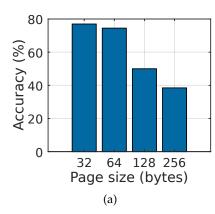

| 3.8 | (a) Tracking accuracy and (b) suspend time overhead, in relation to page size $ p $ .                                                                                                                                                                                                                                                                                                                                                       | 48  |

|     | - 51/25 1//1                                                                                                                                                                                                                                                                                                                                                                                                                                | -+( |

x LIST OF FIGURES

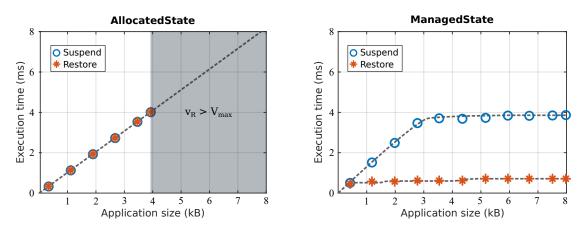

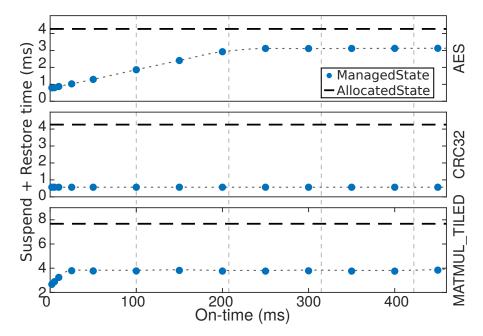

| 3.9        | Suspend and restore time of <i>ManagedState</i> and <i>AllocatedState</i> in relation to application size                                                                                                                                                                                                        | 50                              |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

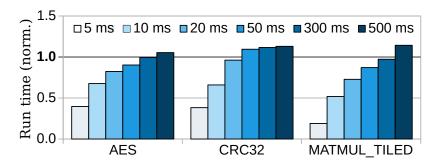

| 3.11       | Accumulated suspend and restore time in relation to on-time Supply voltage at the start and completion of suspend Benchmark run time relative to <i>AllocatedState</i> when powered by square-                                                                                                                   | 51<br>52                        |

|            | wave pulses                                                                                                                                                                                                                                                                                                      | 52                              |

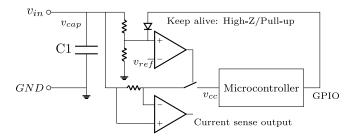

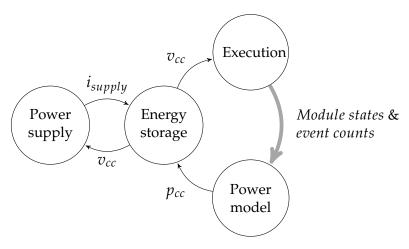

| 4.1<br>4.2 | Hardware test platform                                                                                                                                                                                                                                                                                           | <ul><li>59</li><li>60</li></ul> |

| 4.3        | step                                                                                                                                                                                                                                                                                                             | 61                              |

| 4.4        | Model architecture of Fused. This proof-of-concept implementation targets the system shown in Figure 4.1, but all modules within the virtual prototype, external circuitry and supply can readily be modified or re-                                                                                             | Ü1                              |

|            | placed                                                                                                                                                                                                                                                                                                           | 62                              |

| 4.5        | Average current consumption across all kernels as a function of supply                                                                                                                                                                                                                                           | <b></b>                         |

| 4.6        | voltage, normalized to the current draw at $2V$                                                                                                                                                                                                                                                                  | 65                              |

| 4.0        | tion is highly application-dependent, and can exhibit relatively large variations over time.                                                                                                                                                                                                                     | 66                              |

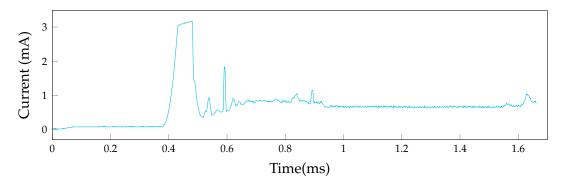

| 4.7        | Current consumption during hardware boot                                                                                                                                                                                                                                                                         | 68                              |

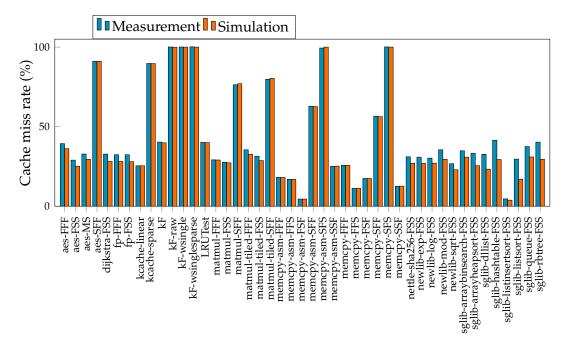

| 4.8        | Cache miss rate across benchmarks with more than 1000 total FRAM                                                                                                                                                                                                                                                 | 71                              |

| 4.9        | accesses                                                                                                                                                                                                                                                                                                         |                                 |

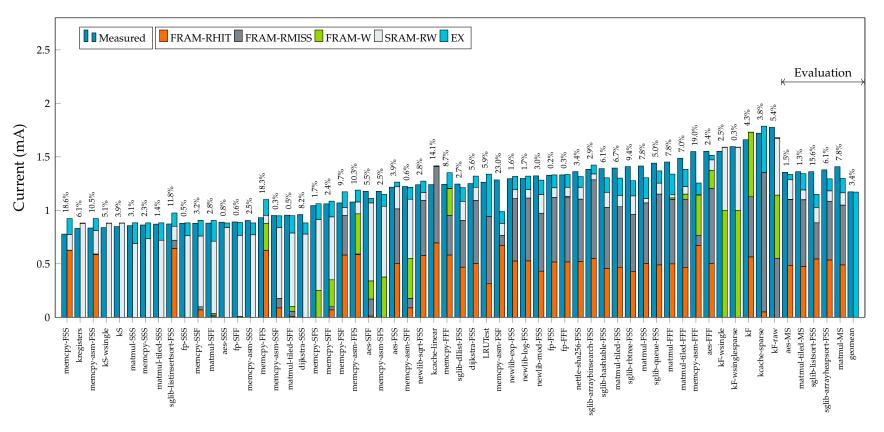

| 4.10       | Measured (left bars) and predicted (right bars) current consumption across test programs, sorted according to measured current consumption. The stacked predicted current breaks down the contributions of each feature. The number above each bar denotes the absolute percentage simulation                    | 72                              |

|            | error.                                                                                                                                                                                                                                                                                                           | 73                              |

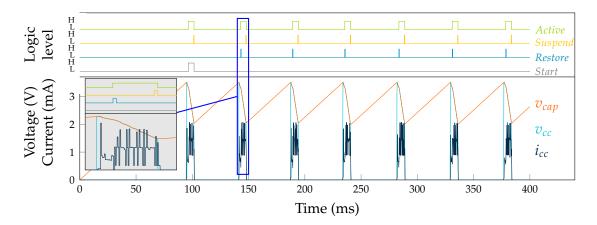

| 4.11       | Simulation trace of a reactive IC system powered by a 200 $\mu$ A current-limited power supply. The top traces show the logic levels of GPIO pins indicating the operation of the device, and the lower traces show the microcontroller supply voltage ( $v_{cc}$ ), the storage capacitor voltage ( $v_{cap}$ ) |                                 |

|            | and the current draw ( $i_{cc}$ )                                                                                                                                                                                                                                                                                | 75                              |

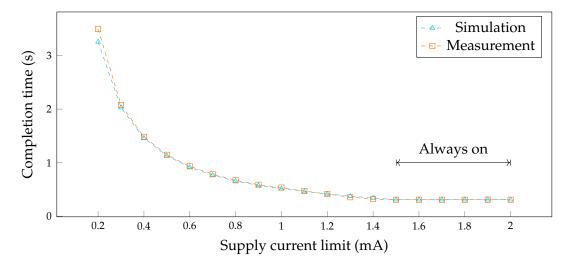

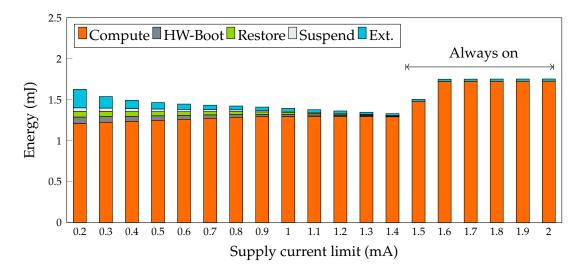

| 4.12       | Completion time of AES workload when running intermittently, pow-                                                                                                                                                                                                                                                | 75                              |

| 4.13       | ered by a current-limited power source                                                                                                                                                                                                                                                                           | <i>7</i> 5                      |

|            | and suspend                                                                                                                                                                                                                                                                                                      | 76                              |

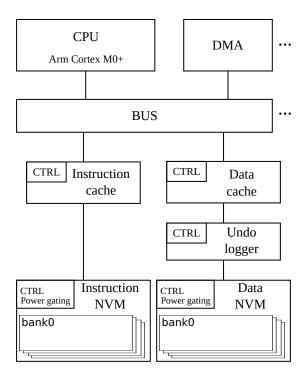

| 5.1        | Top-level architecture of MEMIC.                                                                                                                                                                                                                                                                                 | 82                              |

LIST OF FIGURES xi

| 5.2 | Overview of the <i>MEMIC</i> architecture, and data accesses during normal (undo logger disabled) and FASE execution (undo logger enabled). Annotatated steps are numbered in the order they are performed, although not all steps are performed for every memory access                                                                                                                                                                                                                                                | 83  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.3 | A simple sensor-sampling FASE showing the usage of the unsafe zone and how FASE can be annotated                                                                                                                                                                                                                                                                                                                                                                                                                        | 88  |

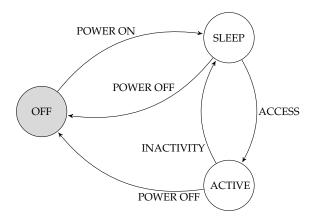

| 5.4 | State machine for power gating inactive memory banks                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 90  |

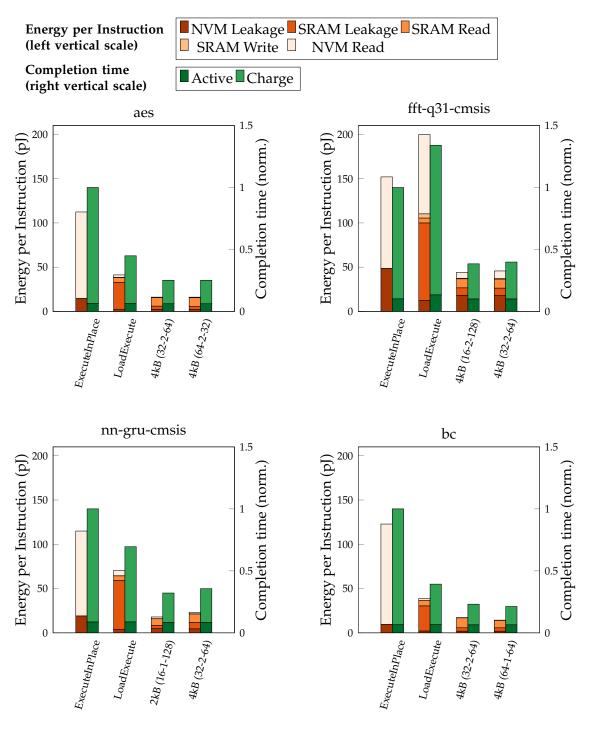

| 5.5 | Instruction access energies per executed instruction (left bars) and workload completion times (right bars, normalized to <i>ExecuteInPlace</i> ) for different instruction memory architectures. The cache configurations are                                                                                                                                                                                                                                                                                          |     |

|     | denoted as "size (Line Width-Associativity-Sets)"                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 94  |

| 5.6 | Data access energies per executed instruction (left bars) and workload completion times (right bars, normalized to <i>AllocatedState</i> ) for different data memory architectures. The cache configurations are denoted as "size (Line Width-Associativity-Sets)". Note that runtime is dependent on total power consumption, not just the component attributed to data access. Hence a large reduction in data access energy leads to a proportionally smaller reduction in total runtime. All configurations use the |     |

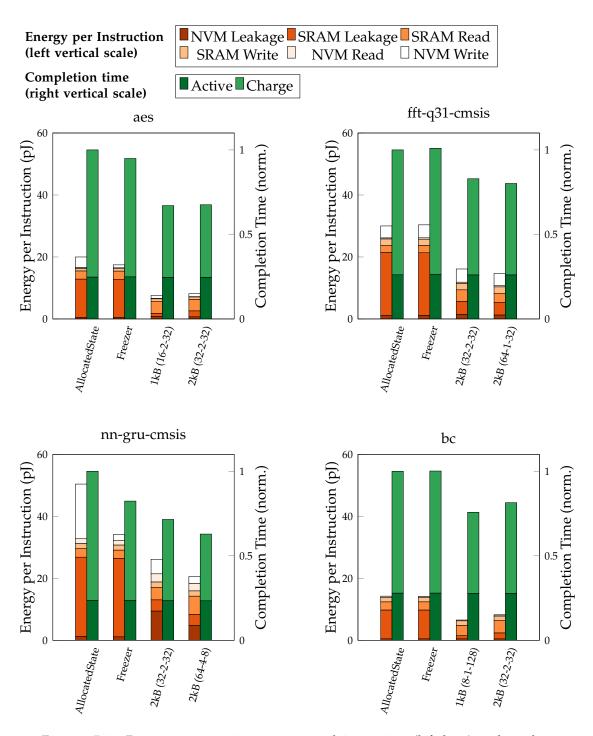

|     | 4 kB (16-2-128) instruction cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 95  |

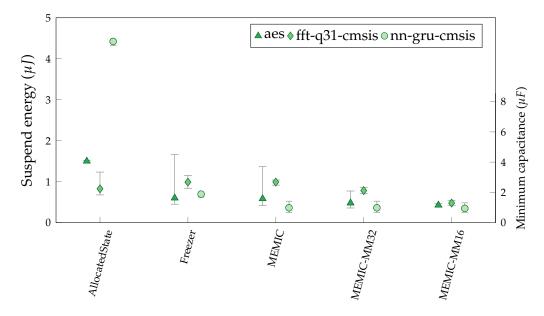

| 5.7 | Energy consumption of suspend (left vertical scale), and the corresponding minimum required capacitance (right vertical scale). The points show the mean value, and the bars show the minimum and maximum values. <i>MEMIC-MMxx</i> denotes <i>MEMIC</i> with the limit on modified lines ( <i>MOD-MAX</i> ) set to <i>xx</i> . <i>MEMIC</i> is the default configuration where <i>MODMAX</i> is                                                                                                                        |     |

|     | set to the total number of lines in the cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 98  |

| 5.8 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 100 |

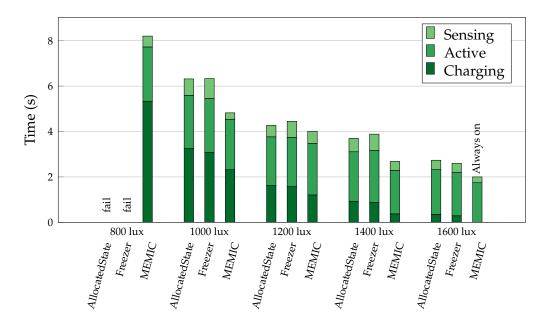

| 5.9 | Average completion time of the nn-gru-cmsis-logger workload on the solar-powered IC device (Figure 5.8) under different lighting conditions. The two baseline configurations use the same instruction cache as <i>MEMIC</i> .                                                                                                                                                                                                                                                                                           |     |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 101 |

# **List of Tables**

|            | in this thesis are highlighted in bold font                                                                                                                                                                                                                               | 12<br>22 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.1        | Overhead of ManagedState on a continuous supply when compared to AllocatedState                                                                                                                                                                                           | 49       |

| 4.1<br>4.2 | Qualitative comparison of simulation tools pertinent to IC List of names and memory footprints for workloads used in the evaluation of <i>Fused</i> . Sizes listed are in bytes. Source code for all workloads is available at https://github.com/uoS-EEC/fused-workloads | 56<br>70 |

| 5.1<br>5.2 | Simulation parameters                                                                                                                                                                                                                                                     | 89<br>91 |

| 5.3        | Completion times of all workloads for three capacitor sizes. All configurations use the 4 kB (16-2-128) instruction cache                                                                                                                                                 | 98       |

| 5.4        | MEMIC evaluated on the correctness criteria, performance goals, and scalability goals from \$2.4                                                                                                                                                                          | 102      |

# **Definitions and Abbreviations**

ADC analog to digital converter

**AES** advanced encryption standard

AMS analog and mixed signal

**API** application programmer's interface

**CMOS** complementary metal oxide semiconductor

**COTS** commercial off-the-shelf

**CPU** central processing unit

**DMA** direct memory access

**EDA** electronic design automation

**EH** energy harvesting

**ESL** electronic system level

**FASE** failure-atomic section

**FIFO** first in first out

**FRAM** ferroelectric random access memory

**FPGA** field-programmable gate-array

GDB GNU debugger

**GPIO** general purpose input/output

IC intermittent computing

**ILPM** instruction level power modelling

**IoT** internet of things

**ISA** instruction set architecture

**LFU** least frequently used

LRU least recently used

**NNLS** non-negative least squares

**NVFF** non-volatile flip flop

**NVM** non-volatile memory

**NVP** non-volatile processor

MMU memory management unit

MRAM magnetoresistive random access memory

MTJ magnetic tunnel junction

PCB printed circuit board

**OS** operating system

**PCM** phase-change memory

**PMM** power management module

**QoS** quality of service

**RAM** random access memory

RTL register transfer level

**SoC** system on chip

**SRAM** static random access memory

**STT-MRAM** spin transfer torque MRAM

**SVS** supply voltage supervisor

TDF timed data flow

TLM transaction level modeling

**UVM** unified verification methodology

VM volatile memory

## **Declaration of Authorship**

I declare that this thesis and the work presented in it is my own and has been generated by me as the result of my own original research.

#### I confirm that:

- 1. This work was done wholly or mainly while in candidature for a research degree at this University;

- 2. Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- 3. Where I have consulted the published work of others, this is always clearly attributed;

- 4. Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- 5. I have acknowledged all main sources of help;

- 6. Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- 7. Parts of this work have been published as: listed in §1.3

| Signed: | Date: |

|---------|-------|

# Chapter 1

## Introduction

The internet of things (IoT) is increasing demand for low-power computing devices to bridge between the cyber- and physical worlds with advanced monitoring capabilities [7]. These devices are beginning to be deployed in a wide variety of domains, such as smart buildings and cities, logistics, healthcare, remote surveillance, industrial automation and wearable computing [2]. However, despite widespread optimism for an IoT comprising tens of billions, or even a trillion, devices, progress has been slower than expected [39]. At such scale, computers need to be small and low-cost, with minimal environmental impact and maximal deployment lifetime. When tens of billions of connected devices are deployed<sup>1</sup>, maintenance operations such as battery replacement or replenishment become practically and economically infeasible.

To extend maintenance-free deployment lifetime without requiring increased battery capacity, devices can instead be powered by energy harvesting (EH). EH devices can extract a small amount of electrical power from ambient energy sources such as light, thermal gradients, or mechanical motion/vibration for an indefinite period of time. However, EH is typically an unstable and unpredictable power source.

To cope with the dynamics of EH, energy-neutral devices [72] buffer harvested energy in a rechargeable battery or supercapacitor, and modulate their energy consumption to match harvested energy over the periodicity of the power source (e.g. 24 h for outdoor solar). Thus they can theoretically operate indefinitely. A typical method of adjusting the power consumption is to operate at a variable duty cycle, calculated based on the amount of harvested and stored energy. During periods of abundant energy harvest, an energy-neutral device can operate at a higher performance level, i.e. at higher duty cycle or clock frequency, and it can buffer some of the extra energy to make up for periods of diminished harvest. However, even rechargeable batteries and supercapacitors

<sup>&</sup>lt;sup>1</sup>The Ericsson mobility report predicts that there will be 26 billion internet-connected devices by 2026, excluding PCs, laptops, tablets and mobile phones. Source: https://www.ericsson.com/en/mobility-report/mobility-visualizer

degrade and eventually expire after hundreds or thousands of charge cycles or years of operation, and, together with their charging circuitry, they often constitute the majority of the total cost of an IoT device.

Instead of relying on energy storage to compensate for EH dynamics, intermittent computing (IC) systems operate in an incremental manner, making progress whenever energy is available [103, 132]. They can be coupled directly to energy harvesters supplying as little as a few micro watts of power, without the use of batteries, because they retain computational progress despite frequently losing power. By enabling tiny long-life devices at low environmental and monetary cost, IC widens the application domain for IoT, thereby opening new opportunities for computation in environments that were previously too harsh and/or constrained. For example, researchers have proposed that IC can be used in micro-satellites [91], which experience potentially hundreds of kelvins of temperature variation, and where every cubic centimeter of volume counts.

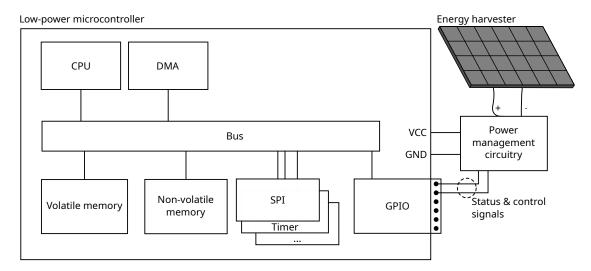

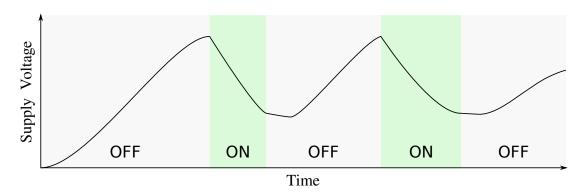

Figure 1.1 depicts a typical IC system, comprising a low-power microcontroller, an energy harvester, and some power management circuitry. The microcontroller itself typically embeds volatile memory, which has fast and energy-efficient access but loses data if power is lost, and some non-volatile memory which is usually slower and less energy efficient, but retains data through power loss. The power management circuitry can perform a wide set of functions, such as voltage conversion, voltage detection etc., based on the specifics of the IC method. The energy harvester harvests energy from ambient sources, such as e.g. solar irradiation. Figure 1.2 illustrates intermittent operation by showing a possible supply voltage trace, whereby brief on-periods of execution are interleaved with off-periods where the supply voltage recovers. The key ability of IC is to retain state so that execution can continue from where it left off after a power failure. Various methods of retaining state have been proposed, as detailed in the background chapter of this thesis. In the pioneering work by Ransford et al. [116], computational state is saved periodically in a checkpoint. When the supply recovers after a power loss, the execution then resumes from the latest checkpoint.

A recent example of an application IC system, was demonstrated by Bing et al. [16]. The application is a batteryless and wireless bicycle trip counter comprising a sensor node attached to the wheel of a bicycle. To the fork of the bike, they attached a strong magnet. The sensor node embeds a copper coil that harvests a pulse of energy every time it passes the magnet as the wheel rotates. It then sends information, , wirelessly to a battery-powered bicycle computer. The transmitted information includes analysis computed through several power cycles (revolutions of the wheel). This is a good example of the usage of IC with a system mounted in a harsh environment (on the rim of a bicycle wheel) with stringent size and weight constraints. Furthermore, there is a symbiotic relation between the variable being measured (the rotation of the wheel) and the energy harvesting method: the data is only valuable while the wheel is rotating,

FIGURE 1.1: A typical intermittent computing system comprising a low-power microcontroller, some power management circuitry, and an energy harvester.

FIGURE 1.2: Illustration of intermittent operation. The device operates during brief on-periods (typically in the order of milliseconds), until its stored energy is depleted. It then remains off until the supply voltage recovers.

and that is also the only time when energy is harvested. Other notable applications of IC includes a batteryless step-counter [118] and a batteryless *Game Boy* clone [155].

## 1.1 Research justification

Most of the IC literature diverges into either purely software-based approaches that support IC on commercial off-the-shelf (COTS) microcontrollers [9, 68, 92, 116], or custom non-volatile processors (in which volatile logic is backed up in, or replaced by, non-volatile logic)[88, 89, 95, 123, 151].

Software solutions to IC generally aim to make the best use of existing hardware by implementing various ways to retain computational progress through power cycles. Providing support for IC through software is attractive because it can enable IC on existing devices with little development cost. Among methods proposed for IC, those

based on checkpointing have the best performance [96, 97, 98], and the best compatibility with existing software [8, 9, 12, 68, 77, 98]. Early checkpointing methods saved and restored the entirety of volatile state, i.e. CPU registers and the contents of volatile memory, in every power cycle [8, 9]. A straightforward optimization of this was to instead only checkpoint the *allocated* volatile memory, comprising the regions of memory allocated for the various data sections (.data, .bss, .stack) [12, 15]. However, during short on-periods, not all allocated state is used, because only a small portion of the application is executed, so loading the entirety of allocated state during boot is inefficient. Furthermore, when saving a new checkpoint at the end of an on-period, it is wasteful to write unmodified data to non-volatile memory (NVM), especially for NVMs with high write-energy [10, 43, 84, 148]. These factors motivate research into a checkpointing method that loads variables only when they are used, and also writes to NVM only data that have changed.

Software support for IC on COTS microcontrollers can only go so far. To achieve optimal performance, hardware support for core IC operations is necessary. Although hardware changes require substantially more development effort than software changes, they have greater potential for efficiency gains. Furthermore, the envisioned use cases for IC involve very large quantities of devices over which to amortize the initial cost of developing and fabricating new hardware platforms; the marginal cost likely outweighs initial development costs.

The backbone of IC is NVM. While initial IC research used flash memory as their NVM, it was soon demonstrated that the byte-addressable and more energy-efficient ferroelectric random access memory (FRAM) was a better candidate [68, 116]. Using a more suitable NVM meant that IC devices could operate using only the energy buffered in a few micro farads of capacitance already necessary for power conditioning purposes, as opposed to requiring supercapacitors to supply the checkpointing energy [9]. Today, magnetoresistive random access memory (MRAM) and phase-change memory (PCM) are emerging as replacements for flash in advanced process nodes for microcontrollers [24]. MRAM is available from several foundries, and in some commercially available microcontrollers [18, 50]. Like FRAM, MRAM is byte-addressable, but it is also more energy-efficient and scalable to advanced process nodes. It is still, however, not as energy-efficient as static random access memory (SRAM), which has orders of magnitude lower write-energy, and a fraction of the read-energy. As such, it is clear that MRAM-enabled conventional microcontrollers still benefit from using SRAM in addition to MRAM. For microcontrollers designed for IC, combining SRAM and NVM is a complex topic with many trade-offs.

Researchers in the closely related field of non-volatile processors (NVPs) tend to incorporate NVMs using a bottom-up approach. They start with new device-level innovations and use them to build a processor that implicitly retains state through power

loss. They either replace each volatile cell (flip-flop/SRAM) with its non-volatile counterpart, or use NVM-backed cells [89, 152]. The latter technique is designed to minimize the active power of the system by essentially adding a non-volatile storage element, such as a magnetic tunnel junction (MTJ), to every volatile flip-flop and SRAMcell. Most accesses are then served from the energy-efficient volatile part of the cell, and the non-volatile part is only accessed to checkpoint and restore state. Replacing each flip-flop in the processor core with its non-volatile counterpart may be a good solution for a simple 8-bit processor, but could impose substantial design effort and power/performance/area overhead if a larger 32-bit pipelined processor, such as the Arm Cortex-M0+, were used. The idea of replacing every volatile storage element with its non-volatile, or NVM-backed, counterpart is also at odds with modern system-onchip (SoC) practices, whereby the chip is composed of multiple unmodifiable functional units (intellectual property blocks) acquired from different design companies. Additionally, fabricating irregularly distributed single memory elements may not be practical due to manufacturing process control requirements. An approach that uses specialized hardware to accommodate emerging NVMs, and uses hardware/software co-design to minimize complexity has the potential to result in a versatile IC platform that can be used with legacy software across myriad applications.

To research hardware support for IC, however, an appropriate modeling methodology is needed. The complex interactions between energy availability, energy consumption, energy management and intermittent operation complicate IC research. Industrystandard development tools and workflows typically decouple power consumption and execution. For example, register transfer level (RTL) power estimation flows first simulate execution to produce activity traces, then use the activity traces to estimate how much power was consumed. Hence, this flow assumes that execution is unaffected by power consumption. Although this flow, or slight variations of it, is common practice in IC literature, it yields incorrect results because the execution depends on energy, ultimately leading researchers in the wrong direction. In particular, the decoupled method leads towards optimizing for execution time without sufficient concern for energy consumption. Furthermore, IC is a field of research where obtaining repeatable and reproducible results from physical experiments is particularly challenging because energy harvesters, which have complex dynamics, are used as power sources. A method of modeling IC is thus an integral addition to experimentation, that will greatly improve researchers' ability to share trustworthy results and methods, ultimately accelerating the progress of IC research.

Other areas of research within the field of IC, include such topics as, for example, wireless communication under intermittent operation, cybersecurity within intermittent computing, formal verification. Because this thesis focusses on the computational aspects of IC, these related topics are only reviewed briefly, and are considered to be outside the scope of this thesis.

## 1.2 Research questions

Following from the above research justification, this thesis addresses three main research questions:

#### Q1 How can the efficiency of IC running on COTS microcontrollers be improved?

Several methods and programming models have been proposed to support IC on COTS microcontrollers. Among them, methods based on checkpointing are the most promising, due to their good performance and compatibility with existing embedded software. The current state of the art for checkpointing is to save and restore all allocated volatile memory. However, not all allocated memory is modified, or even used, in every on-period, especially not when they are short. Through answering **Q1**, this thesis addresses such inefficiencies to improve checkpointing on COTS hardware.

# Q2 How can microcontrollers targeting IC leverage energy-efficient NVM and hardware support to improve efficiency?

Software to support IC on COTS hardware can only go so far. To run IC optimally, hardware support is necessary. Furthermore, new byte-addressable and energy-efficient NVMs are emerging as low-power process nodes scale below 28 nm. Given that NVM is the backbone of IC, these have the potential to greatly improve the performance of IC devices, ultimately enabling IC to be used for a wider range of applications. However, though more energy efficient than existing technologies like flash and FRAM, emerging memories are still much less energy efficient than SRAM, and furthermore have asymmetric read and write energies. **Q2** encompasses the challenge of how best to leverage energy-efficient NVMs, organize the memory system, and provide hardware support for core IC operations in order to accommodate reliable and energy-efficient IC.

# Q3 How can new hardware and software for IC systems be developed efficiently, and their performance evaluated with a high degree of repeatability and reproducibility?

Researching both hardware and software for IC, and particularly assessing performance, is complex due to the interactions between energy availability, energy consumption and intermittent operation. Existing modeling tools are inadequate for modeling IC because they lack flexibility (RTL), accuracy (*gem5*<sup>2</sup>), and closed-loop power-performance simulation (both).

$<sup>^2</sup>$ A widely used simulation framework in the mobile, desktop, and server computing space (https://www.gem5.org)

Furthermore, the dynamics of EH make it difficult to obtain repeatable and reproducible results. A simulation method that can model the interactions correctly and ensure repeatable and reproducible results is needed.

To address this gap, i.e. **Q3**, *Fused*, a full-system simulator for energy-driven computers was presented in Chapter 4.

#### 1.3 Research contributions

This section outlines the key novel contributions reported in this thesis, addressing the aforementioned research questions. The contributions are listed in the order they are presented in the thesis, and associated publications are listed under each contribution. In addition to publishing datasets that support each article (available through eprints. soton.ac.uk), the source code has also been published (where relevant), as mentioned in each contribution.

#### 1.3.1 Taxonomy of IC methods for COTS microcontrollers

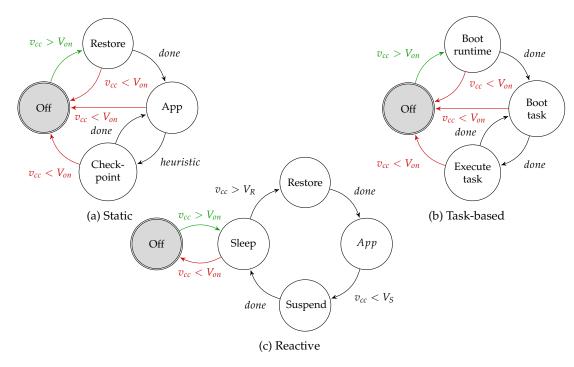

To begin addressing **Q1**, an analysis of the current state of the art for IC support on COTS hardware was needed. To this end, Chapter 2 presents a taxonomy that divides existing methods for IC into three classes, and qualitatively compares them against a set of correctness requirements, performance goals, and scalability goals. An early version of this analysis was included in the first publication listed below, and subsequently extended substantially for the second listed publication.

- S. T. Sliper, D. Balsamo, A. S. Weddell, and G. V. Merrett. "Enabling Intermittent Computing on High-Performance Out-of-Order Processors". In: *Proceedings of the 6th International Workshop on Energy Harvesting & Energy-Neutral Sensing Systems*. ENSsys '18. New York, NY, USA: ACM, 2018, pp. 19–25. ISBN: 978-1-4503-6047-0. DOI: 10.1145/3279755.3279759

- S. T. Sliper, O. Cetinkaya, A. S. Weddell, B. Al-Hashimi, and G. V. Merrett. "Energy-Driven Computing". In: *Philosophical Transactions of the Royal Society A: Mathematical, Physical and Engineering Sciences* 378.2164 (Feb. 7, 2020), p. 20190158. DOI: 10.1098/rsta.2019.0158

# 1.3.2 Paged memory management for efficient state retention on COTS microcontrollers

To complete addressing Q1, Chapter 3 proposes a software memory management layer to support IC on COTS microcontrollers. It substantially reduces time and energy spent on saving and restoring state by carefully controlling which data are loaded when restoring from a checkpoint, and written to NVM when saving checkpoints. This memory management method functionally resembles hierarchical memory, and the evaluation results indicate that hierarchical memory is warranted for IC, even though it is rarely seen in today's low-power microcontrollers (Q2). This work was published in the publication listed below, and the full source code of the method was published as an open-source project at https://github.com/UoS-EEC/ICLib.

• S. T. Sliper, D. Balsamo, N. Nikoleris, W. Wang, A. S. Weddell, and G. V. Merrett. "Efficient State Retention Through Paged Memory Management for Reactive Transient Computing". In: *Proceedings of the 56th Annual Design Automation Conference* 2019 (Las Vegas, NV, USA). DAC '19. New York, NY, USA: ACM, 2019, 26:1–26:6. ISBN: 978-1-4503-6725-7. DOI: 10.1145/3316781.3317812

#### 1.3.3 Full-system simulator for IC research

Addressing **Q3**, and facilitating research of **Q2**, a new full-system energy-driven computing simulator, named *Fused*, is proposed in Chapter 4. Unlike existing simulators, *Fused* simulates energy and execution in a closed feedback loop, and is therefore able to model the complex interactions between execution and energy (storage, management, consumption, harvesting). *Fused* enables investigation into **Q2** with the flexibility needed to explore emerging NVMs and novel hardware support for IC.

A paper describing and evaluating *Fused* has been published in the first reference listed below. *Fused* has been published to the community as an open-source project at https://github.com/UoS-EEC/Fused, and several improvements have been made since the original paper. In the second publication listed below, I assisted the first author by implementing a board-level abstraction in an effort towards simulation of a full wireless sensor node.

• S. T. Sliper, W. Wang, N. Nikoleris, A. S. Weddell, and G. V. Merrett. "Fused: Closed-Loop Performance and Energy Simulation of Embedded Systems". In: *Proceedings of the 2020 IEEE International Symposium on Performance Analysis of Systems and Software*. IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS'20). Boston, MA, USA: IEEE, Apr. 2020

• S. C. Wong, **S. T. Sliper**, W. Wang, A. S. Weddell, S. Gauthier, and G. V. Merrett. "Energy-Aware HW/SW Co-Modeling of Batteryless Wireless Sensor Nodes". In: *Proceedings of the 8th International Workshop on Energy Harvesting and Energy-Neutral Sensing Systems*. ENSsys '20. New York, NY, USA: Association for Computing Machinery, Nov. 16, 2020, pp. 57–63. ISBN: 978-1-4503-8129-1. DOI: 10. 1145/3417308.3430272

#### 1.3.4 Memory system support for efficient IC

Memory system support for IC, which provides added mechanisms and functionality to simplify or accelerate the core operations of IC, can be used to significantly improve performance. Chapter 5 presents memory system support for IC, called *MEMIC*, to address **Q2**. Motivated by results from Chapter 3, Chapter 5 explores hardware-managed instruction and data caching, to optimize the core operations of IC. Additionally, it proposes a method for limiting the volatile state, which reduces the necessary amount of energy buffering, simplifies application development and increases robustness. To support atomicity, *MEMIC* includes a hardware undo-logger that enables the capability to roll back NVM state when re-executing sections of code. *MEMIC* was modeled and evaluated using hardware-software co-design in *Fused*.

This contribution has been submitted for publication and is currently under review. The reference is listed below. To make *MEMIC* readily available to anyone, all *Fused* models, software support code, and simulation scripts associated with *MEMIC* have been published at https://github.com/UoS-EEC/MEMIC and large parts of the software developed for *MEMIC* have been up-streamed to the aforementioned *ICLib* and *Fused* repositories.

• S. T. Sliper, W. Wang, N. Nikoleris, A. S. Weddell, A. Savanth, P. Prabhat, and G. V. Merrett. "Pragmatic Memory-System Support for Intermittent Computing using Emerging Non-Volatile Memory". In: *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems* (2022). DOI: 10.1109/TCAD.2022.3168263

## 1.4 Organization

This thesis begins by providing background, review and a taxonomy of contemporary works in IC in Chapter 2. Then, to address **Q1**, Chapter 3 proposes a novel page-based memory manager that improves the efficiency of checkpointing. Before addressing **Q2**, an appropriate modeling method is needed, so **Q3** must be addressed before **Q2**. Chapter 4 addresses **Q3** by proposing *Fused*, a full-system simulator for IC. Then, in

Chapter 5, memory organization and specialization for IC is presented to address **Q3**. Finally Chapter 6 concludes the thesis and suggests topics for future work.

# **Chapter 2**

# Intermittent computing

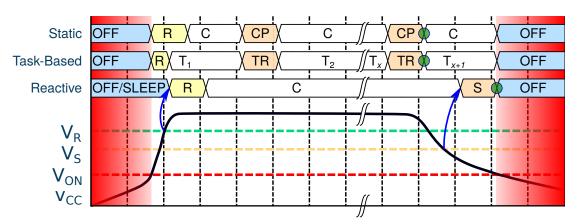

This chapter provides background and a review of current literature relating to IC. It starts by introducing the main challenges pertaining to IC by categorizing published literature (§ 2.1), then outlines application constraints for intermittent operation (§ 2.2); in essence answering the question "Which applications are amenable to intermittent operation?". Next, challenges that are particularly pertinent to this thesis are reviewed in more detail. First, bugs that may occur when re-executing code are then described in § 2.3, to motivate a set of correctness requirements that define the minimum viable IC method in the following section, § 2.4. Performance and scalability goals are then introduced; these are referenced throughout, in order to systematically compare published works. Evaluating related works against the set of requirements and goals set in § 2.4, a taxonomy of software-based IC methods is given in § 2.5. Next, § 2.6 reviews support for atomic sections in detail. Then, background on prototyping techniques for IC systems is presented in § 2.7. Finally, emerging NVM, and how it can be utilized to provide efficient IC, as well as a review of NVPs are discussed in § 2.8.

The majority of this chapter has been published as part of [130, 131, 132].

## 2.1 Challenges of IC

IC brings unique challenges that slow down adoption in the real world. This section provides an overview of published literature in field of IC, categorized into the specific challenges each work addresses, as summarized in Table 2.1. Challenges addressed by this thesis are highlighted in bold font in the table. The remainder of this section provides a brief description of each main category of challenges.

TABLE 2.1: Categorized literature on intermittent computing. Challenges addressed in this thesis are highlighted in bold font.

| Category                    | Literature                                                                                                                                                       |  |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                             | <b>Reactive IC</b> [8, 9, 12, 15, 68, 69, 117, 128, 129, 130, 148]                                                                                               |  |

| Software                    | Task-based IC [21, 25, 28, 30, 38, 46, 53] [62, 92, 96, 122, 161, 164] Static IC [4, 14, 26, 93, 97, 116, 146, 153] OS-support [12, 77] Task scheduling [73, 99] |  |

| Processor hardware          | NVP [76, 80, 88, 89, 90, 95, 123, 151, 152]<br>[42, 74, 87, 104, 107, 135, 165, 166]<br><b>HW support</b> [54, 65, 85, 108, 159, 160]                            |  |

| Energy mgmt. & optimization | [30, 40, 52, 53, 57, 60, 70, 75, 93, 110, 136, 154, 161]                                                                                                         |  |

| Timers                      | [62, 64]                                                                                                                                                         |  |

| Peripheral support          | Software [12, 19, 98, 119, 137]<br>Hardware [85]                                                                                                                 |  |

| FASE support                | [12, 98]                                                                                                                                                         |  |

| Sisyphean tasks             | [29, 98]                                                                                                                                                         |  |

| Security                    | [49, 78, 124, 140, 145]                                                                                                                                          |  |

| Reliability                 | [26]                                                                                                                                                             |  |

| Formal verification         | [11, 138, 139]                                                                                                                                                   |  |

| Approximate computing       | [46, 55, 94, 105]                                                                                                                                                |  |

| Development tools           | Simulation [45, 163] Emulation [47, 58, 121] Debugging [27] Static analysis [30, 137] Hardware prototyping [61]                                                  |  |

| Networking                  | [1, 3, 22, 31, 34, 37, 48, 79, 101, 141, 144, 162]                                                                                                               |  |

| Applications                | [16, 33, 35, 102, 106, 118, 127]                                                                                                                                 |  |

| Machine learning            | [51, 67, 81, 82, 106, 158]                                                                                                                                       |  |

**Software support.** Works relating to software to support IC on COTS microcontrollers are divided into three categories, *reactive IC*, *task-based IC* and *static IC*. These IC methodologies are detailed in § 2.5. Researchers have also worked on the challenges of operating system (OS) support and task scheduling under intermittent operation.

**Processor hardware.** In the hardware domain, the literature is categorized into NVP and hardware support for IC; where NVP involves replacing volatile logic with non-volatile alternatives, and hardware support for IC involves adding logic that improves checkpointing, peripheral support etc. By adding hardware support to improve IC to an otherwise conventional ultra low power microcontroller, instead of replacing or

augmenting all volatile logic with their non-volatile counterparts, hardware support for IC can remain compatible with conventional system on chip (SoC) design practices like combining black-box functional units ("hard IP") acquired from different IP vendors.

**Energy management (mgmt.) & optimization.** This category broadly includes works that have focused on techniques for reducing or managing energy consumption through various techniques, for example by proposing PCB-level circuits that manage energy storage in several capacitors of varying capacity.

**Timers.** Perhaps the most obvious challenge with IC is to maintain a sense of time despite power outages, a topic addressed by the works listed under *Timers*. Without power, clocks cannot run, so an IC device can usually only keep track of time within the current on-period. Recent works have proposed methods that can maintain an approximate sense of time through short off-periods by measuring the decay of a charged capacitor, or the gradual information loss in volatile memory [64], but they are far too inaccurate for e.g. synchronizing wireless communication (3.7–8.7% error over a period of 35 s). These methods may suffice in specific applications, but an IC device is generally unaware of absolute time.

**Peripheral support.** Methods for recovering peripheral state after power-loss; this is generally more complex than recovering memory and processor state, as some peripherals require an ordered and timed sequence of commands to enter certain states.

**FASE support.** A failure-atomic section (FASE) is a section of code that needs to be restarted from the beginning if it is interrupted by a power failure. *FASE support* is needed to express indivisible operations, such as radio transmissions, time-series sampling, and sampling of temporally correlated sensors. Later in this chapter, §2.3 describes bugs that may occur when re-executing arbitrary sections of code, and §2.6 describes techniques to avoid them.

Sisyphean tasks. In reference to the Greek mythological king who was condemned "to push a immense boulder up a hill only for it to roll down every time it neared the top, repeating this action for eternity" [wikipedia], a *Sisyphean task* is a FASE that requires more energy than the device can muster, hence it will be restarted indefinitely, rendering the device non-functional [115]. Using a task-based IC method involves a manual and error prone process of dividing computation into appropriately-sized tasks; this process often leads to sisyphean task. Under certain constraints, it is, however, possible to do this process automatically and with protection against sisyphean tasks [29]. To reduce the effort in sizing application-level FASEs without introducing a sisyphean task, Maeng and Lucia [98] proposed a framework to divide certain peripheral operations, such as DMA data transfer or performing computations in an accelerator, into several FASEs.

**Security.** Literature on security for IC mainly addresses encryption of checkpoints to protect secrets from an attacker that reads the contents of NVM. Reading the contents of locked on-chip NVM, however, requires physical access to the device under attack, a large time-investment, and sophisticated equipment [124]; unless checkpoints are stored off-chip, it is therefore, in the author's opinion, unlikely that encrypted checkpoints are warranted in most realistic scenarios. A more judicious approach would, in most cases, be to address access protection issues with on-chip NVM.

**Reliability.** To the author's knowledge, there is only a single published work that specifically addresses reliability. Choi et al. [26] consider degradation of ceramic capacitors due to e.g. temperature variation or cracking [142]. The characteristics of the energy buffering capacitor are critical for IC methods that depend on stored energy to save checkpoints (reactive IC), or complete tasks (task-based IC). Adapting to changes in capacitor characteristics during deployment may therefore be necessary to ensure decades of operation.

**Formal verification.** Researchers have built up a foundation for formally modeling and verifying IC, by relating intermittent and continuous execution models and forming proofs of equivalence between them (at specific points of execution) [11, 137]. These have since been used for automatic instrumentation of checkpoints and FASEs [138].

**Approximate computing.** The energy-driven nature of IC makes it a good complement for approximate computing, wherein the core idea is to produce produce high-quality results (highly accurate sensing and computation) when energy is plentiful, and lower-quality results when energy is scarce. Thus a device can utilize the energy optimally to produce the most accurate results according to the operating conditions.

**Development tools.** Because of the tight interaction between energy availability and operation, traditional development tools are insufficient for IC. Prior works have highlighted several unique challenges that emerge when researching and developing energy-driven, and particularly intermittent, computing devices [27, 59, 100]. The challenges mostly stem from the interactions between energy and execution, and from the fact that IC devices frequently reboot, thereby complicating debugging. Another issue is with repeatability of EH sources, which have complex power output dynamics that depend on their environment as well as their load. Development tools for IC are discussed further in § 2.7.1.

**Networking.** Because IC devices lack an accurate sense of time, reliably synchronizing communication between intermittent nodes is particularly challenging. Proposed solutions include exploiting external sources of synchronization, such as power grid AC signals recovered from artificial light sources [48], or using back-scatter communication [101] combined with radio-frequency energy harvesting (RF-EH).

**Applications.** Despite a decade of research into IC, only a handful of applications have been demonstrated in the literature. This may be caused by a lack of suitable development tools, and the unsolved challenges related to wireless communication under intermittent operation.

**Machine learning.** Machine learning, most often deployed in high-power data centers, may seem like an odd companion for IC, but when deployed to reduce the need for communication, it can reduce overall energy consumption. For example, *Camaroptera* [106], uses machine learning to decide which photos should be transmitted from a wildlife tracking IC device.

Among the challenges listed in this section, a few can be seen as fundamental challenges that can be mitigated, but not overcome. To answer the question "Which applications are amenable to intermittent operation?", the next section presents a set of conditions that aim to clarify which types of applications are most suitable for intermittent operation.