# UK Patent Application GB 2595239

(43) Date of A Publication

(13) A

24.11.2021

(21) Application No: 2007341.7

(22) Date of Filing: 18.05.2020

(51) INT CL:

**H03M 13/11 (2006.01)**

(71) Applicant(s):

Accelercomm Ltd

Epsilon House, Enterprise Road,

Southampton Science Park, Chilworth, Southampton,

Hampshire, SO16 7NS, United Kingdom

(56) Documents Cited:

**US 20150254130 A**

(72) Inventor(s):

Robert G Mauder

Matthew Brejza

Peter Hailes

(58) Field of Search:

INT CL **H03M, H04L**

Other: **WPI, EPODOC, Patent Fulltext, INTERNET, INSPEC, XPI3E**

(74) Agent and/or Address for Service:

Optimus Patents Limited

Peak Hill House, Steventon, BASINGSTOKE,

Hampshire, RG25 3AZ, United Kingdom

(54) Title of the Invention: **Low density parity check decoder, electronic device, and method therefor**

Abstract Title: **Low density parity check decoder, electronic device, and method thereof**

(57) An electronic device (700) is described that is configured to perform a series of low density parity check, LDPC, decoding operations (800) that use at least one basegraph (200,300) that comprises two or more columns, each column associated with a set of two or more soft bit values. The electronic device includes two or more rotators (705), each rotator (705) configured to rotate an order of a subset of two or more soft bit values of the set of two or more soft bit values of a column when activated in an LDPC decoding operation (801,802); and wherein rotations associated with each column in each basegraph are performed by a particular one of the rotators (705) of the two or more rotators (705), wherein each rotator performs rotations for a set of one or more columns, with at least one of the rotators performing rotations for two or more columns in a same basegraph.

At least one drawing originally filed was informal and the print reproduced here is taken from a later filed formal copy.

GB 2595239 A

FIG. 1

04 11 20

2/18

FIG. 2

04 11 20

3/18

FIG. 3

04 11 20

4/18

FIG. 4

04 11 20

5/18

FIG. 5

FIG. 6

04 11 20

7/18

FIG. 7

04 11 20

8/18

FIG. 8

FIG. 8 (Continued)

04 11 20

10/18

|     | 705     | 201                       | 301                |

|-----|---------|---------------------------|--------------------|

|     | Rotator | Core Column(s) of BG1     | Core Column of BG2 |

| 901 | X1      | dedicated to A1           | dedicated to A1    |

|     | X2      | dedicated to A2           | dedicated to A2    |

|     | Y1      | shared between B1 and C9  | dedicated to B1    |

|     | Y2      | shared between B2 and C2  | dedicated to B2    |

|     | Y3      | shared between B3 and C4  | dedicated to B3    |

|     | Y4      | shared between B4 and C10 | dedicated to B4    |

|     | Y5      | shared between B5 and C12 | dedicated to B5    |

|     | Y6      | shared between B6 and C5  | dedicated to B6    |

|     | Y7      | shared between B7 and C11 | dedicated to B7    |

|     | Y8      | shared between B8 and C1  | dedicated to B8    |

|     | Y9      | shared between B9 and C3  | dedicated to B9    |

|     | Y10     | shared between B10 and C6 | dedicated to B10   |

| 902 | Y11     | shared between B11 and C7 | dedicated to B11   |

|     | Y12     | shared between B12 and C8 | dedicated to B12   |

FIG. 9

| BG1 row group | BG1 rows | Comment             |

|---------------|----------|---------------------|

| 203           | A        | 0 to 3              |

| 1008          | B        | 4 to 19             |

| 1009          | C        | 20 (C1) and 21 (C2) |

|               | D        | 22 (D1) and 23 (D2) |

|               | E        | 24 (E1) and 25 (E2) |

|               | ...      | ...                 |

|               | O        | 44 (O1) and 45 (O2) |

FIG. 10

| BG2 row group | BG2 rows | Comment                  |                                     |

|---------------|----------|--------------------------|-------------------------------------|

| 303           | A        | 0 to 3                   | Core rows                           |

| 1108          | B        | 4 to 10, 13 to 16 and 19 | Non-orthogonal extension rows       |

|               | C        | 11 (C1) and 12 (C2)      | A pair of orthogonal extension rows |

|               | D        | 17 (D1) and 18 (D2)      | A pair of orthogonal extension rows |

|               | E        | 20 (E1) and 21 (E2)      | A pair of orthogonal extension rows |

| 1009          | F        | 22 (F1) and 23 (F2)      | A pair of orthogonal extension rows |

|               | G        | 24 (G1) and 25 (G2)      | A pair of orthogonal extension rows |

|               | ...      | ...                      | ...                                 |

|               | O        | 40 (O1) and 41 (O2)      | A pair of orthogonal extension rows |

FIG. 11

04 11 20

13/18

FIG. 12

FIG. 13

FIG. 13 (Continued)

04 11 20

16/18

| 704                       | 705             | 705               |

|---------------------------|-----------------|-------------------|

| 1st CN sub-processor port | Primary rotator | Alternate rotator |

| 1                         | X1              | Y5                |

| 2                         | Y2              | Y11               |

| 3                         | Y3              | Y8                |

| 4                         | Y4              | Y9                |

| 5                         | Y7              | Y1                |

| 6                         | Y10             | Y6                |

| 7                         | Y12             | X2                |

FIG. 14

04 11 20

17/18

| 704                       | 705             | 705               |

|---------------------------|-----------------|-------------------|

| 2nd CN sub-processor port | Primary rotator | Alternate rotator |

| 1                         | X2              | X1                |

| 2                         | Y1              | Y2                |

| 3                         | Y5              | Y10               |

| 4                         | Y6              | Y4                |

| 5                         | Y8              | Y12               |

| 6                         | Y9              | Y7                |

| 7                         | Y11             | Y3                |

FIG. 15

04 11 20

18/18

FIG. 16

**Title: LOW DENSITY PARITY CHECK DECODER, ELECTRONIC DEVICE, AND METHOD THEREFOR**

**Description**

5

**Field of the invention**

The field of the invention relates to a Low Density Parity Check (LDPC) decoder circuit, an electronic device, and a method for computation of LDPC decoding. The field of the invention is applicable to, but not limited to, channel coding for current and future 10 generations of communication standards.

**Background of the invention**

15 **LDPC coding**

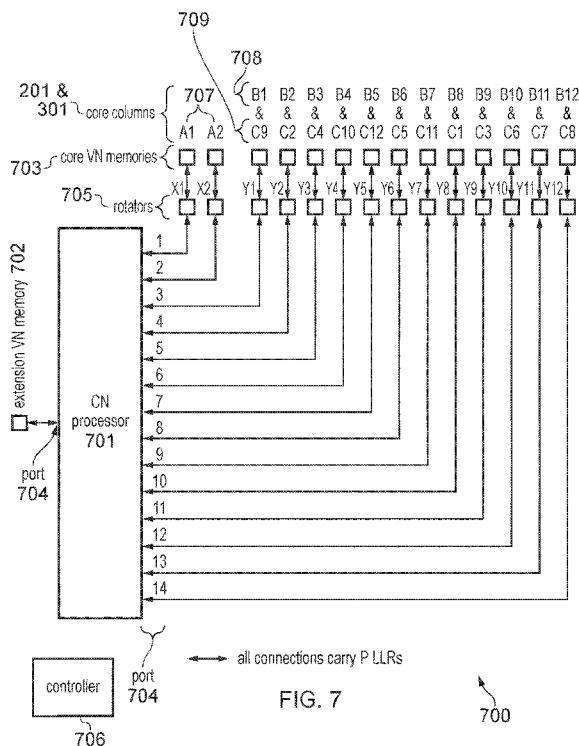

As shown in FIG. 1, a Low-Density Parity Check (LDPC) code may be used to protect data from errors that are imposed during unreliable transmission or storage. The data is typically represented by a vector comprising K data symbols, each of which can take a 20 value in the range '0' to 'M-1', where M is the radix of the code. While extensive research has been conducted on the topic of non-binary LDPC codes, with M typically adopting a value in the set {4, 8, 16, ...}, it is binary LDPC codes with M=2 that are typically adopted in practical applications. Hence, for the sake of simplicity, the remainder of this 25 background discussion assumes that the data vector 102 comprises K bits, each of which can take a value of '0' or '1'.

The known LDPC code operates using two processes, where the first comprises LDPC encoding before unreliable transmission or storage and the second comprises LDPC decoding afterwards. The LDPC encoder 103 and decoder 104 must adopt compatible 30 parameterisations, which may be specified by a Parity Check Matrix (PCM) having N' columns, N'-K rows and populated with binary values of '0' and '1'.

LDPC encoding uses the PCM  $\mathbf{H}$  to convert the vector  $\mathbf{x}$  102 of K data bits into a vector  $\mathbf{y}$  105 of N' encoded bits, where N' is greater than K. This is typically achieved by setting the 35 first K bits in the encoded bit vector (referred to as its systematic bits) equal to the K data bits of vector  $\mathbf{x}$  102, then setting the remaining N'-K bits (referred to as the parity bits), such that  $\mathbf{y} \cdot \mathbf{H} = \mathbf{0}$  in the Galois Field GF(M), where ' $\mathbf{0}$ ' is a syndrome vector comprising N'-K 0-valued bits. As understood in the field, the 'Galois Field' notation means binary with the arithmetic operation + mapping to an XOR function. Hence, it can be said that the 40 first K columns in the PCM correspond to the data bits of vector  $\mathbf{x}$  102, while the set of all columns correspond to the N encoded bits of vector  $\mathbf{y}$  105.

During unreliable storage or transmission, the vector  $\mathbf{y}$  105 of  $N'$  encoded bits is exposed to errors and is typically converted into a vector 106 of  $N'$  encoded soft bits, which express how likely each of the  $N'$  encoded bits of vector  $\mathbf{y}$  105 is to have a value of '0' or '1'. Typically, each soft bit is represented using a Logarithmic Likelihood Ratio (LLR),

5 where:

$$\text{LLR} = \ln \frac{\text{Pr}(\text{bit} = 0)}{\text{Pr}(\text{bit} = 1)}.$$

Hence for the sake of simplicity, the remainder of this background discussion assumes that all soft bits are expressed using LLRs.

10 LDPC decoding 104 may then use the PCM to convert the vector of  $N'$  encoded LLRs 106 into a vector of  $K$  decoded bits 107. Provided that the errors introduced during transmission or storage are not too severe, the  $K$  decoded bits 107 are typically a reproduction of the  $K$  data bits of vector  $\mathbf{x}$  102 that were input into the encoder 103.

## 15 The 3GPP New Radio LDPC code

Referring back to FIG. 1, illustrates a known schematic of LDPC coding and related signal processing operations in a 3<sup>rd</sup> generation partnership project (3GPP) New Radio (NR). As shown in FIG. 1, LDPC codes are adopted to protect data from transmission errors in the 20 3GPP NR standard for fifth generation (5G) mobile communications [1]. In this application, the  $K$  data bits of 102 are formed as a concatenation of three separate bit vectors, where the first vector comprises  $K'-L$  information bits 108, the second vector comprises  $L$  bits introduced by a Cyclic Redundancy Check (CRC) encoder 109 and the third vector comprises  $K-K'$  bits introduced by filler bit insertion 110. Following LDPC 25 encoding 103, rate-matching 111 is used to convert the resultant vector of  $N'$  encoded bits 105 into a vector of  $E_r$  rate-matched bits 112. Following unreliable transmission, derate-matching 113 is used to convert the vector of  $E_r$  rate-matched LLRs 114 into the vector of  $N'$  encoded LLRs 106, which are input into the LDPC decoder 104. Here, the  $N'$  encoded LLRs 106 may also include contributions from LLRs received during previous 30 transmissions in a Hybrid Automatic Repeat Request (HARQ) process and stored using a HARQ buffer 115. Following LDPC decoding, filler bit removal 116 may be used to remove the  $K-K'$  filler bits from the vector of  $K$  decoded bits 107. Then a CRC decoder 117 may be used to check the CRC within the resultant vector of  $K'$  decoded bits 118, in order to determine if any uncorrected transmission errors remain. If not, then the CRC decoder 35 can remove the  $L$  CRC bits and output the  $K'-L$  decoded information bits 119. Either way, the CRC decoder can also output a binary flag 120, to indicate whether or not the CRC check was successful.

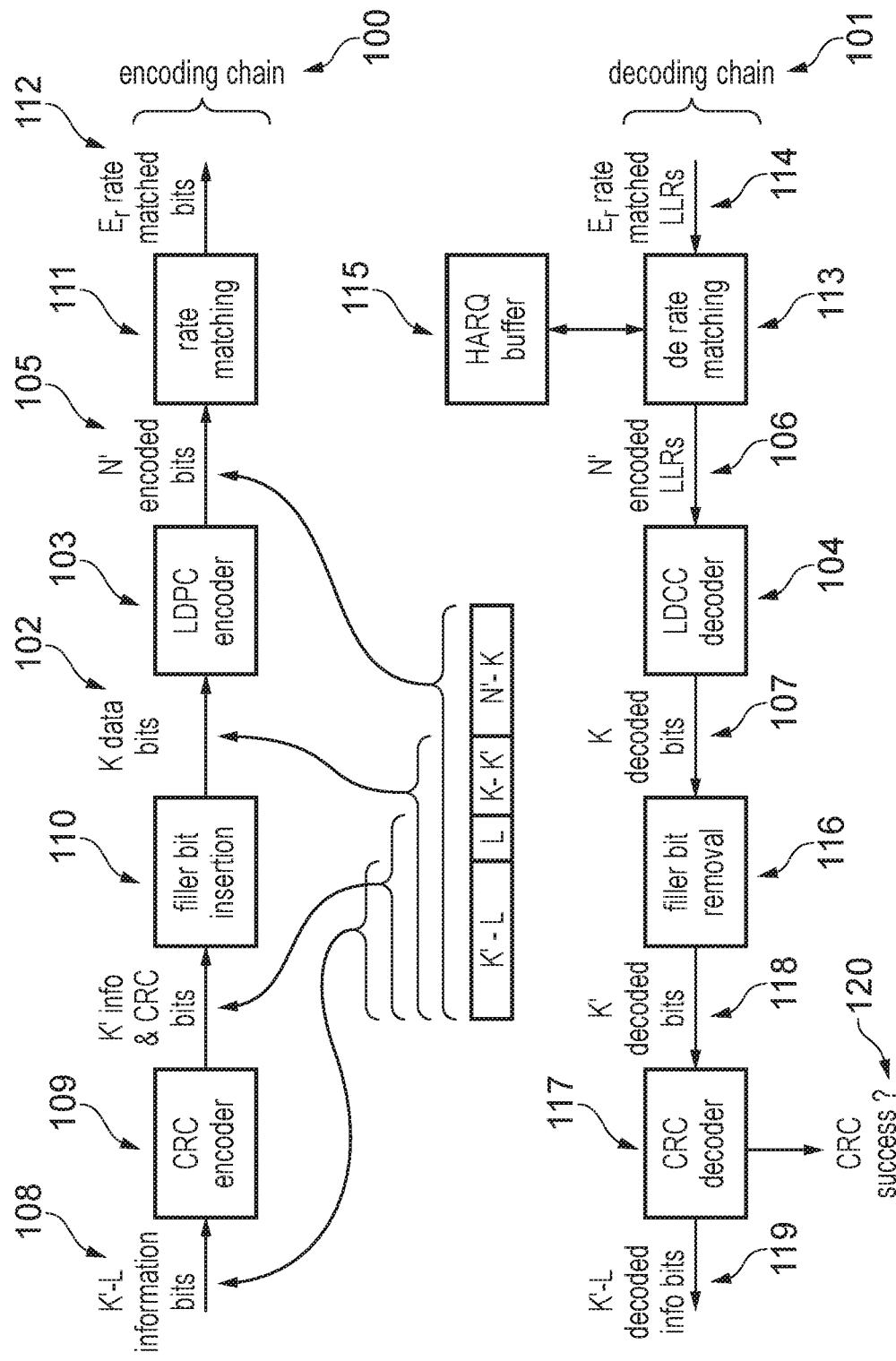

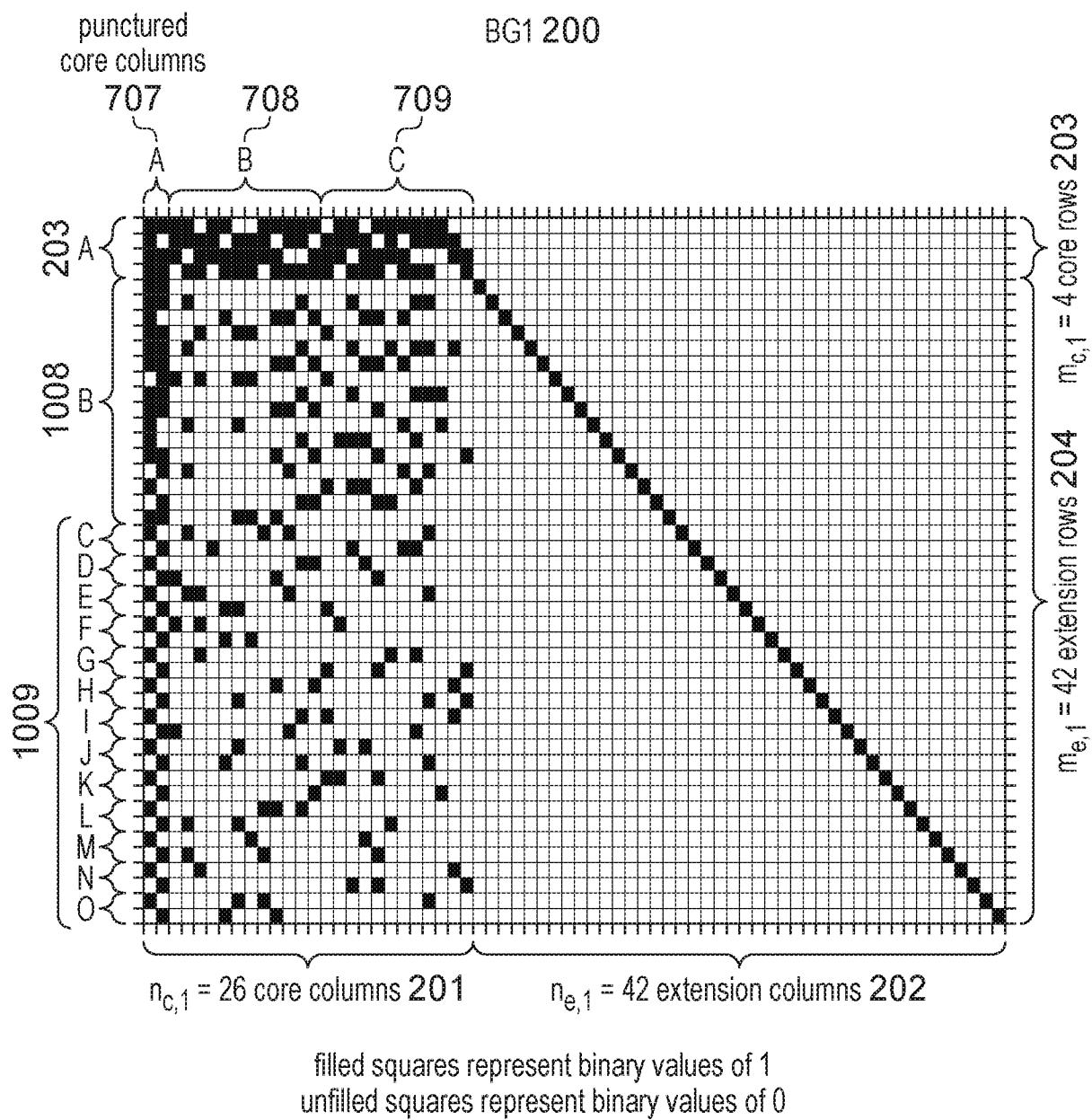

The 3GPP New Radio LDPC code is specified by PCMs that are derived from two 40 basegraphs, called BG1 200 and BG2 300, FIG. 2 and 3 illustrate known representations of BG1 200 and BG2 300 from 3GPP New Radio, respectively. Each basegraph comprises a matrix populated with binary values of '0' and '1'. BG1 200 has  $n_1=n_{c,1}+n_{e,1}=68$  columns,

which are split into  $n_{c,1}=26$  core columns 201 on the left and  $n_{e,1}=42$  extension columns 202 on the right. BG1 200 has  $m_1=m_{c,1}+n_{e,1}=46$  rows, which are split into  $m_{c,1}=4$  core rows 203 at the top and  $m_{e,1}=n_{e,1}=42$  extension rows 204 at the bottom. Meanwhile, BG2 300 has  $n_2=n_{c,2}+n_{e,2}=52$  columns, which are split into  $n_{c,2}=14$  core columns 301 on the left and 5  $n_{e,2}=38$  extension columns 302 on the right. BG2 300 has  $m_2=m_{c,2}+n_{e,2}=42$  rows, which are split into  $m_{c,2}=4$  core rows 303 at the top and  $m_{e,2}=n_{e,2}=38$  extension rows 304 at the bottom.

10 In both basegraphs, the submatrix formed by the intersection of the core columns 201 and 301, and core rows 203 and 303, is densely populated with binary values of '1'. Indeed, 19 out of the  $n_{c,1}=26$  core columns 201 have the binary value of '1' in each of the core rows 203 in BG1 200. Meanwhile, up to 10 out of the  $n_{c,2}=14$  core columns 301 in FIG. 3 have the binary value of '1' in each of the core rows 303 in BG2 300. The submatrix 15 formed by the intersection of the core columns 201 and 301 and the extension rows 204 and 304 is sparsely populated with binary values of '1', except for the first two columns that are referred to as the punctured core columns and which are densely populated with binary values of '1'. Indeed, no more than 9 out of the  $n_{c,1}=26$  core columns 201 have the binary value of '1' in any of the extension rows 204 in BG1 200. Meanwhile, no more than 20 5 out of the  $n_{c,2}=14$  core columns 301 have the binary value of '1' in any of the extension rows 304 in BG2 300.

The submatrix formed by the intersection of the extension columns 202 and 302 and the core rows 203 and 303 is completed filled with binary values of 0 in both basegraphs 200 and 300. The square submatrix formed by the intersection of the extension columns 202 25 and 302 and the extension rows 204 and 304 is mostly filled with binary values of '0', except for the elements that sit on the diagonal that runs from the top left corner of the submatrix to the bottom right corner, which adopt a binary value of '1' in both basegraphs 200 and 300. Note that, in both basegraphs, some extension rows 204 and 304 are orthogonal to one or both of their neighbouring extension rows. Here, two rows 30 (or two columns) can be considered to be orthogonal to each other if their logical AND is a vector comprising only binary values of '0'.

Note that depending on the operation of the rate-matching, some of the extension 35 columns 202 and 302 and the corresponding extension rows 204 and 304 may be deleted from the basegraph at run-time, before it is used to generate the PCM. Here, the extension row 204 and 304 that corresponds to a particular extension column 202 and 302 is the one that it shares a binary value of 1 with. This deletion reduces the number of extension columns 202 and rows 204 in BG1 200 from  $n_{e,1}$  to  $n'_{e,1}$  and reduces the 40 number of extension columns 302 and rows 304 in BG2 300 from  $n_{e,2}$  to  $n'_{e,2}$ . Hence the number of columns becomes  $n'_1=n_{c,1}+n'_{e,1}$  and  $n'_2=n_{c,2}+n'_{e,2}$ , for BG1 200 and BG2 300 respectively, while the number of rows becomes  $m'_1=m_{c,1}+n'_{e,1}$  and  $m'_2=m_{c,2}+n'_{e,2}$ , for BG1 200 and BG2 300 respectively.

The PCM used at run-time for a particular LDPC encoding and decoding process is obtained by selecting one or other of the basegraphs and lifting it using a lifting factor  $Z$ , for which 51 values of up to  $Z_{max}=384$  are supported in 3GPP New Radio. Here, each binary element in the basegraph 200 and 300 is replaced by a submatrix having dimensions of  $Z \times Z$ . Hence, each row or column in the basegraph 200 and 300 corresponds to a set of  $Z$  rows (referred to as a blockrow) or a set of  $Z$  columns (referred to as a blockcolumn) in the PCM. Furthermore, a PCM derived from BG1 200 comprises  $N=n'_1Z$  columns and  $N'-K=m'_1Z$  rows, while a PCM derived from BG2 300 comprises  $N=n'_2Z$  columns and  $N'-K=m'_2Z$  rows. In the case of BG1 200,  $K=22Z$  and the first 22 blockcolumns correspond to the data bits  $\mathbf{x} \times 102$ . Meanwhile,  $K=10Z$  in the case of BG2 300, where the first 10 blockcolumns correspond to the data bits 102. In 3GPP New Radio, the values of  $K$  and  $Z$  are selected according to a set of rules, dependent on the value of  $K'$ .

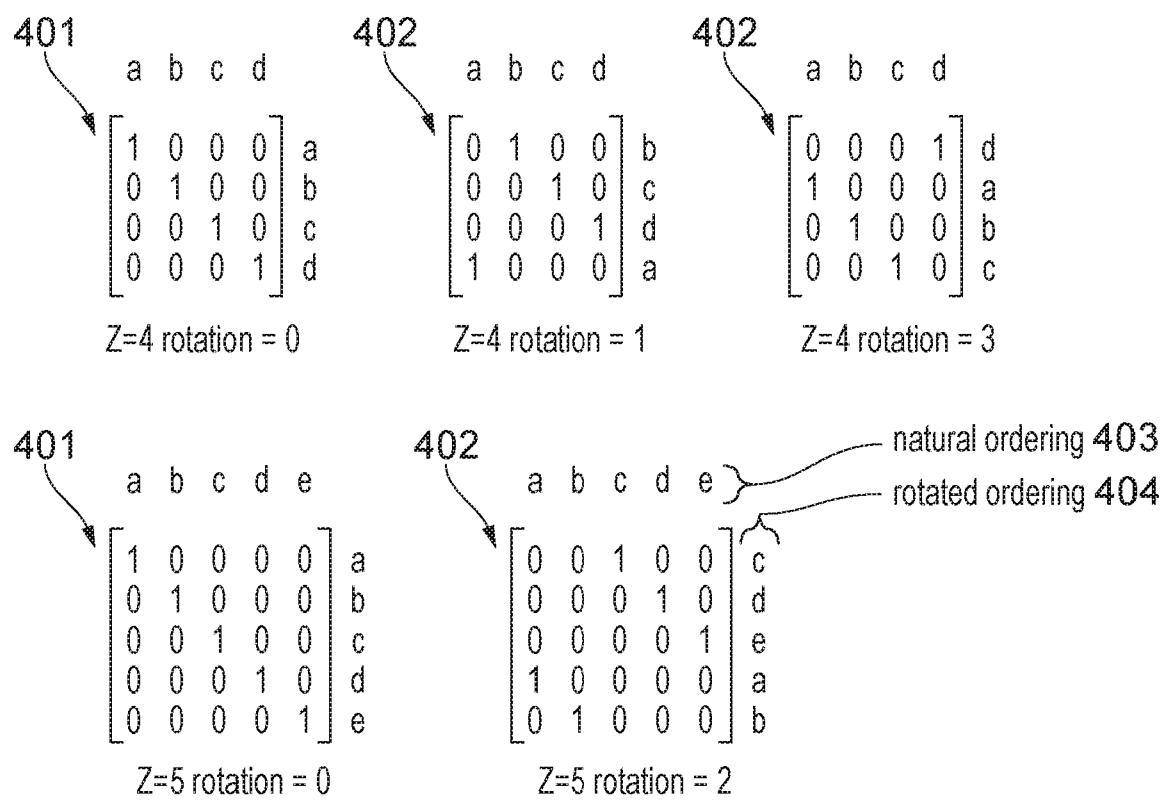

Binary elements in the basegraph having the value '0' are replaced by a  $Z \times Z$  submatrix filled with binary values of '0'. By contrast, binary elements in the basegraph having the value '1' are replaced by a submatrix in which  $Z$  elements adopt a binary value of '1' and the remaining  $Z \times (Z-1)$  elements adopt a binary value of '0'. In the extension blockcolumns, these  $Z$  1-valued binary elements are positioned on the diagonal that runs from the top left corner of the  $Z \times Z$  submatrix 401 to the bottom right corner. By contrast, in the core blockcolumns, these  $Z$  1-valued binary elements are positioned according to a circular rotation 402 of this diagonal, as illustrated in FIG. 4. More specifically, FIG. 4 illustrates a known matrix interpretation of various example rotations applied with exemplifying lifting factors  $Z$ , in order to convert between natural and rotated orderings of variables. The diagonal used for each 1-valued binary element in the core blockcolumns is rotated by a different number of positions in the range '0' to ' $Z-1$ ', dependent on the particular basegraph and value of  $Z$  selected at run-time.

### A conventional LDPC decoder implementation

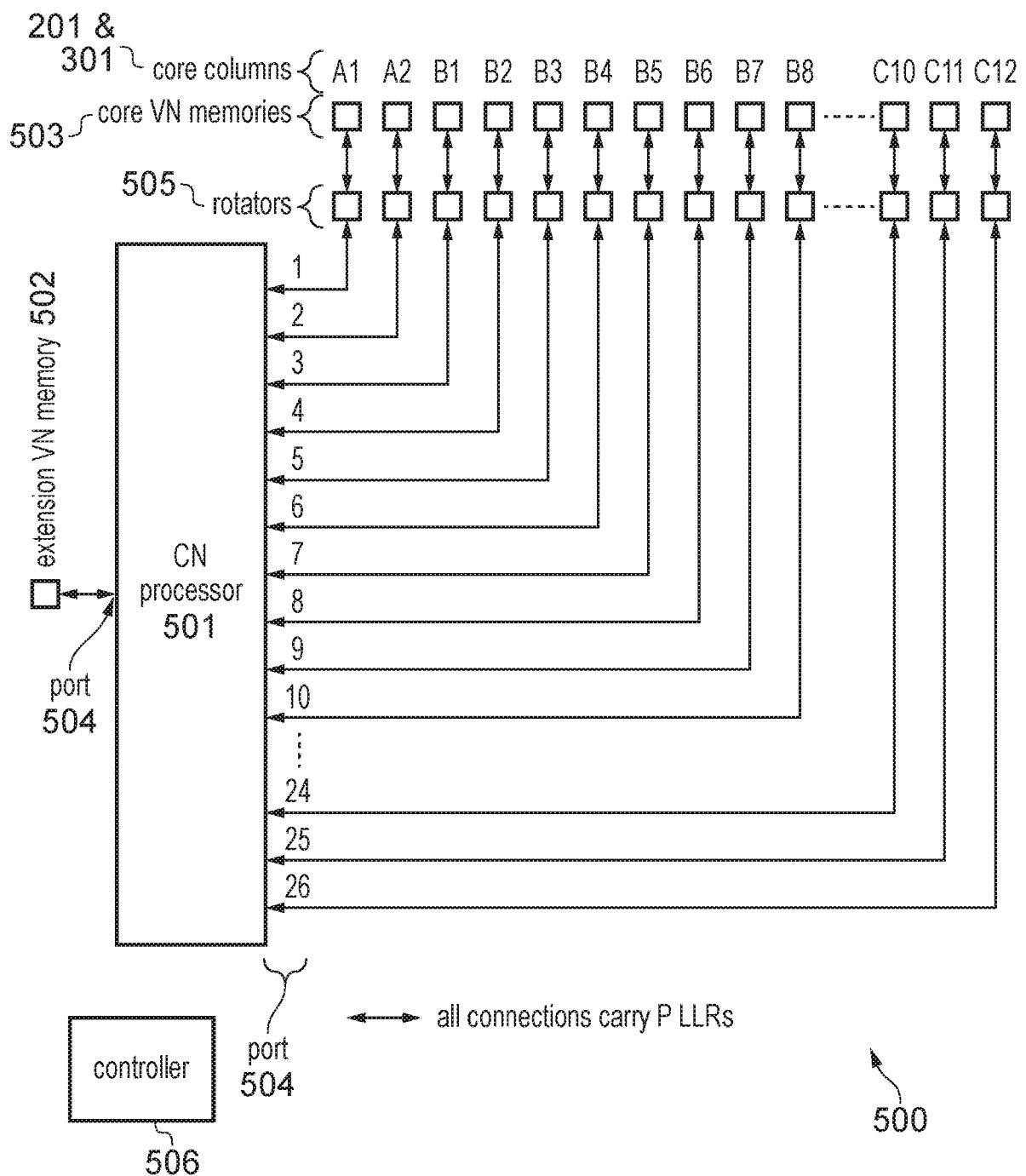

While many LDPC decoder implementations have been proposed previously, this background discussion focuses on a row-parallel layered belief propagation implementation [2], as illustrated in FIG. 5. FIG. 5 illustrates a known row-parallel layered belief propagation implementation of an LDPC decoder, with application for the 3GPP New Radio LDPC code. In general, this type of implementation can be designed to support any number of basegraphs at run-time, having any dimensions and sets of supported lifting factors  $Z$ . However, for the sake of simplicity, this background discussion considers an implementation that is specifically designed to offer run-time support for both 3GPP New Radio basegraphs and all corresponding lifting factors  $Z$ . The implementation of [2] 500 comprises  $n_{c,max}=\max(n_{c,1}, n_{c,2})$  core Variable Node (VN) memories, one extension VN memory 502,  $n_{c,max}$  rotators 505 and one Check Node (CN) processor, which are all operated under the control of a controller 506. Each of the  $n_{c,max}$  core VN memories 503 is connected to an Input-Output (I-O) port 504 of the CN

processor 501 via a corresponding one of the  $n_{c,\max}$  rotators 505. Meanwhile, the extension VN memory 502 is connected directly to an I-O port 504 of the CN processor 501. Hence, the CN processor 501 is connected to a total of  $n_{c,\max}+1$  VN memories 502 and 503, either via a corresponding rotator 505 or directly. The VN memories 502 and 503, rotators 505 and CN processor 501 may be designed to adopt a parallelism of  $P$ , such that each connection can transfer  $P$  number of LLRs at a time. Thus, different memory configurations are known.

10 Each of the  $n_{c,1}$  or  $n_{c,2}$  core blockcolumns in the PCM is mapped to a different one of the core VN memories 503 and the set of the  $n'_{e,1}$  or  $n'_{e,2}$  extension blockcolumns is mapped to the extension VN memory 502. Here, the extension VN memory 502 comprises  $n'_{e,1}$  or  $n'_{e,2}$  sub-memories, each of which is mapped to a different one of the extension blockcolumns. Note that since there is only a single binary value of '1' in each extension blockcolumn 202 and 302 respectively of the basegraph of FIG. 2 and FIG. 3. The 15 inventors of the present invention have recognised and appreciated that each sub-memory in the extension VN memory 502 is equivalently mapped to the one of the  $m'_{e,1}$  or  $m'_{e,2}$  extension blockrows that corresponds to the row of the basegraph that accommodates this binary value of '1'. The LDPC decoding process is initialised by loading each successive set of  $Z$  LLRs from the vector of  $N'$  encoded LLRs 106 into the VN memory 20 or sub-memory that corresponds to each successive blockcolumn in the PCM. Note that the LLRs loaded into the core VN memories 503 corresponding to the first two blockcolumns (which are referred to as the punctured blockcolumns) typically adopt values of 0 in the 3GPP New Radio LDPC code. Meanwhile, the LLRs that correspond to the  $K-K'$  filler bits typically adopt large positive LLR values.

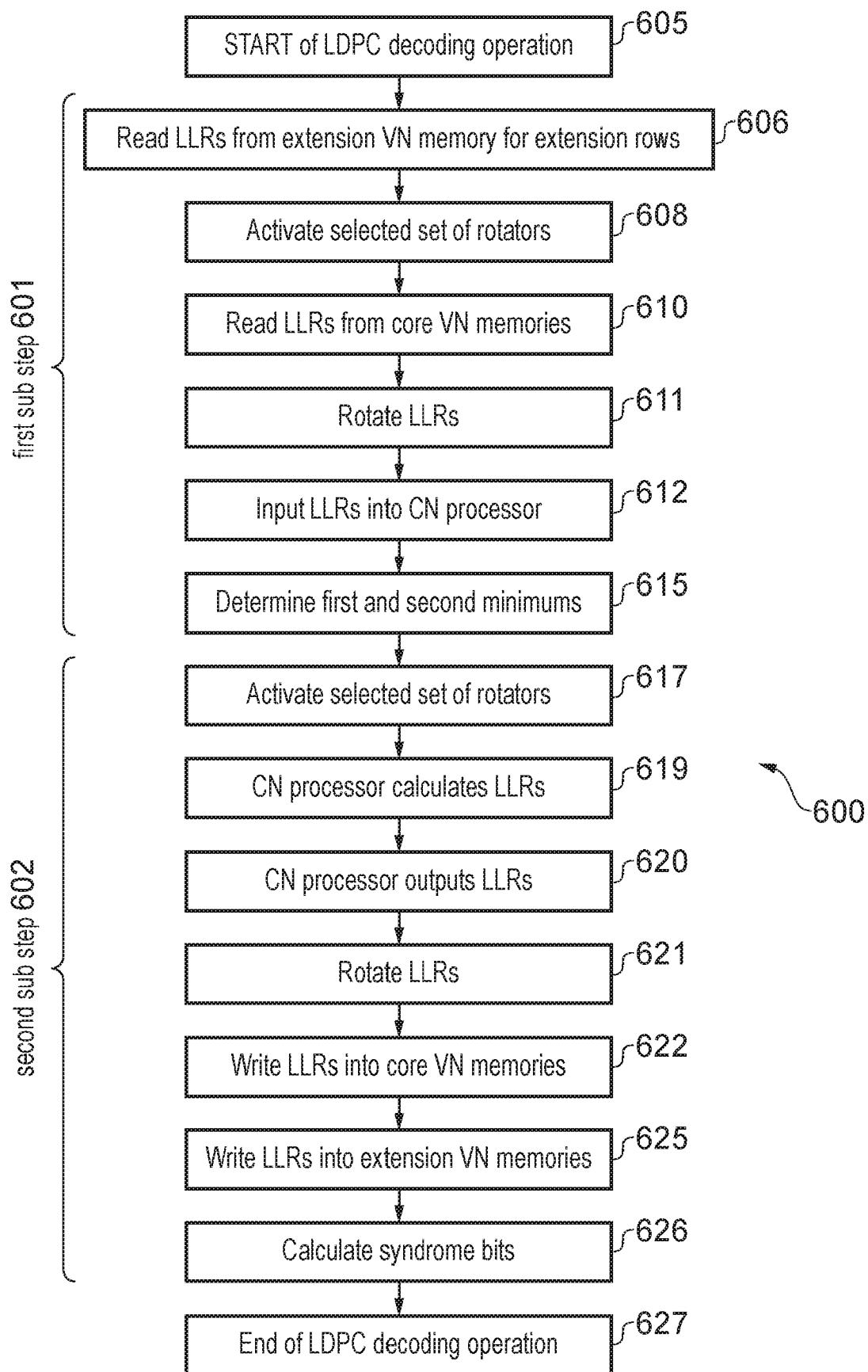

25 The conventional LDPC decoder implementation performs an LDPC decoding process using a number of iterations, where each iteration completes one pass of processing over the PCM. Each iteration is comprised of processing performed for each blockrow of the PCM, where the order in which the blockrows are processed within each iteration is 30 dictated by a layered belief propagation schedule. The processing of each blockrow of the PCM is comprised of a number of LDPC decoding operations, where each operation performs processing for a set of  $P$  rows within the blockrow and where the processing of one LDPC decoding operation is depicted in the flowchart 600 of FIG. 6. Here, FIG. 6 35 illustrates a known flow chart for the operation of a LDPC decoding process for a row-parallel layered belief propagation implementation. Each LDPC decoding operation comprises a first sub-step and a second sub-step, as shown in FIG. 6. A number of processes are performed during each sub-step and these may be spread over a number of consecutive clock cycles.

40 More specifically, the LDPC decoding process is completed over a number of operations, as illustrated in the flowchart 600 of FIG. 6. Each operation of the flowchart 600 processes LLRs associated with  $P$  rows within the same blockrow of the PCM, where these rows are typically consecutive. Typically, the complete set of rows within a

blockrow are processed during a group of  $\text{ceil}(Z/P)$  consecutive operations, with each successive operation of the flowchart 600 typically processing successive sets of  $P$  rows in order. Thus, different LLR configurations are known.

5 Furthermore, the blockrows are typically processed in an order dictated by a schedule, which may repeat the processing of some or all of the blockrows over numerous iterations. During each operation of the flowchart 600 of the LDPC decoding process shown in FIG. 6, binary values of '1' in the core columns 201 and 301 of the corresponding row of the basegraph are used to activate the associated rotators 505, 10 core VN memories 503 and CN processor I-O ports 504 of FIG. 5.

As shown in FIG. 6, each operation of the flowchart 600 commences at 605 followed by completing two sub-steps at 601 and 602, before concluding at 627. The first sub-step 15 601 comprises rotator activation at 608, VN memory reading at 606 and 610, rotation at 611, CN processor inputting at 612 and CN processor calculation at 615. The second sub-step 602 comprises rotator activation at 617, CN processor further calculation at 619, CN processor outputting at 620, rotation at 621, VN memory writing at 622 and 625, and syndrome calculation at 627.

20 During the first sub-step 601 of each operation the LDPC decoding process, each of the activated core VN memories (say core VN memories 503 in FIG. 5) are read under the direction of the controller (say controller 506 in FIG. 5), in order to provide the  $P$  LLRs that are required to complete the processing of the  $P$  rows of the PCM. Furthermore, 25 each of the activated rotators (say activated rotators 505 in FIG. 5) is configured to rotate these  $P$  LLRs into the order required to complete this processing, which is performed under the direction of the controller and according to the rotations used to convert the basegraph 200 and 300 into the PCM. Each activated rotator provides the corresponding set of  $P$  LLRs to the input of the corresponding I-O port (say I-O port 504 of the CN processor 501 in FIG. 5).

30 Furthermore, during the first sub-step 601 in each operation of the LDPC decoding process that corresponds to an extension row 204 and 304 in the basegraph, the CN processor 501 is also provided with a set of  $P$  LLRs that are read from the extension VN memory (say extension VN memory 502 in FIG. 5). More specifically, these LLRs are 35 provided by the particular sub-memory in the extension VN memory that is mapped to that extension row 204 and 304. By contrast, the extension VN memory is deactivated during the first sub-step 601 of each operation of the LDPC decoding process that corresponds to a core row 203 and 303 in the basegraph, with the result that it does not provide any LLRs to the CN processor.

40 In the manner described above, the activated subset of the connections to the inputs of the I-O ports of the CN processor each provide it with a set of  $P$  LLRs in the first sub-step 601 of each operation of the LDPC decoding process. In response to this, the CN

processor performs P sets of calculations in parallel, for the P associated rows of the PCM. This may be achieved using a variety of algorithms [3], including the sum-product, min-sum, normalised min-sum, offset min-sum or adjusted min-sum, for example. The CN processor typically employs internal memory to assist these calculations using results 5 obtained during the previous iteration of processing the P associated rows of the PCM. These results are typically overwritten with new results, which can be used to assist the next iteration of processing the P associated rows of the PCM. In the second sub-step 602 in each operation of the LDPC decoding process, and following the completion of all calculations performed by the CN processor, it may use outputs from its I-O ports to 10 provide a set of P LLRs to each of its connections that are activated in the current operation of the flowchart 600 of the LDPC decoding process.

For example, in the first sub-step 601 of an LDPC decoding process performed for a set of P rows in the PCM, the CN processor may combine P LLRs provided by inputs to each of 15 its A activated I-O ports using the min-sum algorithm. Here, we may represent the input LLRs using the notation  $a_{i,p}$  where  $i$  is in the range 1 to A and indicates which of the A activated I-O ports the LLR is provided on and  $p$  is in the range 1 to P and indicates which of the P LLRs provided on that I-O port this LLR is. In a first calculation, the CN processor may perform a calculation  $b_{i,p} = a_{i,p} - m_{i,p}$  corresponding to each input LLR  $a_{i,p}$ , where  $m_{i,p}$  20 is a corresponding internally stored value, which is initialised to '0' at the start of the LDPC decoding process and which is updated in each iteration of the processing of the P rows in the PCM. Following this, the first and second minimum of the absolute values  $|b_{i,p}|$  is identified for each value of  $p$  and the corresponding values of the index  $i$  are referred to as min1 and min2, respectively. Furthermore, the product of the signs 25  $\text{sign}(b_{i,p})$  is identified for each value of  $p$  and referred to as  $\text{sign}_p$ , where  $\text{sign}(x)$  is '+1', if  $x$  is not less than '0', and '-1' otherwise.

In the second sub-step 602, the CN processor may perform a calculation  $m_{\min1,p} = \text{sign}(b_{i,p}) \times \text{sign}_p \times |b_{\min2,p}|$  corresponding to the input LLR  $a_{i,p}$  having the index  $i$  that 30 equals min1 for each value of  $p$ . Meanwhile, a calculation  $m_{i,p} = \text{sign}(b_{i,p}) \times \text{sign}_p \times |b_{\min1,p}|$  is performed corresponding to all other input LLRs for each value of  $p$ . Here, the value of  $m_{i,p}$  is written into the internally stored value for each combination of  $i$  and  $p$ , so that it can be used during the next iteration of the processing of the P rows, as described above. Finally, the CN processor may perform a calculation  $d_{i,p} = b_{i,p} + m_{i,p}$ , in order to obtain an 35 output LLR  $d_{i,p}$  for each of the P LLRs provided as outputs on each of the A activated I-O ports, in correspondence with the input LLR  $a_{i,p}$ .

Following this, the second sub-step 602, in each operation of the LDPC decoding process, 40 proceeds with each of the activated rotators being configured to rotate the set of P LLRs that it is provided with, into an order that is appropriate for storage in the corresponding activated core VN memory. Furthermore, during the second sub-step 602 in each operation of the LDPC decoding process, the CN processor may also calculate syndrome bits corresponding to the P associated rows of the PCM. Additionally, during the second

sub-step 602 in each operation of the LDPC decoding process that corresponds to an extension row (for example 204 and 304 in the basegraphs of FIG. 2 and FIG. 3), the set of P LLRs that the CN processor provides to the extension VN memory may be written to the one of its sub-memories that is mapped to that extension row.

5

Following the completion of the decoding iterations within the LDPC decoding process, a vector of  $N'$  decoded LLRs may be obtained by concatenating the sets of  $Z$  LLRs that were most recently stored in the VN memories 502 and 503. The vector of  $K$  decoded bits 107 may then be obtained with consideration of the signs of the first  $K$  decoded LLRs, where 10 positive LLRs may be converted into the binary values of '0', while negative LLRs may be converted into binary values of '1'.

When applied to the 3GPP New Radio LDPC code, the inventors of the present invention have recognised and appreciated that a conventional LDPC decoder implementation 500 described above has a first problem, namely a large hardware requirement. This may be attributed to the requirement for  $n_{c,max}=26$  rotators 505,  $n_{c,max}=26$  core VN memories 503 and a CN processor 501 having  $n_{c,max}+1=27$  I-O ports 504. The maximum number of these rotators 505, core VN memories 503 and I-O ports 504 that are activated in any single operation 600 of an LDPC decoding process is 19, which only occurs when processing the 20 core rows 203 of BG1 200. When processing the extension rows 204 of BG1 200, the maximum number of rotators 505 and core VN memories 503 that are activated at a time is 9 and the maximum number of CN processor I-O ports 504 that are activated is 10 (including the I-O port 504 connected to the extension VN memory 502). In the case of BG2 300, there are only 14 core columns 301 and so there are 12 out of the 26 rotators 25 505, 12 out of the 26 core VN memories 503 and 12 out of the 27 I-O ports 504 of the CN processor 501 that are never activated during the processing of BG2 300. Furthermore, the maximum number of rotators 505, core VN memories 503 and CN processor I-O ports 504 that are activated at a time during the processing of BG2 300 is 10, which occurs during the processing of some core rows 303.

30

Furthermore, when applied to the 3GPP New Radio LDPC code, the inventors of the present invention have recognised and appreciated that a conventional LDPC decoder implementation 500 described above has a second problem, namely the requirement to complete a large number of decoding operations, leading to a poor throughput and 35 latency. This may be attributed to the requirement to complete one decoding operation for each set of  $P$  rows in the PCM, which is high when the PCM comprises a high number of rows. Many of these operations perform relatively little processing because some of the rows in the basegraphs have as few as 4 or 5 binary values of 1 in the core columns (201 and 301). Hence, many of the rotators 505, core VN memories 703 and CN processor 40 I-O ports 704 are disabled when processing these rows, representing wastage.

### Summary of the invention

The present invention provides LDPC decoders and methods for LDPC decoding using parallel processing, for example with reduced hardware requirement and/or reduced number of processing operations. In particular, examples of the present invention details

5 efficient mappings between hardware components and algorithmic features. Specific example embodiments of the invention are set forth in the dependent claims. These and other aspects of the invention will be apparent from, and elucidated with reference to, the example embodiments described hereinafter.

10 In a first aspect of the invention, an electronic device is configured to perform a series of low density parity check, LDPC, decoding operations that use at least one basegraph that comprises two or more columns, each column associated with a set of two or more soft bit values, the electronic device comprising: two or more rotators, each rotator configured to rotate an order of a subset of two or more soft bit values of the set of two or more soft bit

15 values of a column when activated in an LDPC decoding operation; and wherein rotations associated with each column in each basegraph are performed by a particular one of the rotators of the two or more rotators, wherein each rotator performs rotations for a set of one or more columns, with at least one of the rotators performing rotations for two or more columns in a same basegraph. In this manner, the number of rotators can be reduced,

20 leading to a hardware resource requirement reduction.

In an optional example, the electronic device may further comprise a controller, operably coupled to the two or more rotators, and configured to independently control an activation and a rotation of each of the two or more rotators based on a current LDPC decoding

25 operation and the at least one basegraph. In this manner, the control of the rotators can be centralised, leading to an increased efficiency in terms of hardware resource requirement.

30 In an optional example, the electronic device may be configured to perform the LDPC decoding operations that comprise sub-steps for a parity check matrix, PCM, of the at least one basegraph, further comprising: a check node, CN, processor operably coupled to the controller and having a plurality of input-output, I-O, ports, wherein the controller may be configured to activate a subset of the a plurality of I-O ports in each LDPC decoding operation, wherein the CN processor is configured to perform LDPC decoding

35 computations for two or more rows of the PCM derived from a single row in the at least one basegraph; and wherein each rotator is operably coupled to a corresponding I-O port of the CN processor and wherein a corresponding rotated subset of two or more soft bit values are passed between each activated rotator and its corresponding I-O port of the CN processor in each LDPC decoding sub-step. In this manner, the number of I-O ports of the

40 CN processor is reduced in accordance with the reduction in the number of rotators, leading to a simpler CN processor having a reduced hardware resource requirement.

In an optional example, the electronic device may further comprise: two or more VN memories, each VN memory configured to store sets of two or more soft bit values of the two or more columns, wherein the two or more VN memories are operably coupled to the controller that is configured to activate a read operation from and a write operation to a 5 subset of the two or more VN memories in the current LDPC decoding operation; and wherein each rotator and the set of columns for which it performs rotations is operably coupled to a corresponding VN memory of the two or more VN memories and wherein the subset of two or more soft bit values are passed between each activated rotator and its corresponding VN memory in each LDPC decoding operation. In this manner, the number 10 of VN memories is reduced in accordance with the reduction in the number of rotators, leading to a reduced hardware resource requirement.

In an optional example of the electronic device, sub-steps in each LDPC decoding operation may be grouped into a first set and a second set, and wherein in each sub-step, the 15 controller may be configured to activate a subset of the two or more rotators corresponding to a subset of the two or more columns that have a binary value of '1' in a row of the at least one basegraph. In this manner, all columns that have a binary value of '1' in a row of the at least one basegraph can be processed by the rotators over the course of one or more sub-steps.

20 In an optional example of the electronic device, in each sub-step of the first set of sub-steps of LDPC decoding operations, the VN memory corresponding to each activated rotator may be configured to provide the corresponding activated rotator with two or more soft bit values, which are read from a location in the VN memory corresponding to a column having a binary value of '1' in the row of the at least one basegraph. In this manner, all soft bits corresponding to columns that have a binary value of '1' in a row of the at least one basegraph can be processed by the rotators over the course of one or more sub-steps.

30 In an optional example of the electronic device, in each sub-step of the second set of sub-steps in the LDPC decoding operations, the CN processor may be configured to provide a corresponding subset of two or more updated soft bit values to each activated rotator using the corresponding I-O port; and each activated rotator provides its corresponding VN memory with the two or more updated soft bit values, which are written to a location in the VN memory corresponding to a column having a binary value of '1' in the row of the at 35 least one basegraph. In this manner, all soft bits corresponding to columns that have a binary value of '1' in a row of the at least one basegraph can be updated by the rotators over the course of one or more sub-steps.

40 In an optional example of the electronic device, during the first set of the LDPC decoding operations, an extension VN memory may be configured to provide two or more soft bit values to an I-O port of the CN processor when the row in the at least one basegraph is an extension row. In this manner, the LDPC decoding operation can benefit from soft-bits corresponding to extension columns.

In an optional example of the electronic device, the CN processor may be configured to determine two or more minimum values and two or more next minimum values from the two or more soft bit values provided as inputs on each of its I-O ports in each of the sub-

5 steps during the first set of sub-steps of the LDPC decoding operations and wherein the CN processor may be configured to use the two or more minimum values and two or more next minimum values to determine the two or more soft bit values provided as outputs on each of its I-O ports in each of the second sub-steps during the second set of sub-steps of the LDPC decoding operations. In this manner, the electronic device can execute LDPC

10 decoding algorithms including the min-sum, the normalised min-sum, the offset min-sum and the adjusted min-sum, over the course of one or more sub-steps.

In an optional example of the electronic device, the CN processor may be configured to perform, during the second set of sub-steps of the LDPC decoding operations, at least one

15 of: provide two or more soft bit values to an extension VN memory using one of its I-O ports when the row in the at least one basegraph is an extension row; calculate a set of two or more syndrome bits. In this manner, the electronic device can provide soft bit outputs corresponding to the extension columns in order to enable turbo-equalisation, for example. Furthermore, the syndrome bits may be exploited to perform early termination,

20 for example.

In an optional example of the electronic device, rows of the at least one basegraph having a number of core columns that is no greater than a number of rotators may be processed using the first set comprising one first sub-step and the second set comprising one second

25 sub-step. In this manner, the number of sub-steps required to execute the LDPC decoding operations is reduced.

In an optional example of the electronic device, rows of the at least one basegraph having a number of core columns that is greater than a number of rotators but having a number

30 of binary values of '1' in the core columns that is no greater than a number of rotators may be processed using the first set comprising one sub-step and the second set comprising one sub-step. In this manner, the number of sub-steps required to execute the LDPC decoding operations is reduced.

35 In an optional example of the electronic device core rows of a first basegraph of the at least one basegraph may be processed using two sub-steps in the first set and two sub-steps in the second set of sub-steps of the LDPC decoding operations, and extension rows of the first basegraph are processed using one first sub-step in the first set and one second sub-step in the second set, and all rows of a second basegraph are processed using one first

40 sub-step in the first set and one second sub-step in the second set. In this manner, the number of sub-steps required to execute the LDPC decoding operations is reduced.

In an optional example of the electronic device, the number of rotators may be fourteen, a number of core VN memories is fourteen and a number of CN processor I-O ports is fifteen. In this manner, LDPC decoding operations for the 3GPP LDPC code can be executed using a reduced hardware resource requirement.

5

In an optional example of the electronic device, the CN processor may be configured to perform at least one of: processing of each sub-step spread over one or more clock cycles; processing of successive sub-steps in a same pipelined set; processing of the first set and the second set in a same pipelined set of LDPC decoding operations; processing of successive pipelined LDPC decoding operations in a same row of the at least one basegraph; processing of successive orthogonal pipelined rows in the at least one basegraph. In this manner, the number of clock cycles required to execute the LDPC decoding operations is reduced.

15

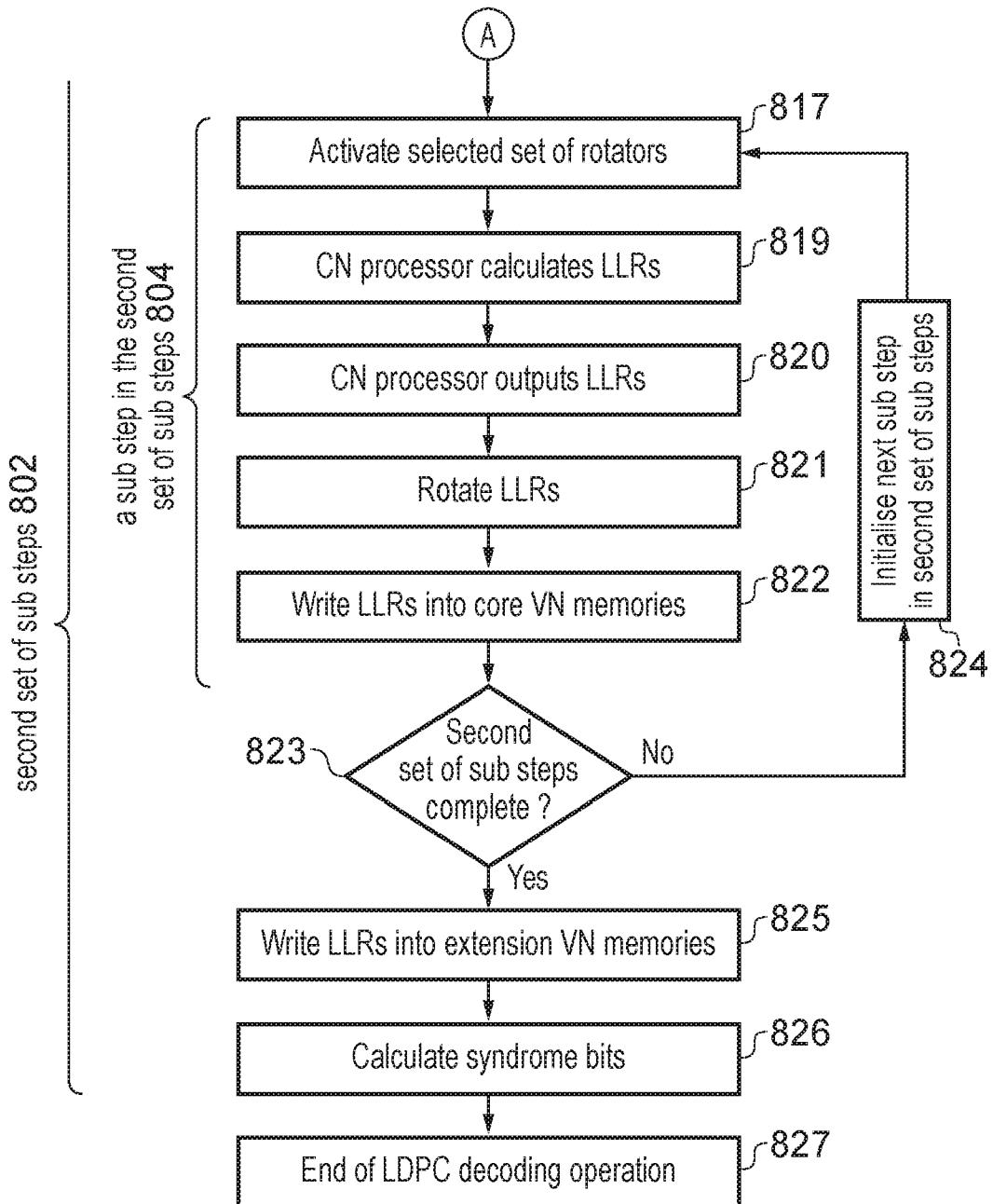

In an optional example of the electronic device, the at least one basegraph includes a plurality of rows, the electronic device comprising: a check node, CN, processor comprising two or more CN sub-processors, each CN sub-processor having one or more input/output (I-O) ports; a controller, operably coupled to the CN processor and configured to activate a subset of the one or more I-O ports based on a current LDPC decoding sub-step of the

20

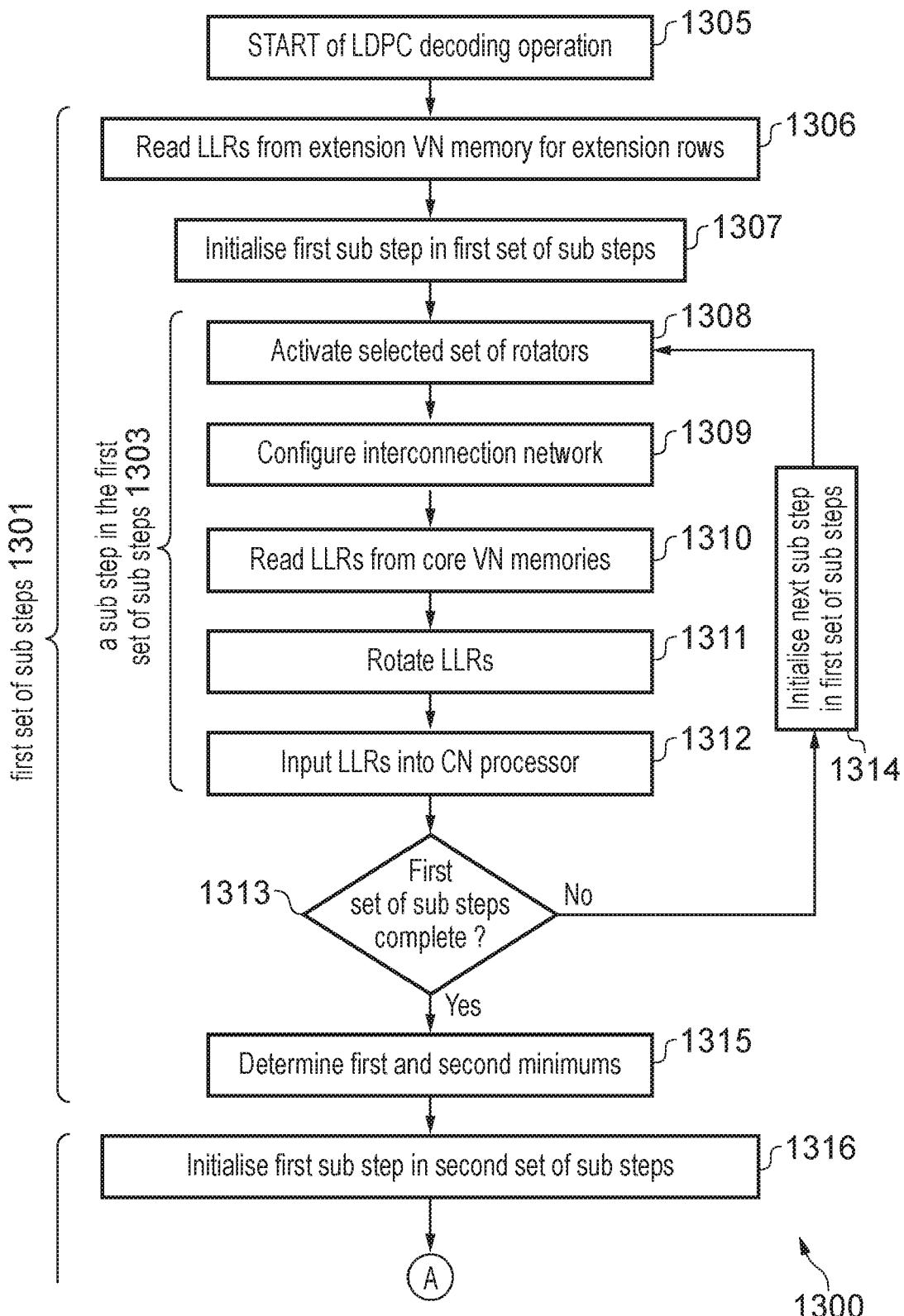

LDPC decoding operations and the at least one basegraph; and wherein the CN processor is configured to support at least two modes of operation: a first mode of operation whereby each CN sub-processor is configured in a single LDPC decoding operation to perform LDPC decoding computations for two or more rows of the PCM that are derived from different orthogonal rows of the plurality of rows in the at least one basegraph; a

25

second mode of operation whereby two or more of the CN sub-processors are configured in a single LDPC decoding operation to co-operate to perform LDPC decoding computations for two or more rows of the PCM that are derived from a single row in the at least one basegraph. In this manner, the number of LDPC decoding operations required to execute the LDPC decoding process may be reduced.

30

In an optional example of the electronic device, in the first mode of operation, the controller may be configured to allocate each row in each set of orthogonal rows in the at least one basegraph to a respective CN sub-processor. In this manner, a single LDPC decoding operation can process more than one row of a basegraph concurrently, reducing the number of LDPC decoding operations required.

35

In an optional example, the electronic device may further comprise: two or more rotators, operably coupled to the controller that is configured to independently control an activation and a rotation of each rotator and configured to rotate an order of two or more soft bit values when activated in an LDPC decoding sub-step; and an interconnection network, operably coupled to the controller and the CN processor and configured to support a connection of I-O ports of the CN sub-processors to incomplete subsets of the two or more rotators; wherein rotations of two or more soft bit values associated with each column in

40

each basegraph are performed by a particular one of the two or more rotators and wherein the controller configures the interconnection network to pass the two or more soft bit values between each activated rotator and a corresponding I-O port of a CN sub-processor in each LDPC decoding sub-step. In this manner, the hardware resource requirement of the

5 interconnection network is reduced relative to that required for a fully-connected interconnection network.

In an optional example, the electronic device may further comprise: two or more VN memories, each VN memory configured to store two or more soft bit values, wherein the

10 two or more VN memories are operably coupled to the controller that is configured to activate a read operation from and a write operation to a subset of the two or more VN memories in the current LDPC decoding sub-step; and wherein each rotator and a corresponding set of columns may be operably coupled to a corresponding VN memory of the two or more VN memories and wherein two or more soft bit values are passed between

15 each activated rotator and its corresponding VN memory in each LDPC decoding sub-step. In this manner, the complete set of soft-bits associated with core columns can be processed by the electronic device using a reduced number of LDPC decoding operations.

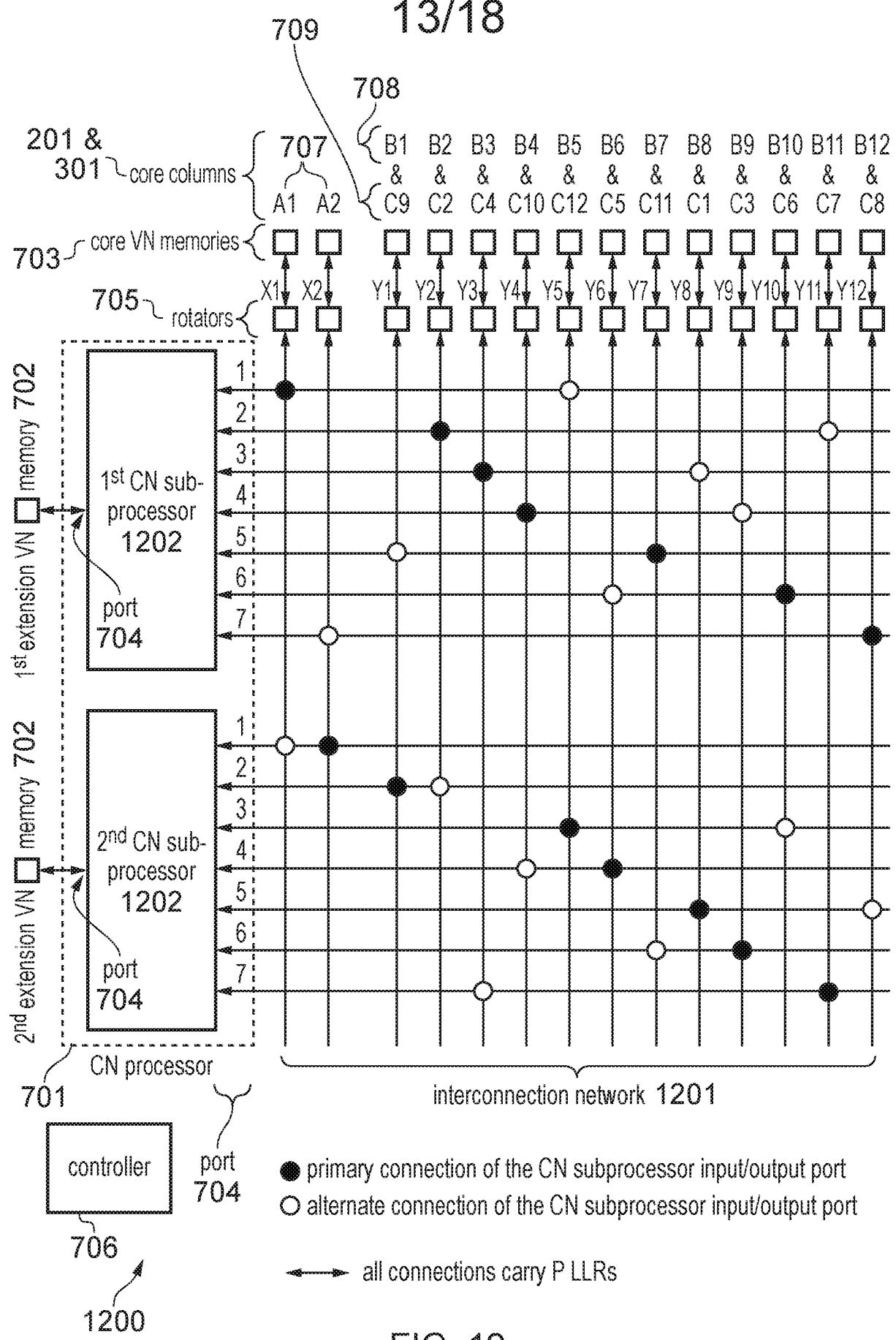

In an optional example of the electronic device, sub-steps in each LDPC decoding operation

20 may be grouped into a first set and a second set, and wherein: in each sub-step, the controller is configured to activate a subset of the two or more rotators corresponding to a subset of the two or more columns that have a binary value of '1' in the row(s) of the at least one basegraph; and activate connections within the interconnection network to connect the activated rotators to corresponding I-O ports of the CN sub-processors. In this

25 manner, all columns that have a binary value of '1' in a row of the at least one basegraph can be processed by the rotators and CN sub-processors over the course of one or more sub-steps.

In an optional example of the electronic device, in each sub-step of the first set of sub-

30 steps of the LDPC decoding operations, the VN memory corresponding to each activated rotator may be configured to provide the corresponding activated rotator with two or more soft bit values, which are read from a location in the VN memory corresponding to a column having the binary value of '1' in the rows of the selected at least one basegraph. In this manner, all soft bits corresponding to columns that have a binary value of '1' in a row

35 of the at least one basegraph can be processed by the rotators over the course of one or more sub-steps.

In an optional example of the electronic device, in each sub-step in the second set of sub-

40 steps of the LDPC decoding operations, each activated rotator may provide its corresponding VN memory with two or more updated soft bit values, which are written to a location in the VN memory corresponding to a column having a binary value of '1' in the row(s) of the at least one basegraph. In this manner, all soft bits corresponding to columns

that have a binary value of '1' in a row of the at least one basegraph can be updated by the rotators over the course of one or more sub-steps.

5 In an optional example of the electronic device, in the first set of the LDPC decoding operations, an extension VN memory may be configured to provide two or more soft bit values to an I-O port of a CN sub-processor for each of the rows that are extension rows in the at least one basegraph. In this manner, the LDPC decoding operation can benefit from soft-bits corresponding to extension columns.

10 In an optional example of the electronic device, each activated CN sub-processor may be configured to determine two or more minimum values and two or more next minimum values from the two or more soft bit values provided as inputs on each of its I-O ports in each of the sub-steps during the first set of sub-steps of the LDPC decoding operations and wherein the CN processor supports at least the following two modes of operation: in the 15 first mode of operation, each activated CN sub-processor may be configured to use its two or more minimum values and two or more next minimum values to determine the two or more soft bit values to output on an I-O port in each of the sub-steps during the second set; in the second mode of operation, each activated CN sub-processor may be configured to use its two or more minimum values and two or more next minimum values and two or 20 more minimum values and two or more next minimum values provided by at least one other activated CN sub-processor to determine the two or more soft bit values to output on each of I-O port in each of the sub-steps during the second set. In this manner, a common hardware resource for CN processing can be reused for both modes of operation, reducing the associated hardware resource requirement.

25 In an optional example of the electronic device, during the second set, an activated CN sub-processor may be configured to perform at least one of: output two or more soft bit values to an extension VN memory using an I-O ports when the corresponding row in the at least one basegraph is an extension row; calculate a set of two or more syndrome bits. In this 30 manner, the electronic device can provide soft bit outputs corresponding to the extension columns in order to enable turbo-equalisation, for example. Furthermore, the syndrome bits may be exploited to perform early termination, for example.

35 In an optional example of the electronic device, the CN processor may comprise two CN sub-processors and wherein the interconnection network supports the connection of each I-O port of the CN sub-processors to two rotators. In this manner, LDPC decoding operations for the 3GPP LDPC code can be executed using a reduced hardware resource requirement.

40 In an optional example of the electronic device, each CN sub-processor may have seven I-O ports connected via the interconnection network to the two or more rotators. In this manner, LDPC decoding operations for the 3GPP LDPC code can be executed using a reduced hardware resource requirement.

In an optional example of the electronic device, the interconnection network connects each of its connected CN sub-processor I-O ports to a primary one of the two or more rotators whenever operating in the second mode of operation. In this manner, LDPC

5 decoding operations for the 3GPP LDPC code can be executed using a reduced hardware resource requirement.

In an optional example of the electronic device, the CN processor may be configured to perform at least one of: processing of each sub-step spread over one or more clock cycles;

10 processing of successive sub-steps in a same pipelined set of sub-steps; processing of the first set and the second set in a same pipelined set of LDPC decoding operations; processing of successive pipelined set of LDPC decoding operations in a same row of the at least one basegraph. In this manner, the number of clock cycles required to execute the LDPC decoding operations is reduced.

15

In a second aspect of the invention, a method for LDPC decoding in an electronic device comprises: performing a series of low density parity check, LDPC, decoding operations that use at least one basegraph that comprises two or more columns, each column associated with a set of two or more soft bit values; rotating an order of a subset of two or more soft

20 bit values of the set of two or more soft bit values of a column when activated in an LDPC decoding operation, wherein rotations associated with each column in each basegraph are performed by a particular one of the rotators of the two or more rotators, wherein each rotator performs rotations for a set of one or more columns, with at least one of the rotators performing rotations for two or more columns in a same basegraph.

25

### Brief description of the drawings

Further details, aspects and embodiments of the invention will be described, by way of example only, with reference to the drawings. In the drawings, like reference numbers are

30 used to identify like or functionally similar elements. Elements in the FIG's are illustrated for simplicity and clarity and have not necessarily been drawn to scale.

FIG. 1 illustrates a known schematic of LDPC coding and related signal processing operations in 3GPP New Radio.

35

FIG. 2 illustrates a known representation of BG1 from 3GPP New Radio.

FIG. 3 illustrates a known representation of BG2 from 3GPP New Radio.

40 FIG. 4 illustrates a known matrix interpretation of various example rotations applied with exemplifying lifting factors Z, in order to convert between natural and rotated orderings of variables.

FIG. 5 illustrates a known row-parallel layered belief propagation implementation of an LDPC decoder, with application for the 3GPP New Radio LDPC code.

FIG. 6 illustrates a known flow chart for the operation of a LDPC decoding process for a

5 row-parallel layered belief propagation implementation.

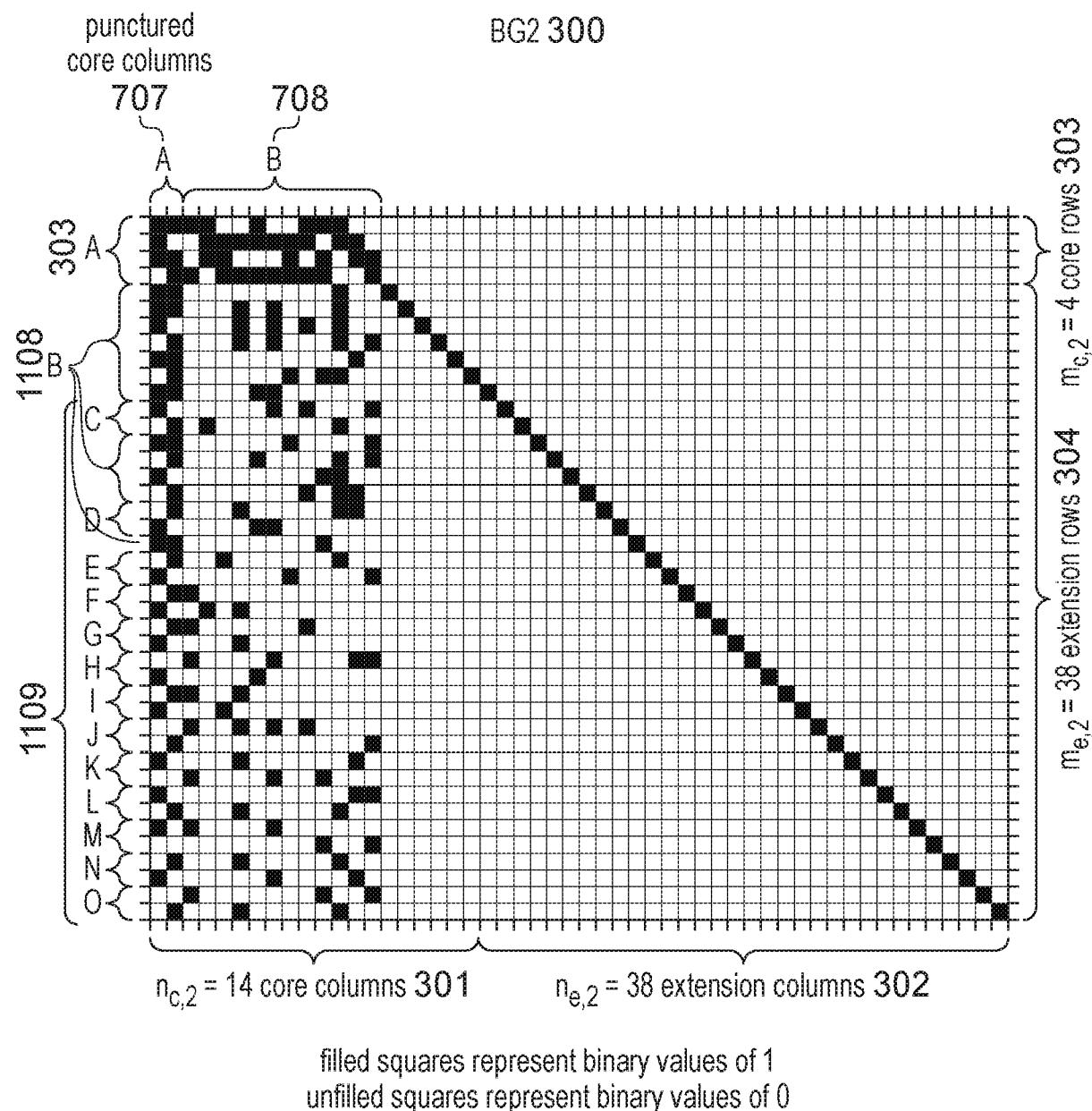

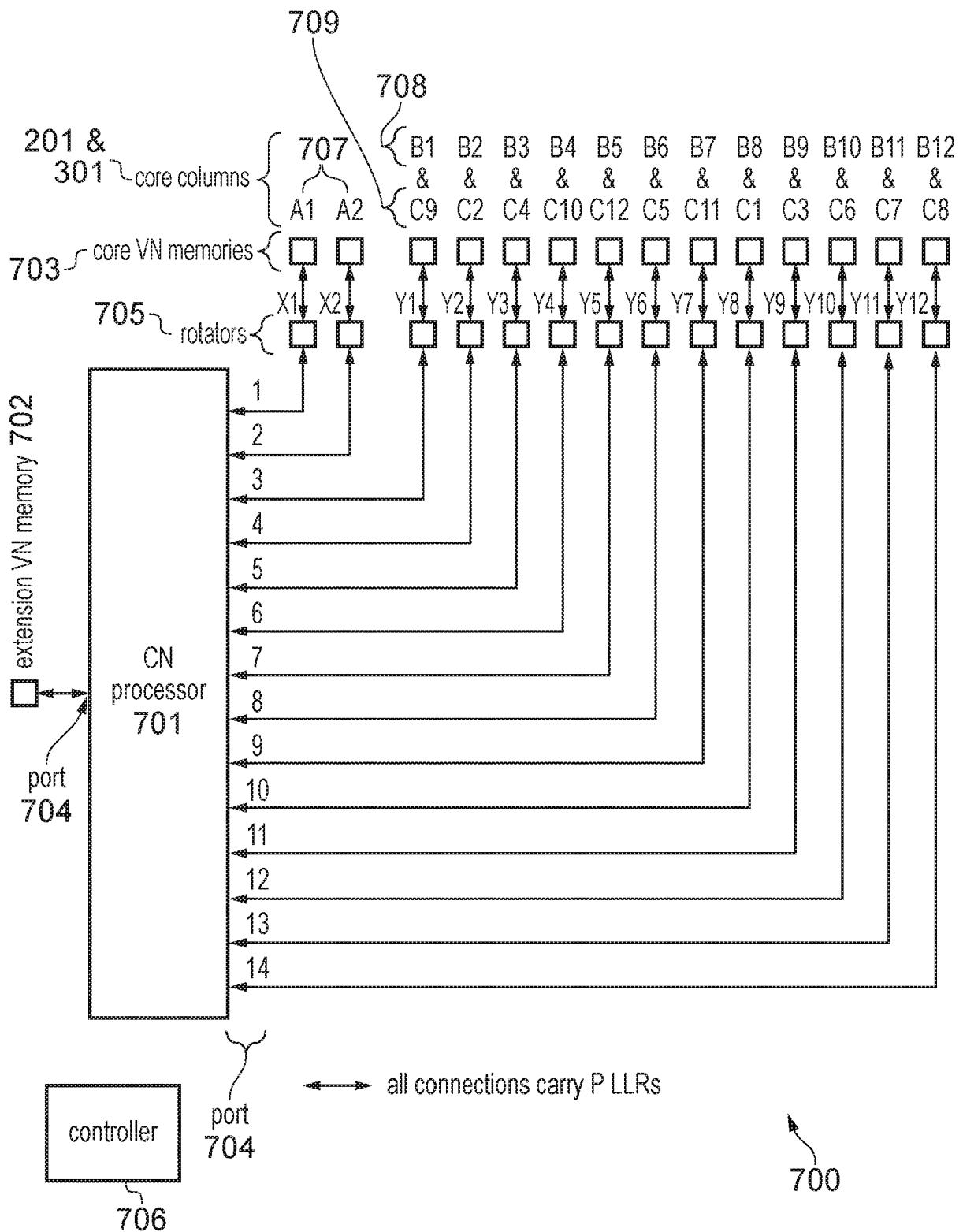

FIG. 7 illustrates an example embodiment of a LDPC decoder according to some examples of the invention, having a reduced hardware requirement, with application for the 3GPP New Radio LDPC code.

10

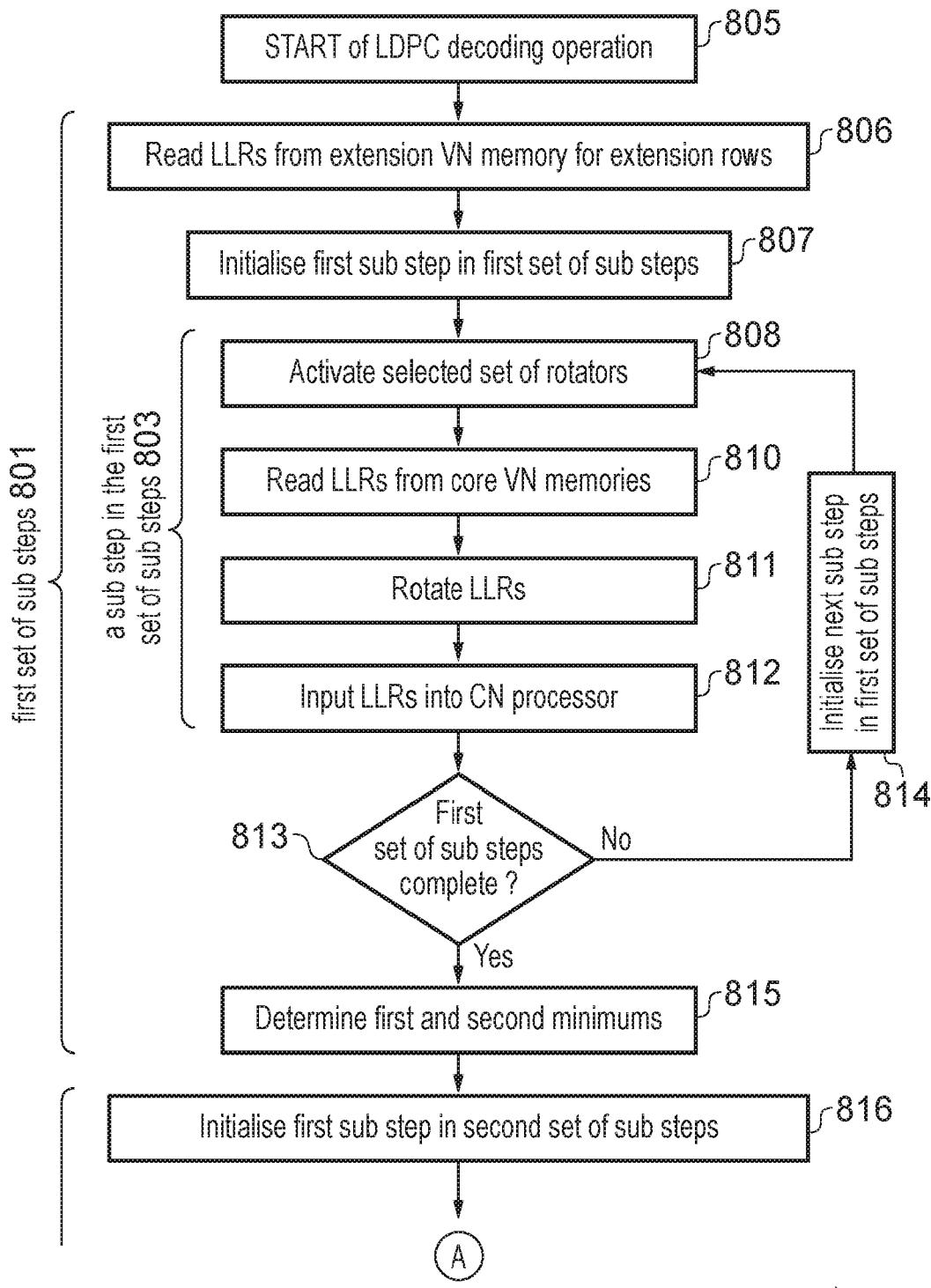

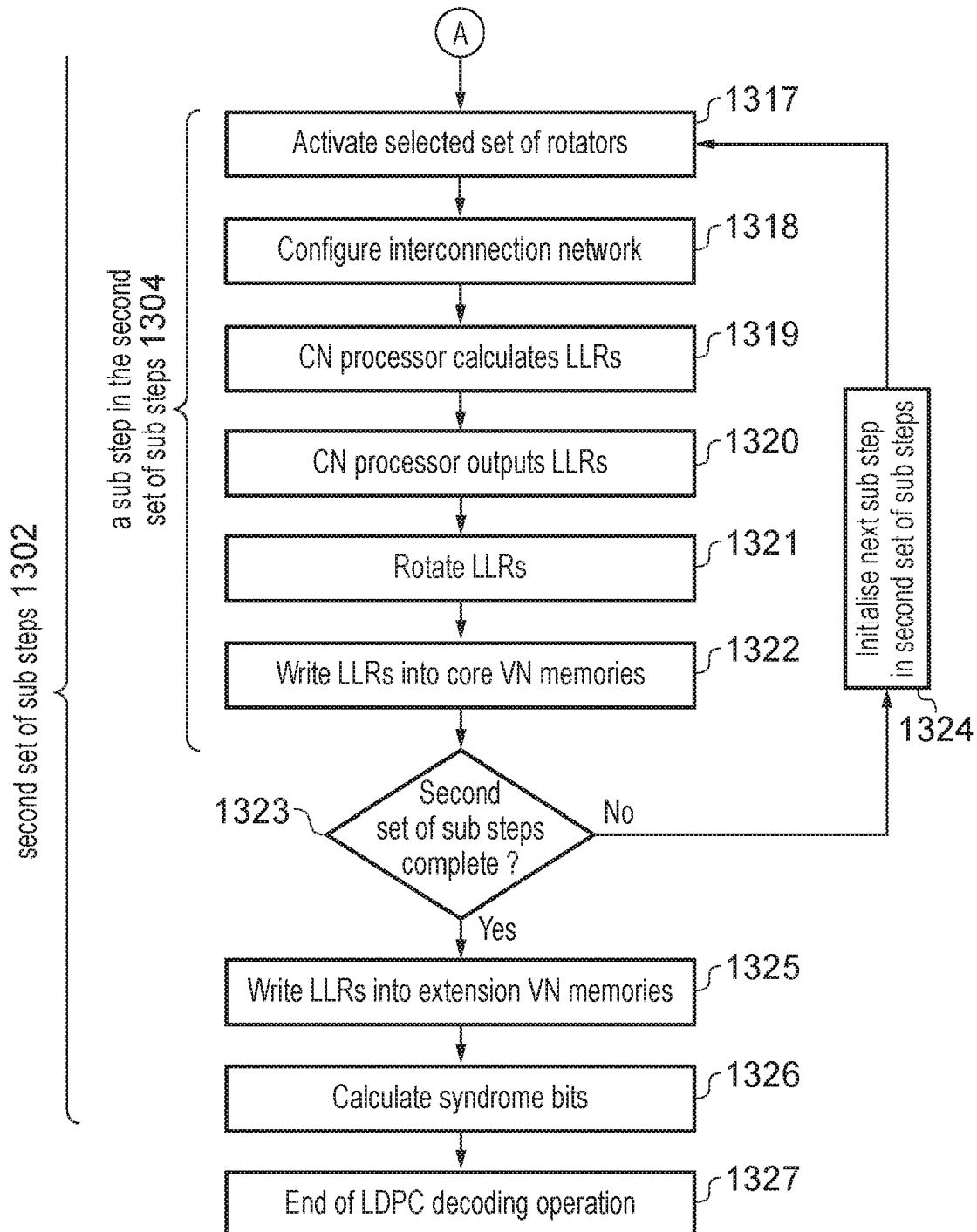

FIG. 8 illustrates a flow chart for the operation of a LDPC decoding process for an example embodiment of the LDPC decoder having a reduced hardware requirement, according to some examples of the invention.

15

FIG. 9 illustrates a mapping between rotators and core columns of BG1 and BG2 from the 3GPP New Radio LDPC code, for an example embodiment of the LDPC decoder according to some examples of the invention.

20

FIG. 10 illustrates a grouping of rows in BG1 from the 3GPP New Radio LDPC code, for an example embodiment of the LDPC decoder according to some examples of the invention having a reduced hardware requirement and reduced number of LDPC decoding operations.

25

FIG. 11 illustrates a grouping of rows in BG2 from the 3GPP New Radio LDPC code, for an example embodiment of the LDPC decoder according to some examples of the invention having a reduced hardware requirement and reduced number of LDPC decoding operations.

30

FIG. 12 illustrates a further example embodiment of the LDPC decoder according to some examples of the invention having a reduced hardware requirement and reduced number of LDPC decoding operations, with application for the 3GPP New Radio LDPC code.

35

FIG. 13 illustrates a further flow chart for an operation of a LDPC decoding process for an example embodiment of the LDPC decoder according to some examples of the invention having a reduced hardware requirement and reduced number of LDPC decoding operations.

40

FIG. 14 illustrates a mapping between ports of a first Check Node (CN) sub-processor and rotators for an example embodiment of the LDPC decoder according to some examples of the invention having a reduced hardware requirement and reduced number of LDPC decoding operations, with application for the 3GPP New Radio LDPC code.

FIG. 15 illustrates a mapping between ports of a second CN sub-processor and rotators for an example embodiment of the LDPC decoder according to some examples of the invention having a reduced hardware requirement and reduced number of LDPC decoding operations, with application for the 3GPP New Radio LDPC code.

5

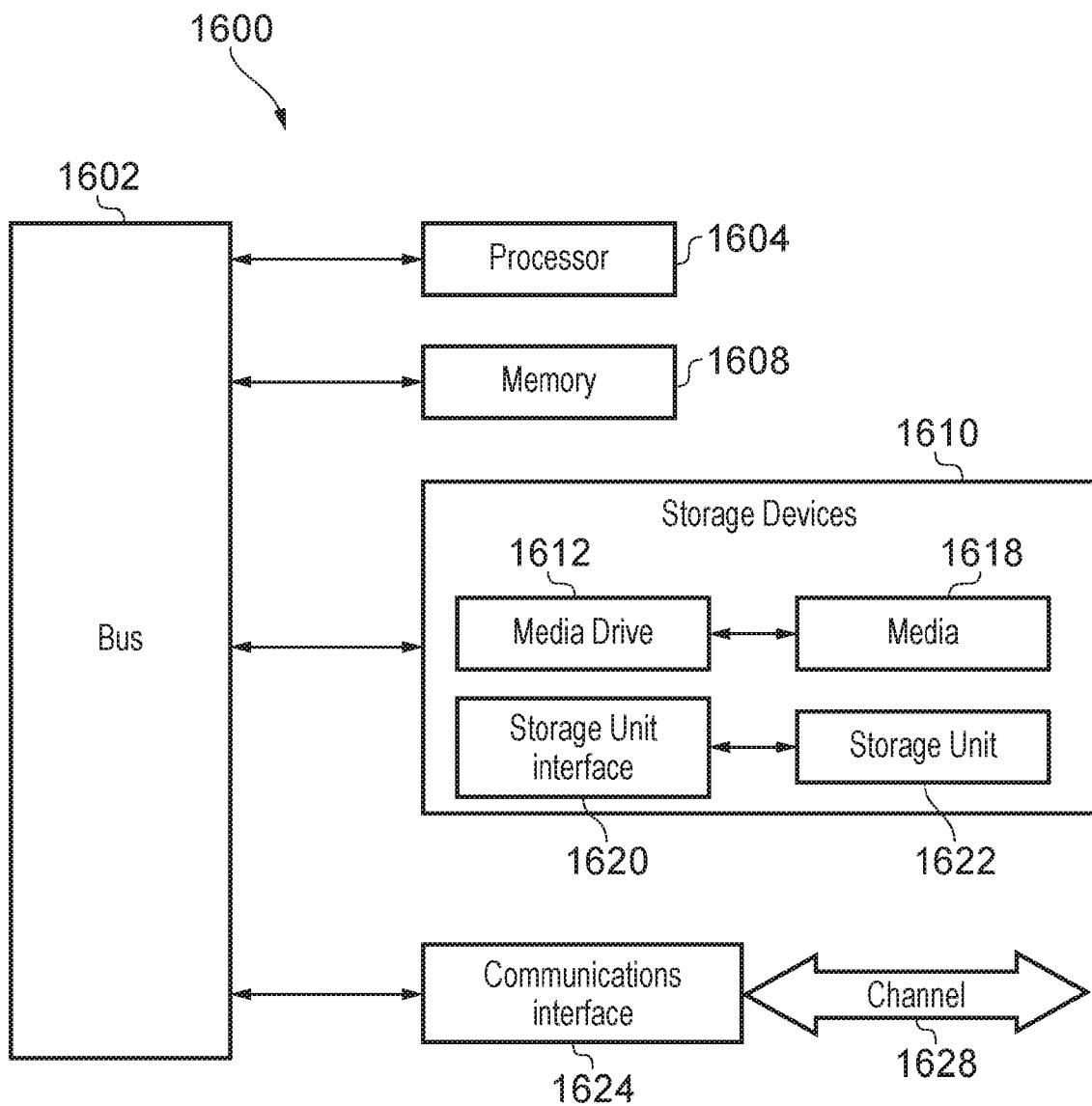

FIG. 16 illustrates a typical computing system that may be employed in an electronic device such as a wireless communication unit to perform LDPC decoding in accordance with some example embodiments of the invention.

10

### Detailed description

#### **An enhanced and generalized LDPC decoder implementation**

15 In some examples of the invention, the inventors have proposed a Low-Density Parity Check (LDPC) code that may be used to protect data from errors that are imposed during unreliable transmission or storage. The data is typically represented by a vector comprising K data symbols, each of which can take a value in the range '0' to 'M-1', where M is the radix of the code. While extensive research has been conducted on the

20 topic of non-binary LDPC codes, with M typically adopting a value in the set {4, 8, 16, ...}, it is binary LDPC codes with M=2 that are typically adopted in practical applications. Hence, for the sake of simplicity, the remainder of this document assumes that the data vector (e.g. data vector 102 from FIG. 1) comprises K bits, each of which can take a value of '0' or '1'. However, it is envisaged for the appreciation of those skilled in the relevant

25 art that the concepts described herein may be also applied to non-binary LDPC codes.

Therefore, in accordance with the inventive concepts described herein, an LDPC encoder converts the data vector comprising K bits into a vector  $\mathbf{y}$  (e.g. vector  $\mathbf{y}$  105 from FIG. 1) of  $N'$  encoded bits, which may be stored or transmitted. During unreliable storage or

30 transmission, the vector  $\mathbf{y}$  of  $N'$  encoded bits is exposed to errors and is typically converted into a vector 106 of  $N'$  encoded soft bits, which express how likely each of the  $N'$  encoded bits of vector  $\mathbf{y}$  is to have a value of '0' or '1'. Typically, each soft bit is represented using a Logarithmic Likelihood Ratio (LLR), where:

$$\text{LLR} = \ln \frac{\text{Pr}(\text{bit} = 0)}{\text{Pr}(\text{bit} = 1)}.$$

35 Hence for the sake of simplicity, the remainder of this document assumes that all soft bits are expressed using LLRs. However, those skilled in the relevant art will also recognize how the inventive concepts described herein may be also applied to other representations of soft bits or soft non-binary symbols in the case of non-binary LDPC codes.

40

In accordance with some examples described herein, an LDPC decoder implementation comprising control, datapath and memory components may be used to convert the

vector 106 of  $N^l$  encoded soft bits into a vector comprising  $K$  decoded bits. In general, an LDPC decoder can be designed to support any number of basegraphs at run-time, having any dimensions and sets of supported lifting factors  $Z$ . However, for the sake of simplicity, this document considers an implementation that is specifically designed to offer run-time

5 support for both 3GPP New Radio basegraphs and all corresponding lifting factors  $Z$ . However, those skilled in the relevant art will also recognize how the inventive concepts described herein may also be applied to other LDPC code basegraphs and sets of supported lifting factors  $Z$ .

10 Different memories within in an LDPC decoder implementation may be used for different purposes, including the storage of LLRs associated VNs. Each VN memory may comprise one or more addresses, each of which may store sets of  $P$  LLRs. Furthermore, in accordance with some examples described herein, each VN memory may include one or more sub-memories, which may be implemented using different physical memory

15 devices, such as Random Access Memories (RAMs). Alternatively, in accordance with some examples described herein, the sub-memories may be implemented as virtual memories occupying different address spaces within the same physical memory. Furthermore, in accordance with some examples described herein, each VN memory may include registers and circuitries that allow sets of LLRs spanning across two or more

20 addresses to be read or written together. Those skilled in the relevant art will also recognize how the inventive concepts described herein may be adapted to adopt one or more or each of these different options.

25 The LDPC decoding process is completed over a number of operations, as illustrated in the known flowchart 600 of FIG. 6. To aid an appreciation of the inventive concepts of the present invention, let us first consider and elaborate on one aspect of the known LDPC decoding process approach. Each operation of the flowchart 600 processes LLRs associated with  $P$  rows within the same blockrow of the PCM, where these rows are typically consecutive. Typically, the complete set of rows within a blockrow are processed

30 during a group of  $\text{ceil}(Z/P)$  consecutive operations, with each successive operation of the flowchart 600 typically processing successive sets of  $P$  rows in order. Cases where  $Z$  is not divisible by  $P$  may be handled using a number of methods, which include deactivating some of the processing in some operations, or performing processing for dummy LLRs associated with an additional number of dummy rows in order to increase the number of

35 rows in the blockrow to a multiple of  $P$ . Indeed, in accordance with some examples described herein, it may be considered that dummy rows can be processed without activating the processing required for actual rows of the PCM. Hence, it may be considered that all methods of handling values of  $Z$  that are not divisible by  $P$  are conceptual special cases of using dummy LLRs and of processing dummy rows. For the

40 sake of simplicity, this is assumed throughout the rest of this document. In this way, each operation the LDPC decoding process operates on a set of  $P$  LLRs (which may include some dummy LLRs) that are required to complete the processing of the  $P$  rows (which may include some dummy rows) of the PCM.

In some examples of the invention, different datapath components within an LDPC decoder implementation may be used for different purposes, including performing the rotation of LLRs being written into VN memories, during a second sub-step 602 in each 5 operation of an LDPC decoding process. Here, the rotators may be configured to undo the rotation that was applied during the first sub-step 601 of the current operation of the LDPC decoding process. In this case, each set of P LLRs may be written in their natural ordering (for example as shown at 403 in FIG. 4), in place of the LLRs that were read from the corresponding core VN memory during the first sub-step 601 of the current operation 10 of the LDPC decoding process.

Alternatively, in some examples of the invention, the core VN memories may operate in a ping-pong manner with each set of P LLRs being written to a different sub-memory of the corresponding core VN memory to that which provided the LLRs during the first sub-step 15 601 of the current operation in the LDPC decoding process. This ping-pong arrangement allows the LLRs to be written into the core VN memories 503 using a rotated ordering (for example as shown at 404 in FIG. 4). This can avoid the requirement for the rotators to perform a rotation during both the reading of LLRs from the corresponding core VN memory and the writing of LLRs to that core VN memory, instead requiring a rotation to 20 be performed during only one or other of these operations. Note that, in accordance with some examples described herein, avoiding a rotation may be considered to be equivalent to performing a rotation by zero positions and that this may be implemented by using an internal bypass within the rotator. For the sake of simplicity, this is assumed throughout the remainder of this document. Note that, in accordance with some examples described 25 herein, some rotators may remain activated between the first sub-step 601 and the second sub-step 602, without the requirement for the second rotator activation at 617 operation to do anything. However, this no-operation may be considered to be a special case of the second rotator activation 617 operation, as is assumed throughout the remainder of this document.

30 Note that the processing of each sub-step 601, 602 within each operation of the LDPC decoding process may be spread over a number of consecutive clock cycles, each having different dedicated hardware in a practical implementation (such as illustrated in FIG. 5). Likewise, the processing of successive operations in the same row of the basegraph may 35 be pipelined, and the processing of successive orthogonal rows in the basegraph may be pipelined.

The LDPC decoding process may continue until a fixed number of decoding iterations have been performed, or until some or all of the syndrome bits associated with the rows 40 in the PCM have binary values of '0'. Following the completion of the decoding iterations within the LDPC decoding process, a vector of N' decoded LLRs may be obtained by concatenating the sets of Z LLRs that were most recently stored in the VN memories 502 and 503. Note that, in accordance with some examples described herein, when a ping-

pong memory arrangement is employed for the core VN memories, it may be necessary to undo any rotation that was most recently applied to the LLRs, in order to restore their natural ordering.

## 5 A novel LDPC decoder implementation having reduced hardware requirement

When applied to the 3GPP New Radio LDPC code, the conventional LDPC decoder implementation 500 described previously has a first problem, namely it includes a large hardware requirement. This may be attributed to the requirement for  $n_{c,\max}=26$  rotators

10 505,  $n_{c,\max}=26$  core VN memories 503 and a CN processor 501 having  $n_{c,\max}+1=27$  I-O ports 504. This motivates a novel LDPC decoder implementation 700 having a reduced hardware requirement, as exemplified in FIG. 7. Here, FIG. 7 illustrates an example embodiment of a LDPC decoder according to some examples of the invention, having a reduced hardware requirement, with application for the 3GPP New Radio LDPC code.

15 More specifically, the proposed implementation 700 adopts a reduced number  $n_{\text{rot}}$  of rotators 705, a reduced number  $n_{\text{rot}}$  of core VN memories 703 and a CN processor 701 having a reduced number  $n_{\text{rot}}+1$  of I-O ports 704, where  $n_{\text{rot}} < n_{c,\max}$ . As in the conventional LDPC decoder implementation 500 described above, each operation within flowchart 800 of the LDPC decoding process completes the processing for a set of P rows in the PCM. In

20 cases where the number of core columns (201 and 301) in the basegraph is no greater than  $n_{\text{rot}}$ , then each operation within flowchart 800 of FIG. 8 of the LDPC decoding process uses only a first sub-step 601 and a second sub-step 602, as in the conventional implementation 500.

25 In cases where the number of core columns (201 and 301) in the basegraph is greater than  $n_{\text{rot}}$ , but the number of binary values of '1' in the current row does not exceed  $n_{\text{rot}}$ , in accordance with some examples described herein, then it may be possible to carefully configure the proposed LDPC decoder implementation 700 such that the corresponding operation 800 within flowchart of the LDPC decoding process may be completed using

30 only a first sub-step 601 and a second sub-step 602, as in the conventional implementation 500 and as will be exemplified below for the 3GPP New Radio LDPC code.

However, in cases where the number of binary values of '1' in the core columns (201 and 301) of the corresponding basegraph row exceeds  $n_{\text{rot}}$ , then each operation within

35 flowchart 800 of the LDPC decoding process comprises a first set of two or more sub-steps 801 and a second set of two or more sub-steps 802. With careful configuration, in accordance with some examples described herein, the number of further sub-steps 803 within respective first set of sub-steps 801 and further sub-steps 804 within respective second set of sub-steps 801 can be minimised, as will be exemplified below for the 3GPP

40 New Radio LDPC code.

Hence, the novel LDPC decoder implementation 700 has a significantly reduced hardware requirement but maintains the same performance as the conventional implementation

(500) in all but a small number of cases. More specifically, in the case of the 3GPP New Radio LDPC code, the number of rotators 705 and core VN memories 703 is reduced from  $n_{c,\max} = 26$  to  $n_{\text{rot}} = 14$ , while the number of CN processor I-O ports 704 is reduced from  $n_{c,\max} + 1 = 27$  to  $n_{\text{rot}} + 1 = 15$ , as will be detailed below. Advantageously, this is achieved

5 without increasing the number of sub-steps required during any of the processing, except during the processing of the 4 core rows of BG1, where the number of sub-steps is doubled.

10 The novel LDPC decoder implementation 700 performs an LDPC decoding process using a number of iterations, where each iteration completes one pass of processing over the PCM. Each iteration is comprised of processing performed for each blockrow of the PCM, where the order in which the blockrows are processed within each iteration is dictated by a layered belief propagation schedule. The processing of each blockrow of the PCM is comprised of a number of LDPC decoding operations, where each operation performs 15 processing for a set of P rows within the blockrow and where the processing of one LDPC decoding operation is depicted in the flowchart 800 of FIG. 8.

20 More specifically, FIG. 8 illustrates a flow chart for the operation of a LDPC decoding process for an example embodiment of the LDPC decoder having a reduced hardware requirement. Each LDPC decoding operation comprises a first set of sub-steps and a second set of sub-steps, as shown in FIG. 8. A number of processes are performed during each sub-step and these may be spread over a number of consecutive clock cycles.

25 More specifically, in accordance with some examples described herein and as shown in FIG. 8, the processing performed in each operation within flowchart 800 of the LDPC decoding commences 805 by completing a first set of sub-steps 801 and a second set of sub-steps 802, before concluding 827. The first set of sub-steps 801 comprises VN memory reading 806, initialising its first sub-step 807, completing the sub-step (808 to 812), determining whether a next sub-step is required 813, initialising the next sub-step if 30 required 814 or performing CN processor calculations 815 otherwise. Each sub-step 803 in the first set of sub-steps 801 comprises rotator activation 808, VN memory reading 810, rotation 811 and CN processor inputting 812. The second set of sub-steps 802 comprises initialising its first sub-step 816, completing the sub-step (817 to 822), determining whether a next sub-step is required 823, initialising the next sub-step if 35 required 824 or VN memory writing 825 and syndrome bit calculation 826 otherwise. Each sub-step 804 in the second set of sub-steps 802 comprises rotator activation 817, CN processor further calculation 819, CN processor outputting 820, rotation 821 and VN memory writing 822.

40 In the general case, each of the  $n_{\text{rot}}$  rotators 705 (together with its corresponding core VN memories 703 and its corresponding CN processor I-O port 704) is allocated to a non-overlapping set of core columns (201 and 301) in each supported basegraph, in a one-to-many arrangement. More specifically, in some examples of the invention, rotations

associated with each column in each basegraph are performed by a particular one of the rotators 705, where each rotator performs rotations for a set of one or more columns, with at least one of the rotators performing rotations for two or more columns in a same basegraph. In this manner, a reduced number of rotators 705 can be used and the

5 hardware resource requirement can be reduced.

As shown in FIG. 8, in accordance with some examples described herein, during each sub-step (e.g. sub-steps 803 and 804) in each set of sub-steps (e.g. sub-steps 801 and 802) within each operation within flowchart 800 of the LDPC decoding process performed

10 within a particular row of a basegraph, a non-overlapping subset of the core columns (201 and 301) in that row having binary values of 1 and having different allocated rotators 705 is selected. Note that in some cases, the subset may comprise one, some or all of the core columns. These rotators 705 and their corresponding core VN memories 703 and CN processor I-O ports 704 are activated within the sub-step (803 and 804) and

15 used to enable processing of the selected core columns (201 and 301). More specifically, the rotator 705, core VN memory 703 and CN processor I-O port 704 associated with a core column (201 and 301) having a binary value of 1 in a particular row of a basegraph are activated in a particular one of the sub-steps in each set of sub-steps (801 and 802) performed during the processing of that row. The selection of which sub-step is used for

20 each core column (201 and 301) is chosen to avoid the processing of more than one column that shares the same rotator 705 in the same sub-step. A number of sub-steps (e.g. sub-steps 803 and 804) are completed until all core columns (201 and 301) in the row having binary values of 1 have been selected and processed.

25 During each sub-step 803 in the first set of sub-steps 801, each of the activated core VN memories 703 are read under the direction of the controller 706, in order to provide the required set of P LLRs. Furthermore, each of the activated rotators 705 is configured to rotate these P LLRs into the required order, under the direction of the controller 706. Each activated rotator 705 provides the corresponding set of P LLRs to the input of the

30 corresponding I-O port 704 of the CN processor 701.

Furthermore, during one of the sub-steps in the first set of sub-steps 801 in each operation within flowchart 800 of the LDPC decoding process that corresponds to an extension row (204 and 304) in the basegraph, the CN processor 701 may also be

35 provided with a set of P LLRs that are read from the extension VN memory 702. More specifically, these LLRs are provided by the particular sub-memory in the extension VN memory 702 that is mapped to that extension row (204 and 304). By contrast, the extension VN memory 702 is deactivated during all other circumstances in the first set of sub-steps 801.

40 The activated subset of the connections to the inputs of the I-O ports 704 of the CN processor 701 each provide it with a set of P LLRs in each 803 of the first set of sub-steps 801 of each operation within flowchart 800 of the LDPC decoding process. Note that in

some cases, the subset may comprise one, some or all of the connections to the inputs of the I-O ports 704. As in the conventional LDPC decoder implementation 500, the CN processor 701 may operate using a variety of algorithms [3], including the sum-product, min-sum, normalised min-sum, offset min-sum or adjusted min-sum, for example. In the 5 case of the min-sum algorithm, we may represent the input LLRs using the notation  $a_{s,i,p}$  where s is in the range 1 to S and indicates which sub-step 803 in the first set of S sub-steps 801 is being performed, i is in the range 1 to A and indicates which of the A activated I-O ports 704 the LLR is provided on and p is in the range 1 to P and indicates which of the P LLRs provided on that I-O port 704 this LLR is. In a first calculation, the CN 10 processor 701 may perform a calculation  $b_{s,i,p} = a_{s,i,p} - m_{s,i,p}$  corresponding to each input LLR  $a_{s,i,p}$ , where  $m_{s,i,p}$  is a corresponding internally stored value which is initialised to 0 at the start of the LDPC decoding process and which is updated in each iteration of the processing of the P rows in the PCM. Across the sequence of sub-steps 803 during the 15 first set of sub-steps 801, the first and second minimum of the absolute values  $|b_{s,i,p}|$  is identified for each value of p and the corresponding values of the indices s and i are referred to as min1 and min2, respectively. Furthermore, the product of the signs  $\text{sign}(b_{s,i,p})$  is identified for each value of p and referred to as  $\text{sign}_p$ .

In each of the second set of sub-steps 802 within flowchart 800, the CN processor 701 20 may perform a calculation  $m_{\min1,\min1,p} = \text{sign}(b_{s,i,p}) \times \text{sign}_p \times |b_{\min2,\min2,p}|$  corresponding to the input LLR  $a_{s,i,p}$  having the indices s and i that correspond to min1 for each value of p. Meanwhile, a calculation  $m_{s,i,p} = \text{sign}(b_{s,i,p}) \times \text{sign}_p \times |b_{\min1,\min1,p}|$  is performed 25 corresponding to all other input LLRs for each value of p. Here, the value of  $m_{s,i,p}$  is written into the internally stored value for each combination of s, i and p, so that it can be used during the next iteration of the processing of the P rows, as described above. Finally, the CN processor 701 may perform a calculation  $d_{s,i,p} = b_{s,i,p} + m_{s,i,p}$ , in order to 30 obtain an output LLR  $d_{s,i,p}$  for each of the P LLRs provided as outputs on each of the A activated I-O ports 704 in each of the S sub-steps 804, in correspondence with the input LLR  $a_{s,i,p}$ . Note that the notation here assumes that the set of rotators 705, core VN 35 memories 703 and CN processor I-O ports 704 that are activated during each 804 of the second set of sub-steps 802 is the same as in the correspond sub-step 803 in the first set of sub-steps 801. In other arrangements, a different activation arrangement may be used for the two sets of sub-steps (801 and 802), and more complicated notation would be required.