# Southampton

### University of Southampton Research Repository

Copyright ⓒ and Moral Rights for this thesis and, where applicable, any accompanying data are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis and the accompanying data cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content of the thesis and accompanying research data (where applicable) must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holder/s.

When referring to this thesis and any accompanying data, full bibliographic details must be given, e.g.

Thesis: Jiaqi Wang (2023) "Ultra-fine Signal Classification Using Memristor-Enabled Hardware", University of Southampton, Faculty of Engineering and Physical Sciences, Electronics and Computer Science, PhD Thesis, 109.

### UNIVERSITY OF SOUTHAMPTON

Faculty of Engineering and Physical Sciences

Electronics and Computer Science

## Ultra-Fine Signal Classification Using Memristor-Enabled Hardware

by

Jiaqi Wang https://orcid.org/0000-0002-2503-1001

> A thesis for the degree of Doctor of Philosophy

> > February 2023

#### UNIVERSITY OF SOUTHAMPTON

#### ABSTRACT

#### FACULTY OF ENGINEERING AND PHYSICAL SCIENCES ELECTRONICS AND COMPUTER SCIENCE

#### Doctor of Philosophy

#### ULTRA-FINE SIGNAL CLASSIFICATION USING MEMRISTOR-ENABLE HARDWARE

by Jiaqi Wang

Neural activity recording system promotes the development of diagnostic and therapeutic programs and neuroscience research. Direct recordings of neural signals from the brain have helped scientists access to study and unlock the secrets of neural coding gradually. This can be realised by applying implantable neural recording systems to monitor and record neural signals. Then, the neural information can be transmitted to the external device for processing, storage or application. However, the power consumption of the neural recording system is the primary constraint to monitoring large groups of neurons. It leads the development of neural recording systems in two directions: 'high-channelcount but wired' and 'wireless but low-channel-count'. To address the power issue, we proposed a neural front-end that aims to detect neural spikes by thresholding and output as one-bit digital data so that the afterwards processing can only work on spikes rather than processing all the data points. The most significant feature is that we induce memristors as trimming devices to tune the threshold voltage for spike detection. Meanwhile, it contributes to rejecting up to 50mV DC offset from electrodes. The measurement presents that the memristor-based pre-amplifier is capable of achieving above 95% spike detection accuracy with hundreds of nanowatt power consumption per channel. This design indicates a promising approach to conduct spike-detection on-chip with low power consumption and demonstrates the potential of a hybrid memristor/CMOS circuit for power-efficient large-scale neural interfacing application.

# Contents

List of Figures

List of Tables

| Declaration of Authorship                                |        |     |       |           |

|----------------------------------------------------------|--------|-----|-------|-----------|

| Acknowledgements                                         |        |     |       |           |

| 1 Introduction                                           |        |     |       | 1         |

| 1.1 The Topic Area, Challenges and Motivation            |        |     |       | 1         |

| 1.2 The Proposed Solution                                |        |     |       | 3         |

| 1.3 Research Objectives                                  |        |     |       | 5         |

| 1.4 Contribution                                         |        |     |       | 5         |

| 1.5 List of Publications                                 |        |     |       | 6         |

| 1.6 Thesis Organisation                                  |        |     | <br>• | 7         |

| 2 Neural Information Processing                          |        |     |       | 8         |

| 2.1 Neural Signals                                       |        |     |       | 8         |

| 2.2 Neural Electrode Techniques                          |        |     |       | 10        |

| 2.3 Neural Front-End                                     |        |     |       | 13        |

| 2.3.1 Overview of Neural Front-End                       |        |     |       | 13        |

| 2.3.2 Offset Rejection: AC-Coupled vs DC-Coupled Solut   | ion    |     |       | 14        |

| 2.3.3 Neural Signal Processing: Spike Detection vs Spike | Sortin | g . |       | 17        |

| 2.3.4 State-Of-the-Art Neural Front-Ends                 |        |     |       | 19        |

| 2.4 Main Reference Circuit: Neural Pre-amplifier         |        |     |       | 20        |

| 2.4.1 Design Concept                                     |        |     |       | 20        |

| 2.4.2 Operational Principles                             |        |     |       | 22        |

| 2.5 Summary                                              |        |     |       | 26        |

| 3 Integrating Memristive Technology into CMOS Design     |        |     |       | <b>27</b> |

| 3.1 Verilog-A Memristor Model                            |        |     |       | 28        |

| 3.2 Integration of Memristor Model into Cadence          |        |     |       | 29        |

| 3.2.1 Import Verilog-A Model into Cadence                |        |     |       | 29        |

| 3.2.2 Simulation Setup for Memristor-based Circuit       |        |     |       | 30        |

| 3.3 Summary                                              |        |     |       | 32        |

| 4 A Memristor-based Pre-amplifier Topology               |        |     |       | 33        |

| 4.1 Transistor Level Analysis                            |        |     |       | 33        |

|   | 4.2                                                                                                                | Theoretical Analysis of Performance Metric                                                                                                                                                                                                                                                                                                                                                                                                         |

|---|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                                                                                                    | 4.2.1 Overview of Performance Metric                                                                                                                                                                                                                                                                                                                                                                                                               |

|   |                                                                                                                    | 4.2.2 Input Range                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |                                                                                                                    | 4.2.3 Open Loop Voltage Gain                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |                                                                                                                    | 4.2.4 Noise Performance                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |                                                                                                                    | 4.2.5 Tuneable Range and Sensitivity                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | 4.3                                                                                                                | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5 | Me                                                                                                                 | hodology of Measuring Memristor-based AC-Coupled Pre-amplifier 44                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 5.1                                                                                                                | Transient Simulation Setup                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   |                                                                                                                    | 5.1.1 Input Range                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |                                                                                                                    | 5.1.2 Voltage Gain and Linearity 48                                                                                                                                                                                                                                                                                                                                                                                                                |

|   |                                                                                                                    | 5.1.3 Input Offset Voltage                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   |                                                                                                                    | 5.1.4 Tunable Range and Sensitivity                                                                                                                                                                                                                                                                                                                                                                                                                |

|   | 5.2                                                                                                                | PSS Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |                                                                                                                    | 5.2.1 Open Loop Voltage Gain and Bandwidth 52                                                                                                                                                                                                                                                                                                                                                                                                      |

|   |                                                                                                                    | 5.2.2 Noise Performance and Detection Accuracy                                                                                                                                                                                                                                                                                                                                                                                                     |

|   |                                                                                                                    | 5.2.3 CMRR and PSRR 55                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   | 5.3                                                                                                                | Power Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   | 5.4                                                                                                                | Clock Skew and Jitter 57                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 5.5                                                                                                                | Simulation with Spike Train                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   |                                                                                                                    | 5.5.1 Spike Train Generation                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |                                                                                                                    | 5.5.2 Spike Train Simulation                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | 5.6                                                                                                                | Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|   | 5.7                                                                                                                | Summary 64                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6 | AN                                                                                                                 | Iemristor-based DC-Coupled Pre-amplifier Topology 65                                                                                                                                                                                                                                                                                                                                                                                               |

|   | 6.1                                                                                                                | The Proposed Circuit                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | 6.2                                                                                                                | Transient Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   | 6.3                                                                                                                | PSS Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | 6.4                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | 0.4                                                                                                                | Tuneable Offset Range    68                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 6.5                                                                                                                | Tuneable Offset Range68Noise Analysis69                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|   | 6.5                                                                                                                | Noise Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | $\begin{array}{c} 6.5 \\ 6.6 \end{array}$                                                                          | Noise Analysis       69         Oversampling       70                                                                                                                                                                                                                                                                                                                                                                                              |

|   | $6.5 \\ 6.6 \\ 6.7$                                                                                                | Noise Analysis69Oversampling70Clock Skew and Jitter71                                                                                                                                                                                                                                                                                                                                                                                              |

| 7 | $6.5 \\ 6.6 \\ 6.7 \\ 6.8 \\ 6.9$                                                                                  | Noise Analysis69Oversampling70Clock Skew and Jitter71Spike Train Detection72                                                                                                                                                                                                                                                                                                                                                                       |

| 7 | $6.5 \\ 6.6 \\ 6.7 \\ 6.8 \\ 6.9$                                                                                  | Noise Analysis69Oversampling70Clock Skew and Jitter71Spike Train Detection72Summary74                                                                                                                                                                                                                                                                                                                                                              |

| 7 | <ul> <li>6.5</li> <li>6.6</li> <li>6.7</li> <li>6.8</li> <li>6.9</li> <li>Lay</li> </ul>                           | Noise Analysis69Oversampling70Clock Skew and Jitter71Spike Train Detection72Summary74Out Design and Chip Testing75                                                                                                                                                                                                                                                                                                                                 |

| 7 | <ul> <li>6.5</li> <li>6.6</li> <li>6.7</li> <li>6.8</li> <li>6.9</li> <li>Lay</li> <li>7.1</li> </ul>              | Noise Analysis69Oversampling70Clock Skew and Jitter71Spike Train Detection72Summary74Out Design and Chip Testing75Layout Design75                                                                                                                                                                                                                                                                                                                  |

| 7 | <ul> <li>6.5</li> <li>6.6</li> <li>6.7</li> <li>6.8</li> <li>6.9</li> <li>Lay</li> <li>7.1</li> <li>7.2</li> </ul> | Noise Analysis69Oversampling70Clock Skew and Jitter71Spike Train Detection72Summary74Out Design and Chip Testing75Layout Design75Post-Layout Simulation79                                                                                                                                                                                                                                                                                          |

| 7 | <ul> <li>6.5</li> <li>6.6</li> <li>6.7</li> <li>6.8</li> <li>6.9</li> <li>Lay</li> <li>7.1</li> <li>7.2</li> </ul> | Noise Analysis69Oversampling70Clock Skew and Jitter71Spike Train Detection72Summary74Out Design and Chip Testing75Layout Design75Post-Layout Simulation79Strategy of Chip Testing80                                                                                                                                                                                                                                                                |

| 7 | <ul> <li>6.5</li> <li>6.6</li> <li>6.7</li> <li>6.8</li> <li>6.9</li> <li>Lay</li> <li>7.1</li> <li>7.2</li> </ul> | Noise Analysis69Oversampling70Clock Skew and Jitter71Spike Train Detection72Summary74Out Design and Chip Testing75Layout Design75Post-Layout Simulation79Strategy of Chip Testing807.3.1Programming Memristive Device80                                                                                                                                                                                                                            |

| 7 | <ul> <li>6.5</li> <li>6.6</li> <li>6.7</li> <li>6.8</li> <li>6.9</li> <li>Lay</li> <li>7.1</li> <li>7.2</li> </ul> | Noise Analysis       69         Oversampling       70         Clock Skew and Jitter       71         Spike Train Detection       72         Summary       74         Out Design and Chip Testing       75         Layout Design       75         Post-Layout Simulation       79         Strategy of Chip Testing       80         7.3.1       Programming Memristive Device       80         7.3.2       Measurement of the Bias Current       81 |

| 7 | <ul> <li>6.5</li> <li>6.6</li> <li>6.7</li> <li>6.8</li> <li>6.9</li> <li>Lay</li> <li>7.1</li> <li>7.2</li> </ul> | Noise Analysis69Oversampling70Clock Skew and Jitter71Spike Train Detection72Summary74Out Design and Chip Testing75Layout Design75Post-Layout Simulation79Strategy of Chip Testing807.3.1Programming Memristive Device807.3.2Measurement of the Bias Current817.3.3Determining the Operation Phases83                                                                                                                                               |

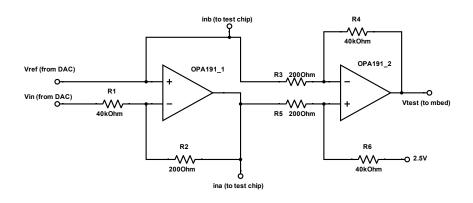

|                             | 7.4   | Precise Signal Generation Board for Chip Test           |     |  |  |  |

|-----------------------------|-------|---------------------------------------------------------|-----|--|--|--|

| 7.5 Pre-amplifier Chip Test |       |                                                         |     |  |  |  |

|                             |       | 7.5.1 Testing on the Chip without Memristor             | 87  |  |  |  |

|                             |       | 7.5.2 Testing on the Chip with Memristor                | 88  |  |  |  |

|                             |       | 7.5.3 Circuitry Improvements                            | 90  |  |  |  |

|                             | 7.6   | Summary                                                 | 91  |  |  |  |

| 8                           | ΑN    | $\textbf{Iemristor-Based} \ \Delta \Sigma \textbf{ADC}$ | 92  |  |  |  |

|                             | 8.1   | Architecture of $\Delta\Sigma ADC$                      | 93  |  |  |  |

|                             | 8.2   | Performance $\Delta \Sigma ADC$                         | 94  |  |  |  |

|                             | 8.3   | Simulation with Spike Train                             | 96  |  |  |  |

|                             | 8.4   | Summary                                                 | 97  |  |  |  |

| 9                           | Cor   | clusion and Future Work                                 | 98  |  |  |  |

|                             | 9.1   | Conclusion                                              | 98  |  |  |  |

|                             | 9.2   | Recommendation for Future Work                          | 99  |  |  |  |

| Bi                          | bliog | graphy                                                  | 101 |  |  |  |

# List of Figures

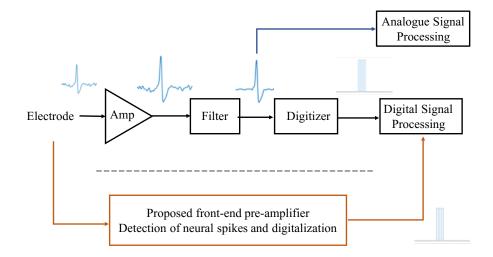

| 1.1  | Structure comparison among the previous works in digital and analogue forms and our proposed work                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

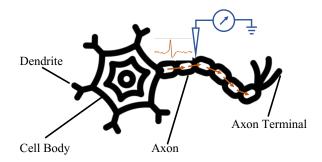

| 2.1  | Dendrites, cell bodies, axons, and axon terminals make up a neuron. More-<br>over, the transmembrane potential of the neuron can be captured by the<br>electrodes.                                                                                                                                                                                                                                                                                                                                                                                                     |

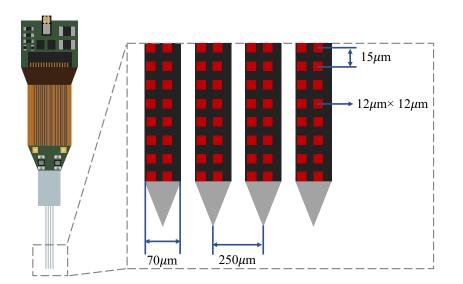

| 2.2  | Architecture and dimensions of Neuropixels 2.0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

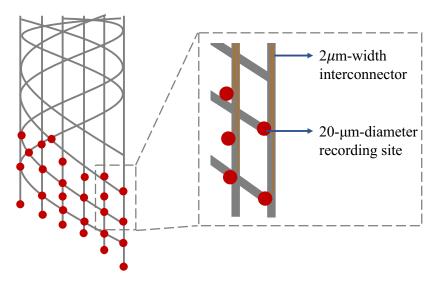

| 2.3  | Architecture and dimensions of mesh electrodes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

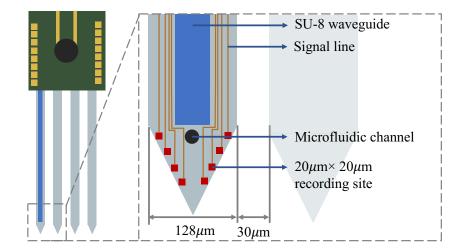

| 2.4  | The architecture and dimensions of multi-shank electrodes, where SU-8 is<br>a type of negative photoresist utilised as the core layer for waveguide.                                                                                                                                                                                                                                                                                                                                                                                                                   |

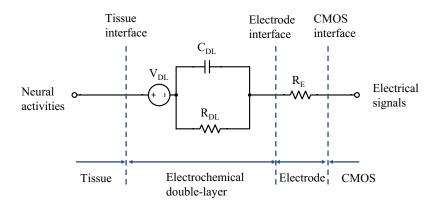

| 2.5  | Electrical model of the electrode between the brain tissue and CMOS de-<br>vice, where $V_{DL}$ , $C_{DL}$ and $R_{DL}$ are the double-layer potential, double-layer<br>capacitance and resistance, respectively, and $R_E$ is the resistance from the<br>electrode to the CMOS device.                                                                                                                                                                                                                                                                                |

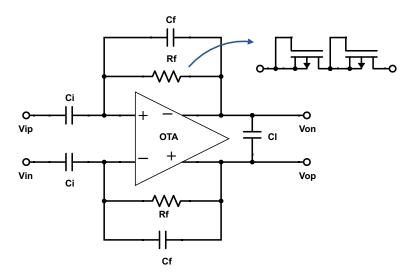

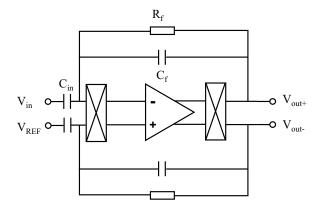

| 2.6  | AC-coupled neural amplifier with capacitive-feedback network (CFN) topology. The resistor $R_f$ is a MOS-bipolar pseudo-resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

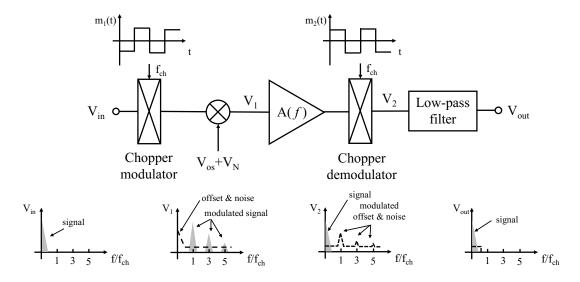

| 2.7  | The general block diagram of the chopper shows the principles and signal transmission in the frequency domain.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2.8  | The conventional chopper-stabilised neural amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

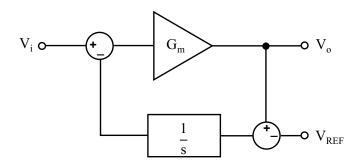

| 2.9  | General schematic of DC servo loop.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

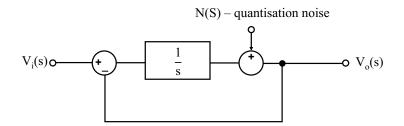

| 2.10 | One-bit delta-sigma modulator in s-domain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

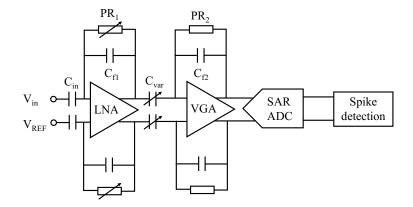

| 2.11 | AC-coupled capacitive-feedback front-end.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

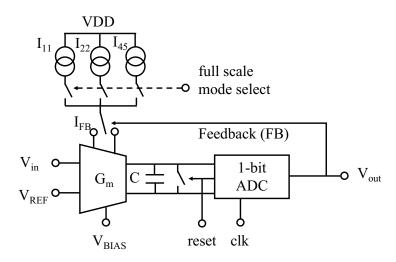

| 2.12 | The architecture of one-bit delta-sigma ADC where utilises three scales of current sources to conduct calibration.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

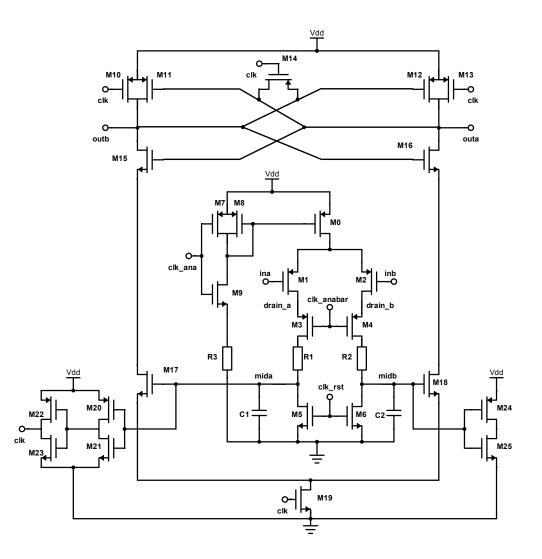

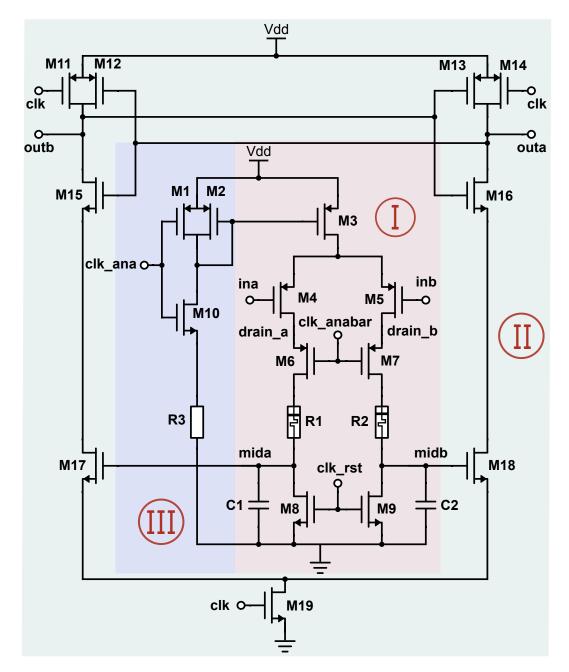

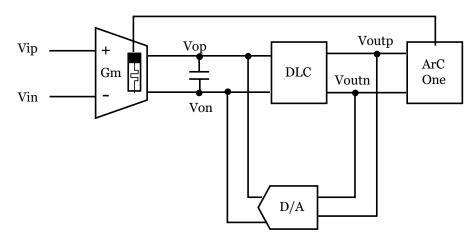

| 2.13 | The architecture of pre-amplifier. It consists of three parts: (i) the core integrating amplifier, (ii) the dynamic latch comparator and (iii) the current bias control unit. Control signals, including <i>clk</i> , <i>clk_ana</i> , <i>clk_anabar</i> , <i>clk_rst</i> are all assumed to be generated by voltage sources which are strictly periodic.                                                                                                                                                                                                              |

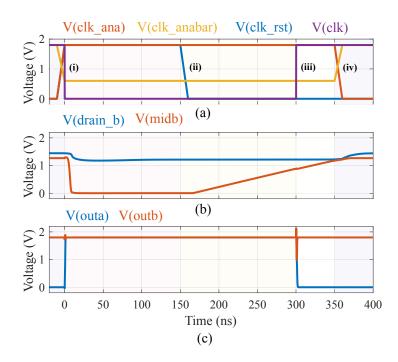

| 2.14 | Transient simulation of one detection cycle of the neural spike. One detec-<br>tion with four phases completes in $350ns$ as an example, which has been<br>labelled and highlighted with different backgrounds. It contains (i) reset,<br>(ii)integration, (iii) digitisation and (iv) off phases. (a) presents the control<br>of clocks; (b) compares the amplifier output ( <i>midb</i> ) with the drain of the<br>input transistor ( <i>drain_b</i> ); (c) presents the digital output from DLC. Input<br>signals are set as: $ina = 1V + 50\mu V$ and $inb = 1V$ . |

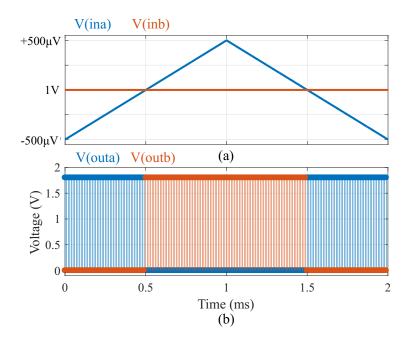

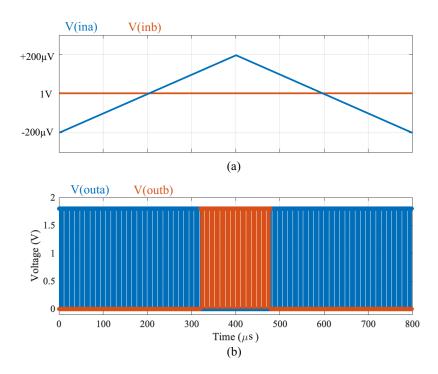

| 2.15 | Pre-amplifier basic functionality test: Input A (ina) is slowly swept between $[1V - 100\mu V, 1V + 100\mu V]$ over $2ms$ while the pre-amplifier is carrying out a conversion every $10\mu s$ to detect the relationship between inputs A and B. Input B (inb) remains stable at $1V$ throughout. In this test, the amplifier was balanced $(R1 = R2)$ . When $V_{ina} < V_{inb}$ , the left branch current is larger than the right branch current, inducing $V_{mida} - V_{midb} > 0$ . The DLC captures this relation and generates binary signals: $V_{outa} = 1$ and $V_{outb} = 0$ , which appears in the bottom panel as a predominantly orange output trace. Conversely, when $V_{ina} > V_{inb}$ , $V_{outa} = 0$ and $V_{outb} = 1$ , which appears as a combined orange/blue output trace. Note: this type of simulation can also be used to test the offset tuning range and tuning sensitivity on the resistive state of memristive devices. When $R1 > R2$ , $V_{ina}$ must be lower than $V_{inb}$ to ensure a balanced output, creating an offset, this is read in the output trace as an encroachment of the blue region into the orange (and vice versa for $R1 < R2$ ). | 25 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

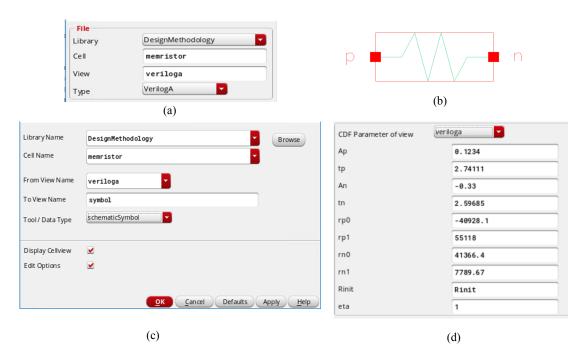

| 3.1  | The operation sequence of importing memristor into Cadence. (a) Process<br>of building a new cell view in Verilog-A type for memristor. (b) Symbol<br>of the memristor. (c) Process of creating a symbol for memristor from<br>Verilog-A cell view. (d) The parameters of the memristor can be modified<br>in the object properties window.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 30 |

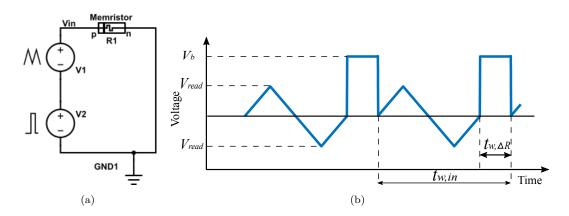

| 3.2  | (a) Testbench of applying pulse and triangular wave to memristor to con-<br>duct the write and read operations in the transient simulation. (b) Pulse<br>chain that provokes the memristor. The input signal sequence can be di-<br>vided into two parts: triangular wave and pulse. For all the simulations of<br>our device, the read voltage is defined as $V_{read} = 0.5V$ with $1ms$ duration.<br>The pulses can be determined with specific duration/width $(t_{w,\Delta R})$ , am-<br>plitude $(V_b)$ and the number of pulses to provoke the memristor. With the<br>combination of two stages, the $RS$ of the memristor model can be tracked<br>for each stimulus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31 |

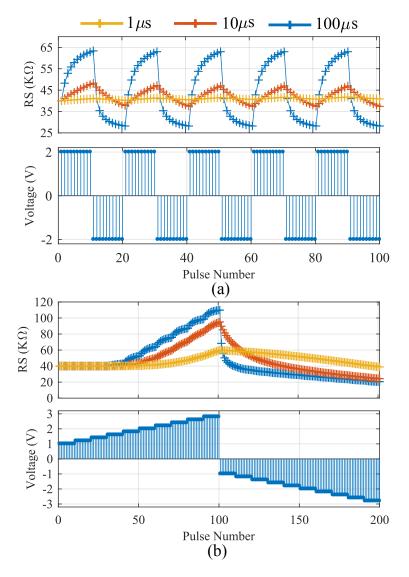

| 3.3  | Simulation results for the quadratic memristive Verilog-A model in Ca-<br>dence. (a) shows the responses of the model to $1, 10, 100\mu s$ pulse widths<br>with constant amplitudes ( $\pm 2V$ ). (b) presents the model response to the<br>voltage ramp from 1V to 3V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 32 |

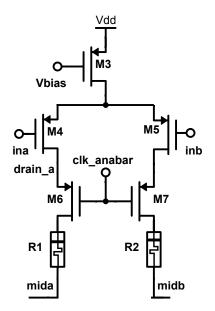

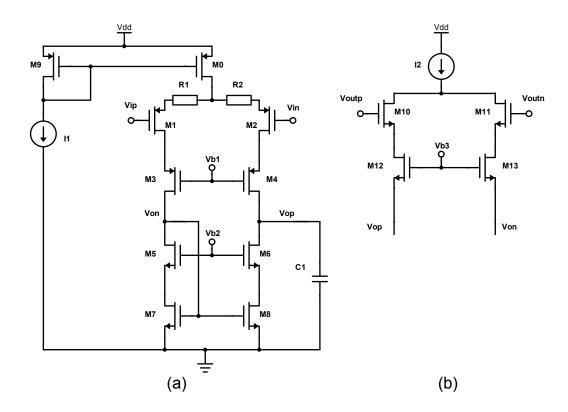

| 4.1  | The schematic of the proposed pre-amplifier. Compared to the initial design in Figure 2.13, this circuit uses external $clk$ to control that the DLC can be fed by sufficient voltage difference and increase detection accuracy.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 34 |

| 4.2  | Part of schematic of core amplifier aiding the input range analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 37 |

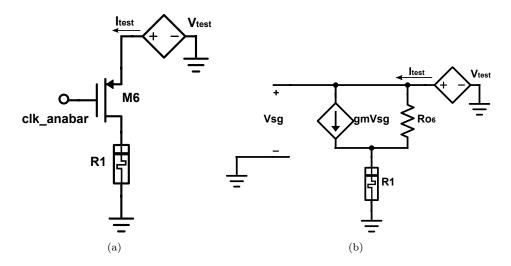

| 4.3  | The circuit diagram of M6 and R1 with a test voltage source presented as (a) a large signal and (b) a small signal. $R_o$ represents the drain-source resistance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 41 |

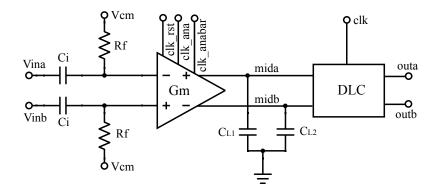

| 5.1  | Block diagram of the proposed neural recording front-end. The open-loop network OTA filters the raw data to obtain the MUA. The minute signals charge the load capacitors $(C_{L1,2})$ to realise the integration and boost the voltage difference of <i>mida</i> & <i>midb</i> , which triggers the DLC to process digitisation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 45 |

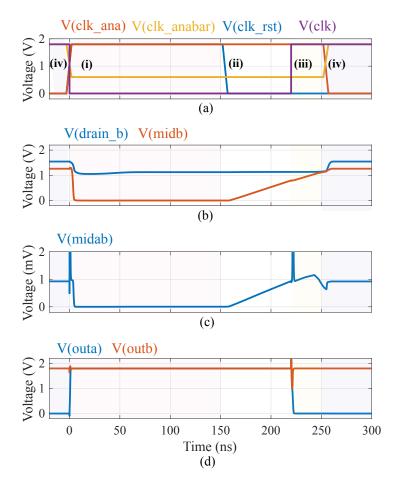

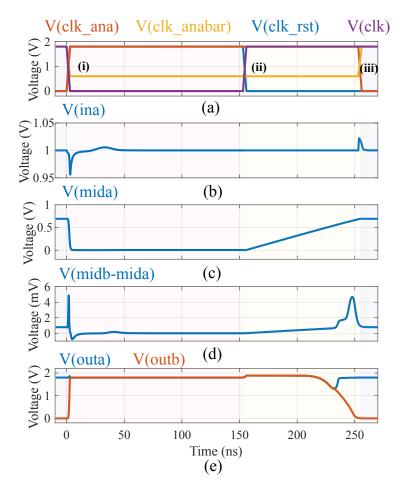

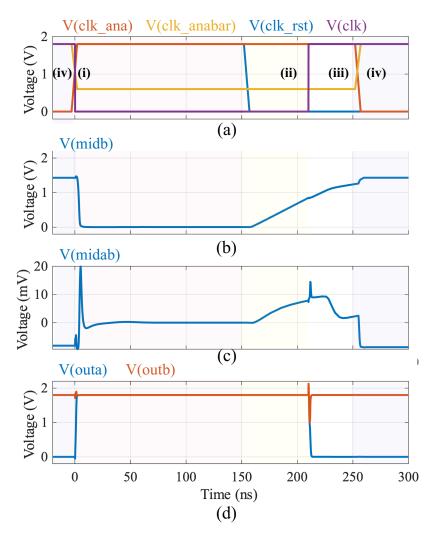

| 5.2  | Transient simulation of one detection cycle of the neural spike. One detec-<br>tion with four phases completes in 250 <i>ns</i> , under the condition of $V_{ina} = 1V + 50\mu V$ and $V_{inb} = 1V$ . It contains (i) reset, (ii) integration, (iii) de-<br>tection and (iv) off phases. Full detection cycle is presented, including (a)<br>control signals, (b) output of the amplifier ( <i>midb</i> ) and drain voltage of in-<br>put transistor ( <i>drain_b</i> ), (c) differential output of the OTA ( $\Delta V_{mid}$ ) and<br>(d) digital outputs                                                                                                                                                                                                                                                      |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

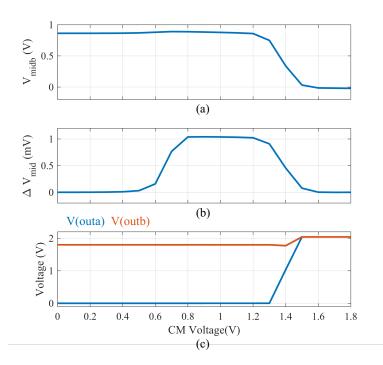

| 5.3  | Input range results of pre-amplifier. In this simulation, the common mode voltage was swept from zero to $1.8V$ with $0.1V$ differential input. For $V_{CM} \in [0-1.3]V$ , we notice that (a) $V_{midb}$ reaches sufficiently high voltage to prompt a stable output from the (c) DLC for our chosen differential input the output is always correct. However, the core's analogue gain in (b) is maximised in the narrower range $[0.8, 1.2]V$                                                                                                                                                                                                                                                                                                                                                                  |

| 5.4  | Intermediate differential output $\Delta V_{mid}$ evolution as a function of $V_{CM}$ .<br>Differential input voltage is $50\mu V$ and the integration phase is not time-<br>constrained (see Figure 5.3). Voltage traces for different $V_{CM}$ s follow each<br>other closely except in the edge cases $V_{CM} \in \{0.7V, 1.2\}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

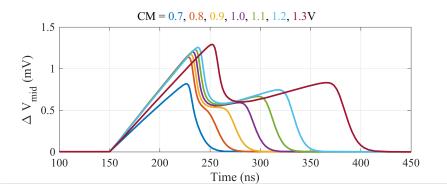

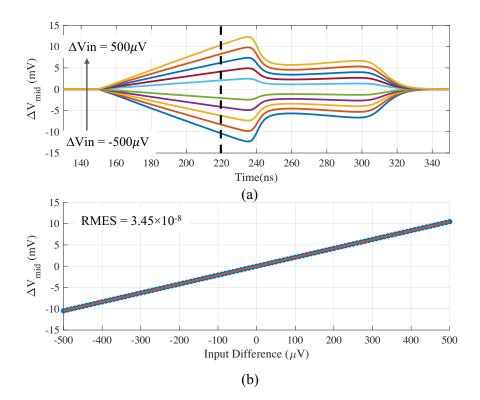

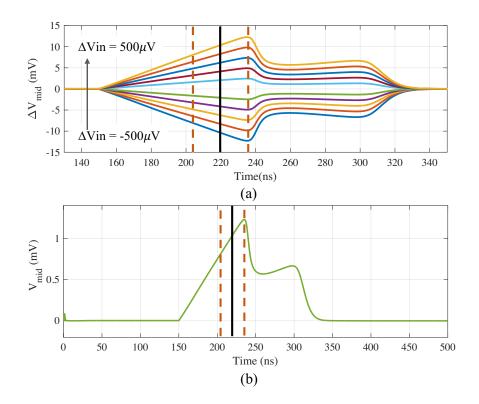

| 5.5  | Simulation results of the differential gain analysis. In this simulation, <i>inb</i> was set at $1V$ while <i>ina</i> was swept from $1V - 500\mu V$ to $1V + 500\mu V$ with in steps of $10\mu V$ . (a) $\Delta V_{mid}$ throughout an intentionally excessively long integration phase. As $V_{mida,b}$ increases, the cascode transistors eventually triode causing the gain to peak and decrease. Peak gain times occur at $t = 237ns$ and are aligned within $1ps$ difference. An indicative integration time leaving a substantial margin for error can be set to, e.g. $220ns$ (dashed line in (a)). (b) Output voltage difference $\Delta V_{mid}$ at integration time $\tau = 220ns$ vs input differential voltage. A linear curve excellently fits the result. The gain is constant at approx. $G = 20$ |

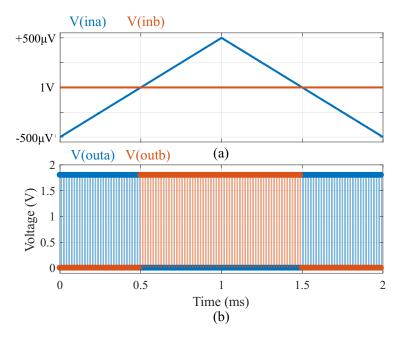

| 5.6  | Pre-amplifier basic functionality test: Input A (ina) is slowly swept between $[1V - 500\mu V, 1V + 500\mu V]$ over $2ms$ while the pre-amplifier is carrying out a conversion every $1\mu s$ to detect the relationship between inputs A and B.<br>Input B (inb) remains stable at $1V$ throughout. In this test, the amplifier was balanced $(R1 = R2)$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

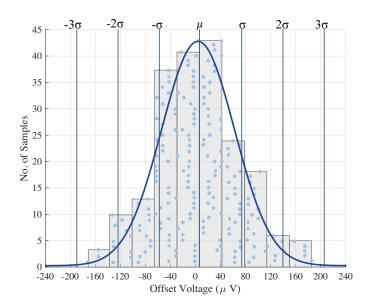

| 5.7  | Histogram of Monte Carlo simulation with 200 samples of the input offset         voltage.       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

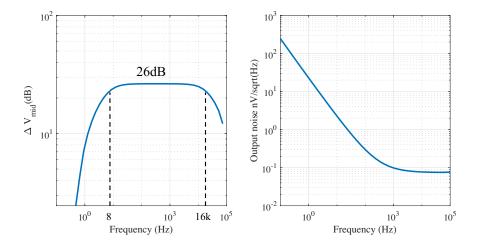

| 5.8  | OTA gain and input noise as a function of frequency. (a) The open-loop<br>network OTA presents bandpass filtering with a mid-band gain of 26 dB.<br>(b) Output noise of the detection cycle from (periodic) noise simulation. 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

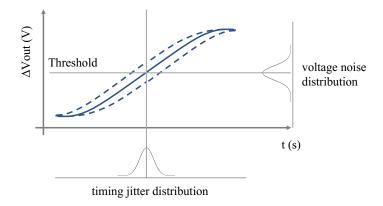

| 5.9  | Principle of periodic noise jitter analysis at the threshold point 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

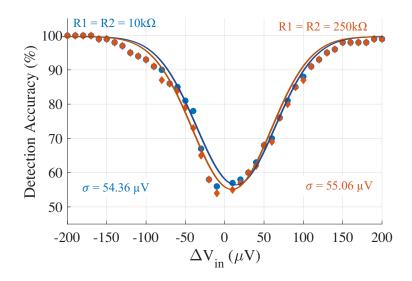

| 5.10 | Detection accuracy of different $\Delta V_{in}$ from transient noise simulation under<br>the conditions of $R1 = R2 = 10k\Omega$ (blue) and $R1 = R2 = 250k\Omega$ (orange).<br>The Gaussian fittings and input-referred noise/standard derivation ( $\sigma$ ) are<br>given                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

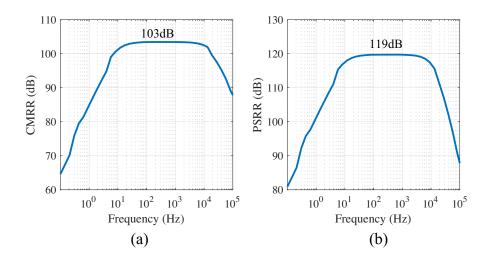

| 5.11 | CMRR and PSRR of the open-loop network pre-amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

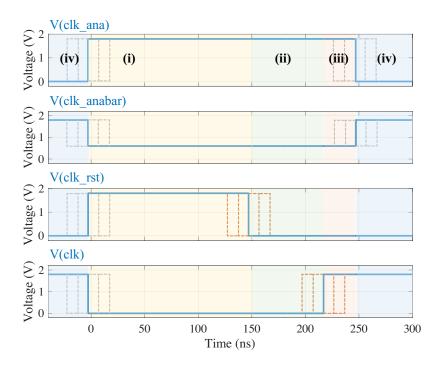

| 5.12 | Clocking of the AC-coupled front-end with the jitter effect presented in dash<br>lines. The timing diagram presents four phases: i) reset, ii) integration, iii)<br>digitisation and iv) off phases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5.13 | Simulation results of (a) differential output voltage of OTA ( $\Delta V_{mid}$ ) and (b) output voltage ( $V_{mid}$ ). The <i>clk</i> signal occurs at 220ns ideally and samples the output of OTA, whilst the tolerant variation range is within orange dash lines.                                                                       |  |  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

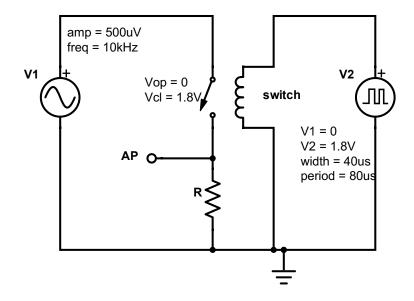

| 5.14 | Schematic of spike train generation, where the output is at the port 'AP'.                                                                                                                                                                                                                                                                  |  |  |

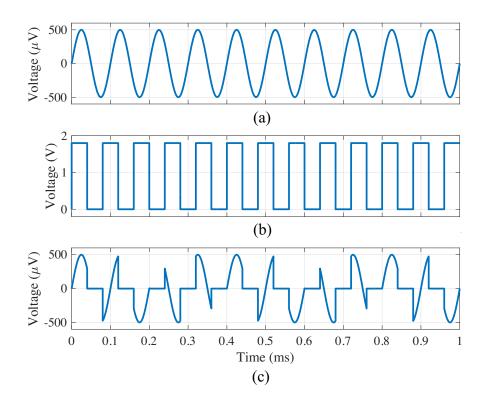

| 5.15 | The timing diagram of spike train generation. (a) is sine wave with the amplitude of $500\mu V$ and frequency of $10kHz$ . (b) is the periodic pulse, and (c) is the generated spike train.                                                                                                                                                 |  |  |

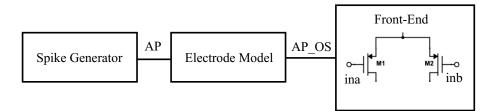

| 5.16 | The block diagram presents the module and connection of the testbench                                                                                                                                                                                                                                                                       |  |  |

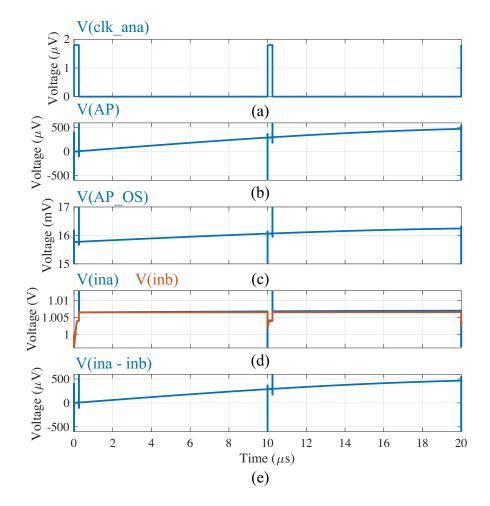

| 5.17 | The timing diagram of the control signal and spikes. (a) $clk\_ana$ controls<br>the on and off status of the OTA. (b) Spike train $(AP)$ from spike generator.<br>(c) shows the spike with 15.77mV DC offset appended. (d) presents the<br>input voltages of OTA. (e) is the differential input voltage of OTA                              |  |  |

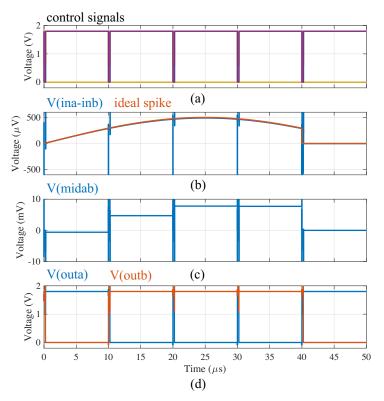

| 5.18 | Simulation result of spike detection. (a) presents control signals which are the same as Figure 5.2. (b) presents the differential input voltage $ina - inb$ and the ideal spike. (c) shows the differential output voltage of OTA, and (d) presents the digital outputs.                                                                   |  |  |

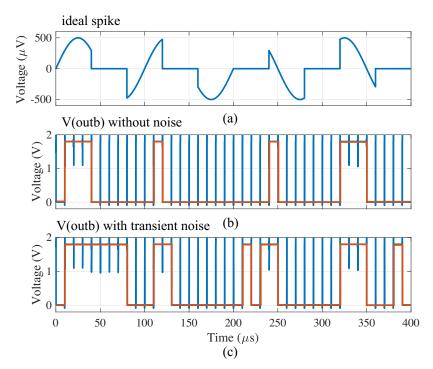

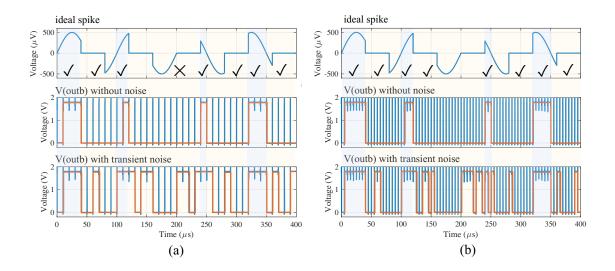

| 5.19 | Simulation result of spike detection within $400\mu s$ . (a) presents the ideal spike. (b) is digital output in noiseless simulation, and (c) is obtained from transient noise simulation.                                                                                                                                                  |  |  |

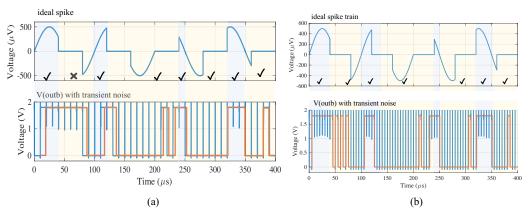

| 5.20 | The timing diagram is to present the spike detection accuracy. The detection cycle is $10\mu s$ in (a) and $5\mu s$ in (b), respectively.                                                                                                                                                                                                   |  |  |

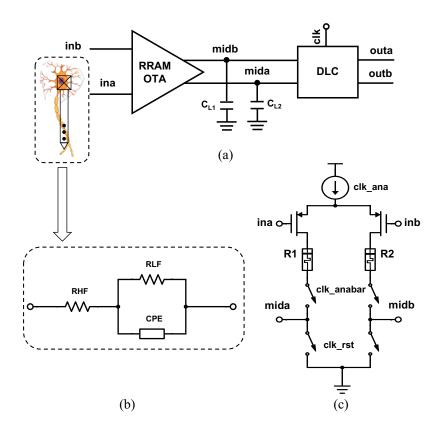

| 6.1  | DC-coupled front-end. (a) Block diagram of the neural recording front-end.<br>(b) The electrical model of the tissue-electrode interface. (c) Simplified schematic of the OTA assembled with memristive devices.                                                                                                                            |  |  |

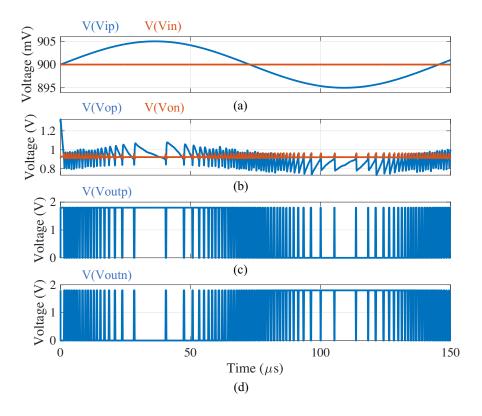

| 6.2  | The timing diagram of one neural detection cycle $(250ns)$ . (a) clocking scheme. (b) input voltage of the front-end from the electrode. (c) the output voltage of the core amplifier. (d) the differential output voltage of the amplifier. (e) digital outputs from the DLC. (In this simulation, $ina = 1V + 50\mu V$ and $inb = 1V$ .). |  |  |

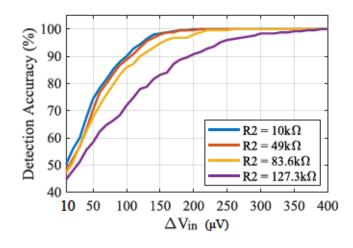

| 6.3  | Detection accuracy of front-end system vs differential input voltages $\Delta V_{in}$ from $10\mu V$ to $400\mu V$ . In this case, $R1 = 10k\Omega$ , $R2 \in \{10, 49, 83.6, 127.3\}k\Omega$ in order to compensate the DC offset of $\{1m, 10m, 50m\}V$ .                                                                                 |  |  |

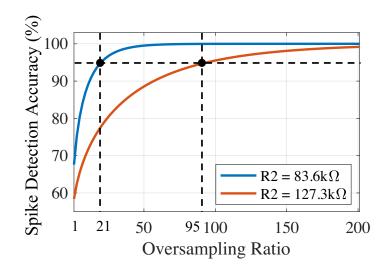

| 6.4  | Spike detection accuracy under oversampling. The initial value takes from Fig. 6.3, where the accuracy of $R2 = 83.6k\Omega$ and $R2 = 127.2k\Omega$ are $67.6\%$ and $58.4\%$ respectively under $\Delta V_{in} = 50\mu V$ .                                                                                                               |  |  |

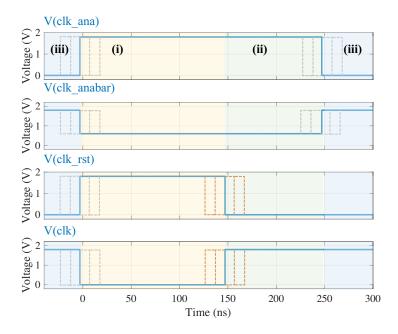

| 6.5  | Clocking of the AC-coupled front-end with the jitter effect presented in dash line. The timing diagram presents three phases: i) reset, ii) detection and iii) off phases.                                                                                                                                                                  |  |  |

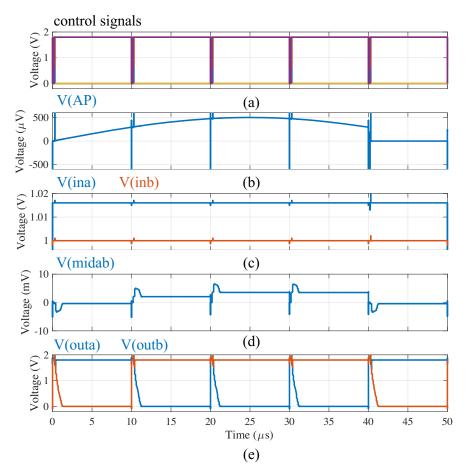

| 6.6  | Simulation result of spike detection. (a) presents control signals which are the same as Figure 6.2. (b) is the spike train generated in Figure 5.16. (c) presents the input voltages of OTA. (d) shows the differential output voltage of OTA, and (e) presents the digital outputs.                                                       |  |  |

| 6.7  | The timing diagram is to present the spike detection accuracy. The detection cycle is $10\mu s$ in (a) and $5\mu s$ in (b), respectively.                                                                                                                                                                                                   |  |  |

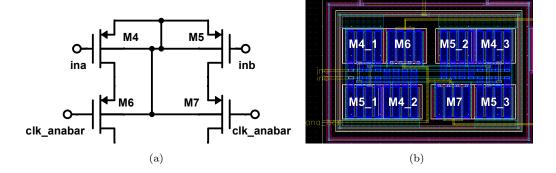

| 7.1  | Differential input and cascode pair in both (a) schematic and (b) layout view. The bulks of the above components are connected to the source of M4&M5.                                                                                                                                                                                                                                                                      |

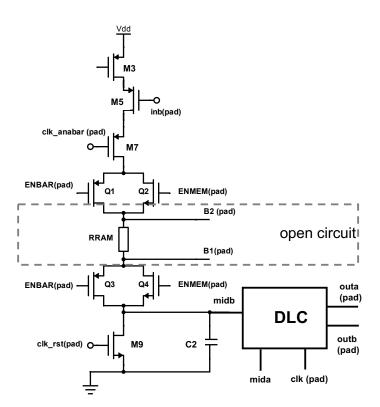

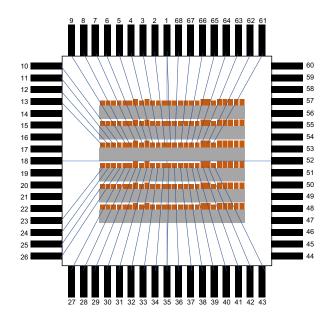

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

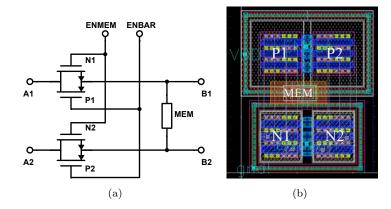

| 7.2  | Schematic and layout of the programming circuit of the memristive device.<br>(a) Terminals A and B can be the user terminal and programming terminal<br>or in reverse. The status of memristive in the application or programming<br>is controlled by two signals, <i>ENMEM</i> and <i>ENBAR</i> . In layout (b), the<br>memristive device is in the middle and connects to PMOS (upper device)<br>and NMOS (lower device). |

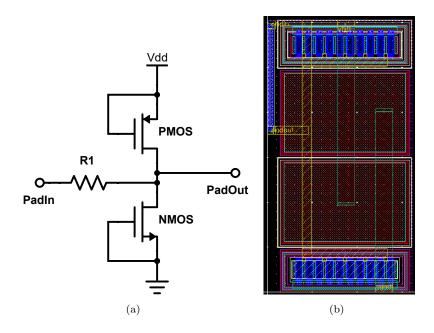

| 7.3  | The schematic (a) and layout (b) of ESD Cell based on TSMC180nm technology.                                                                                                                                                                                                                                                                                                                                                 |

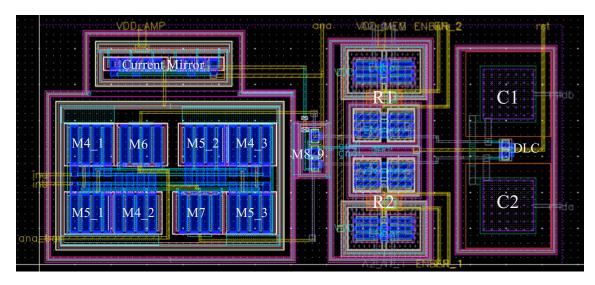

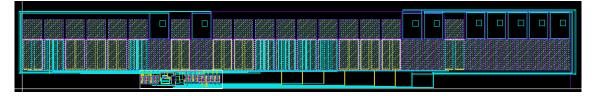

| 7.4  | Layout of the core pre-amplifier circuit with the input and output on the boundary to connect the ESD cell or the pad directly.                                                                                                                                                                                                                                                                                             |

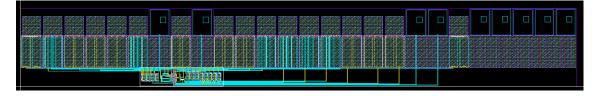

| 7.5  | Complete layout design of the pre-amplifier. This design has two types of pads: i) the commercial pad from the foundry and ii) the in-house pad for programming the memristive devices.                                                                                                                                                                                                                                     |

| 7.6  | The input voltage ramp is applied to the circuit for the post-layout circuit to determine the inherent offset voltage. The figure shows that the inherent offset voltage is $V_{os} = V_{ina} - V_{inb} = 120\mu V$ .                                                                                                                                                                                                       |

| 7.7  | Timing diagram for post-layout simulation.                                                                                                                                                                                                                                                                                                                                                                                  |

| 7.8  | The schematic of utilising two OPA191 to generate and test precise analogue signals.                                                                                                                                                                                                                                                                                                                                        |

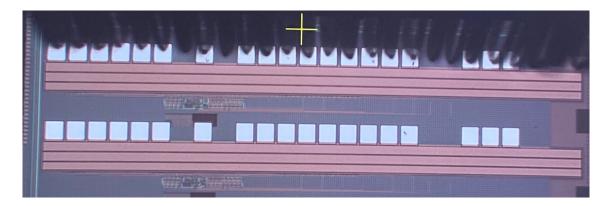

| 7.9  | Full view of the chip without the memristor electrode.                                                                                                                                                                                                                                                                                                                                                                      |

| 7.10 | The schematic view presents the connection inside the chip where there exist open circuit due to missing memristor.                                                                                                                                                                                                                                                                                                         |

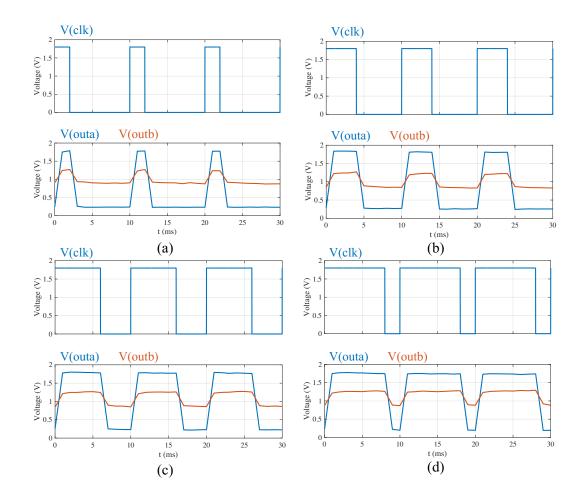

| 7.11 | Testing Result of the DLC with floating inputs with different pulse widths.<br>In this test, the pulse in the duration of $10ms$ with four pulse widths $\in \{2ms, 4ms, 6ms, 8ms\}$ are fed into the chip (presented at the top trace of sub-figures). The digital outputs are presented in the bottom trace of each sub-figure.                                                                                           |

| 7.12 | The pre-amplifier chip with the memristor pads and wiring on the top (in white). But the wirings across the padring short the power.                                                                                                                                                                                                                                                                                        |

| 7.13 | The full layout with new wiring route for memristors and electrodes that prevents shorting circuit.                                                                                                                                                                                                                                                                                                                         |

| 7.14 | The full layout with new wiring route that prevents shorting circuit                                                                                                                                                                                                                                                                                                                                                        |

| 8.1  | The block diagram of proposed $\Delta\Sigma ADC$                                                                                                                                                                                                                                                                                                                                                                            |

| 8.2  | The schematic of OTA of $\Delta\Sigma$ ADC. (a) The OTA is the input and the integrator interface in the $\Delta\Sigma$ modulator. (b) The IDAC shown on the right creates a current feedback loop                                                                                                                                                                                                                          |

| 8.3  | The timing diagram of $\Delta\Sigma$ ADC. (a) the input of the system. (b) the output of the OTA. The one-bit IDAC provides the modulation. (c) and (d) are the outputs of the DLC, respectively.                                                                                                                                                                                                                           |

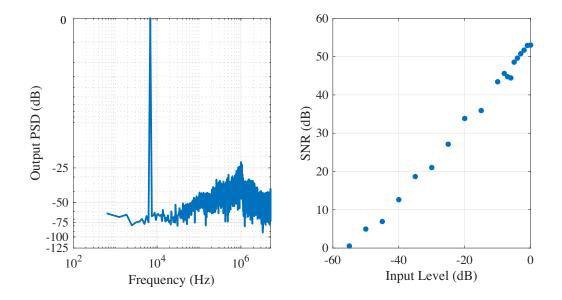

| 8.4  | Performance of $\Delta\Sigma$ ADC. (a) the output spectrum for the input sine wave<br>of 10 $mV_{pp}$ under the noise simulation. (b) SNR versus input level where<br>indicates 55dB DR                                                                                                                                                                                                                                     |

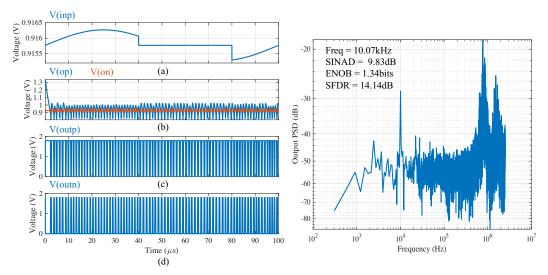

| 8.5 | Left: the timing diagram of $\Delta\Sigma$ ADC with (a) the spike train input with |    |

|-----|------------------------------------------------------------------------------------|----|

|     | 15.77mV DC offset. (b) the output of the OTA. (c) and (d) are the outputs          |    |

|     | of the DLC, respectively. Right: output spectrum for spike train with the          |    |

|     | maximum amplitude of $500\mu V$ and $15.77mV$ DC offset.                           | 97 |

# List of Tables

| 2.1 | Summary of the characteristics of different neural signal modalities                                      | 10       |

|-----|-----------------------------------------------------------------------------------------------------------|----------|

| 2.2 | Comparisons of the novel electrodes                                                                       | 12       |

| 2.3 | Parameters of the electrical model from the measurement of different ma-                                  |          |

|     | terials                                                                                                   | 12       |

| 2.4 | Comparison among state-of-art neural front-end and the specification of                                   |          |

|     | this work.                                                                                                | 21       |

| 4.1 | Specification of the memristive integrating OTA.                                                          | 36       |

|     |                                                                                                           | 00       |

| 5.1 | Specification and overview of simulation methodology for the memristor-<br>based OTA.                     | 45       |

| 5.2 | Results of a normal distribution from Monte Carlo simulation. $\ldots$ .                                  | 50       |

| 5.3 | The offset voltage of pre-amplifier vs memristor device resistive state is quoted at $1\mu V$ resolution. | 52       |

| 5.4 | Performance metrics of the discrete-mode threshold detection system                                       | 56       |

| 6.1 | Sizes of devices in the proposed architecture, where the bias current of the                              |          |

|     | core amplifier is $I_{tail} = 3\mu A$ . R3 is replaced by a diode-connected NMOS.                         |          |

|     | The detailed schematic is in Figure 4.1.                                                                  | 65       |

| 6.2 | Performance metric of memristor amplifier (The energy and average power                                   |          |

|     | consumption are of one detection cycle with $250ns$ , including both mem-                                 |          |

| 0.0 | ristor amplifier and DLC).                                                                                | 68       |

| 6.3 | The compensated DC offset versus the resistive state of memristors under $R1 = 10 \ k\Omega$ .            | 69       |