### University of Southampton Research Repository

Copyright © and Moral Rights for this thesis and, where applicable, any accompanying data are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis and the accompanying data cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content of the thesis and accompanying research data (where applicable) must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holder/s.

When referring to this thesis and any accompanying data, full bibliographic details must be given, e.g.

Thesis: Author (Year of Submission) "Full thesis title", University of Southampton, name of the University Faculty or School or Department, PhD Thesis, pagination.

Data: Author (Year) Title. URI [dataset]

### University of Southampton

Faculty of Engineering and Physical Sciences School of Electronics and Computer Science

# Memory Consolidation in Memristive Systems

DOI: 10.1002/0470841559.ch1

by

**Christos Giotis**

ORCiD: 0000-0002-1825-0097

A thesis for the degree of Doctor of Philosophy

February 2023

### University of Southampton

#### **Abstract**

### **Memory Consolidation in Memristive Systems**

by Christos Giotis

This thesis investigates the challenge of memory consolidation and learning in artificial synapses. The adoption and evolution of artificial intelligence (AI) also byproducts a frequently overlooked exponentially increasing need for information processing and data storage. This issue is either met with the physical expansion of storage facilities or with the inevitable forgetting of old information in favour of new; both of which seriously hinder the performance of embedded AI systems. This work presents a novel approach in emulating the complex biochemical mechanisms which allow neuronal synapses to store multiple memories on top of the other and at different timescales, like a palimpsest, and which give rise to the incredible learning capacity of biological intelligence.

This work mainly focused on exploiting the intrinsic time dependent volatility in emerging memristive nanotechnologies to showcase palimpsest consolidation. Memristive volatility was studied using a data-driven approach and device-agnostic characterisation and mathematical modelling methods were developed to uncover the main properties of the mechanism. It was found that volatility can exist bidirectionally in TiO2 memristors and that its time constants can be manipulated via the invasiveness and/or frequency of device stimulation. Importantly, within a given observation time window, volatility was shown to operate at two timescales; a fast decay of large magnitude followed by a saturating steady state and a small non-volatile residue. By operating memristive devices as binary synapses, spiking plasticity events were able to store long-term memories in the non-volatile residue, while expressing the opposing state in the short-term. Palimpsest consolidation was examined in simulated memory networks which were able to protect long-term memories while expressing up to hundreds of uncorrelated short-term memories. It was also found that these networks bear close resemblance to the visual working memory of mammalian brains. The same plasticity dynamics were finally extended towards the context of neuronal activity detection, where memristive sensors were able to 'learn' during high spiking frequencies and 'forget' during less active timeframes.

The results presented in this thesis verify the candidacy of volatile memristors as natural facilitators of learning in AI. The ability to learn continuously without catastrophically forgetting old memories, can create new possibilities in the way AI can be used to undertake more generalised tasks. Moreover, the same artificial synapses have shown immense potential in neural interfacing. This can potentially reshape the ways AI is currently interpreted and lead to novel research which aims to integrate both biological and artificial intelligence.

# **Contents**

| Li | st of   | Figures  | 5                                                  | ix   |

|----|---------|----------|----------------------------------------------------|------|

| Li | st of ' | Tables   |                                                    | xi   |

| D  | eclara  | ation of | f Authorship                                       | xiii |

| A  | cknov   | wledge   | ments                                              | xv   |

| 1  | Intr    | oductio  | on                                                 | 1    |

|    | 1.1     | Motiv    | vation                                             | 1    |

|    | 1.2     | Resea    | rch Objectives                                     | 3    |

|    | 1.3     | Thesis   | s Organisation                                     | 4    |

| 2  | Mer     | nory a   | nd Learning: Biology and Engineering               | 7    |

|    | 2.1     | Introd   | luction                                            | 7    |

|    | 2.2     | Memo     | ory Consolidation Conceptually                     | 8    |

|    | 2.3     | The S    | ynapse: An Overview                                | 9    |

|    |         | 2.3.1    | Plasticity Mechanisms                              | 10   |

|    |         | 2.3.2    | Synaptic Metaplasticity                            | 12   |

|    | 2.4     | Comp     | outational Models                                  | 13   |

|    |         | 2.4.1    | Defining Memory Capacity                           | 13   |

|    |         | 2.4.2    | Memory Storage                                     | 14   |

|    |         | 2.4.3    | Cascade Metaplasticity Model                       | 14   |

|    |         | 2.4.4    | Palimpsest Consolidation Model                     | 16   |

|    | 2.5     | RRAN     | M Technologies                                     | 17   |

|    |         | 2.5.1    | An Overview                                        | 17   |

|    |         | 2.5.2    | RRAM Switching Mechanisms                          | 18   |

|    |         | 2.5.3    | RRAM Volatility                                    | 20   |

|    | 2.6     | Hardy    | ware Synapses                                      | 21   |

|    | 2.7     | Memi     | ristors as Neural Interfaces                       | 23   |

|    | 2.8     | Sumn     | nary                                               | 25   |

| 3  | Bidi    | irection | nal Volatility in TiO <sub>2</sub> RRAM            | 27   |

|    | 3.1     |          | duction                                            | 27   |

|    | 3.2     | Defin    | ing Volatility in RRAM                             | 28   |

|    | 3.3     |          | ectional Volatility: Characterisation              |      |

|    |         | 3.3.1    | Characterisation Methodology                       |      |

|    |         |          | 3 3 1 1 Stimulation Parameters and RRAM Relayation | 30   |

vi *CONTENTS*

|    |                                                    | 3.3.1.2 Volatility Proof of Concept                             | 32         |  |  |

|----|----------------------------------------------------|-----------------------------------------------------------------|------------|--|--|

|    |                                                    | 3.3.1.3 Characterisation Protocol and Sampling Space            | 34         |  |  |

|    |                                                    | 3.3.2 Effects of Stimulation Regime on Volatile Characteristics | 36         |  |  |

|    |                                                    | 3.3.2.1 Programming Pulse Amplitude                             | 36         |  |  |

|    |                                                    | 3.3.2.2 Programming Pulse Number                                | 37         |  |  |

|    |                                                    | · · · · · · · · · · · · · · · · · · ·                           | 39         |  |  |

|    |                                                    | 3.3.3 Characterisation Discussion                               | 41         |  |  |

|    | 3.4                                                | Bidirectional Volatility: Modelling                             | 42         |  |  |

|    |                                                    | 3.4.1 Modelling State Space and Methodology                     | 42         |  |  |

|    |                                                    |                                                                 | 42         |  |  |

|    |                                                    |                                                                 | 42         |  |  |

|    |                                                    | 3.4.2.2 Relaxation Time Constant                                | 44         |  |  |

|    |                                                    | 3.4.2.3 Stretch Factor                                          | 46         |  |  |

|    |                                                    | 3.4.2.4 Saturation Offset                                       | 47         |  |  |

|    |                                                    | 3.4.2.5 Model Simulation                                        | 49         |  |  |

|    |                                                    | 3.4.3 Modelling Discussion                                      | 50         |  |  |

|    | 3.5                                                | Thermal Effects on RRAM Volatility                              | 51         |  |  |

|    |                                                    | 3.5.1 Thermal Volatility State Space and Methodology            | 51         |  |  |

|    |                                                    | 3.5.2 Thermal Volatility Results and Discussion                 | 52         |  |  |

|    | 3.6                                                |                                                                 | 54         |  |  |

| 1  | D.12.                                              | masset Mamany Canaalidation                                     | 57         |  |  |

| 4  | 4.1                                                | i y                                                             | 57         |  |  |

|    | 4.1                                                |                                                                 | 58         |  |  |

|    | 4.2                                                | J .                                                             | 60         |  |  |

|    | 4.3                                                | J 1                                                             | 60         |  |  |

|    |                                                    | J 1                                                             | 63         |  |  |

|    | 4.4                                                | J                                                               | 67         |  |  |

|    | 4.4                                                |                                                                 | 67         |  |  |

|    |                                                    |                                                                 | 69         |  |  |

|    | 4.5                                                |                                                                 | 71         |  |  |

|    | 4.6                                                | o j                                                             | 73         |  |  |

|    | 4.7                                                |                                                                 | 75<br>76   |  |  |

|    | 4./                                                | Summary                                                         | 70         |  |  |

| 5  | Dete                                               | ection of High Neuronal Activity                                | <b>7</b> 9 |  |  |

|    | 5.1                                                | Introduction                                                    | 79         |  |  |

|    | 5.2                                                | Aim and Methodology                                             | 80         |  |  |

|    | 5.3                                                | Results and Discussion                                          | 81         |  |  |

|    | 5.4                                                | Summary                                                         | 84         |  |  |

| 6  | Con                                                | clusions and Future Work                                        | 87         |  |  |

| U  | 6.1                                                |                                                                 | 87         |  |  |

|    | 6.2                                                |                                                                 | 89         |  |  |

|    | 0.2                                                | radio 5 recommendations for future work                         | 09         |  |  |

| Aŗ | pend                                               | lix A Volatility Model Parameters                               | 93         |  |  |

| Αŗ | Appendix B Memristive Synapse Eligibility Study 95 |                                                                 |            |  |  |

| CONTENTS | vii |

|----------|-----|

|          |     |

| Appendix C Simulated Memory Network Set-up | 97  |

|--------------------------------------------|-----|

| Appendix C.1 STM Lifetime Statistics       | 97  |

| Appendix C.2 Network Model                 | 97  |

| Appendix D Contributions                   | 101 |

| Bibliography                               | 103 |

# **List of Figures**

| 1.1  | Main motivation of this thesis                            | 2  |

|------|-----------------------------------------------------------|----|

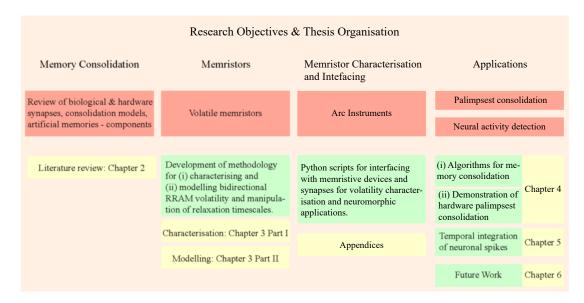

| 1.2  | Project objectives and thesis organisation                | 3  |

| 2.1  | Chapter's outline and objectives                          | 7  |

| 2.2  | Mechanisms of memory consolidation                        | 8  |

| 2.3  | Schematic model of neuronal synapse                       | 9  |

| 2.4  | Schematic illustration of LTP and LTD                     | 11 |

| 2.5  | Types of STDP in biological neurons                       | 12 |

| 2.6  | Cascade metaplasticity model                              | 15 |

| 2.7  | Synaptic metaplasticity on multiple timescales            | 16 |

| 2.8  | Non-volatile RRAM switching ( $\Delta R$ ) operation      | 19 |

| 2.9  | RRAM switching sensitivity and I-V curve                  | 19 |

| 2.10 | Neuronal spike detection using MIS                        | 24 |

| 3.1  | Chapter's outline and objectives                          | 27 |

| 3.2  | Typical volatility in TiO <sub>2</sub> RRAM               | 29 |

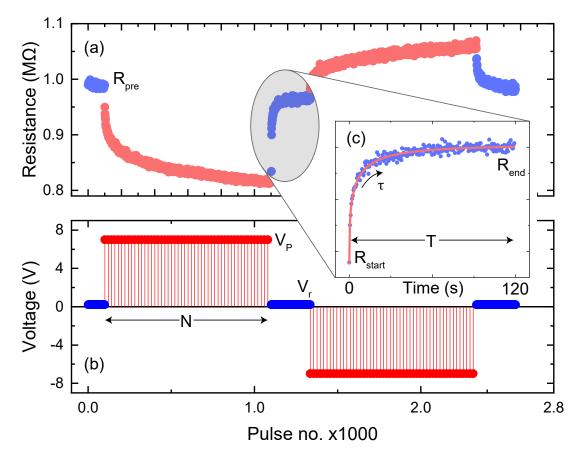

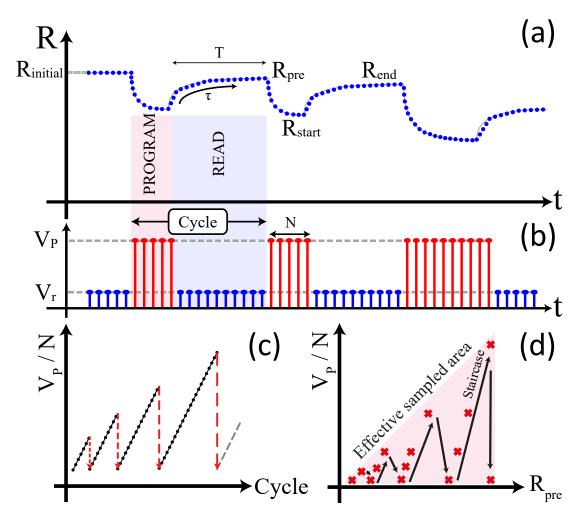

| 3.3  | Data sampling methodology for volatility characterisation | 31 |

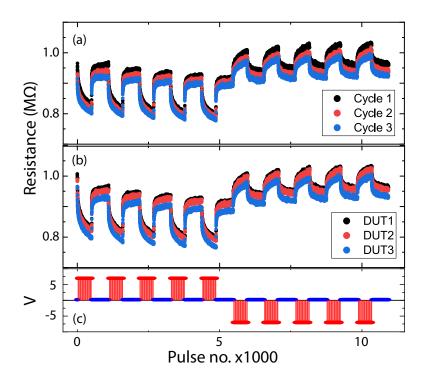

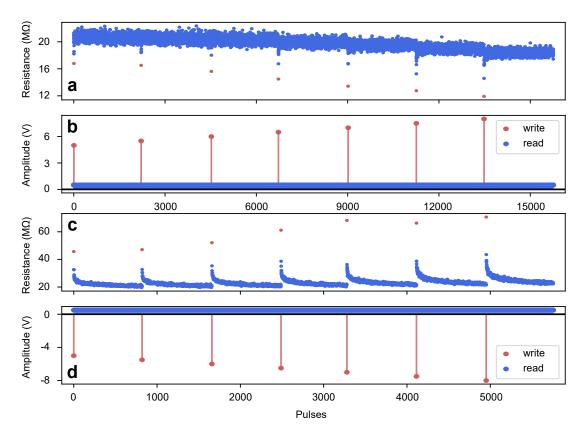

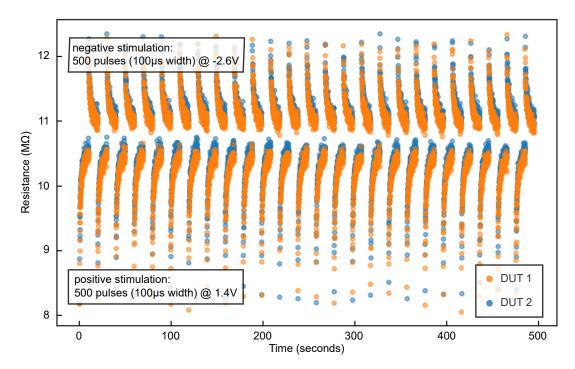

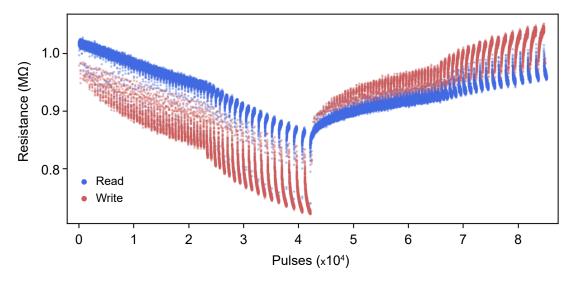

| 3.4  | RRAM volatility - repeatability test                      | 32 |

| 3.5  | Intra/interdevice volatility variability                  | 34 |

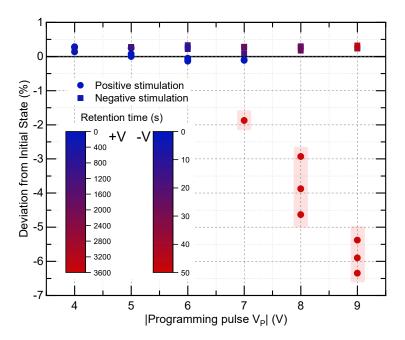

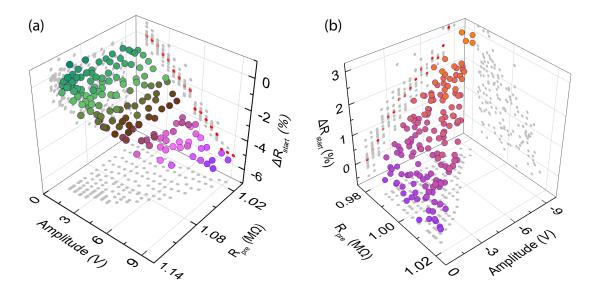

| 3.6  | Effect of stimulation amplitude $V_P$ on RRAM volatility  | 36 |

| 3.7  | Effect of pulse number N on RRAM volatility               | 38 |

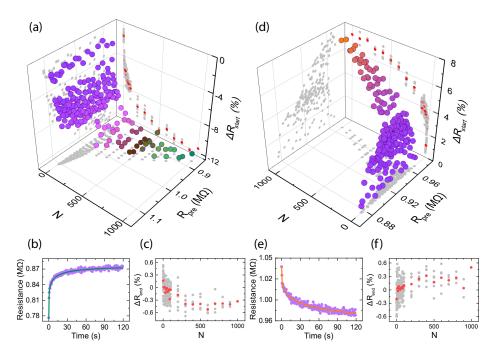

| 3.8  | Volatile RRAM relaxation constants                        | 40 |

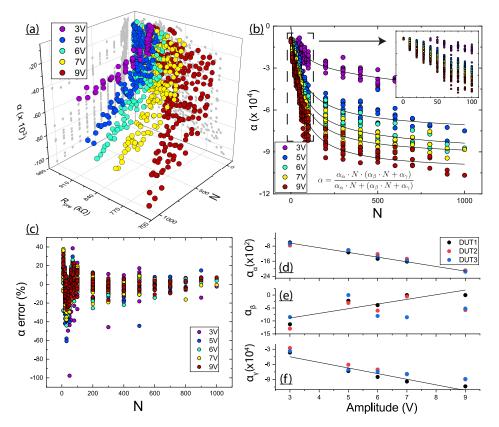

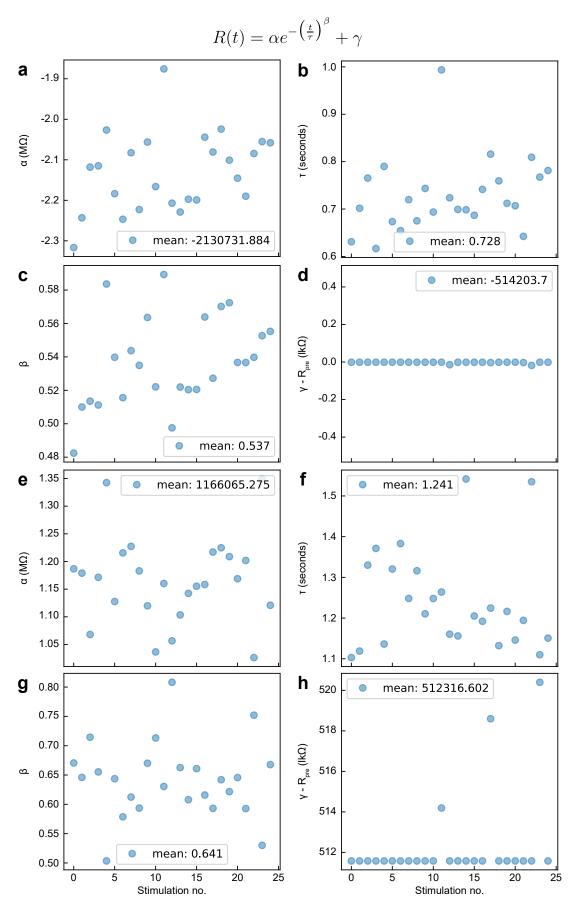

| 3.9  | Volatility modelling: switching component $\alpha$        | 43 |

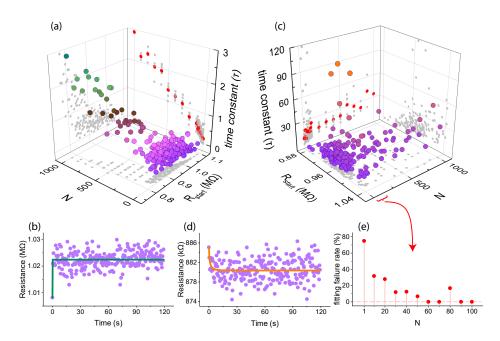

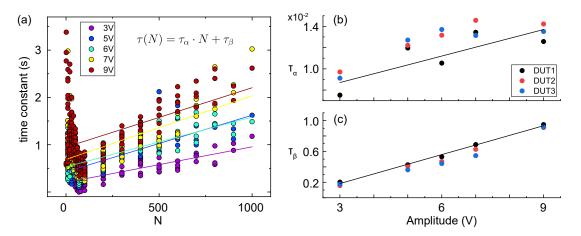

| 3.10 | Volatility modelling: time constant τ                     | 45 |

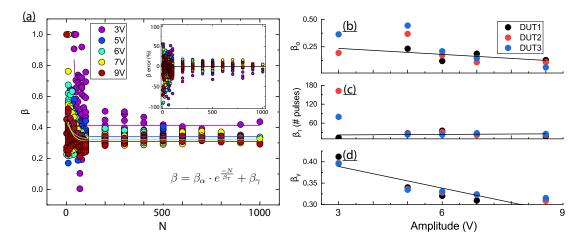

| 3.11 | Volatility modelling: stretch factor $\beta$              | 46 |

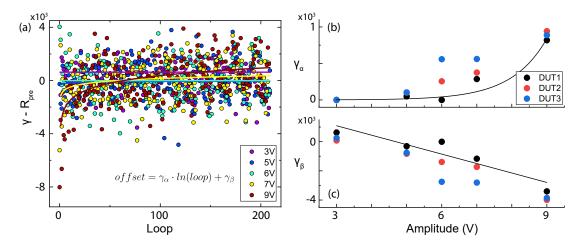

| 3.12 | Volatility modelling: non-volatile residue                | 47 |

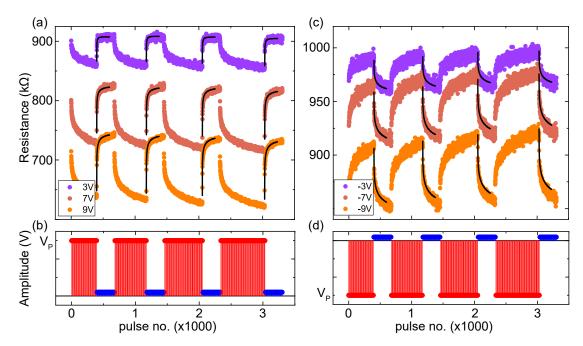

| 3.13 | Volatility modelling: simulation                          | 49 |

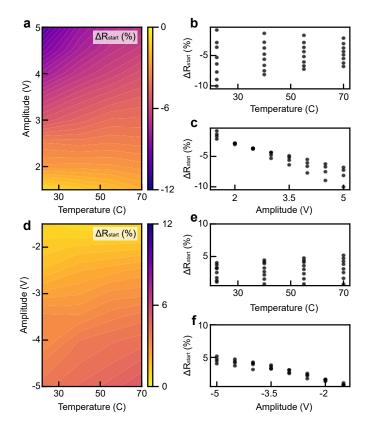

| 3.14 | Thermal volatility: volatile switching                    | 52 |

| 3.15 | Thermal volatility: relaxation time constant              | 53 |

| 4.1  | Chapter's outline and objectives                          | 57 |

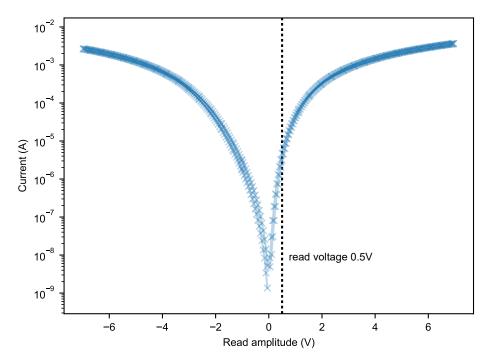

| 4.2  | I-V measurements on a $TiO_2$ memristive synapse          | 61 |

| 4.3  | Optimisation of $V_P$ in plasticity events                | 62 |

| 4.4  | Demonstration of a palimpsest memristive synapse          | 63 |

| 4.5  | Analogue state history of hardware memristive synapses    | 64 |

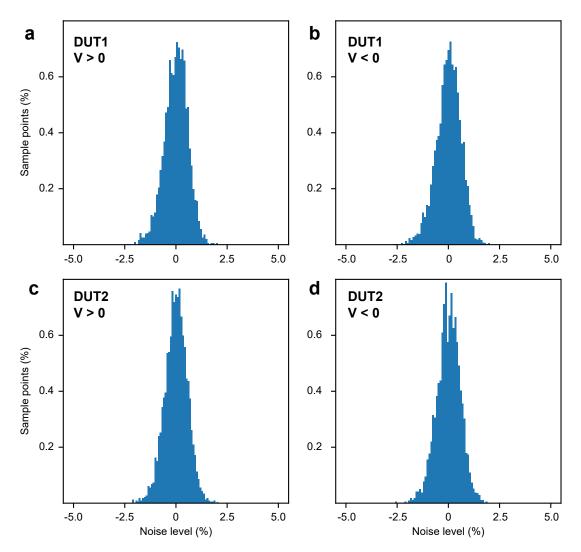

| 4.6  | Noise distribution of hardware synapses                   | 65 |

| 4.7  | Hardware palimpsest memory network                        | 66 |

| 4.8  | Retention study in RRAM synapses                          | 68 |

x LIST OF FIGURES

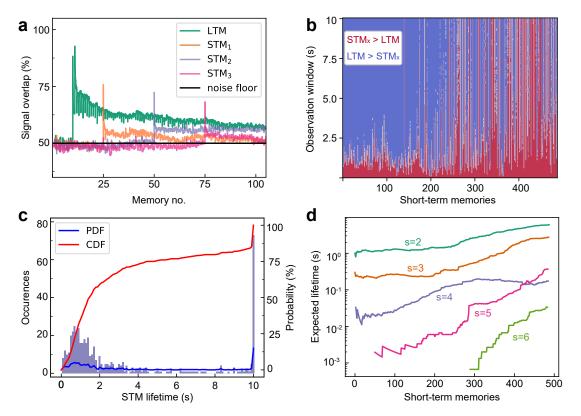

| 4.9  | Continuo                           | us uncorrelated memory stream                              | 69 |  |

|------|------------------------------------|------------------------------------------------------------|----|--|

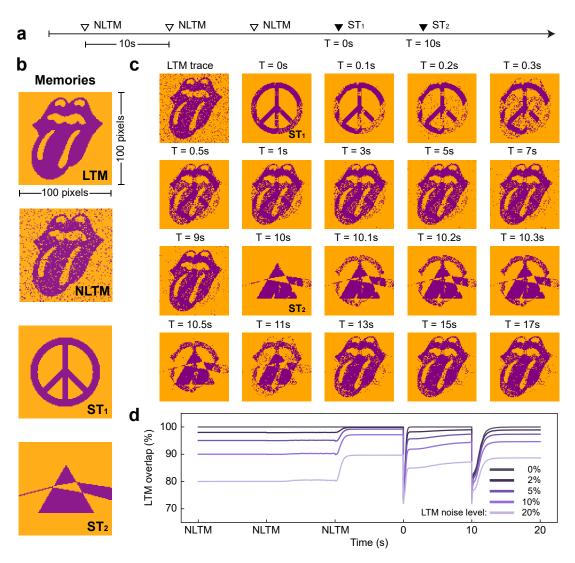

| 4.10 | Metaplast                          | ic memory network as visual working memory                 | 72 |  |

| 5.1  | Chapter's                          | outline and objectives                                     | 79 |  |

| 5.2  | Neuronal                           | activity detection: a schematic                            | 80 |  |

| 5.3  | Temporal analysis of neuronal data |                                                            |    |  |

| 5.4  | Neuronal                           | activity detection with volatile RRAM                      | 83 |  |

| Арр  | endix B.1                          | Long volatility study under positive stimulation           | 95 |  |

| App  | endix B.2                          | Long volatility study under bidirectional stimulation      | 96 |  |

| App  | endix C.1                          | Simulation model parameters for palimpsest memory network. | 98 |  |

| App  | endix C.2                          | Noise distribution for palimpsest memory network           | 99 |  |

# **List of Tables**

| 2.1 | Existing hardware implementations of artificial synapses        | 23 |

|-----|-----------------------------------------------------------------|----|

| 3.1 | Volatility characterisation protocol: model parameters          | 35 |

| 4.1 | From device to synapse to system level                          | 58 |

| 4.2 | Model operation parameters for palimpsest memory network        | 68 |

| 4.3 | Comparison of RRAM palimpsest synapses and previous implementa- |    |

|     | tions                                                           | 74 |

| Apr | pendix A.1 Volatility extracted model parameters                | 94 |

xiv LIST OF TABLES

### **Declaration of Authorship**

I declare that this thesis and the work presented in it is my own and has been generated by me as the result of my own original research.

I confirm that:

This work was done wholly or mainly while in candidature for a research degree at this University;

Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

Where I have consulted the published work of others, this is always clearly attributed;

Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work; I have acknowledged all main sources of help;

Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

Parts of this work have been published as:

C. Giotis, A. Serb, S. Stathopoulos, L. Michalas, A. Khiat and T. Prodromakis, "Bidirectional Volatile Signatures of Metal–Oxide Memristors—Part I: Characterization," *IEEE Transactions on Electron Devices*, vol. 67, no. 11, pp. 5158-5165, Nov. 2020, doi: 10.1109/TED.2020.3014854.

C. Giotis, A. Serb, S. Stathopoulos and T. Prodromakis, "Bidirectional Volatile Signatures of Metal-Oxide Memristors—Part II: Modelling," *IEEE Transactions on Electron Devices*, vol. 67, no. 11, pp. 5166-5173, Nov. 2020, doi: 10.1109/TED.2020.3022343.

T. Abbey, C. Giotis, A. Serb, S. Stathopoulos and T. Prodromakis, "Thermal Effects on Initial Volatile Response and Relaxation Dynamics of Resistive RAM Devices" *IEEE Electron Device Letters*, vol. 43, no. 3, pp. 386-389, March 2022, doi: 10.1109/LED.2022.3145620.

C. Giotis, A. Serb, V. Manouras, S. Stathopoulos, and T. Prodromakis, "Palimpsest Memories Stored in Memristive Synapses," *Science Advances*, vol. 8, no. 25, Jun. 2021, doi: 10.1126/sciadv.abn7920.

| Signed: | Data. |

|---------|-------|

| Signed. | Date: |

xvi LIST OF TABLES

### Acknowledgements

"The sooner you realise this is your work, your PhD, the better.", I was told on my first day. Some words to live by and, to a large extent, the truth. In this line of work progress comes only when you alone push for it and stops the moment you stop. Nevertheless, the work presented in this thesis is by no means an individual result. I have had the great fortune of collaborating with and being supported by beautiful minds as well as the joy of sharing this journey with colourful people.

First of all, I would like to express my immense gratitude to my supervisors *Professor Themis Prodromakis* and *Dr. Alexander* Serb for believing in my and sharing their passion for engineering artificial intelligence. Thank you so much. Your guidance has been instrumental in shaping my attitude towards conducting scientific research and envisioning a better future. Most importantly however, thank you for your continuous support and your unlimited energy for giving me advice along the way, in way transcending most professional relationships. My path will forever be a function of the experiences I have shared with you.

Equally importantly, I would like to thank my past and present friends and colleagues at the Centre for Electronics Frontiers and Southampton. Dr. Spyros Stathopoulos I couldn't make a comprehensive list even if I wanted to! Your selfless support in experimental design, software development and many more has helped me come where I am. Thank you for our late discussions, your unique take in life and for bringing me closer to the musical dark side! Dr. Loukas Michalas, you showed me very early in my PhD how to be a practical scientist - something I have carried on throughout this project. Thank you for your help, our talks and for showing me the best places in Southampton! Dr. Ali Khiat, your devices were amazing! Thank you for providing the foundation of my work. Vasilis Manouras, you set aside your own work to help when my PhD was on the line! Thank you for the beauties you fabricated, the music we shared and the endless laughs and discussions! Tom Abbey, our collaboration was great! Thanks for introducing me to the city's jam scene! Dr. Dimitra Georgiadou you were always a text away! Thank you for all your support, advice, the music and the movies! Vangelis and Ilias, we survived COVID together and we were there for each other's low days. I will always remember the camaraderie of Carlton House, thank you! Thodori, Eva, Kosta I laughed and shared with you. Art, walks, talks, the whole lot. You are beautiful, thank you!

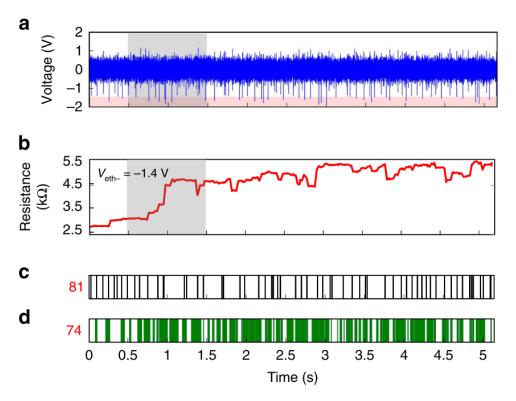

Moreover, I would like to acknowledge *Professor Koushik Maharatna* who has been my internal examiner throughout my PhD. Thank you for your valuable feedback regarding my work and my thesis structure. Also, I would like to thank *Professor Stefano Vassanelli* from the University of Padova for kindly collaborating with us and providing me with the data required to design the experiments presented in Chapter 5 of this thesis.

LIST OF TABLES xvii

I wouldn't be the person I am without my family. *Mom, Dad,* you've been together through thick and thin, you've given me and my sister the world and always with a smile. I couldn't have asked for a better place to grow up in. You are the perfect example - you have never given up, always hopeful and have always worked towards sharing a better tomorrow with us. You taught us how to love and be loved and for that we will always be complete. My sister *Eirini*, my number 1. You are my best friend, always eager to understand me and selflessly support me. I only hope I am your equal in those regards. I cannot wait to share the rest of my life with you friend! To all of you, thank you. Those who live without love see the world in black and white, play music with half the notes. Our life together is a vibrant colour explosion, the loudest, most playful concert for the ages. It's us four for life.

My work, my aspirations, my life would mean nothing if I couldn't share it with true friends. Nikola and Dorry, we met as children and became men together. We dreamt wild dreams and did stupid things - I wouldn't change anything. You are my brothers, my life with you has been a trip, thank you for everything! Pano, we climbed mountains together, saw Athens for what it is and what it could be and became family. May we keep climbing. Georgina you are the fire I wish will always keep burning in my life. Be who you are, passionate and feisty and let's roam free through everything! I will always be here for you! Petro my free spirit, your life is an adventure and I am so happy to be a part of it. Thanks for watching floating cities in the skies with me, Pegasus will always be there for us. Niko, Mike, Iasona, you have celebrated with me at my best, you've picked me up at my worst. I can only do the same for you. Our band is a beautiful incoherence and I love every minute of it. Ruth, Stelio, Niko, Filippe, I know you forever and you have never stopped bringing joy and laughter in my life. Always looking out for each other, dreaming, dancing and tasting together. I don't want to think of a life without you, I want to be here for you and hope we will share our futures together! I wish all of you nothing but fortune in your lives. I wish you the energy to materialise all your dreams and live free in the way you choose to! Thank you all for being part of me - the best is yet to come!

And no one showed us to the land And no one knows the where's or why's But something stirs and something tries And starts to climb toward the light. - Pink Floyd

Life, like science, is art. Art that is passionate and audacious. We seek to find hidden truths and translate them to our language. Seek on, seek free.

Love, Freedom, Passion, Good Vibes and a Smile,

Christos Giotis (2022)

xviii LIST OF TABLES

To my beloved Grandmother Rinoula. My second mother, feisty and loving, who was over the moon when she learnt I was going to be a man of science. I carry your memory with me every day.

This one is for you Yiayia. Love.

# Chapter 1

## Introduction

### 1.1 Motivation

Progressive deciphering of the human brain and its constituent processing methods has inspired phenomenal advances in Artificial Intelligence (AI) in recent years [1]–[3]. The capabilities of deep learning algorithms and artificial neural networks (ANNs) have already transformed modern societies. ANNs employ finely tuned neuronal layers which perform statistical learning over input data for a given state space. This process yields great generalisation performance **over single or highly correlated learning tasks** such as image classification, speech recognition and natural language processing [4], [5]. Owing to this, AI is set to be further adopted in executable tasks [6] with strong attention on embedding it on edge-systems [7], [8].

Yet, it is evident that current deep learning algorithms bring strong inefficiencies towards realising artificial general intelligence (AGI) even in a centralised (cloud-based) environment. For context, using a comparable number of trainable synapses (the biological learning unit), approximately  $10^{13}$ - $10^{14}$ , biological neural networks in the cerebral cortex facilitate general cognition [9], [10], a capacity much larger than their engineered counterparts. ANNs cannot achieve this capacity by learning sequentially since incoming synaptic modifications impose destructive interference on the networks' state, known as *catastrophic forgetting* [11]. In other words, ANNs must forget old memories in favour of new ones. The adoption of AI in more learning tasks of increasing complexity thus arrives at the cost of ever-increasing computational and memory resources [7], [12], [13]. Artificial memory is further challenged by the limits of Moore's law [14] prohibiting the scaling of ANNs in form factors small enough for AGI on the edge.

To address this challenge, strong focus has been put on loading AI's operations on complementary processing methods. Graphics processing units (GPUs), tensor processing units (TPUs), field-programmable gate arrays (FPGAs) and other specialised CMOS-based circuitry [15]–[18] allow more efficient, accelerated training and deployment of

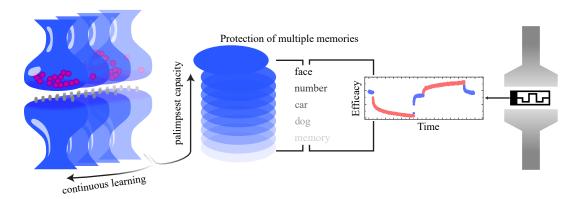

FIGURE 1.1: Motivation of this thesis. A solution to the discrepancy of learning capacity between biological and artificial synapses and catastrophic forgetting by emulating biological consolidation in volatile memristors.

software-based ANNs. Concurrently, more specified neuromorphic technologies aim to directly emulate brain and learning functions in hardware, completely bypassing the need for software implementations of ANNs [19]–[22]. The appeal of neuromorphic systems first rises from attributes such as learning speed and energy efficiency [23]. To date though, neither implementation has demonstrated a solution to catastrophic forgetting. Since ANNs need to increase exponentially in size to yield linearly higher accuracy [24], it is natural to look for different approaches in increasing learning capacity.

One such approach seeks to increase the re-usability of ANNs allowing the same synapses to be used for **multiple and uncorrelated tasks**; a property naturally observed. Biological synapses are able to consolidate multiple memories which can be revealed at different timescales - much like a palimpsest [25]. Synapses can remember long-term plasticity events, namely potentiation (LTP) and depression (LTD) while expressing altered states in the short-term [26]. This temporal partition enables the brain to use the same resources for multiple computation processes and offers a practical partition to the issue of catastrophic forgetting.

Palimpsest storage is realised biologically via the bidirectional interaction of hidden biochemical processes affecting the manifestation of synaptic efficacy at different timescales [25], after each memory modification. These processes are characterised by their own degrees of plasticity (i.e. learning rates) and lifetimes (i.e. 'forgetting time constants'). These properties make memristive devices natural candidates for hardware palimpsest consolidation, which have already showcased their potential in synaptic emulation [20], [21], [27]–[29]. In particular, frequently overlooked volatile resistive RAM (RRAM) families are also governed by hidden electrochemical processes affecting their analogue state, much akin to biological synapses. Thus, the primary motivation of this thesis has been the harnessing of RRAM's intrinsic volatile properties to consolidate multiple uncorrelated memories at different timescales and at palimpsest fashion (see

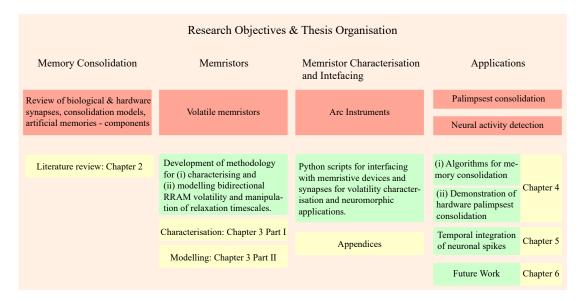

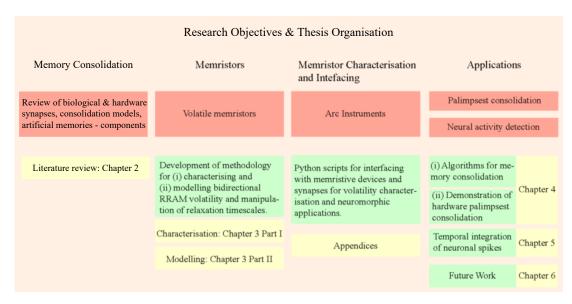

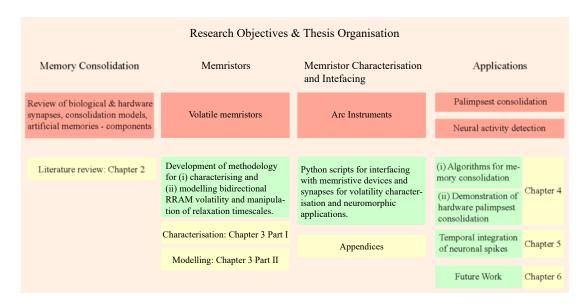

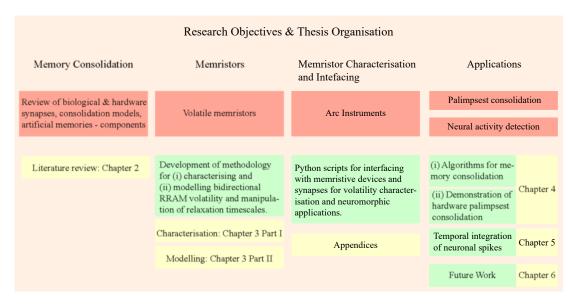

FIGURE 1.2: Project objectives and thesis organisation.

Figure 1.1 for a high-level description). If appropriately tuned bidirectionally, the relaxation dynamics of RRAM can replicate the hidden biochemical states that protect memories from synaptic modifications. Such memristive synapses can address catastrophic forgetting and pave the way for AI hardware that can learn on the Edge.

### 1.2 Research Objectives

The research objectives of this project are as follows:

- 1. Assess the candidacy of volatile RRAM technologies for emulating synaptic memory consolidation.

- 2. Characterise the intrinsic time-dependent signatures of RRAM volatility.

- 3. Accurately model the intrinsic time-dependent signatures of RRAM volatility.

- 4. Demonstrate in hardware how palimpsest memory consolidation can naturally arise via volatile RRAM.

- 5. Extend the technology's principal operations towards further neuromorphic applications.

To achieve the objectives of this project a number of key steps have been taken (see Figure 1.2 for an objective outline and the subsequent thesis organisation). Firstly, a thorough review has been conducted to verify the suitability of  $\text{TiO}_x$ -based RRAM technologies for palimpsest memory consolidation. This review has covered relevant neuroscience theories of synaptic operations and memory consolidation, a background

foundation of memristive devices as synaptic emulators as well as key hardware and software learning implementations. RRAM can efficiently replicate plasticity events either in the form of LTP or LTD and plasticity rates can explicitly be modulated via appropriate stimulation tuning. Moreover, it has been concluded that RRAM volatility could provide a reference to the hidden relaxation properties of biological synapses. However, no volatility framework that could be utilised to express the necessary timescales bidirectionally has been found to exist.

Thus, **secondly**, this project has set to develop a complete framework for both characterising and modelling RRAM volatility bidirectionally. This framework aims to decipher the relationship between relaxation timescales and plasticity stimulation to support appropriate interfacing with memristive synapses. This study has shown that RRAM volatility is governed by two distinct timescales; a fast volatile regime and a slow non-volatile residue after stimulation. **Thirdly**, necessary 'bridging' algorithms have been designed to manipulate memristive volatility both in hardware and in simulations and replicate basic synaptic functions. The volatile and non-volatile timescales have been exploited to realise a fast learning, plastic short-term memory and a slower but more rigid long-term compartment in a single device.

Fourthly, experiments have been designed to demonstrate automatic palimpsest consolidation in volatile RRAM synapses using this dual memory capacity, accompanied by explanatory data analysis. These experiments have practically demonstrated that volatile synapses can consolidate memories in the long-term capacity and automatically protect them against multiple short-term memory modifications. This proof of concept in hardware has satisfied the main motivation of this thesis. Finally, owing to the ubiquity of intrinsic time referencing in biology, this project has aimed at applying volatile learning properties in further neuromorphic applications. This has been carried through in the general context of brain-computer interfacing (BCI). There, single devices have shown great potential in encoding high neuronal spiking activity without a need for pre-processing spiking data.

### 1.3 Thesis Organisation

This thesis is organised as follows. Chapter 2 surveys the literature to give an overview of memory and learning in biology and in computational models, as well as of recent engineered implementations. This includes a description of biological synapses, their main plasticity mechanisms and mathematical descriptions of memory consolidation to form the theoretical foundation of this work. Moreover, an introduction of RRAM technologies and their core properties is made, followed by a review of memristive technologies' involvement in artificial synaptic learning and in neuronal interfacing. Chapter 3 presents novel methodologies for characterising and modelling memristive

volatility under various ranges of operating conditions. The experimental results presented in this chapter link to the theory behind memory consolidation to form the foundation of the main application designed in this thesis. In Chapter 4, memristive volatility parameters are translated into synaptic stimulation protocols to demonstrate palimpsest memory consolidation in hardware. The results are both experimental and simulated and provide a thorough analysis of volatile memristor suitability for learning applications. Chapter 5 presents a brief proof of concept study on how the same learning properties of volatile memristors can be utilised to perform unsupervised temporal integration of neuronal spikes for high activity detection. Finally, Chapter 6 summarises this thesis and provides the author's recommendations on future extensions of this work.

# **Chapter 2**

# Memory and Learning: Biology and Engineering

### 2.1 Introduction

The ability to learn, recall and consolidate memories is a fundamental aspect of biological and artificial intelligence. Memory consolidation and learning occur biologically via the synapse, an 'adjustable connection' between neurons which regulates the transmission of signals in the brain. Naturally, this has drawn extensive scientific attention both towards understanding synaptic mechanisms as well as engineering them. This chapter introduces the synaptic mechanisms required for learning, both biologically and computationally, and gives an overview of how these mechanisms can be reverse-engineered for artificial intelligence and further neuromorphic applications.

FIGURE 2.1: Chapter's outline and objectives.

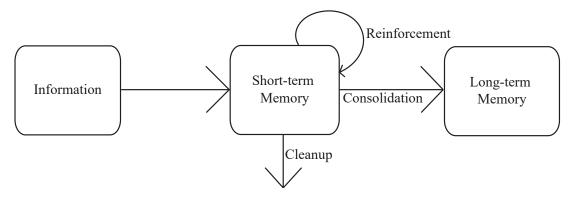

FIGURE 2.2: Mechanisms of memory consolidation. Information is initially stored in a fast and labile short-term memory. Reinforcement of memory enables it to be consolidated into a slower but stable long-term memory. A cleanup mechanism is required to ensure forgetting of information deemed unimportant to the system.

### 2.2 Memory Consolidation Conceptually

Efficient handling of information in any learning system requires both mechanisms for retaining important memories and equally importantly, forgetting less significant ones. The human brain deals with this challenge by storing memories in distinct short and long-term time phases [30] [31]. While the information in the short-term memory is easily recorded, it is also easily forgotten. Contrarily, information in the long-term memory is recorded with more difficulty but is also more stable [30]. This mismatch of stability can act as a cleanup filter in any learning system, whereby information that has not been forgotten in the short-term can progressively be stored more securely. The process of transferring information from the labile short-term phase to the more stable long-term memory is referred to as *memory consolidation* [32].

At a higher level, consolidation of memory can be perceived as a controlled process. For it to function, the system needs the two types of mentioned memory systems and four mechanisms; signal transfer, positive reinforcement, a threshold metric and cleanup. A heuristic approach is the following. Consolidation occurs via the transfer mechanism which moves information to the system's long-term memory. The transfer may only be triggered if a threshold condition has been met. In turn, memories can meet this condition if they are reinforced in the short-term. All memories that fail to reach the transfer threshold are discarded by the cleanup mechanism. Crucially, both the memory stages and the mechanisms are orthogonal modules of the consolidation model and in theory, they can be implemented in numerous ways both in vivo and in silico. A higher level depiction of the model is shown in Fig. 2.2.

Importantly, consolidation can occur both at a systems level and at a memory-unit level. That is, the distinction between short and long-term memory can either be spatial or structural within the storage system respectively. The spatial consolidation paradigm

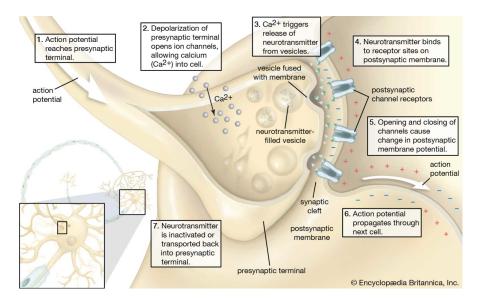

FIGURE 2.3: Neurotransmitter release during synaptic operation [37]. The electrical signal from the presynaptic neuron is converted into chemical information through neurotransmitters and back to electrical form in the postsynaptic neuron.

is employed in conventional computing where fast but volatile RAM devices consolidate data to slower but stable hard drives. Evidence for systems consolidation in the brain involves the transfer of information from the hippocampus (*short*) to the neocortex (*long*) [33] [32]. At the unit level, consolidation can occur through changes in protein concentrations in the synapse [30] [34].

### 2.3 The Synapse: An Overview

Information processing occurs in the human brain via signal transfer between individual neurons. This signal has the form of short spikes of electrical current (Fig. 2.3 (1)) propagating from the outward end of a transmitting neuron (*axon*) to the inward end of a receiving neuron (*dendrite*) [9] [35]. The junction between these two elements is termed *synapse* and it is widely considered the principal unit of memory and computation within the brain [9] [36]. In reality, this form of neural communication is not the only one that has been observed [9]. This work, however, only considers the synapse as a connection between a transmitting (*presynaptic*) and a receiving (*postsynaptic*) neuron.

Conceptually, it is very important to understand a reduced model of how a synapse operates, to appreciate how it can function both as the memory and the computational unit of the brain. Generally, synapses can be categorised into two major types; excitatory and inhibitory. Excitatory synapses activate the postsynaptic neuron when triggered and inhibitory ones stop the electrical signal flow [9]. While information is both transmitted and received by neurons in electrical form, the synapse operates with slower, biochemical processes and makes use of concentrations of specialised molecules

called *neurotransmitters* [9] [38]. Such molecules are contained and released within *synaptic vesicles*, "packets" of quantised amounts of molecules.

The electrical potential induced by a presynaptic neuron triggers a change in potential difference within the synapse. This in turn releases quantised amounts of neurotransmitters (Fig. 2.3 (3,4)) which carry the signal to the postsynaptic neuron (Fig. 2.3 (5,6)). This signal can either be of excitatory (e.g. in the case of Glutamate-mediated synapses) or inhibitory (e.g. GABA) nature [39] [9]. Specifically, the effect of either excitatory or inhibitory events is determined by the number of vesicles released. The more excitatory neurotransmitters are released, the more likely the postsynaptic neuron to fire. Conversely, the more inhibitory neurotransmitters are released, the less likely is for the neuron to fire. The release of synaptic vesicles depends on the level of presynaptic activity. However, the number of (available) vesicles formed within the synapse can be variable and their synthesis depends on the history of synaptic activity [9]. The degree of likelihood that a synapse releases a specific amount of neurotransmitters and thus excites or inhibits the postsynaptic neuron is called synaptic efficacy. Efficacy is the equivalent of the weight of a connection in an artificial neural network (ANN). In turn, the mechanism by which efficacy changes is called synaptic plasticity and its two sides are potentiation, i.e. increase in efficacy and depression, i.e. decrease in efficacy.

### 2.3.1 Plasticity Mechanisms

Synaptic plasticity refers to mechanisms by which synaptic efficacy is modulated. It is explicitly activity-dependent, meaning that it is reactive to signalling neuronal inputs and is widely regarded as a primary facilitator of biological memory [40]. Plasticity can be categorised using various metrics. Most notably, it can be distinguished by the lifetime of the efficacy changes it induces (short- and long-term plasticity), as well as by the underlying mechanisms facilitating it. Additionally, higher levels of plasticity can be identified and in fact, are considered to be key mechanisms of memory consolidation. This section will give a conceptual overview of these characteristics since they will be a recurring topic in the next chapters of this thesis.

First, synaptic efficacy is known to be modulated for short-lived timeframes by what is termed short-term plasticity. The mechanism has been recorded in numerous organisms of varying complexity and is believed to have lasting ranges from milliseconds to minutes [41]. Typically, short-term plasticity is expressed relative to paired-pulse stimulations, whereby an input pulse can affect a synapse's response to a closely spaced subsequent pulse. Short-term plasticity can facilitate both an increase (facilitation) and a decrease (depression) in efficacy. The plasticity direction is normally determined by the temporal interval between pulse sequences, with small interpulse periods (< 20ms) typically (but not always) leading to short-term depression and larger (20-500ms) to

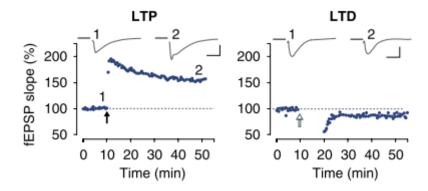

FIGURE 2.4: Schematic illustration of LTP and LTD, shown as the increase and decrease of the field excitatory postsynaptic potential (fESP) in the hippocampus over the timeframe of 1 hour [40].

short-term facilitation [41], [42]. Short-term plasticity is believed to provide biological brains with filtering capabilities. Specifically, since high-frequency stimulation can cause short-term depression, high-efficacy synapses can respond to sparse signals with high accuracy but may dampen denser input signals; effectively acting as a low-pass filter. Equivalent but opposite relationships can turn low-efficacy synapses into high-pass filters [43].

While short-term plasticity and its associated filtering capabilities can provide some interesting properties in neural networks, experiences perceived by the brain can also induce long-term changes in synaptic efficacy. These changes occur concurrently at ensembles of synaptic circuits and have been reported to persist for hours to days in mammalian brains [44], [45]. Such actions result in the permanent or semi-permanent rewiring of biological neural networks, which is the foundation of all learning. Long-term plasticity takes form both via potentiation (LTP) and depression (LTD), which are umbrella terms for various mechanisms governing efficacy modulation in multiple brain regions and for multiple purposes [40]. An illustration of both mechanisms is shown in Fig. 2.4. Particularly, the co-existence of both LTP and LTD within individual synapses and the corresponding bidirectional nature of efficacy [46], is a key justification for perceiving synaptic memory as an analogue weighted value - a perception which is a pillar of modern deep learning algorithms [1].

One of the most widely studied mechanisms for inducing long-term plasticity is spike-timing-dependent plasticity (STDP). This mechanism is of great interest since it is also the main learning rule of neuromorphic applications [23]. STDP is aligned with the long-standing Hebbian learning rule, which proposes the existence of a mechanism for increasing the signal transmission efficiency between neurons that tend to communicate frequently [47]. This is commonly summarised by the popular heuristic 'neurons that fire together, wire together', which effectively suggests that synaptic plasticity must act as a mechanism for learning in neural networks.

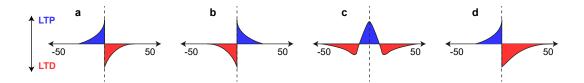

FIGURE 2.5: Types of STDP in biological neurons. The x-axis measures the temporal difference between the presynaptic and postsynaptic firing  $t_{pre}$  -  $t_{post}$  in milliseconds (ms). LTP and LTD are colour-coded in blue and red respectively.

In its basis, STDP between a presynaptic and a postsynaptic neuron is determined by the temporal relationship of their activity. STDP is determined by the magnitude of the time difference between spiking events occurring at two neurons,  $t_{pre}$  -  $t_{post}$ , as well as the sign of this value. Most pronounced plasticity changes occur at time differences of 25-50ms, although many different directions have been observed (see Fig. 2.5 for common examples as described in [48], [49]). Most neuromorphic applications follow the learning rule shown in Fig. 2.5a [23], [29]. If the firing of a postsynaptic neuron succeeds that of the presynaptic neuron then the corresponding synapse undergoes LTP; conversely, if the postsynaptic firing precedes the presynaptic then the synapse undergoes LTD.

Strong association between LTP/LTD and memory can also be drawn due to their similar underpinning properties [50]. First, plasticity can be reinforced via repetition. Second, the change in a synapse's efficacy is correlated to the strength of an input signal. Moreover, the mechanisms by which plasticity is facilitated are mostly intrinsic to individual synapses, meaning that they do not affect their neighbours and give rise to the incredible degree of freedom found in learning brains.

### 2.3.2 Synaptic Metaplasticity

It is evident that synaptic plasticity is a key facilitator of biological memory. Changes in synaptic efficacy 'rewire' neural networks and regulate their function, thereby altering their output to specific inputs and thus enabling learning. Nevertheless, plasticity itself cannot account for memory consolidation and/or protection. After all, reinforcement can aid plasticity but it does so bidirectionally. In other words, modifications in efficacy, caused by ongoing input signals between neurons inevitably cause the degradation of older memories [25]. Intuitively, this would mean that brains should constantly keep forgetting memories in favour of new ones.

The mechanism that is regarded to be protecting memory degradation in the synapse is metaplasticity. Metaplasticity can be thought of as a higher-level attribute of synaptic plasticity. It describes the mechanism by which a synapse can undergo changes to its degree of plasticity [51]. Metaplasticity thus does not refer to the absolute changes of

synaptic efficacy but to the freedom by which efficacy can change. For instance, it has been observed that synapses in the hippocampus may be subject to stimulation that can favour LTD and limit LTP in the future [52], [53].

Synaptic metaplasticity can solve the challenge of protecting consolidated memories in the brain and thus has been a big inspiration for this project. While there are still many unknowns as to how plasticity is regulated molecularly, biological evidence for its existence has been observed [33], [54]. Moreover, computational neuroscience has made significant progress in approximating these effects. The next section will cover some key computational aspects of memory consolidation and protection, which have been utilised in the design of artificial synapses throughout this work.

### 2.4 Computational Models

### 2.4.1 Defining Memory Capacity

As it is outlined in Chapter 1 and will later be discussed in detail in Chapter 4, the primary aim of this work is to realise palimpsest memory consolidation in a hardware implementation. Since this involves the coexistence of multiple memory states within a system, it is imperative that a clear metric is defined to distinguish between palimpsest and non-palimpsest memory consolidation. To find such a metric, this work considers the possible different states that a memory unit can concurrently hold *without forgetting old information*. Importantly, the co-storage of multiple states could theoretically occur both concurrently (being able to read/recall multiple states from a memory unit at the same time) or could be partitioned in time. The latter would involve overwriting a memory state for some time while retaining the ability to reverse back to a previous state after that time has elapsed. Such an ability is believed to be present in biological synapses, has already been formulated mathematically (see Section 2.4.4 of this chapter) and is the primary inspiration for this work.

Accordingly, this work defines the *capacity* of a memory system as the total number of states that can be arranged in a temporal palimpsest fashion. For example, a typical SSD memory unit can only store 1 state since it cannot be retrieved when overwritten. A theoretical system which could store an N-th signal while retaining the ability to recall the previous N-1 signals would have capacity N. This definition should be distinguished from conventional definitions of memory capacity in the context of information theory (i.e. bits as units of signal entropy [55]) which is largely used to evaluate artificial memories [56], [57]. For example, if a theoretical memory unit can take 4 distinct states with equal probability but can only do so irreversibly with respect to previous states, then its capacity within the context of this work will be equal to 1 state and not 2 bits. Therefore, since no practical demonstration of palimpsest memory consolidation has been

shown in hardware, we can deduce that all known memory systems have a capacity of 1 state and thus the main aim of this work can be rephrased to simply demonstrate a memory capacity greater than 1.

### 2.4.2 Memory Storage

Memories are retained in the brain through changes in the efficacies of relevant synapses. To better understand this notion certain assumptions should be made. Firstly, every experience that can be remembered, can also be translated into some input stimulus on some neural ensemble. Secondly, this input has the form of presynaptic spikes directed towards some postsynaptic neurons. This activity in turn induces plasticity changes in the set of synapses connecting the neurons activated while the experience is recorded. Memory traces of a given experience can then be remembered as long as the efficacies of those synapses remain close to the values prescribed by the experience [25].

Specifically, traces of a stored memory within an ensemble of synapses lie in the modifications in their synaptic efficacies. The memory signal is strongest immediately after modification occurs. The ongoing plasticity events induced in the memory system add noise to the memory trace which is assumed to decay over time. At any point, the memory signal can be computed as the "overlap between the state of the synaptic ensemble and the pattern of modifications originally imposed by the memory being remembered" [58] (see Chapter 4).

The brain comprises a finite number of synaptic connections, the efficacy of which is limited by bounded values. Since memories are retained by ensembles of synapses, those bounds also limit the possible combinations of efficacies, i.e. memories that can be stored. Moreover, the efficacy of a given synapse undergoes ongoing plasticity changes which constantly add noise to the traces of older memories. Yet the human brain exhibits the ability to recall information for years and still keep storing new memories. Computational metaplasticity models offer a perspective on how this is achievable and an inspiration for engineering equivalent mechanisms.

### 2.4.3 Cascade Metaplasticity Model

Using a metaplastic metric, a synapse can vary from being completely *rigid* (i.e. not liable to plasticity changes) to *plastic* (i.e. very prone to plasticity changes). From a memory consolidation perspective, designing a metaplastic synapse ensures the short and long-term memory types at a structural level, as mentioned in Section 2.2.

Computationally, metaplasticity can be visualised using the cascade model of a binary synapse, developed by Fusi et. al. [59]. The synapse can obtain two efficacy states,

FIGURE 2.6: Cascade model of metaplastic synapse. Binary efficacy values consist of weak and strong. Each potentiation event induces a plasticity change towards plastic strong<sub>1</sub> state with transition probability  $q_i$  if a synapse is in weak<sub>i</sub> state. Importantly, plasticity transition  $q_i$  becomes exponentially less likely for higher values of i. Alternatively, it consolidates memories into more rigid  $strong_i$  metaplastic states with transition probability  $p_i^+$ , if the synapse is in state  $strong_{i-1}$ . Each depression event acts respectively on the synapse for metaplastic transition probabilities  $p_i^-$ .

potentiated and depressed. Metaplasticity works as a hidden variable, where continuous plasticity events of equal polarity push the synapse deeper into states i with lower efficacy transition probabilities,  $q_i$ . The model is illustrated in Fig. 2.6 [59]. Referring to Section 2.2, the *reinforcement* mechanism of the system is the repetition of plasticity events and the *transfer* mechanism is the transition to different metaplastic states. Information is consolidated by being "entrenched" into more stable states, while information that is not reinforced can easily be overwritten.

The cascade model provides a straightforward explanation of how metaplasticity aids memory consolidation. However, it is not robust enough to support consolidation in general forms. This has been recently demonstrated in the case of binarised neural networks that employ weights with cascade metaplastic properties [60]. There, it is shown that such networks can only generalise over multiple tasks/memories which are highly correlated. This can be intuitively understood since cascade synapses can only hold one binary state which is catastrophically forgotten as soon as it is changed. Cascade metaplasticity thus favours a form of static consolidation by a binary approach towards interfering memories: either incoming memories are completely ignored if the synapse is rigid or are written by permanently overwriting the existing state. While this paradigm has been proven useful in expanding the storage of correlated memories which share the same efficacy states [60], it still challenges online AI in real learning scenarios where the nature of incoming memories is unknown a priori. What is needed is the flexibility to learn uncorrelated memories fast, and concurrently protect older consolidated counterparts. Importantly, this should be done automatically and in an unsupervised manner.

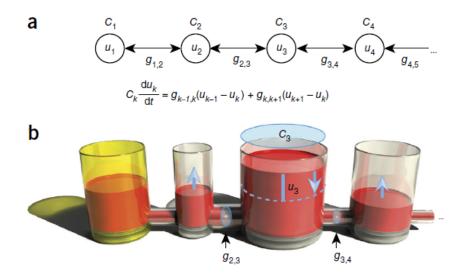

FIGURE 2.7: Synaptic model. (a) Chain plasticity model consisting of  $u_k$  biochemical processes, where  $k \in [1, m]$ , for m different processes. Each variable interacts with its neighbours, while  $u_1$  is connected to  $u_2$  and the input and  $u_m$  communicates with  $u_{m-1}$  and a leak term (equivalent to  $u_{m+1} = 0$ ). Parameters  $g_{k,k+1}$  are the strengths of the interactions between two variables. Combined with  $C_k$ , they determine the timescale on which each process operates. (b) Intuitive illustration of hidden variables. The chain model behaves like an ensemble of communicating beakers. Each variable  $u_k$  measures the deviation of each variable from the equilibrium, as shown with  $u_3$ . Variables  $g_{k,k+1}$  represent the connection weight between two beakers and  $C_k$  reflects the area/volume of each beaker.

### 2.4.4 Palimpsest Consolidation Model

An explanation for the brain's incredible learning capacity would be that a specific synapse is used for the storage of multiple memories. Memories then, are not stored statically in a *one next to the other* fashion but are more likely to be stored in a palimpsest fashion, i.e. *one on top of the other* [61]. In such a scenario, however, plasticity events triggered by multiple memories stored in a given synapse, deviate its efficacy from values that would suffice for recalling previously stored memories.

The challenge of storing and retaining memories is encompassed by the *plasticity / rigidity dilemma* [11]. Plastic synapses are good at storing new information but their liability to further plasticity events makes them forget as easily. Rigid synapses are good at retaining old information but they fail at storing new memories. As proposed by Fusi et.al. [25], for consolidation to occur at a synaptic level, metaplasticity has to be multidimensional and a synapse must contain both plastic and rigid components. The authors argue that memories are retained by multiple biochemical processes, operating at different timescales and interacting with each other bidirectionally. Visualisation of such interaction is provided in Figure 2.7 [25].

This synaptic model consists of a visible weight w(t) and multiple hidden variables operating at progressively slower timescales. Computationally, this is described by

a chain model. The first element of the chain is the synaptic weight and is also the most plastic component. Its value is very sensitive to plasticity events, resulting in high initial memory strengths. The remaining chain elements represent the hidden variables affecting synaptic metaplasticity and equilibrate around the average values of their neighbours (Fig. 2.7a).

The chain model can be expressed by a chain of communicating liquid beakers (Fig. 2.7b). The yellow beaker represents the synaptic weight and the most plastic component. Potentiation events equate to adding liquid to this beaker and depression events act oppositely. Progressive plasticity events tend to perturb the equilibrium levels of deeper hidden beakers. Thus, the information of persistent plasticity patterns becomes "entrenched" within the synapse and can dictate the trend of the synaptic weight for longer, via the continuous propagation of liquid in between the beakers.

For instance, if many potentiation events occur, slower variables deviate higher than their equilibrium level. Then, possible depression events can affect the synaptic efficacy within a fast timescale but such information becomes overwritten by the bidirectional communication in the long run. In such cases, the synapse becomes rigidly potentiated. The same unit is able to recall a depression event for a short, vulnerable timescale and a long-term potentiation over a stable long-term period. Over an ensemble of N synapses, memories are consolidated structurally, in a *palimpsest* fashion. Importantly, this configuration allows both the automatic consolidation of memories, reinforced only by the frequency of storage and the protection of old memories in the long term. This is a significant advantage which can allow hardware AI to undertake multiple learning tasks without catastrophically forgetting previously learnt memories.

This work has focused on creating equivalent synaptic models on hardware by engineering the appropriate timescales required for palimpsest consolidation. Such a task can only be undertaken by utilising emerging nanotechnologies which have equivalently complex memory capabilities. Novel *memristive* technologies have thus been considered, and in particular resistive random-access memories or RRAM, the learning capabilities of which are discussed in the following section.

### 2.5 RRAM Technologies

### 2.5.1 An Overview

Since their inception [62] and first realisation [63], memristive devices show great potential in neuromorphic computing [64] [65]. While several types of memristors exist, this project focuses on Resistive Random Access Memory (RRAM) devices. These are two terminal (Metal-Oxide-Metal) devices which operate as tunable resistors whose resistive states depend on the history of applied bias. Their activation process usually

also requires an invasive form of initial biasing called *electroforming* [66]. RRAM offers a significant leap in storage per area with memristors being able to store more than 6 bits of information in a single device [67].

Device resolution and history dependence make RRAM a natural integrator element, a perfect candidate for neural implementations on hardware, for example, the Tempotron [68] [69]. Moreover, memristors exhibit a direct resemblance to synaptic efficacy properties such as long-term potentiation (LTP) and depression (LTD) [21] [70]. Lately, their tunability has been examined in numerous neuromorphic applications including the encoding of neuronal spikes [71] [72], unsupervised learning [20] and in-memory computing [73] [65]. Memristors have also been used to realise metaplastic phenomena [74] [27], where plasticity effects vary depending on timing conditions. However, no prior work has associated RRAM technology with consolidation in a *palimpsest* fashion.

### 2.5.2 RRAM Switching Mechanisms

The change in a memristor's resistive state R is induced via the application of appropriately invasive biasing voltages V. Assuming some device-specific threshold value  $V_{th}$ , higher *programming* amplitudes induce changes in R, while sub-threshold *read* amplitudes can be used to read a device's state at any time. Thus, by employing sequences of programming events accordingly, one can manipulate resistive changes  $\Delta R$  within some resistive range, as illustrated in Fig. 2.8. There, a chosen RRAM device responds bidirectionally to programming events of opposite polarities. Specifically, R (shown in grey data points) increases with positive voltages and decreases when negative amplitudes are applied. The apparent accumulation of  $\Delta R$  with successive programming events gives rise to the intrinsic integration properties of RRAM. Moreover, the device's behaviour shows dependence on the degree of invasiveness by which programming events are applied; a common pattern that will also be prevalent in this work.

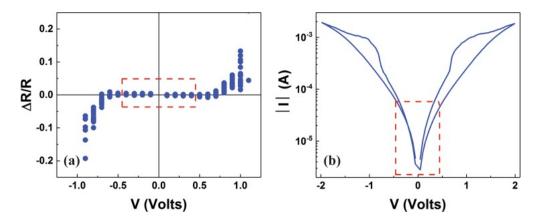

This dependence is represented with more clarity in Fig. 2.9 by [76]. (a) shows how the relative change in resistance  $\frac{\Delta R}{R}$  is affected by increasing programming amplitudes in both polarities. The transition between sub-threshold voltages (boxed in red dashed lines) to invasive programming amplitudes is shown as  $\frac{\Delta R}{R}$  deviates from 0. Concurrently, (b) shows a characteristic I-V relationship during  $\Delta R$  which is reflected by the hysteresis in the I-V curve. This relationship is of significant importance since quantifying the parameters by which RRAM switching can be manipulated is an essential first step towards the design and implementation of memristor-based neuromorphic applications.

However, while memristive properties are promising candidates for post von-Neumann neuromorphic architectures, no unified theory yet exists to encompass their operation,

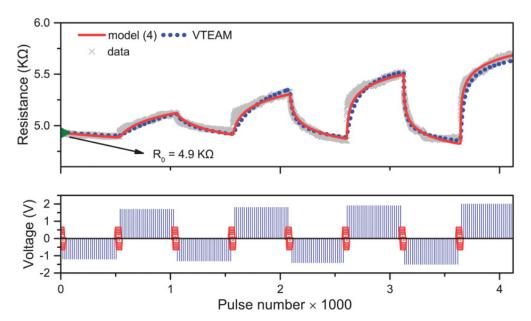

FIGURE 2.8: A typical representation of RRAM  $\Delta R$ , presented in [75]. Consecutive trains of positive programming pulses (shown in blue in the bottom half) cause R to progressively increase (grey data points in the top half), while negative programming pulses decrease R. Importantly, the boundaries of  $\Delta R$  saturation widen as the absolute programming amplitude increases. The switching behaviour is accurately modelled, as illustrated via the overlapping red line and grey data points.

FIGURE 2.9: RRAM switching characterisation as presented in [76]. (a) The dependence of relative  $\Delta R$  on the programming pulse amplitude. As shown, the data can be categorised into two distinct regions, the sub-threshold region (boxed in red) and the invasive bias region, where device R is changing. (b) I-V dependence for the same RRAM device. The apparent hysteresis loop is an indication of a change in the resistive state due to invasive biasing.

even though progress has been made [76] [77] [78]. Evidence suggests that RRAM operation may depend upon a variety of factors, such as the oxide film and the electrode materials [79]. Resistive switching may occur either through electrochemical changes in their active electrodes [80] [81], via redox reactions which induce conductivity changes of the Metal-Oxide film of the device [82], or via thermal ionic diffusion due to current induced changes [81]. Lastly, switching may occur via the alteration of the electrode-oxide interfacial potential barrier [79].

Concurrently, work has been conducted to model the behaviour of RRAM devices under bias. Results suggest that one can simulate with great accuracy resistive switching for known biasing regimes [75]. This model describes the rate of change of device resistance as:

$$\frac{dR}{dt} = s(v) \times f(R, v) \tag{2.1}$$

where s(v) is the voltage sensitivity function of the device, depending only on the pulsing scheme and f(R, v) is the device window function which imposes soft switching boundaries as a function of resistance R and voltage v.

This is also shown in Fig. 2.8 where this model (red line) is used to fit raw switching data (grey). Nevertheless, this work only assumes ideal non-volatile devices and cannot be used to simulate metaplastic timescales.

#### 2.5.3 RRAM Volatility

Within the context of this work, RRAM volatility is defined as the *overall monotonic* drift of device resistive state, *after* and not *during* device programming protocols. Volatility is thus defined as a strictly transient phenomenon, observed under non-invasive and sub-switching-threshold reading voltage amplitudes, that is observed only after appropriate invasive stimulation protocols. This is to be distinguished by the commonly observed stochastic fluctuations in RRAM resistive state when successive state readings are performed. Such fluctuations are present both during passive device readings [83] and during both positive and negative amplitude stimulation protocols [84][77]. Such fluctuations do not show any dependence on the device state history and in this work are considered to be and referred to as noise (see Chapter 3 - 4 as well as Appendix C). On the contrary, RRAM volatility studied in this work follows clear monotonic trends which tend to average out over multiple continuous noisy fluctuations and over longer periods of time.

Volatile behaviour has been reported in RRAM studies in the past [85][68][86]. The passive drift of resistive state over time has been linked with memory consolidation as a potential cleanup mechanism [27] (see Section 2.2). Work by Cortese et.al. suggests that

volatility is a result of ionic diffusion occurring after the removal of the applied electric field [85]. This gradually increases the electrode-oxide interfacial barrier and thus the device's resistive state. This is supported by Liu et.al who report similar diffusion phenomena [87].

It has already become evident that memristive volatility can be designed to a desired effect [88]–[90]. However, in order to fully realise the potential of the volatile RRAM families a systematic approach is needed for characterising and modelling volatility. Existing volatility models suggest that volatile device families can be switched in a non-volatile way only if a minimum energy level has been input during stimulation, while they behave in a volatile manner otherwise [68].. This is explained by separating volatile from non-volatile switching via quantised energy levels needed to induce stable changes in a device's interfacial barrier (the proposed mechanism for manipulation of R). In this scenario, a device's state is always drawn towards a local R attractor. A SPICE model has also been described and has served as inspiration for work conducted in this project. Moreover, routines have been developed to distinguish between volatile and non-volatile regions of memristive operation [86]. Furthermore, attempts to model volatility via equivalent circuits have been presented by [91].

Literature on volatile RRAM switching has focused on predicting the phenomenon within non-volatile technologies. The work that has so far been conducted in this project offers a novel, data-driven volatility model. This can be used in the development of synaptic circuits, with multiple timescale variables, extending the ideas proposed mentioned in [25] and discussed in 2.4.4.

# 2.6 Hardware Synapses

The advantages in learning that can be brought to AI hardware by direct emulation of the discussed synaptic properties have already attracted the interest of the field. This is particularly true within the broader context of memristive technologies, where multiple studies have demonstrated the technologies' intrinsic resemblance to synaptic plasticity.

Memristive synapses have first demonstrated basic plasticity rules in hardware in as LTP and LTD. Based on the analogue switching regime of non-volatile memristors, multiple implementations have shown that efficacy changes become more pronounced as potentiation/depression cycles are applied successively. These studies are also based on phase change memory (PCM) memristive technologies which undergo changes in conductance as bidirectional stimulation is applied to them to reflect potentiation and depression. Emulation of plasticity in this paradigm has been achieved both in standalone devices [29], [92], [93] or by integrating memristors into more complex systems [94], [95]. While these are significant milestones towards designing artificial synapses,

plasticity alone is not sufficient for learning and protecting memories from incoming interference; a fundamental functionality for autonomous learning systems.

To address this issue, both RRAM and PCM memristor studies have worked towards emulating synaptic metaplasticity [51], [59] directly via manipulating the learning rate of the artificial synapses. This has been shown in integrated CMOS-based synapses in the context of spiking neural networks (SNNs) [95], [96]. Metaplasticity has been a very popular research target since it can address the protection of consolidated memories from ongoing interference. Similarly, non-volatile RRAM has also exhibited tunable switching/learning rate via the direct manipulation of stimulation bias [74], [97]–[100]. While these studies have successfully shown tunable switching rates, they do not consider memory consolidation holistically. First, metaplasticity is manipulated by explicit changes in external stimulation. This implies that the need for changes in the switching rates and thus consolidation is known a priori. This is not realistic for autonomous AI where agents are expected to learn in an online fashion and in unpredictable scenarios. Moreover, all these studies consider metaplasticity bidirectionally and exclusively on either LTP or LTD scenarios. For metaplasticity to have full effect, it is essential that it also addresses catastrophic forgetting bidirectionally, allowing a synapse to protect consolidated memories from all forms of interference at the same time [59].

Finally, several studies have focused on memory protection directly, albeit in the context of passive memory lifetime. This has been a feature exclusive to volatile RRAM, which has shown a transition from short- to long-term memory lifetimes [21], [27], [101], [102]. The transition is induced by the frequency of stimulation of a particular memory and can be directly associated with the reinforcement mechanism for consolidation that is discussed in 2.2. However, the transition in all those studies is both irreversible and unidirectional. Specifically, long-term memory has only been shown via LTP, where a binary potentiated state is written for longer time periods due to successive stimulation. While this solidifies the candidature of volatile RRAM as an efficient synaptic emulator, these studies fail to consider the protection of long-term memories under interference caused by opposing synaptic modifications. Thus, the issue of catastrophic forgetting remains unaddressed.

All mentioned studies have either focused on expressing synaptic plasticity or emulating metaplasticity in a static way. Long-term memory has been discussed both in terms of reduced learning rates or longer state lifetimes. A summary of the mentioned technologies is presented in Table 2.1 in chronological order. Consequently, there still remains a clear gap in addressing memory consolidation **and** reversible protection from catastrophic forgetting in an autonomous way. This niche can be addressed by manipulating multiple consolidation timescales as discussed in 2.4.4. Filling this gap is the main objective of this work and is thoroughly discussed in the following chapters of this thesis.

| Example                | Technology                | Туре          | Speed      | Metaplasticity     | Consolidation | LTP/LTD | Lifetime | Timescales | Capacity |

|------------------------|---------------------------|---------------|------------|--------------------|---------------|---------|----------|------------|----------|

| Chang et.al. [27]      | WO <sub>x</sub> RRAM      | Single device | 1ms        | No                 | Yes           | LTP     | < minute | 1          | 1        |

| Ohno et.al. [102]      | Ag <sub>2</sub> S synapse | Single device | 500ms      | No                 | Yes           | LTP     | ≈ 20s    | 1          | 1        |

| Ambrogio et.al. [94]   | GST PCM                   | Multi device  | 250ns      | No                 | No            | LTP/LTD | n/a      | n/a        | 1        |

| Berdan et.al. [21]     | TiO <sub>x</sub> RRAM     | Single device | > s        | No                 | Yes           | LTP     | 10s      | 1          | 1        |

| Tan et.al. [101]       | WO <sub>x</sub> RRAM      | Single device | 10μs       | Explicitly tunable | Yes           | LTP     | minutes  | 1          | 1        |

| Boybat et.al. [29]     | GST PCM                   | Single device | < µs       | No                 | No            | LTP/LTD | n/a      | n/a        | 1        |

| Burr et.al. [93]       | GST PCM                   | Single device | n/a        | No                 | No            | LTP/LTD | n/a      | n/a        | 1        |

| Cheng et.al. [98]      | YSZ RRAM                  | Single device | 0.75-1.5ms | History dependent  | No            | LTP/LTD | n/a      | n/a        | 1        |

| La Barbera et.al. [92] | GST PCM                   | Single device | 5-300ns    | No                 | No            | LTP/LTD | n/a      | n/a        | 1        |

| Lee et.al. [100]       | KN memristor              | Single device | 100µs      | Explicitly tunable | No            | LTP     | n/a      | n/a        | 1        |

| Liu et.al. [99]        | Graphene memristor        | Single device | 100ns      | Explicitly tunable | No            | LTP/LTD | n/a      | n/a        | 1        |

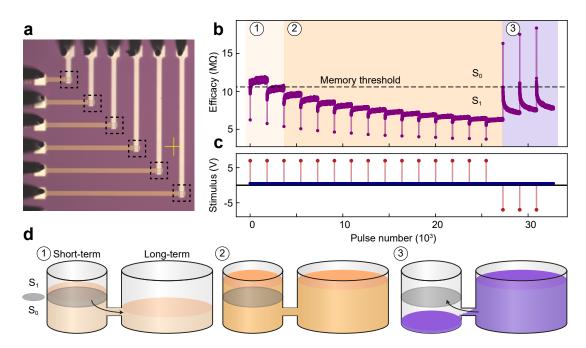

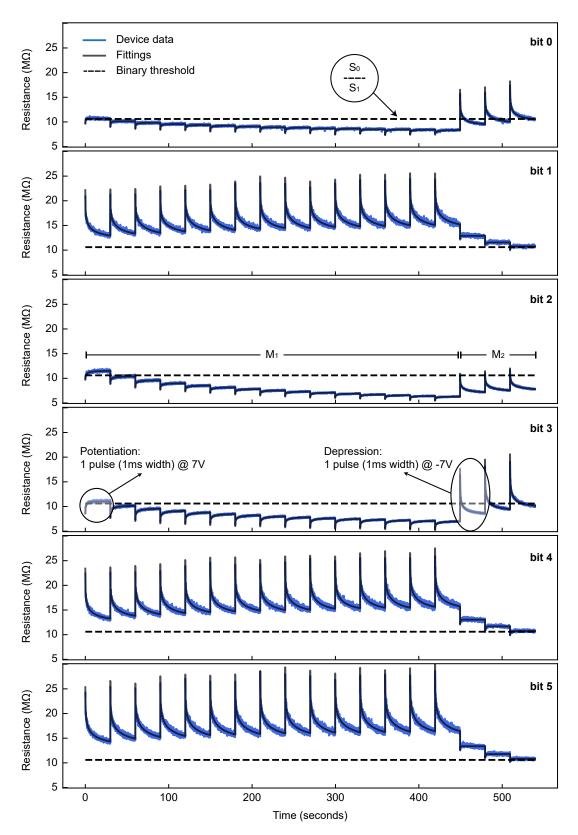

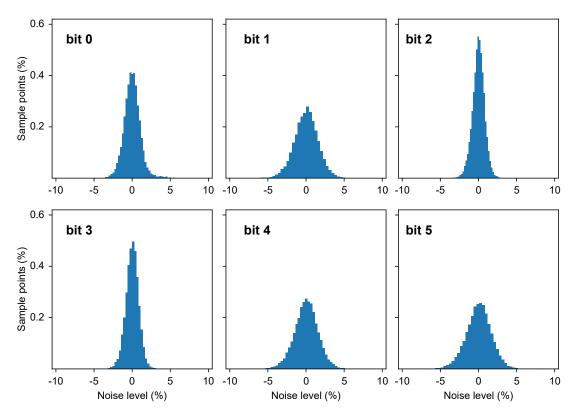

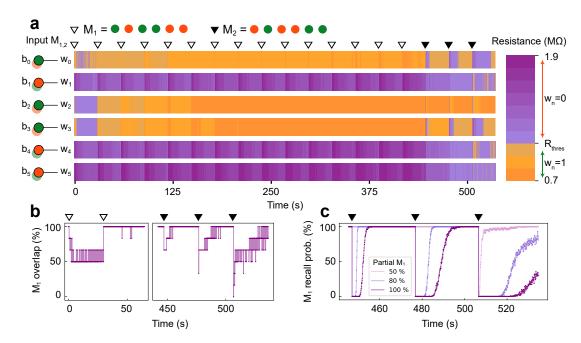

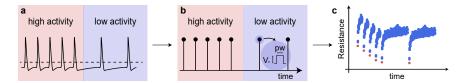

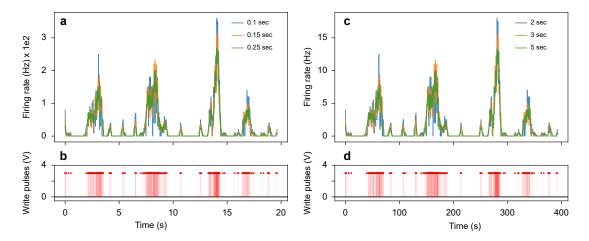

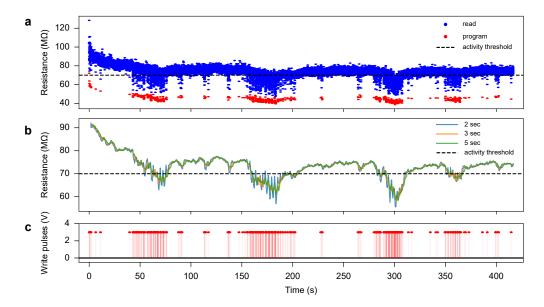

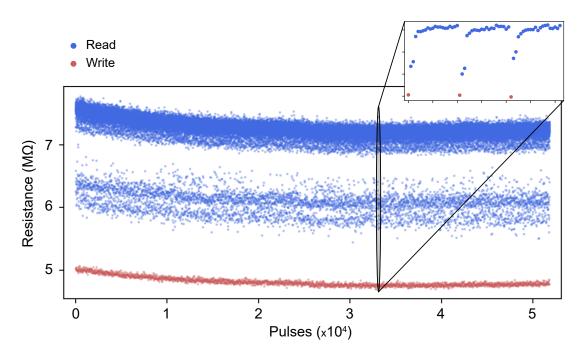

| Wu et.al. [97]         | HfO <sub>x</sub> RRAM     | Single device | 1µs        | Explicitly tunable | No            | LTP/LTD | n/a      | n/a        | 1        |