# optica

### **Buried 3D spot-size converters for silicon photonics**

## W. Zhang,<sup>1</sup> <sup>(i)</sup> M. Ebert,<sup>1</sup> J. D. Reynolds,<sup>1,2</sup> B. Chen,<sup>1</sup> <sup>(i)</sup> X. Yan,<sup>1</sup> H. Du,<sup>1</sup> <sup>(i)</sup> M. Banakar,<sup>1</sup> D. T. Tran,<sup>1</sup> C. G. Littlejohns,<sup>1</sup> G. T. Reed,<sup>1</sup> and D. J. Thomson<sup>1,\*</sup>

<sup>1</sup>Optoelectronics Research Centre, Zepler Institute for Photonics and Nanoelectronics, Faculty of Engineering and Physical Sciences, University of Southampton, Southampton SO17 1BJ, UK

<sup>2</sup>Sustainable Electronic Technologies Research Group, Electronics and Computer Science, Faculty of Engineering and Physical Sciences,

University of Southampton, Southampton SO17 1BJ, UK

\*Corresponding author: d.thomson@soton.ac.uk

Received 10 May 2021; revised 9 July 2021; accepted 9 July 2021 (Doc. ID 431064); published 13 August 2021

In this article, an efficient spot-size converter (SSC) for low-loss optical mode transition between large and small waveguides based upon a buried three-dimensional (3D) taper is demonstrated. The SCC can pave the way for scalable, low-loss coupling between on-chip waveguides of different sizes and with external components such as optical fibers and III-V active components, and it can be a key element in solving the challenges surrounding the economic high volume packaging and assembly of photonic integrated circuits. Through the use of a bespoke fabrication process, continual tapering of the waveguide dimensions both in width and height is achieved, offering minimal perturbance of the optical mode throughout the structure. The SSC exploits the space of the buried oxide (BOX) on a standard silicon-on-insulator wafer, leaving a planar top wafer surface, meaning that, crucially, further processing of the wafer is not inhibited in any way. Fabricated proof-of-concept devices demonstrate coupling between standard single-mode 220 nm thick silicon waveguides and large-core waveguides with dimensions about 3  $\mu$ m wide and 1.5  $\mu$ m height with BOX thickness of 2  $\mu$ m. Coupling losses as low as 0.56 dB are achieved, limited mostly by the material loss of the polysilicon used. Substantial improvements can be yielded by simply changing the infill material and through optimization of the fabrication process and design. The demonstrated SSC approach can further be applied to other photonic platforms such as silicon nitride on insulator and so on. © 2021 Optical Society of America under the terms of the OSA Open Access Publishing Agreement

https://doi.org/10.1364/OPTICA.431064

#### **1. INTRODUCTION**

Silicon photonics (SiPh) has been developed as a mature platform for the mass production of versatile integrated photonic circuits powered by the compatible, complementary metal-oxidesemiconductor (CMOS) technology. This has made it possible for SiPh interconnects to replace the traditional low-bandwidth electrical input/output (I/O) ports for high-performance and high-bandwidth optoelectronics applications [1]. Co-packaged optics is believed to be the next integration phase, requiring optics to be closer to high-performance system-on-chips (SoCs). It is becoming a scalable optical technology enabling high-volume, low-cost transceivers that can be co-packaged within larger electronic systems, e.g., switch application-specific integrated circuits (ASICs). It will also allow dense optical/electrical (O/E) chiplet integration and provide high bandwidth as well as energy and cost efficiency for data communication and computation [2].

At the present stage, beyond the challenges of achieving a high bandwidth [3,4], a robust solution for SiPh component assembly and packaging is required, which is currently orders of magnitude more expensive than electronic packaging. This is mainly due to the fact that SiPh packaging and assembly faces several challenges, such as automated high throughput [5,6], accurate alignment of optical fibers [1,7] as well as the hybrid and heterogeneous integration of III-V active components (laser, amplifiers, and detectors [8–12]).

To address these problems, robust and highly precise vertical and horizontal alignment is typically required for fiber array packaging and the monolithic/butt-coupled integration of III-V components where the optical mode is butt-coupled to a silicon rib waveguide [6,7,9,10]. The main challenge for butt-coupling strategies is matching the mode field of SiPh waveguides with optical fiber and output facets of III-V components. This has been widely explored in the last 20 years to provide a reduction in coupling losses while operating over a wide optical bandwidth and with tolerance to practical alignment errors.

For high-efficiency coupling to standard single-mode optical fibers (SMF28), the typical mode field diameter (MFD) of the waveguide couplers should be matched with that of the fiber, which is around  $\sim 10 \ \mu m$  at 1.55  $\ \mu m$  wavelength. Typical single-mode silicon photonic waveguide have dimensions  $\sim 220 \ nm \times 450 \ nm$  and therefore result in almost a 3 order of magnitude mode area mismatch to that of standard optical fibers. To solve this issue, inversely tapered SiPh waveguides have been proposed to couple light from the waveguide core to the fibers [13–17]. The efficiency of coupling is high between inversed waveguides and fibers, but

its implementations are concerned with the fabrication tolerance, yield, and required package alignment accuracies. Thus, spot size converters (SSC) have been introduced to transfer the optical mode from a high-index waveguide to a low-index large waveguide [7]. The SSCs are usually part of the cladding of the high-index contrast waveguides, bridging the inverse high-index taper and large core low-index cladding waveguides. Typical materials used for the SSC are SU8 [16,18,19], silicon oxide [20], silicon nitride [21-25] and SiON [26]. These SSCs protrude from the planar waveguide surface and can impede further CMOS wafer-scale processing, for example, chemical mechanical polishing (CMP). Besides, for most of these demonstrated SSC solutions, non-silicon materials are used, or silicon deep-trench etching with suspended SiO<sub>2</sub> waveguides must be adopted, which are not well suited for CMOS-compatible processing. For a universal SSC design, the photonic mode expansion requires both lateral and vertical dimension tapering. It should give the designers the flexibility to control the SSC size for different edge coupled components [1,7–10].

Under such context, here a buried 3D SSC approach has been realized, capable of converting a traditional submicrometer silicon rib waveguide mode into a micrometer-scale waveguide. The SSC is composed of polysilicon, which is filled into a 3D tapered trench on conventional silicon-on-insulator (SOI) wafers with 220 nm silicon overlayer and 2 µm buried silicon dioxide (BOX) layer. The fabrication process uses aspect-ratio-dependent lag etching of the BOX, of which the etch depth is trench width dependent, a technique that has been used in microelectromechanical system (MEMS) device fabrication [27]. The BOX trench depth was engineered from 0 nm to approximately 1.3 µm in depth with the width enlarged up to around 3  $\mu$ m. The trench is filled with polysilicon and later planarized. The demonstrated 3D SSC approach only requires silicon-based materials and provides a top planar surface, which does not restrict further processing options. The total mode transition loss of the fabricated SSC is as low as 0.5 dB, limited by the material loss of the polysilicon material used. Excluding the polysilicon material loss, the 3D SSC exhibits an optical loss  $\sim$  0.2 dB that is mainly due to the geometrical designs and roughness from fabrication.

Previous demonstrations of SSC based upon 3D tapers have had many drawbacks, meaning that they are not well suited for the silicon photonics industry. For example, the demonstrations in [28-30] rely on anisotropic chemical etch to a specific crystal plane to create the taper shape. This limits how the taper can be orientated on the wafer, creating a design restriction, and it requires non-standard SOI wafers with a specific crystal orientation, fixes the taper length based upon the two waveguide heights required, is limited to a linear taper shape in depth, and limits the material of the taper to one with a crystal plane-dependent etch. In [31], the taper was formed using a gray-tone lithography approach, which results in high surface roughness and therefore high optical loss. In [32], multiple lithography and etching steps were required, which would add significant process effort and result in abrupt steps in waveguide height. The 3D taper in [33] uses a submicrometer loading effect requiring multiple oxidation and etching steps in order to smooth the taper surface, which again adds process complexity. Reference [34] uses a non-standard fabrication technique to impress a height taper in SU8, which would be difficult to realize in a CMOS manufacturing facility. In [35], localized focused ion beam milling is used to create the height taper; however, again, this is a non-standard technique for CMOS processing that would not

provide the throughput required for the high-volume fabrication. Demonstrations [28-33] start with a thick silicon layer and etch it down to make the thin silicon layer. The thickness of the thin silicon will then vary by the same original silicon thickness variation across the wafer plus any etch rate variation. The thickness variation of thick SOI wafers is, however, typically large comparable to final thickness that would be required for a thin silicon layer containing a high-speed silicon optical modulator, for example (220-340 nm), and therefore an intolerably large thickness variation will likely result in the thin silicon layer. In all cases of 3Dtaper-based SSC [19,28-33,35] and non-3D-taper-based SSC, for example [18,20-22,26,36,37], the top surface of the wafer is not planar after the taper formation, which impacts onward processing. For example, CMP is not possible on the thin silicon layer as required for the hybrid integration of lasers and amplifiers and the fabrication of modulators and detectors. The method introducing a multilayer SSC [22,23,25] is also difficult for leveraging current silicon photonic lines that are mostly processing a single high-index waveguide layer, but this is promising for future 3D photonic circuit integration.

Our demonstrated 3D-taper-based SSC can be formed using a single lithography and etching step followed by deposition of the waveguide taper material and planarization. These are all processes that can be simply implemented in a typical CMOS fabrication facility. For our proof-of-concept demonstration, polysilicon was used as the waveguide taper material; however, our approach is flexible through the deposition of other photonic materials to form the waveguide taper such as silicon nitride and its photonic Damascene process [38]. In our approach, the taper shape can be nonlinear and optimized both through the layout and the etch process. The length and orientation is also flexible, and standard 100 SOI wafers can be used. The starting material, which is where the small waveguides are eventually formed, is thin SOI with a thickness variation smaller than  $\pm 10$  nm. The thick waveguides, which are more tolerant to thickness variation, are then formed in the etched trenches. Finally, in our approach the top surface of the wafer remains planar after the taper formation with the thicker waveguides extending downward into the wafer, and thus forward processing of the wafer is not impacted.

This work paves the way for scalable, low-loss butt-coupling for fibers and bonded III-V active components. In addition to this, our demonstrated 3D SSC can facilitate the realization of an optimal photonic platform where multiple waveguide sizes can be formed on chip to achieve the best performance from each component, rather than using a universal waveguide height where the performance of each component is compromised to an extent. For example, high-bandwidth components such as optical modulators and detectors can be formed in submicrometer waveguides where low capacitance, low access resistance, and a compact optical mode is critical, while passive elements can be formed in larger waveguides, where propagation loss, sensitivity to fabrication tolerances, and polarization dependence are of more importance. Our proposed SSC can act as the low-loss optical bridge between the different waveguide sizes and also to form the larger waveguides themselves. The trench etching of this SSC could also be used as an interlayer slope waveguide coupler for a multilayer silicon photonics platform [39].

#### 2. DESIGN AND FABRICATION

#### A. Design of the SSC

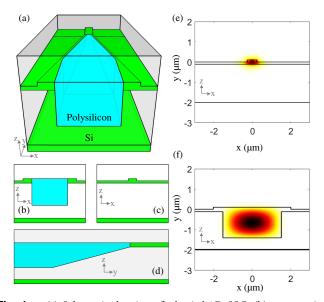

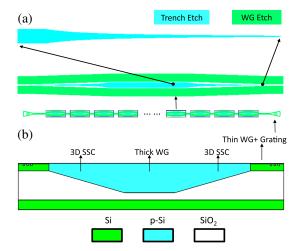

The 3D SSC design is schematically shown in Fig. 1 based on SOI with a 220 nm silicon overlayer and a 2  $\mu$ m BOX. In Fig. 1(a), conventional single crystalline SOI rib waveguide [Fig. 1(c)] is connected with a buried polysilicon 3D SSC and a thick polysilicon waveguide [Fig. 1(b)], of which the thickness is limited by the 2  $\mu$ m BOX, and the width can have an extensive range >3  $\mu$ m. The SSC exploits the space of the BOX and provides a planar surface above the silicon and polysilicon layer. The slope of the BOX in Fig. 1(d) is realized through reactive ion etching and will be explained in Section 2.B. The single-mode rib waveguide has a height of 220 nm and width 450 nm [Fig. 1(c)], and the large waveguide realized here has a width of 3  $\mu$ m and height 1.5  $\mu$ m. The optical modes of small and large waveguides are shown in Figs. 1(e) and 1(f), respectively. From thick waveguide to thin waveguide, the polysilicon depth was designed to decrease linearly as shown in Fig. 1(d), which was experimentally focused on. By 3D finite-difference time-domain (FDTD) simulation verification, the polysilicon width can be linearly or nonlinearly modulated to have a transmission efficiency above 99% for both the TE polarization (220 nm × 450 nm SOI rib/strip waveguide) and TM polarization (220 nm  $\times$  450 nm strip waveguide). No polarization sensitivities of the SSC concept were observed in simulation. It should be noted that, referring to the previously reported 1.5 µm SOI platform with 300 nm BOX [40], the mode leakage to the handle wafer is negligible for the designed SSCs and thick waveguides shown in Fig. 1. Hereafter, the experimental work focuses on the TE polarization.

#### B. Fabrication of the SSC

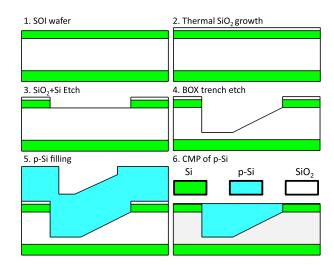

The fabrication process flow of the SSC is shown in Fig. 2. Starting from the SOI wafer, a 30 nm silicon dioxide layer was thermally

**Fig. 1.** (a) Schematic drawing of a buried 3D SSC; (b) cross section of the larger waveguide; (c) cross section of the submicrometer silicon rib waveguide; (d) cross section of the propagation direction, including thick waveguide, SSC, and silicon rib waveguide; (e) optical mode of the submicrometer single-mode silicon rib waveguides (width 450 nm, height 220 nm); (f) optical mode of the large waveguide (width 3 um, height 1.5 um).

Fig. 2. Fabrication process flow of the 3D polysilicon SSC.

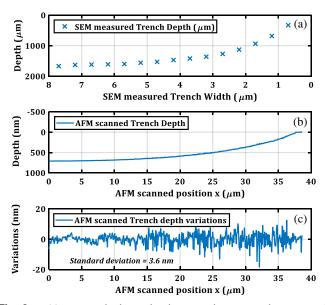

**Fig. 3.** (a) Measured relationship between the patterned resist trench width and etched depth of silicon oxide. (b) AFM scanned depth profile of the SSC trench. (c) The depth variations of the etched sloping trench.

grown on the surface as a chemical mechanical polishing (CMP) stopping layer for step 6. Next, DUV-248 scanner lithography was used to define the positions of SSC trenches in the photoresist. The silicon dioxide and silicon overlayer were then etched by inductively coupled plasma (ICP) etching in step 3. For the SSC trench etching, a new recipe was developed employing the lag effect to form the taper shape within the BOX. The etched BOX trench was then filled with amorphous silicon, which was deposited by lowpressure chemical vapour deposition (LPCVD). Next, the wafer was annealed to transform amorphous silicon into polycrystalline silicon and CMP was used to planarize the wafer back to the 30 nm silicon dioxide stop layer. Again, scanner lithography was used to pattern the waveguides and grating couplers in the top silicon layer, which are etched by ICP. Finally, a 1 µm silicon dioxide top cladding layer was deposited by plasma-enhanced chemical vapor deposition (PECVD). The developed in-house CMP process results in less than 10 nm trench thickness thinning (dishing)

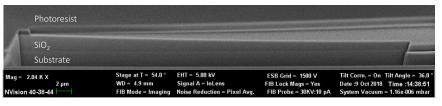

**Fig. 4.** Cross-section view of the etched sloping trench on silicon dioxide.

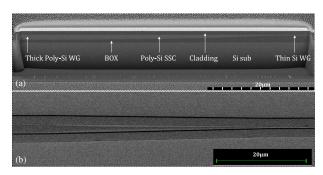

**Fig. 5.** (a) Cross-section view and (b) top view of the fabrications of the polysilicon SSC.

when trench width is 7  $\mu$ m. No additional steps were introduced to reduce any roughness resulting from the CMP process.

The developed SSC trench etching recipe used  $C_4F_8$  and Ar at flow rates 35 sccm and 15 sccm, respectively. The RF platen power and chamber pressure were 100 W and 3mT respectively. A thick resist with total height 1.3 µm was coated for the etching steps 3 and 4 in Fig. 2. For recipe development, 2  $\mu$ m thermal SiO<sub>2</sub> on bulk silicon wafers were used. Ultimately, the developed etching recipe allows SiO<sub>2</sub> etch rate variation by changing the trench window width defined by the thick top resist as shown in Fig. 3(a). Explicitly, the SSC trench structures were realized by exploiting the aspect ratio dry etching (ARDE) effect [41], where the etch rate at the bottom of the trench correlates with the aspect ratio [42]. The etch rate depends on several mechanisms such as ion shadowing, Knudsen transport of neutrals, differential charging of the insulator, and an influx of neutrals, ions, and electrons as well as the removal of the reaction products [43]. Using a  $C_4F_8$  gas chemistry in the plasma promotes the amount of polymerization within the process, enabling an even stronger ARDE [44]. During the etch process, the narrow and thin tip of the SSC should not be attacked, while the SiO<sub>2</sub> in the wider and thicker waveguide area can be etched down deeply. By changing the trench width from 0 to 8  $\mu$ m, the etched depth varies from 0 to 1.7  $\mu$ m. The trench slope was scanned by atomic force microscopy (AFM) on the test wafer during the recipe development to verify the profile and roughness of the trench surface as exhibited in Fig. 3(b). A trench depth of zero was successfully realized at the beginning of the slope on the right side, which is essential to achieve low optical transition loss in the 3D SSC. The scanned region covers a trench depth and length around 700 nm and 37 µm, respectively. Roughness on the surface of the taper is within  $\pm 10$  nm for the entire scanned length, and it is within  $\pm 5$  nm for depths larger than 600 nm as shown in Fig. 3(c), which is interpreted from Fig. 3(b). Longer etching times can be used to adjust the trench depth while simultaneously keeping a smooth depth transition as will be shown in the fabricated device. The trench aspect ratios are changeable by modifying the recipe. For example, for two different recipe variants

**Fig. 6.** (a) Top view of polysilicon section width variation of the SSC; (b) side view of the waveguide, SSC to 220 nm SOI rib waveguides.

in our process development, with a 7  $\mu$ m wide trench a similar depth was achieved, whereas for a 700 nm wide trench a difference in etch depth of around 750 nm was observed. The etching recipe is therefore flexible and can be redesigned for different application requirements.

An example of the trench profile achieved in SiO<sub>2</sub> on bulk Si wafers taken by scanning electron microscope (SEM) is displayed in Fig. 4. The taper length is 50  $\mu$ m, and the width of the trench was linearly tapered from 200 nm to 3  $\mu$ m, which results in a trench slope with depth from 0 to 1.3  $\mu$ m. The optimized maximum etched depth of the recipe has a limit of 2  $\mu$ m as depicted in Fig. 3(a), which considers the targeted SOI wafers that have a 2  $\mu$ m thick BOX. To this step, we have demonstrated that a sloped trench etched into the BOX of an SOI wafer can be realized to form a 3D tapered polysilicon SSC.

To achieve a gently varied slope along the 3D SSC length, the width of the SSC was modulated by following the depth versus width relation of Fig. 3(a) as shown in Fig. 6(a). The width of the SSC is designed to increase from the tip to the large waveguide end slowly and nonlinearly. The final achieved 3D SSC in standard SOI wafers is shown in Figs. 5(a) and 5(b). In Fig. 5(a), the cross-section SEM of the taper clearly shows different sections, including the thick waveguide, 3D SSC, and top thin silicon waveguides. The top-view SEM image of Fig. 5(b) reveals the adiabatic change of the BOX trench width and top-layer waveguide profiles. The total length of the taper shown in Figs. 5(a) and 5(b) is 50  $\mu$ m. The top waveguide layer [Fig. 6(a)] after etching has a width of 4  $\mu$ m and 1  $\mu$ m for the thick waveguide and thin waveguide, respectively, in the SSC region. Beyond the SSC, the 1  $\mu$ m wide waveguide in the thin silicon layer then linearly tapers down to 450 nm.

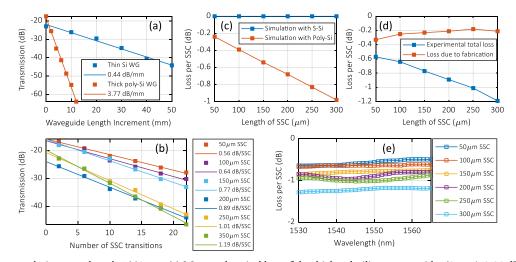

**Fig. 7.** (a)–(d) Loss analysis at wavelength 1550 nm. (a) Measured optical loss of the thick polysilicon waveguides  $(3.77 \pm 0.23 \text{ dB/mm})$  and thin silicon overlayer waveguide  $(0.44 \pm 0.06 \text{ dB/mm})$ ; (b) measured optical transmission losses of the SSCs with different lengths. The extracted losses per SSC are  $0.56 \pm 0.05$ ,  $0.64 \pm 0.10$ ,  $0.77 \pm 0.09$ ,  $0.89 \pm 0.07$ ,  $1.01 \pm 0.07$ , and  $1.19 \pm 0.08 \text{ dB}$  for different SSC lengths 50, 100, 150, 200, 250, and 300 µm, respectively; (c) simulated transmission losses of the SSCs consisting of single-crystalline silicon (S-Si) and polysilicon. (d) Summary of the experimental total optical loss and loss due to experimental fabrications after excluding the polysilicon loss. (e) Measured C-band insertion loss per SSC.

#### 3. RESULTS AND DISCUSSION

To quantify the optical transition loss of the fabricated SSCs at wavelengths around 1550 nm, a series of waveguides, each consisting of a different number of SSCs, were fabricated as designed in Fig. 6(a). Separately, different lengths of the thick polysilicon waveguides have also been fabricated to characterize the optical losses resulting from the polysilicon material. The optical losses are fitted by the cutback method. As shown in Fig. 7(a), the measured optical loss of the polysilicon waveguide ( $\alpha_{p-wg}$ ) is 3.77 dB/mm, and the single-mode top layer thin waveguide ( $\alpha_{Si-wg}$ ) is 0.44 dB/mm. The measured transition loss of the 3D SSC grows with length as shown in Fig. 7(b). Explicitly, the optical losses of the SSCs are measured to be 0.56, 0.64, 0.77, 0.89, 1.01, and 1.19 dB for lengths of 50, 100, 150, 200, 250, and 300 µm, respectively. The optical loss of the SSC mostly stems from the material loss of the polysilicon. A detailed influence of the polysilicon material loss is analyzed as follows.

To make a conservative estimate of the polysilicon materialinduced losses ( $\alpha_p$ ), the contribution from surface roughness ( $\alpha_r$ ), which is treated to be as high as the losses of the thin silicon waveguide, is subtracted from the measured thick polysilicon waveguide loss. The optical power confinement factor for the polysilicon region ( $\Gamma_p$ ) of the thick waveguide is calculated to be 99.79%. The polysilicon material loss is then calculated as 3.34 dB/mm by  $\alpha_p = (\alpha_{p-\text{wg}} - \alpha_r)/\Gamma_p$ . To further analyze the polysilicon contribution to the transition loss of the SSCs, 3D FDTD simulations of the SSC were performed by considering the material used to fill the trench as polysilicon with loss 3.34 dB/mm or single-crystalline silicon (S-Si) with negligible loss. The results show the SSC optical losses are negligible for S-Si and, in contrast, are very profound for polysilicon as shown in Fig. 7(c). Therefore, the maximum optical losses due to fabrication-induced imperfections of the SSC and roughness of all sections can be estimated by deducting the polysilicon-induced material loss from the total measured loss of the SSC as shown in Fig. 7(d), which indicates losses as low as about  $0.2 \, dB$  for taper lengths from  $100 \text{ to } 300 \, \mu \text{m}$ .

In the future, the 3D SSC transition loss reductions can therefore be realized by using a lower-loss infill material. Optimizing the optical properties of the polysilicon can achieve losses down to 0.92 dB/mm [45,46], which can result in a material loss of 0.05 dB for a 50 µm long SSC. Similarly, depositing single crystalline silicon by PECVD and recrystallization with a proximity single crystalline silicon seed [47,48] can reduce the loss sources from polysilicon: light absorption by sub-bandgap states in silicon grain boundaries and optical scattering by Si crystalline grains. Waveguides in an SOI platform with a 1.5 µm thick single crystalline silicon overlayer show losses less than 3 dB/cm as reported in 2005 [40], even with relatively low-quality sidewall etching. Further loss reduction can be achieved by smoothing the etched trench surfaces [38] to therefore reduce scattering losses close to the tip region of the SSC. Hence, overall loss below 0.2 dB can be expected through design and process optimization. Figure 7(e) presents the insertion loss across the entire C band with a loss variation less than  $\pm 0.1$  dB. Furthermore, the demonstrated SSC approach can also be applied to the silicon nitride photonic platform, where the deposited silicon nitride material usually has very low optical losses compared with polysilicon [38,49].

To the first concerned application toward coupling with standard cleaved optical fibers with MFD around 10  $\mu$ m, the demonstrated SSC approach successfully enlarged the 220 nm SOI waveguide to approximately 1.5 µm. With this MFD, directly interfacing with a cleaved single-mode fiber would result in large coupling losses as indicated by the  $3 \,\mu m \times 3 \,\mu m$  waveguide to fiber coupling in [50]. However, it is feasible with our 3D SSC approach to expand the waveguide to 3 µm by using SOI wafers with thicker BOX layer. Microscale SOI platforms are another mature and commercialized solution for photonics applications, where standard fiber-to-chip coupling has been realized with around 1 dB and 1.2 dB losses for TE and TM polarizations, respectively [51]. In that work, buried 2D tapered SSCs have been implemented with a cross section of  $13 \,\mu\text{m} \times 13 \,\mu\text{m}$  for interfacing with fibers and performing mode conversion to small micrometer-scale waveguides [51]. By combining our buried 3D SSC with this work, low-loss coupling between submicrometer

waveguides and optical fibers is possible. With a much thicker BOX layer, or the use of localized  $SiO_2$  infilling trenches, 3D tapers to a waveguide depth of 10 um would be possible, allowing a direct interface with optical fibers.

The second scenario is butt-coupling with III-V components, a hybrid integration approach allowing edge-coupling of III-V and SOI chip to chip and a common approach for flip-chip bonding technology. III-V semiconductor optical amplifiers (SOAs) are widely reported with integration with silicon chips to build power-efficient, tuneable, and low-linewidth external cavities lasers [52,53], for which SSCs are used for low-loss light coupling between chips. The calculated mode field diameter of the thick waveguide part of the SSC [Fig. 1(f)] is about 2.9  $\mu$ m  $\times$  1.5  $\mu$ m, which is close to the mode field diameter  $(2 \,\mu\text{m} \times 1.3 \,\mu\text{m})$ of the indium phosphide SOA waveguides reported in [54]. Conventional inverse taper SSCs have been used to expand the SOA mode to match the mode of a Si inverse taper waveguide with a SiON core [54]. The 3D buried SSC approach can be feasibly and purposely optimized and applied to such scenarios that allow the silicon waveguide mode to be directly matched with the SOA waveguides. As shown in [54], the MFD is sensitive to inverse tapering of the width but much less sensitive to waveguide expansion, which is in favor with our micrometer-scale 3D buried SSC for light coupling from chip to chip. The proposed buried 3D SSC can also be widely exploited for other silicon photonic applications, which will not be addressed in detailed hereafter.

#### 4. CONCLUSION

In conclusion, a low-loss buried 3D SSC integration approach for silicon photonics has been demonstrated. Smooth gradient and width modulated trenches have been developed by performing an optimized width-dependent ICP etching recipe and filling the etched trenches with polysilicon to realize a 3D taper allowing optical transitions from large waveguides to standard thin silicon waveguides. The demonstrated total losses for the polysilicon SSC are as low as 0.56 dB. The material loss of the polysilicon has been shown to contribute significantly to the total loss with the loss contribution from experimental fabrication calculated to be just 0.2 dB. Through the use of a lower-loss infill material, together with improvements in design, fabrication losses below 0.2 dB are expected. The buried 3D SSC requires only silicon materials and leaves a flat, planar wafer surface, enabling compatibility with standard SiPh components and process steps for wafer-scale mass production. Such a SSC can be used for scalable, low-loss butt-coupling for optical fibers, III-V active components, and the development of multilayer photonics.

**Funding.** Engineering and Physical Sciences Research Council (EP/R003076/1, EP/N013247/1, EP/T019697/1); European Commission (780930).

**Acknowledgment.** G. T. Reed is a Royal Society Wolfson Merit Award holder and is grateful to both the Royal Society and the Wolfson Foundation for funding the award. D. J. Thomson acknowledges funding from the Royal Society for his University Research Fellowship (UF150325).

**Disclosures.** The authors declare no conflicts of interest.

**Data Availability.** Data underlying the results presented in this paper are available in Ref. [55].

#### REFERENCES

- C. R. Doerr, "Silicon photonic integration in telecommunications," Front. Phys. 3, 1–16 (2015).

- N. Mehta, S. Lin, B. Yin, S. Moazeni, and V. Stojanovic, "A laserforwarded coherent transceiver in 45-nm SOI CMOS using monolithic microring resonators," IEEE J. Solid-State Circuits 55, 1096–1107 (2020).

- B. Snyder, N. Mangal, G. Lepage, S. Balakrishnan, X. Sun, N. Pantano, M. Rakowski, L. Bogaerts, P. De Heyn, P. Verheyen, A. Miller, M. Pantouvaki, P. Absil, and J. Van Campenhout, "Packaging and assembly challenges for 50G silicon photonics interposers," in *Optical Fiber Communication Conference and Exposition (OFC)* (2018), pp. 1–3.

- L. Carroll, J.-S. Lee, C. Scarcella, K. Gradkowski, M. Duperron, H. Lu, Y. Zhao, C. Eason, P. Morrissey, M. Rensing, S. Collins, H. Hwang, and P. O'Brien, "Photonic packaging: transforming silicon photonic integrated circuits into photonic devices," Appl. Sci. 6, 426 (2016).

- T. Barwicz, T. W. Lichoulas, Y. Taira, Y. Martin, S. Takenobu, A. Janta-Polczynski, H. Numata, E. L. Kimbrell, J. W. Nah, B. Peng, D. Childers, R. Leidy, M. Khater, S. Kamlapurkar, E. Cyr, S. Engelmann, P. Fortier, and N. Boyer, "Automated, high-throughput photonic packaging," Opt. Fiber Technol. 44, 24–35 (2018).

- R. Polster, L. Y. Dai, O. A. Jimenez, Q. Cheng, M. Lipson, and K. Bergman, "Wafer-scale high-density edge coupling for high throughput testing of silicon photonics," in *Optical Fiber Communication Conference and Exposition (OFC)* (2018), pp. 1–3.

- R. Marchetti, C. Lacava, L. Carroll, K. Gradkowski, and P. Minzioni, "Coupling strategies for silicon photonics integrated chips [invited]," Photon. Res. 7, 201–239 (2019).

- G. De Valicourt, C. M. Chang, M. S. Eggleston, A. Melikyan, C. Zhu, J. Lee, J. E. Simsarian, S. Chandrasekhar, J. H. Sinsky, K. W. Kim, P. Dong, A. Maho, A. Verdier, R. Brenot, and Y. K. Chen, "Photonic integrated circuit based on hybrid III-V/silicon integration," J. Lightwave Technol. 36, 265–273 (2018).

- G. De Valicourt, C. M. Chang, M. S. Eggleston, A. Melikyan, C. Bolle, N. Kaneda, M. P. Earnshaw, Y. K. Chen, A. Maho, R. Brenot, and P. Dong, "Hybrid-integrated wavelength and reflectivity tunable III-V/silicon transmitter," J. Lightwave Technol. 35, 1376–1382 (2017).

- S. Feng, Y. Geng, K. M. Lau, and A. W. Poon, "Epitaxial III-V-on-silicon waveguide butt-coupled photodetectors," Opt. Lett. 37, 4035–4037 (2012).

- Y.-J. Chen, R.-Y. Chen, Y.-H. Fang, C.-H. Liang, W.-K. Hsu, C.-L. Chen, W.-C. Lin, C.-Y. Weng, J.-Y. Chu, and Y.-J. Chiu, "Hybrid III-V-on-SOI optical spot size converter by self-aligned selective undercut dry etching of Si," Opt. Lett. 45, 4188–4191 (2020).

- A. Y. Liu, S. Srinivasan, J. Norman, A. C. Gossard, and J. E. Bowers, "Quantum dot lasers for silicon photonics [invited]," Photon. Res. 3, B1–B9 (2015).

- K. Kasaya, O. Mitomi, M. Naganuma, Y. Kondo, and Y. Noguchi, "A simple laterally tapered waveguide for low-loss coupling to single-mode fibers," IEEE Photon. Technol. Lett. 5, 345–347 (1993).

- P. Cheben, J. H. Schmid, S. Wang, D.-X. Xu, M. Vachon, S. Janz, J. Lapointe, Y. Painchaud, and M.-J. Picard, "Broadband polarization independent nanophotonic coupler for silicon waveguides with ultra-high efficiency," Opt. Express 23, 22553–22563 (2015).

- T. G. Tiecke, K. P. Nayak, J. D. Thompson, T. Peyronel, N. P. de Leon, V. Vuletić, and M. D. Lukin, "Efficient fiber-optical interface for nanophotonic devices," Optica 2, 70–75 (2015).

- W. Liu, J. Zhang, L. Liu, D. Dai, and Y. Shi, "High efficiency silicon edge coupler based on uniform arrayed waveguides with un-patterned cladding," IEEE Photon. Technol. Lett. **32**, 1077–1080 (2020).

- A. He, X. Guo, K. Wang, Y. Zhang, and Y. Su, "Low loss, large bandwidth fiber-chip edge couplers based on silicon-on-insulator platform," J. Lightwave Technol. 38, 4780–4786 (2020).

- O. A. J. Gordillo, U. D. Dave, and M. Lipson, "Bridging between Si and few-mode fiber higher order modes," in *Conference on Lasers and Electro-Optics* (OSA, 2020), paper SM2O.6.

- H. Luo, F. Xie, Y. Cao, S. Yu, L. Chen, and X. Cai, "Low-loss and broadband fiber-to-chip coupler by 3D fabrication on a silicon photonic platform," Opt. Lett. 45, 1236–1239 (2020).

- Q. Fang, T.-Y. Liow, J. F. Song, C. W. Tan, M. Bin Yu, G. Q. Lo, and D.-L. Kwong, "Suspended optical fiber-to-waveguide mode size converter for Silicon photonics," Opt. Express 18, 7763–7769 (2010).

- Y. Maegami, M. Okano, G. Cong, K. Suzuki, M. Ohno, T. Narushima, N. Yokoyama, M. Seki, M. Ohtsuka, S. Namiki, and K. Yamada, "Simple and fully CMOS-compatible low-loss fiber coupling structure for a silicon photonics platform," Opt. Lett. 45, 2095–2098 (2020).

- M.-J. Picard, C. Latrasse, C. Larouche, Y. Painchaud, M. Poulin, F. Pelletier, and M. Guy, "CMOS-compatible spot-size converter for optical fiber to sub-μm silicon waveguide coupling with low-loss low-wavelength dependence and high tolerance to misalignment," Proc. SPIE 9752, 97520W (2016).

- M. Papes, P. Cheben, D. Benedikovic, J. H. Schmid, J. Pond, R. Halir, A. Ortega-Moñux, G. Wangüemert-Pérez, W. N. Ye, D. Xu, S. Janz, M. Dado, and V. Vašinek, "Fiber-chip edge coupler with large mode size for silicon photonic wire waveguides," Opt. Express 24, 5026–5038 (2016).

- P. K. J. Singaravelu, G. C. R. Devarapu, S. A. Schulz, Q. Wilmart, S. Malhouitre, S. Olivier, and L. O'Faolain, "Low-loss, compact, spot-sizeconverter based vertical couplers for photonic integrated circuits," J. Phys. D 52, 214001 (2019).

- N. Kohli, M. Ménard, and W. N. Ye, "Efficient TE/TM spot-size converter for broadband coupling to single mode fibers," OSA Contin. 2, 2428–2438 (2019).

- T. Tsuchizawa, K. Yamada, H. Fukuda, T. Watanabe, J. I. Takahashi, M. Takahashi, T. Shoji, E. Tamechika, S. I. Itabashi, and H. Morita, "Microphotonics devices based on silicon microfabrication technology," IEEE J. Sel. Top. Quantum Electron. 11, 232–239 (2005).

- S. L. Lai, D. Johnson, and R. Westerman, "Aspect ratio dependent etching lag reduction in deep silicon etch processes," J. Vac. Sci. Technol. A 24, 1283–1288 (2006).

- N. Fang, Z. Yang, A. Wu, J. Chen, M. Zhang, S. Zou, and X. Wang, "Three-dimensional tapered spot-size converter based on (111) silicon-on-insulator," IEEE Photon. Technol. Lett. 21, 820–822 (2009).

- Z. Yang, "Fabrication and characterization of integrated threedimensional linear taper on silicon-on-insulator," Opt. Eng. 48, 030503 (2009).

- R. Holly, K. Hingerl, R. Merz, and P. Hudek, "Fabrication of silicon 3D taper structures for optical fibre to chip interface," Microelectron. Eng. 84, 1248–1251 (2007).

- M. Fritze, J. Knecht, C. Bozler, C. Keast, J. Fijol, S. Jacobson, P. Keating, J. LeBlanc, E. Fike, B. Kessler, M. Frish, and C. Manolatou, "Fabrication of three-dimensional mode converters for silicon-based integrated optics," J. Vac. Sci. Technol. B 21, 2897–2902 (2003).

- A. N. M. M. Choudhury, T. R. Stanczyk, D. Richardson, A. Donval, R. Oron, and M. Oron, "Method of improving light coupling efficiency between optical fibers and silicon waveguides," IEEE Photon. Technol. Lett. 17, 1881–1883 (2005).

- L.-H. Li, "Monolithically integrated low-loss three-dimensional spot-size converter and silicon photonic waveguides constructed by nanotuned Bosch process and oxidation," J. Micro/Nanolithography MEMS MOEMS 10, 023002 (2011).

- C.-W. Liao, Y.-T. Yang, S.-W. Huang, and M.-C. M. Lee, "Fiber-corematched three-dimensional adiabatic tapered couplers for integrated photonic devices," J. Lightwave Technol. 29, 770–774 (2011).

- H. Choo, M.-K. Kim, M. Staffaroni, T. J. Seok, J. Bokor, S. Cabrini, P. J. Schuck, M. C. Wu, and E. Yablonovitch, "Nanofocusing in a metalinsulator-metal gap plasmon waveguide with a three-dimensional linear taper," Nat. Photonics 6, 838–844 (2012).

- T. Shoji, T. Tsuchizawa, T. Watanabe, K. Yamada, and H. Morita, "Low loss mode size converter from 0.3 [micro sign]m square Si wire waveguides to singlemode fibres," Electron. Lett. 38, 1669–1670 (2002).

- Q. Fang, J. Song, X. Luo, X. Tu, L. Jia, M. Yu, and G. Lo, "Low loss fiber-to-waveguide converter with a 3-D functional taper for silicon photonics," IEEE Photon. Technol. Lett. 28, 2533–2536 (2016).

- M. H. P. Pfeiffer, J. Liu, A. S. Raja, T. Morais, B. Ghadiani, and T. J. Kippenberg, "Ultra-smooth silicon nitride waveguides based on the

Damascene reflow process: fabrication and loss origins," Optica 5, 884–892 (2018).

- R. Petra, S. Z. Oo, A. Tarazona, R. Cernansky, S. A. Reynolds, A. Z. Khokhar, V. Mittal, D. J. Thomson, A. Politi, G. Z. Mashanovich, G. T. Reed, and H. M. H. Chong, "HWCVD a-Si:H interlayer slope waveguide coupler for multilayer silicon photonics platform," Opt. Express 27, 15735–15749 (2019).

- 40. W. R. Headley, *Optical Ring Resonators in Silicon-on- insulator* (University of Surrey, 2005).

- R. A. Gottscho, "Microscopic uniformity in plasma etching," J. Vac. Sci. Technol. B 10, 2133–2147 (1992).

- W. Rangelow, "Critical tasks in high aspect ratio silicon dry etching for microelectromechanical systems," J. Vac. Sci. Technol. A 21, 1550–1562 (2003).

- D. Keil and E. Anderson, "Characterization of reactive ion etch lag scaling," J. Vac. Sci. Technol. B 19, 2082–2088 (2001).

- 44. X. Li, L. Ling, X. Hua, M. Fukasawa, G. S. Oehrlein, M. Barela, and H. M. Anderson, "Effects of Ar and O<sub>2</sub> additives on SiO<sub>2</sub> etching in C4F8-based plasmas," J. Vac. Sci. Technol. A **21**, 284–293 (2003).

- M. Douix, C. Baudot, D. Marris-Morini, A. Valéry, D. Fowler, P. Acosta-Alba, S. Kerdilès, C. Euvrard, R. Blanc, R. Beneyton, A. Souhaité, S. Crémer, N. Vulliet, L. Vivien, and F. Boeuf, "Low loss poly-silicon for high performance capacitive silicon modulators," Opt. Express 26, 5983–5990 (2018).

- J. Fujikata, M. Takahashi, S. Takahashi, T. Horikawa, and T. Nakamura, "High-speed and high-efficiency Si optical modulator with MOS junction, using solid-phase crystallization of polycrystalline silicon," Jpn. J. Appl. Phys. 55, 042202 (2016).

- W. Chen, R. Cariou, G. Hamon, R. Léal, J.-L. Maurice, and P. R. i Cabarrocas, "Influence of deposition rate on the structural properties of plasma-enhanced CVD epitaxial silicon," Sci. Rep. 7, 43968 (2017).

- K. Debnath, A. Z. Khokhar, G. T. Reed, and S. Saito, "Fabrication of arbitrarily narrow vertical dielectric slots in silicon waveguides," IEEE Photon. Technol. Lett. 29, 1269–1272 (2017).

- T. D. Bucio, C. Lacava, M. Clementi, J. Faneca, I. Skandalos, A. Baldycheva, M. Galli, K. Debnath, P. Petropoulos, and F. Gardes, "Silicon nitride photonics for the near-infrared," IEEE J. Sel. Top. Quantum Electron. 26, 1–13 (2020).

- T. Aalto, M. Cherchi, M. Harjanne, S. Bhat, P. Heimala, F. Sun, M. Kapulainen, T. Hassinen, and T. Vehmas, "Open-access 3-μm SOI waveguide platform for dense photonic integrated circuits," IEEE J. Sel. Top. Quantum Electron. 25, 1–9 (2019).

- A. J. Zilkie, P. Srinivasan, A. Trita, T. Schrans, G. Yu, J. Byrd, D. A. Nelson, K. Muth, D. Lerose, M. Alalusi, K. Masuda, M. Ziebell, H. Abediasl, J. Drake, G. Miller, H. Nykanen, E. Kho, Y. Liu, H. Liang, H. Yang, F. H. Peters, A. S. Nagra, and A. G. Rickman, "Multi-micron silicon photonics platform for highly manufacturable and versatile photonic integrated circuits," IEEE J. Sel. Top. Quantum Electron. 25, 1–13 (2019).

- A. J. Zilkie, P. Seddighian, B. J. Bijlani, W. Qian, D. C. Lee, S. Fathololoumi, J. Fong, R. Shafiiha, D. Feng, B. J. Luff, X. Zheng, J. E. Cunningham, A. V. Krishnamoorthy, and M. Asghari, "Power-efficient III-V/silicon external cavity DBR lasers," Opt. Express 20, 23456–23462 (2012).

- 53. J. X. B. Sia, X. Li, W. Wang, Z. Qiao, X. Guo, J. Zhou, C. G. Littlejohns, C. Liu, G. T. Reed, and H. Wang, "Sub-kHz linewidth, hybrid III-V/silicon wavelength-tunable laser diode operating at the application-rich 1647– 1690 nm," Opt. Express 28, 25215–25224 (2020).

- 54. T. Matsumoto, T. Kurahashi, R. Konoike, K. Suzuki, K. Tanizawa, A. Uetake, K. Takabayashi, K. Ikeda, H. Kawashima, S. Akiyama, and S. Sekiguchi, "Hybrid-integration of SOA on silicon photonics platform based on flip-chip bonding," J. Lightwave Technol. **37**, 307–313 (2019).

- 55. https://doi.org/10.5258/SOTON/D1718.