## University of Southampton Research Repository

Copyright © and Moral Rights for this thesis and, where applicable, any accompanying data are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis and the accompanying data cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content of the thesis and accompanying research data (where applicable) must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holder/s.

When referring to this thesis and any accompanying data, full bibliographic details must be given, e.g.

Thesis: Author (Year of Submission) "Full thesis title", University of Southampton, name of the University Faculty or School or Department, PhD Thesis, pagination.

Data: Author (Year) Title. URI [dataset]

UNIVERSITY OF SOUTHAMPTON

# Neural Spike Classification Acceleration with RRAM Technologies

by

Patrick Foster

A report submitted in partial fulfillment for the

degree of Doctor of Philosophy

in the

Faculty of Engineering and Physical Sciences

Zepler Institute

November 2023

## Academic Thesis: Declaration of Authorship

---

I, Patrick Foster declare that this thesis and the work presented in it are my own and has been generated by me as the result of my own original research.

*Neural Spike Classification Acceleration with RRAM Technologies*

I confirm that:

This work was done wholly or mainly while in candidature for a research degree at this University;

Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

Where I have consulted the published work of others, this is always clearly attributed;

Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

I have acknowledged all main sources of help;

Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

Parts of this work have been published as:

Patrick Foster, Jinqi Huang, Alex Serb, Spyros Stathopoulos, Christos Papavassiliou, and Themis Prodromakis. An FPGA-based system for generalised electron devices testing. *Scientific Reports*, 2022.

P. Foster, J. Huang, A. Serb, T. Prodromakis, and C. Papavassiliou. An FPGA based system for interfacing with crossbar arrays. In *2020 IEEE International Symposium on Circuits and Systems (ISCAS)*, pages 1–4, 2020.

## Copyright Declaration

The copyright of this thesis rests with the author and is made available under a Creative Commons Attribution Non-Commercial No Derivatives licence. Researchers are free to copy, distribute or transmit the thesis on the condition that they attribute it, that they do not use it for commercial purposes and that they do not alter, transform or build upon it. For any reuse or redistribution, researchers must make clear to others the licence terms of this work.

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF ENGINEERING AND PHYSICAL SCIENCES

ZEPLER INSTITUTE

by **Patrick Foster**

Spike classification is an area of critical importance in neurological medicine. The behaviour of neurons is critical in diagnosis of disease, understanding neural structures, and operating prostheses. The probe technology used to gather *in situ* data from neurons has seen significant advances in the past decade, but the technology required to process this vast amount of data lags behind and this thesis aims to address the data processing aspect of this issue. A novel analogue circuit that conducts most of the sorting in the pre-processing stage is presented, demonstrating the feasibility of such a system using memristive devices. This thesis covers the progress made during this research project; the development of a new instrument for the testing of memristors and memristor related circuits, the design of a new analogue cell for use in template matching systems, and the testing and simulation of this cell both in isolation and in a simple template matching system. The circuit developed demonstrated comparable energy dissipation to current state of the art spike sorting systems, without the need to digitise the signals being processed. This development opens the path to the fabrication of an integrated memristor based spike sorting system suitable for neural signal processing.

# Contents

|                         |                                                           |           |

|-------------------------|-----------------------------------------------------------|-----------|

| <b>Nomenclature</b>     | <b>xix</b>                                                |           |

| <b>Acknowledgements</b> | <b>xxi</b>                                                |           |

| <b>1</b>                | <b>Introduction</b>                                       | <b>1</b>  |

| 1.1                     | Motivation                                                | 1         |

| 1.2                     | Research Objectives                                       | 2         |

| 1.3                     | Structure                                                 | 3         |

| 1.4                     | Contributions                                             | 3         |

| <b>2</b>                | <b>Processing of Neuronal Spike Signals</b>               | <b>5</b>  |

| 2.1                     | Neural Signals                                            | 5         |

| 2.2                     | Spike Detection and Sorting                               | 6         |

| 2.2.1                   | Software Sorting                                          | 7         |

| 2.2.2                   | Hardware Sorting                                          | 7         |

| 2.3                     | Memory                                                    | 8         |

| 2.3.1                   | Crossbar Arrays                                           | 11        |

| 2.4                     | Instrumentation                                           | 11        |

| 2.5                     | Summary                                                   | 12        |

| <b>3</b>                | <b>Mixed signal parallel instrumentation</b>              | <b>13</b> |

| 3.1                     | Introduction                                              | 13        |

| 3.2                     | Instrumentation                                           | 13        |

| 3.3                     | ArC TWO                                                   | 14        |

| 3.4                     | Specification                                             | 15        |

| 3.5                     | Design                                                    | 15        |

| 3.6                     | Performance                                               | 20        |

| 3.6.1                   | Noise Floor                                               | 20        |

| 3.6.2                   | Crossbar Array Read Accuracy                              | 22        |

| 3.6.3                   | Pulse Performance                                         | 23        |

| 3.6.4                   | Device Characterisation                                   | 24        |

| 3.6.5                   | Mixed Signal Testing                                      | 25        |

| 3.7                     | Conclusion                                                | 26        |

| <b>4</b>                | <b>Template matching using RRAM configurable circuits</b> | <b>27</b> |

| 4.1                     | Introduction                                              | 27        |

| 4.2                     | Template Matching                                         | 27        |

| 4.3                     | Inverter TXL                                              | 28        |

---

|          |                                          |           |

|----------|------------------------------------------|-----------|

| 4.4      | Split TXL . . . . .                      | 30        |

| 4.5      | Capacitive Subtractor TXL . . . . .      | 31        |

| 4.6      | Conclusions . . . . .                    | 32        |

| <b>5</b> | <b>Split TXL</b>                         | <b>35</b> |

| 5.1      | Introduction . . . . .                   | 35        |

| 5.2      | Objective . . . . .                      | 35        |

| 5.3      | Design . . . . .                         | 36        |

| 5.4      | Model . . . . .                          | 38        |

| 5.4.1    | Resistor Model . . . . .                 | 38        |

| 5.4.2    | Memristor Model . . . . .                | 40        |

| 5.5      | Integrated Simulation . . . . .          | 41        |

| 5.5.1    | Design . . . . .                         | 41        |

| 5.5.2    | Assessment . . . . .                     | 42        |

| 5.5.3    | Energy . . . . .                         | 44        |

| 5.5.4    | Process Variation . . . . .              | 45        |

| 5.6      | TXL Template . . . . .                   | 46        |

| 5.7      | Conclusion . . . . .                     | 48        |

| <b>6</b> | <b>Future Directions and Conclusions</b> | <b>49</b> |

| 6.1      | Conclusions . . . . .                    | 49        |

| 6.2      | Future Directions . . . . .              | 50        |

| 6.2.1    | TXL . . . . .                            | 50        |

| 6.2.2    | Further development of ArC TWO . . . . . | 50        |

| 6.2.2.1  | Pulse Generator . . . . .                | 51        |

| <b>A</b> | <b>ArC Neuro Prototype</b>               | <b>53</b> |

| A.1      | Overview . . . . .                       | 53        |

| A.2      | Software . . . . .                       | 54        |

| A.2.1    | . . . . .                                | 54        |

| <b>B</b> | <b>ArC Neuro Block 1</b>                 | <b>55</b> |

| B.1      | Overview . . . . .                       | 55        |

| B.2      | Design Issues . . . . .                  | 56        |

| <b>C</b> | <b>ArC Neuro Block 2</b>                 | <b>59</b> |

| C.1      | Overview . . . . .                       | 59        |

| C.2      | Design Issues . . . . .                  | 61        |

| <b>D</b> | <b>ArC Neuro Block 3</b>                 | <b>63</b> |

| D.1      | Overview . . . . .                       | 63        |

| <b>E</b> | <b>ArC TWO Daughterboards</b>            | <b>65</b> |

| E.1      | 32NNA68 . . . . .                        | 65        |

| E.2      | 32SLP48DIP . . . . .                     | 65        |

| E.3      | 32BNC12/32SMA32 . . . . .                | 66        |

| E.4      | 32NNA68VAR . . . . .                     | 66        |

| E.5      | TXL daughterboards . . . . .             | 67        |

|                                  |           |

|----------------------------------|-----------|

| <b>F ArC TWO Contributions</b>   | <b>69</b> |

| F.1 FPGA Configuration . . . . . | 69        |

| F.1.1 AMP PRP . . . . .          | 69        |

| F.2 Software . . . . .           | 70        |

| <b>Bibliography</b>              | <b>71</b> |

# List of Figures

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

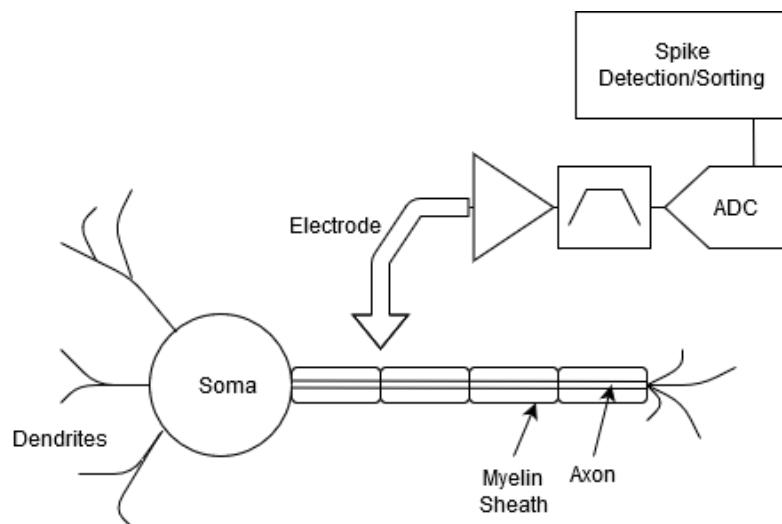

| 2.1  | Diagram of a neuron with an implanted electrode and associated instrumentation. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5  |

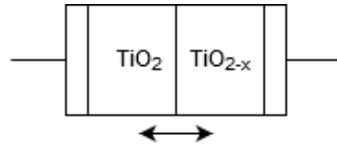

| 2.2  | Diagram of a $\text{TiO}_{2-x}$ memristor. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10 |

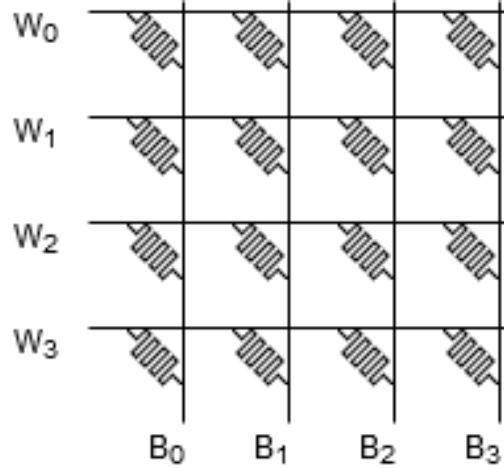

| 2.3  | Diagram of a small memristor crossbar array. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11 |

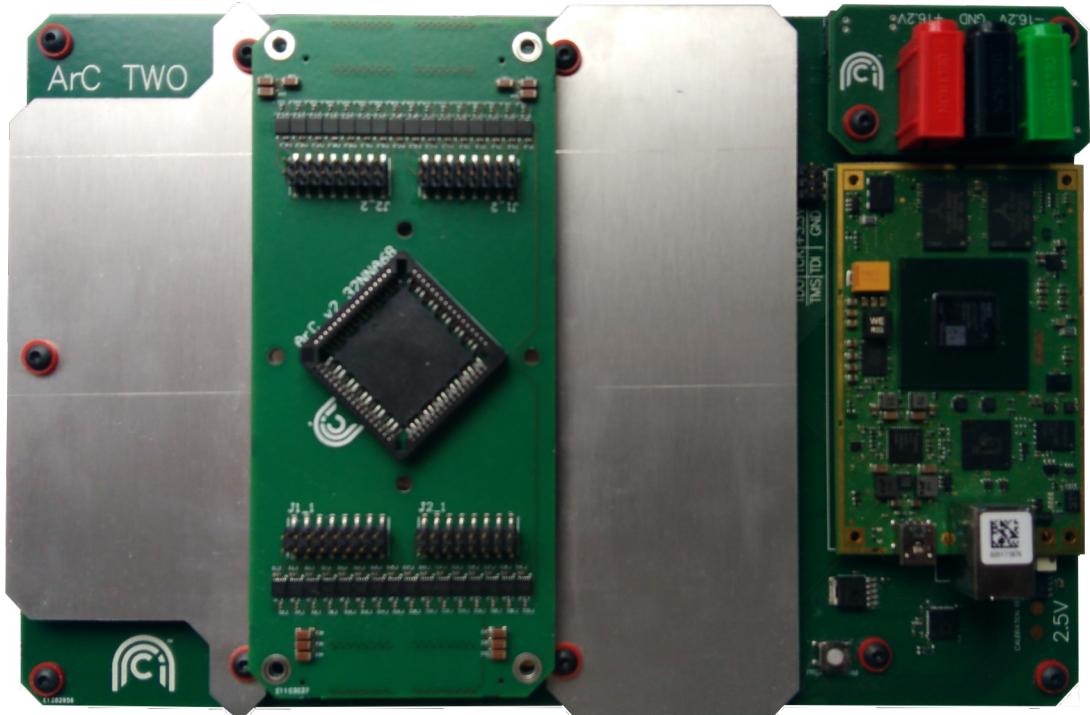

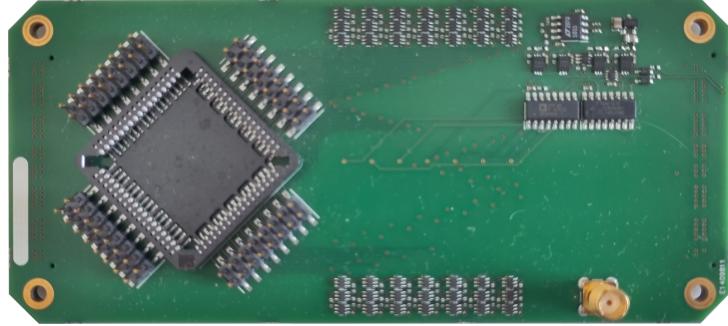

| 3.1  | Photograph of the ArC TWO. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 14 |

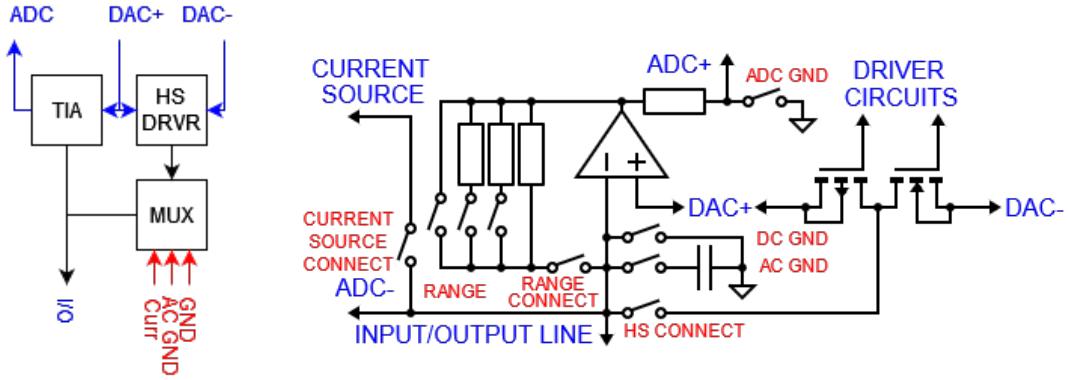

| 3.2  | Left: A system-level schematic of the channel. Right: A component-level schematic of the channel architecture. Signals are labelled in blue, switches are labelled in red. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16 |

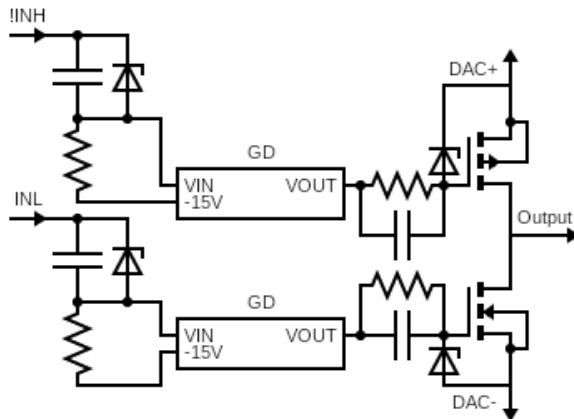

| 3.3  | Concept schematic of the gate driver circuit. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 16 |

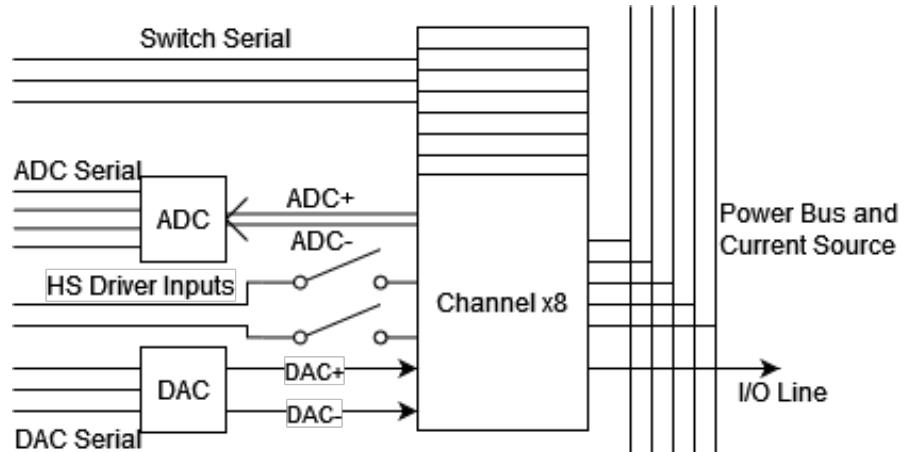

| 3.4  | Concept schematic of the channel cluster, showing connections for one of the eight channels of the cluster. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17 |

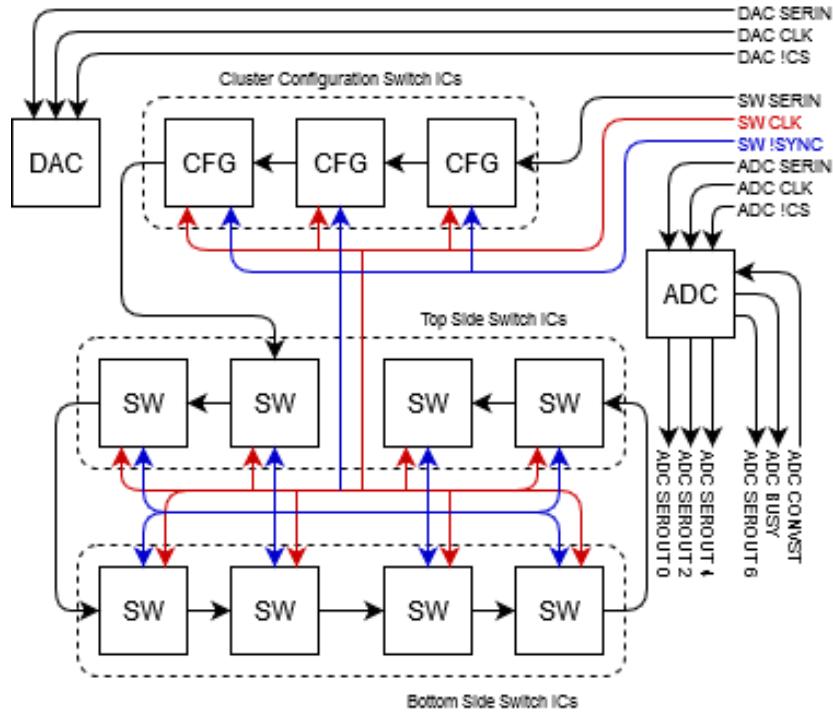

| 3.5  | Diagram of the serial connections within the channel cluster, showing the daisy-chain SPI bus that weaves through all switch ICs in the cluster. . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 18 |

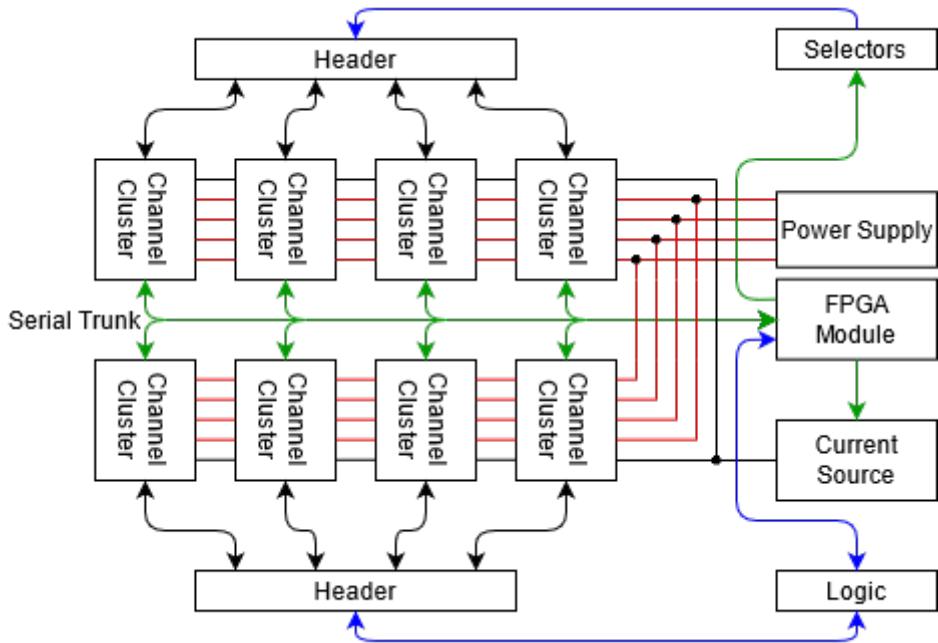

| 3.6  | Block diagram of the full instrument, showing various systems as arranged on the PCB. Analogue signals are shown in black, parallel digital signals in blue, serial signals in green, and power in red. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 18 |

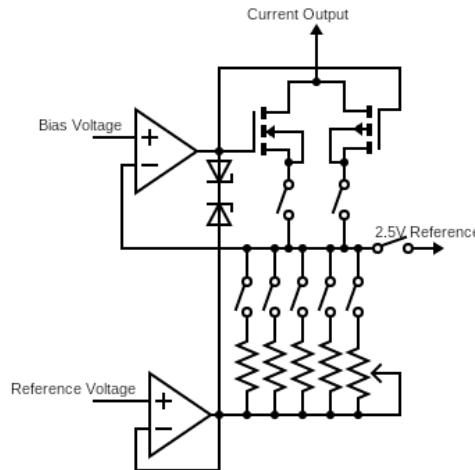

| 3.7  | Concept schematic of the current source. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19 |

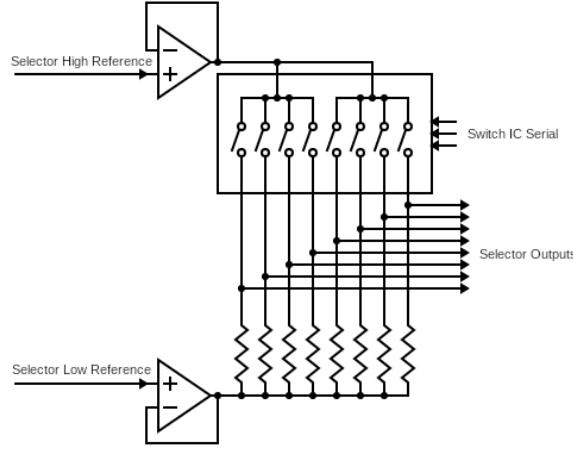

| 3.8  | Concept schematic of one quarter of the selectors bank. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20 |

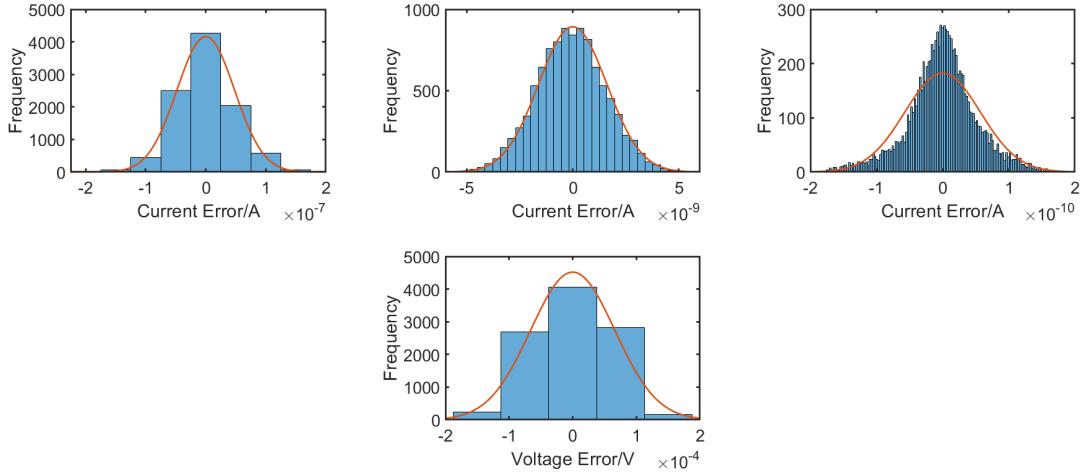

| 3.9  | Histograms showing noise characteristics of the various modes of measurement. All histograms have one bin per ADC code with widths of 47.6 nA, 355 pA, 2.60 pA, and 78.1 $\mu\text{V}$ respectively. Top: 10k point histograms of current read-out tests, overlaid with Gaussian distribution estimates. Top left: $820\ \Omega$ TIA range yields $\sigma = 48\ \text{nA}$ . Top centre: $110\ \text{k}\Omega$ TIA range yields $\sigma = 1.6\ \text{nA}$ . Top right: $15\ \text{M}\Omega$ TIA range yields $\sigma = 57\ \text{pA}$ . Bottom centre: 10k point histogram of a read-out voltage error test ( $\text{V}=\text{GND}$ ), overlaid with Gaussian distribution estimate of $\sigma = 65\ \mu\text{V}$ . . . . . | 21 |

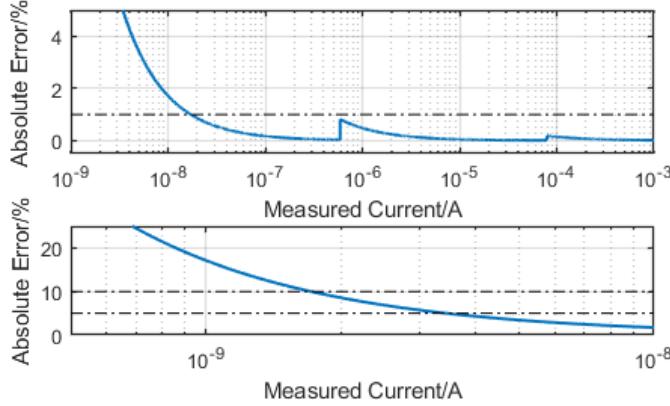

| 3.10 | Graph showing predicted absolute error based on $3\sigma$ current noise error, with dotted lines to show 1, 5, and 10% error. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 22 |

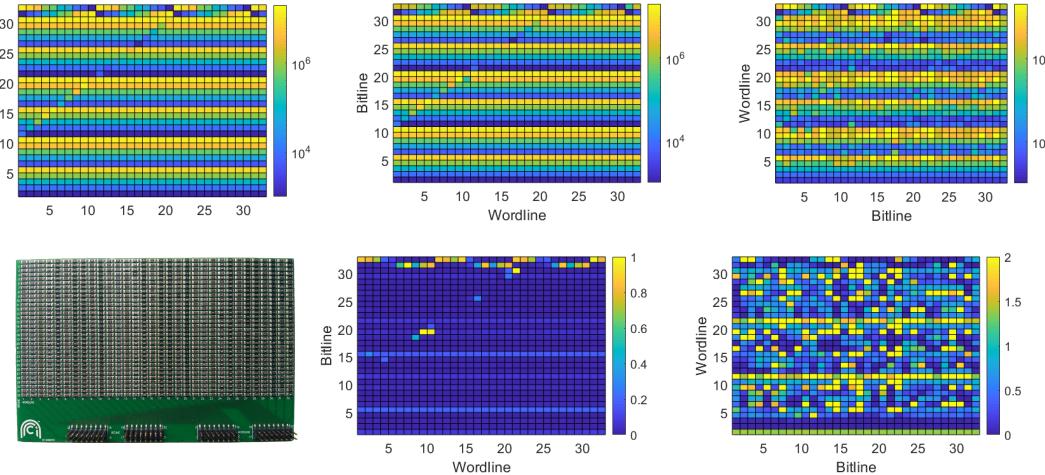

| 3.11 | Array read operations for a 32x32 resistor array. Top left shows the array as designed, with resistors ranging from $1\ \text{k}\Omega$ to $15\ \text{M}\Omega$ . The colourbar is scaled from $1\ \text{k}\Omega$ to $20\ \text{M}\Omega$ . Top centre shows the array as read in columns and bottom centre shows the proportional error. Top right shows the array as read in rows and bottom right shows the proportional error. Bottom left is a photograph of the test array. . . . .                                                                                                                                                                                                                                  | 22 |

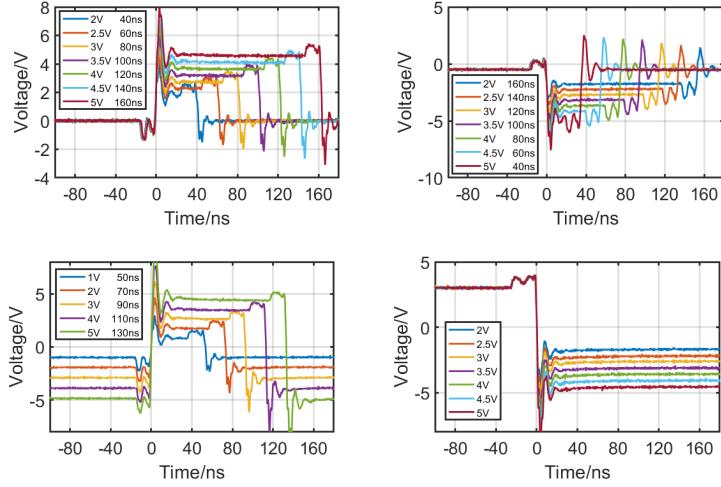

| 3.12 | Oscilloscope captures of a variety of pulses produced with the high speed pulse generator. Top left: +VE pulses starting at 0 V. Top right: -VE pulses starting at $-0.5\ \text{V}$ . Bottom left: +VE pulses symmetrical around 0 V. Bottom right: Continuous pulses starting at 3 V. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                              | 24 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

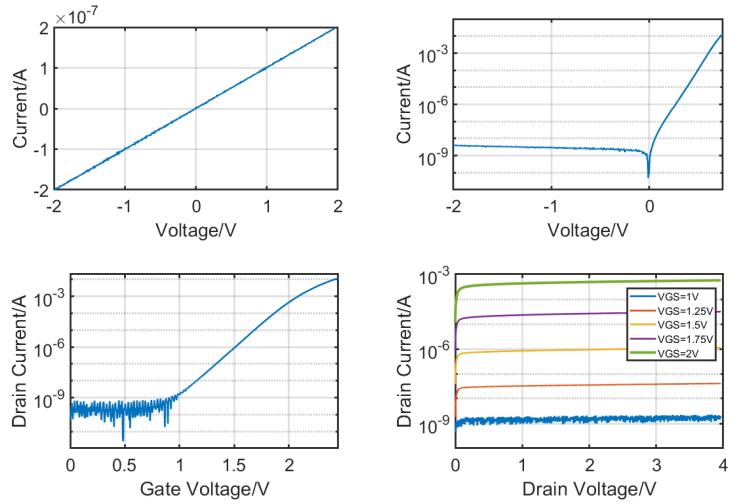

| 3.13 | IV characteristics of a small selection of components. Top left: IV sweep of a $10\text{ M}\Omega$ resistor. Top right: IV sweep of a 1N4148 diode, from $-2\text{ V}$ to $0.75\text{ V}$ . Bottom left and right: Gate terminal drain terminal sweeps of a 2N7000 nFET. . . . .                                                                                                                                                                                                                                                                                              | 25 |

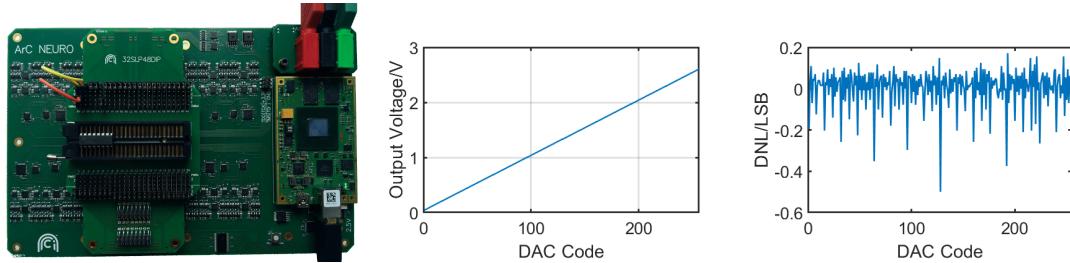

| 3.14 | Results from an automated test of an AD558J DAC (Left) in $2.56\text{ V}$ range. Centre shows the output from code 0 to code 255. Right shows the normalised differential non-linearity. . . . .                                                                                                                                                                                                                                                                                                                                                                              | 25 |

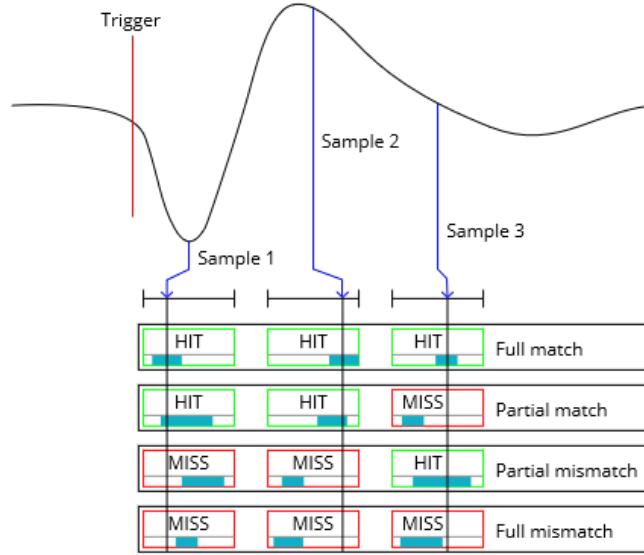

| 4.1  | An example of template matching with window comparators. This diagram shows three samples captured from a waveform being tested against four templates. . . . .                                                                                                                                                                                                                                                                                                                                                                                                               | 28 |

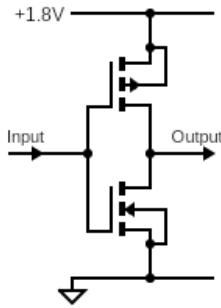

| 4.2  | Circuit diagram of a TXL cell. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29 |

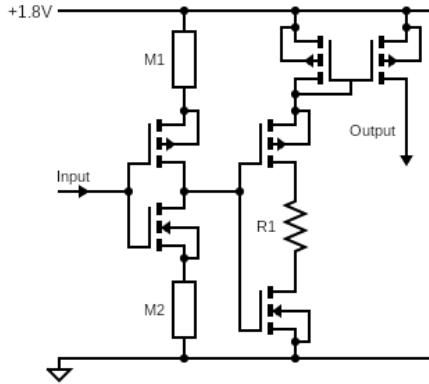

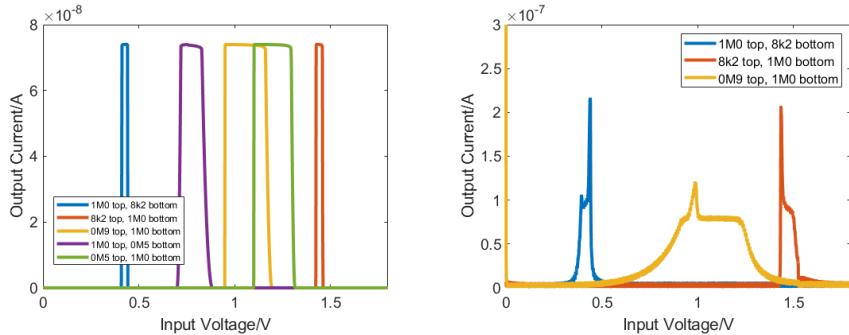

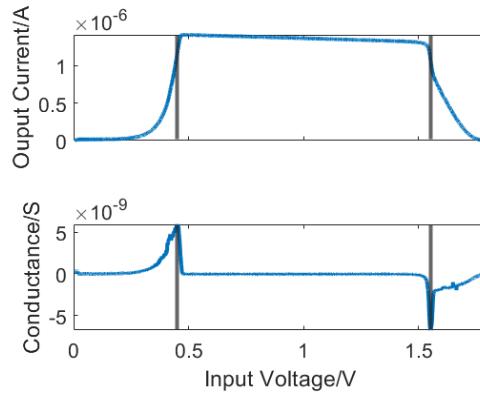

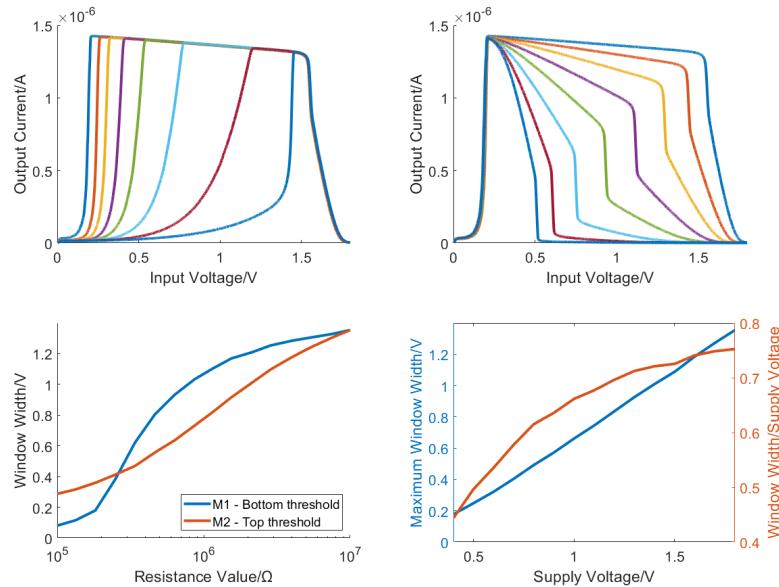

| 4.3  | Simulated and real behaviour of the TXL cell, showing the output current at several settings of the top (M1) and bottom (M2) memristors. Left: simulated behaviour. Right: data collected from tests on a PCB model. .                                                                                                                                                                                                                                                                                                                                                        | 29 |

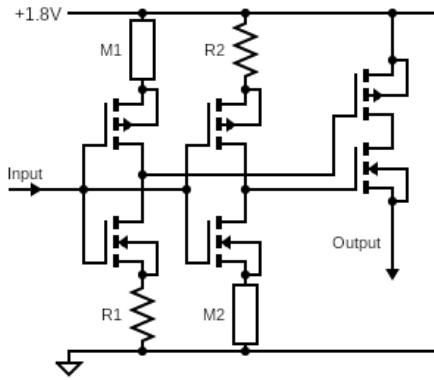

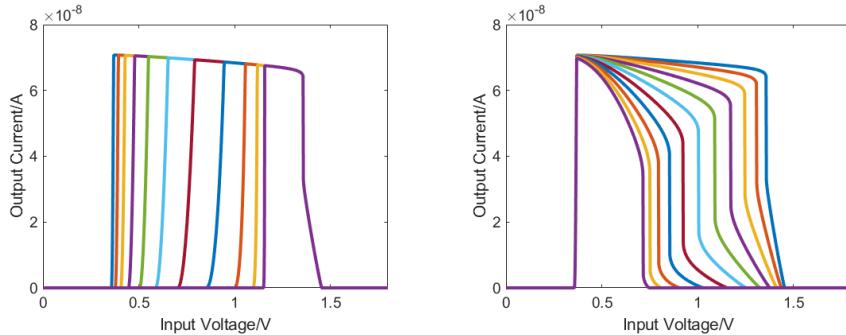

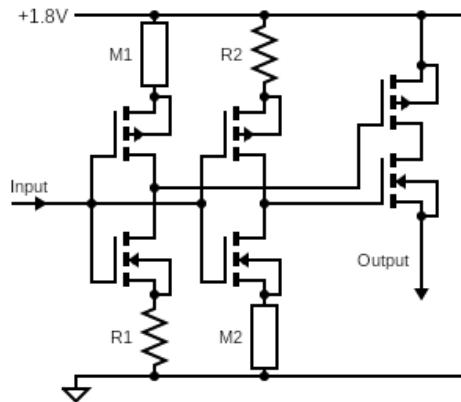

| 4.4  | Circuit diagram of the Split TXL design. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 30 |

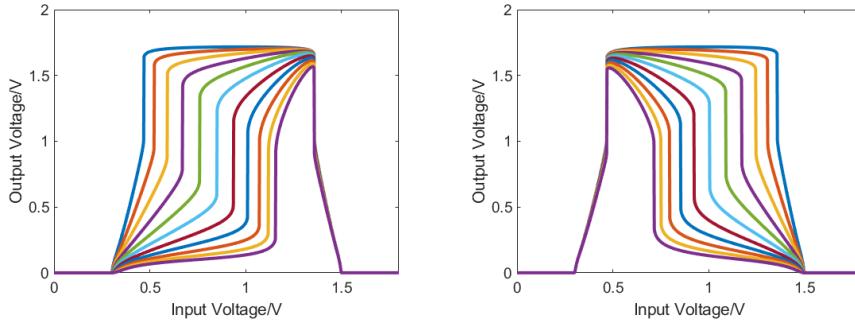

| 4.5  | Simulated input output relationship of the Split TXL design. R1 and R2 are fixed at $1\text{ M}\Omega$ while one of the memristors is swept from $100\text{ k}\Omega$ to $10\text{ M}\Omega$ . Left: sweep of M1. Right: sweep of M2. . . . .                                                                                                                                                                                                                                                                                                                                 | 30 |

| 4.6  | Circuit diagram of the capacitive subtractor design. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 31 |

| 4.7  | Simulated input output relationship of the capacitive subtractor design. R1 and R2 are fixed at $1\text{ M}\Omega$ while one of the memristors is swept from $100\text{ k}\Omega$ to $10\text{ M}\Omega$ . Left: sweep of M1. Right: sweep of M2. . . . .                                                                                                                                                                                                                                                                                                                     | 32 |

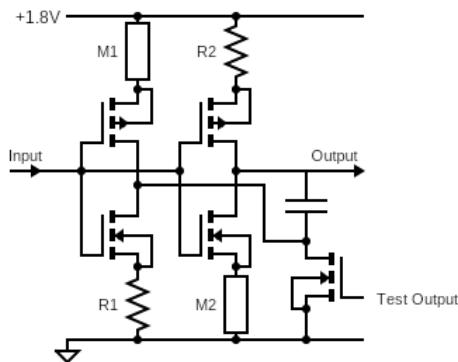

| 5.1  | A diagram of the split TXL circuit. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 36 |

| 5.2  | A diagram of the split TXL circuit. . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 37 |

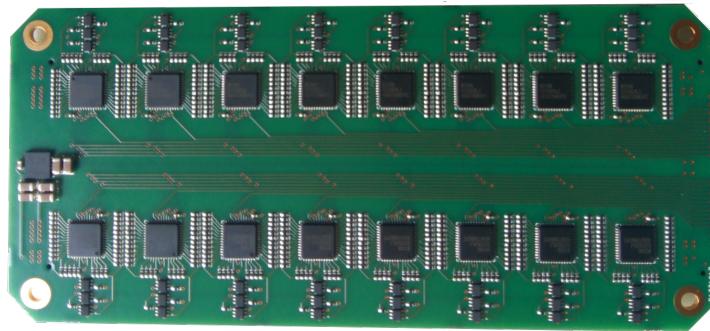

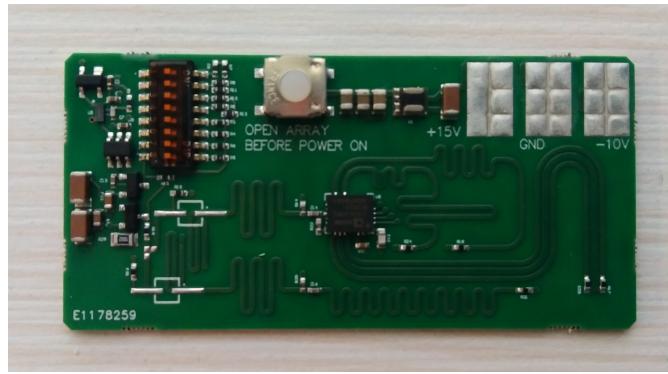

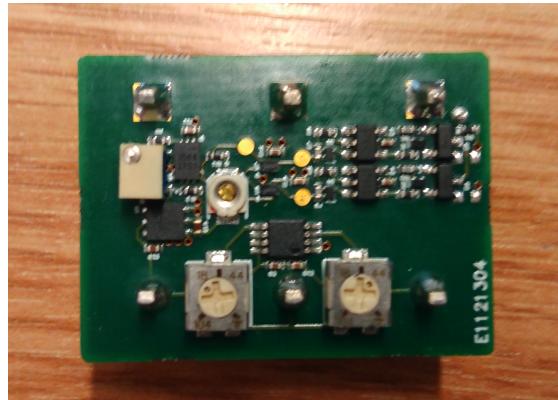

| 5.3  | A photograph of the resistor version of the PCB model of the TXL. .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 38 |

| 5.4  | A diagram of the method used to determine window width. In this case the window width is calculated as $1.1\text{ V}$ . . . . .                                                                                                                                                                                                                                                                                                                                                                                                                                               | 39 |

| 5.5  | Top Left: A graph of the IV characteristics of the PCB model of the TXL circuit, sweeping M1 between $10\text{ M}\Omega$ and $100\text{ k}\Omega$ . Top right: A graph of an identical sweep of M2. Bottom right: A graph of the width of the window as a function of resistor state. Bottom left: A graph of the maximum window width as a function of the supply voltage. . . . .                                                                                                                                                                                           | 39 |

| 5.6  | A photograph of the memristor version of the PCB model of the TXL. .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 40 |

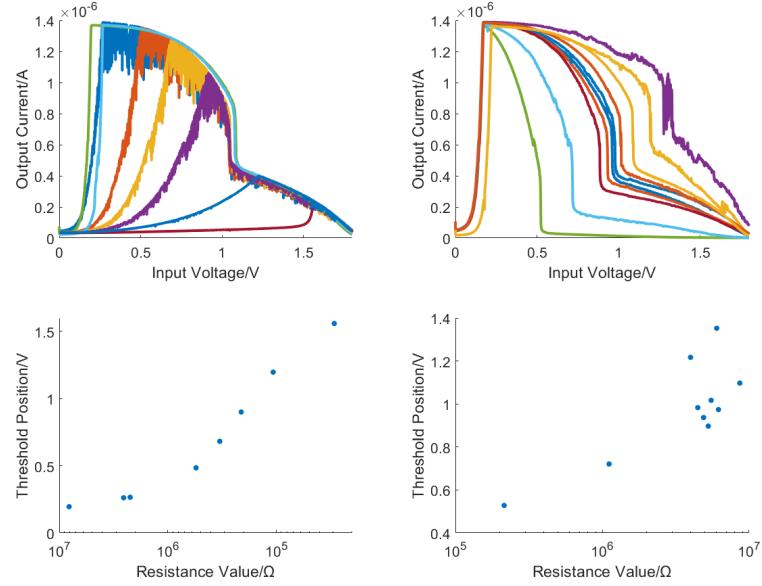

| 5.7  | Top left: A graph of the IV characteristics of the memristor model, sweeping M1 from $8\text{ M}\Omega$ to $30\text{ k}\Omega$ , with M2 at $6\text{-}8\text{ M}\Omega$ . Top right: A graph of a similar sweep of M2 from $200\text{ k}\Omega$ to $8.6\text{ M}\Omega$ , with M1 at $5.6\text{-}6.5\text{ M}\Omega$ . Bottom left: A scatter plot of the window width as a function of the memristor state. Note that the X axis is reversed compared to the bottom right figure. Bottom right: A scatter plot of the window width as a function of memristor state. . . . . | 41 |

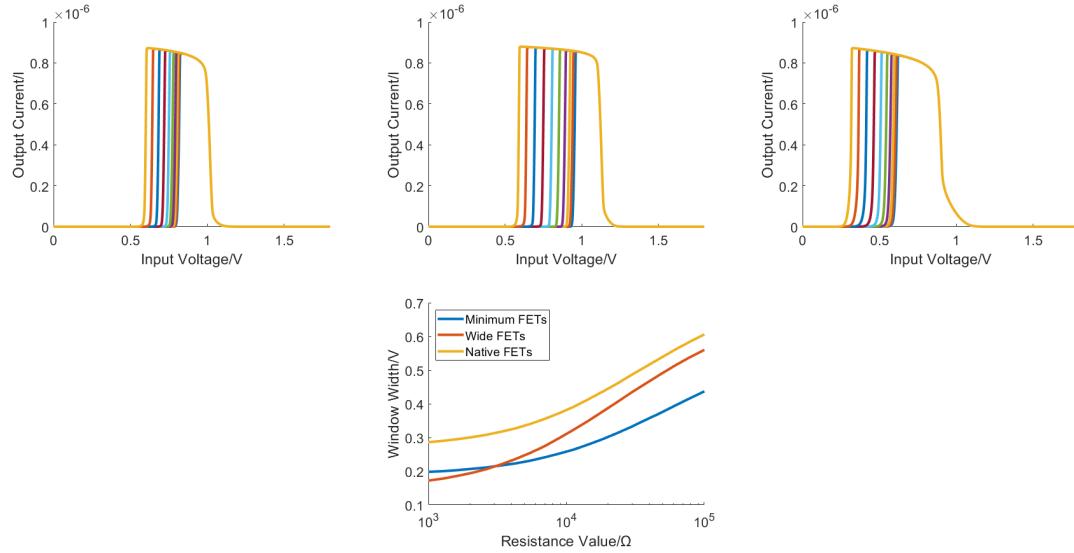

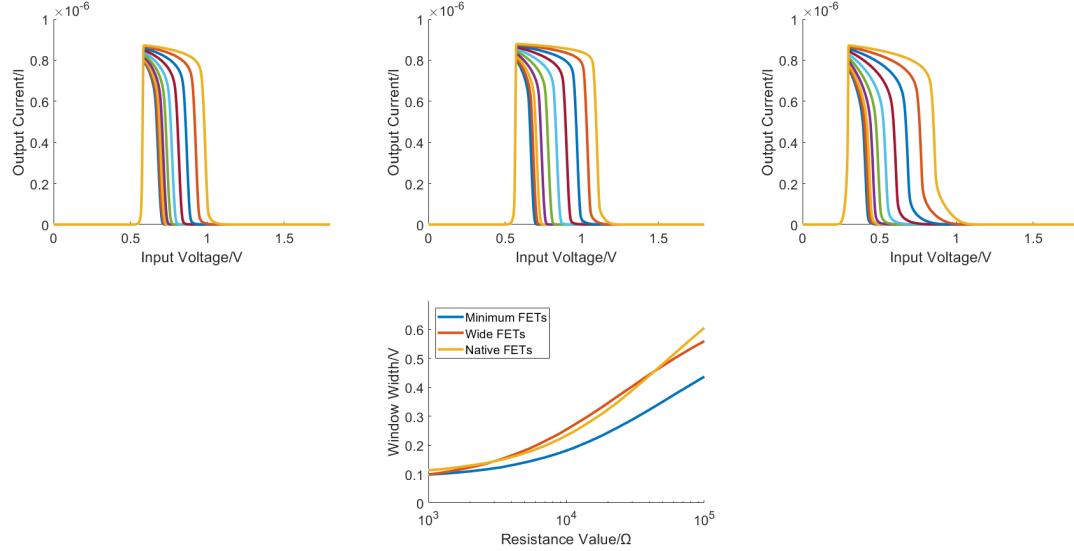

| 5.8  | Top left: A graph of the IV characteristics of the minimum circuit, sweeping M1 from $1\text{ k}\Omega$ to $100\text{ k}\Omega$ . Top centre: A graph of an identical sweep of M1 with the wide circuit. Top right: A graph of an identical sweep of M1 with the native circuit. Bottom: A graph of the window width of all three circuits as a function of M1. . . . .                                                                                                                                                                                                       | 43 |

|      |                                                                                                                                                                                                                                                                                                                                                                         |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.9  | Top left: A graph of the IV characteristics of the minimum circuit, sweeping M2 from $1\text{ k}\Omega$ to $100\text{ k}\Omega$ . Top centre: A graph of an identical sweep of M2 with the wide circuit. Top right: A graph of an identical sweep of M2 with the native circuit. Bottom: A graph of the window width of all three circuits as a function of M2. . . . . | 43 |

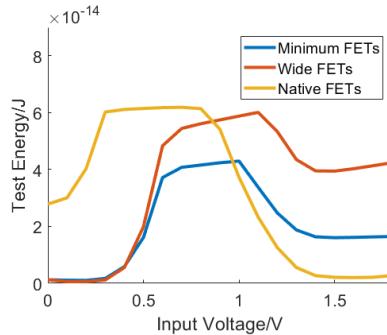

| 5.10 | A graph of the test energy of a single simulated TXL cell, as a function of input voltage. . . . .                                                                                                                                                                                                                                                                      | 44 |

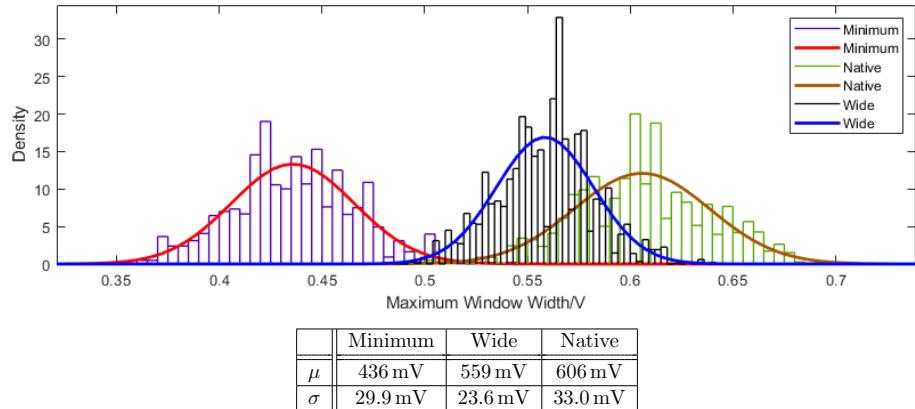

| 5.11 | Top: A histogram plot and fit of a 250 point Monte Carlo simulation of the maximum window width. Bottom: A table of the fit parameters, assuming a normal distribution. . . . .                                                                                                                                                                                         | 45 |

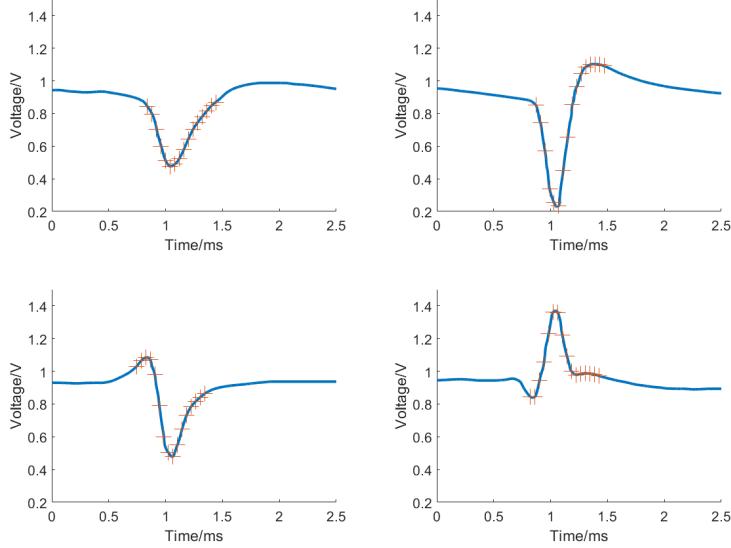

| 5.12 | Graphs of the sample neural spikes used in the array test, with the samples collected marked in orange. Top left: Sample spike 1. Top right: Sample spike 2. Bottom left: Sample spike 3. Bottom right: Sample spike 4. . . . .                                                                                                                                         | 46 |

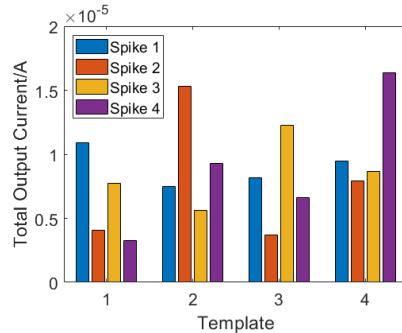

| 5.13 | A graph of the test energy of a single simulated TXL cell, as a function of input voltage. . . . .                                                                                                                                                                                                                                                                      | 47 |

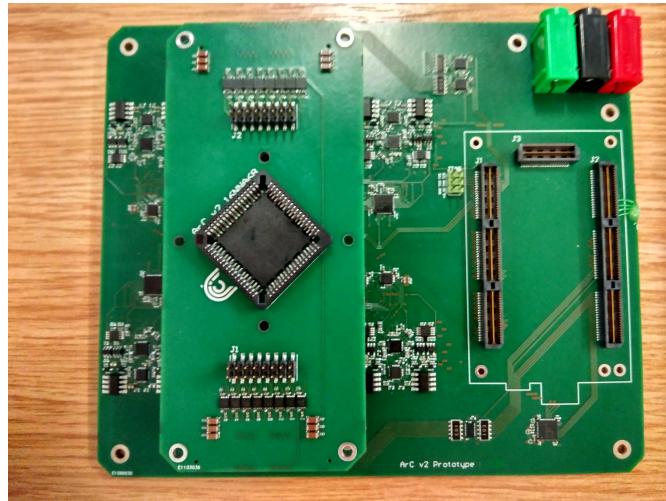

| 5.14 | A photograph of the TXL channel demonstrator. . . . .                                                                                                                                                                                                                                                                                                                   | 48 |

| 6.1  | A photograph of the SRD-based pulse generator. . . . .                                                                                                                                                                                                                                                                                                                  | 51 |

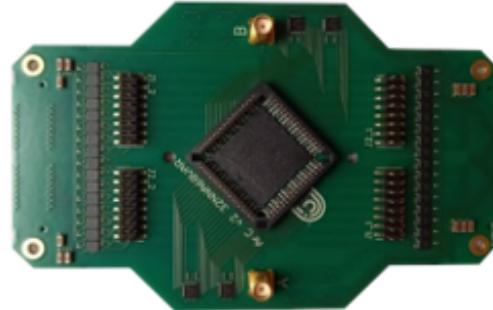

| A.1  | A photograph of the prototype instrument, with mounted daughter-board. . . . .                                                                                                                                                                                                                                                                                          | 53 |

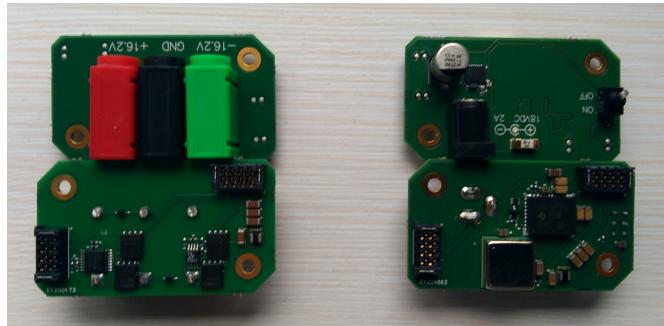

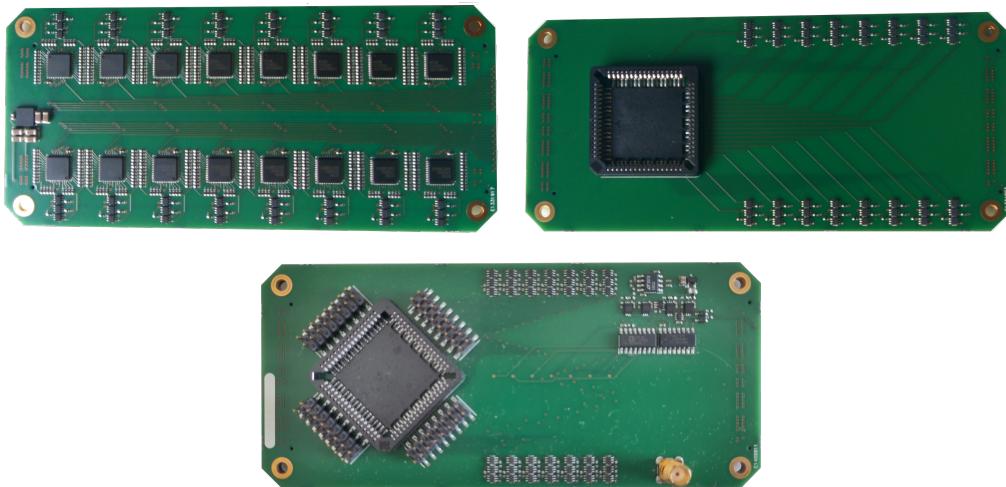

| B.1  | Photograph of the block 1 ArC Neuro. . . . .                                                                                                                                                                                                                                                                                                                            | 55 |

| B.2  | A photograph of the PCB design used to test the revised high speed driver circuit. . . . .                                                                                                                                                                                                                                                                              | 56 |

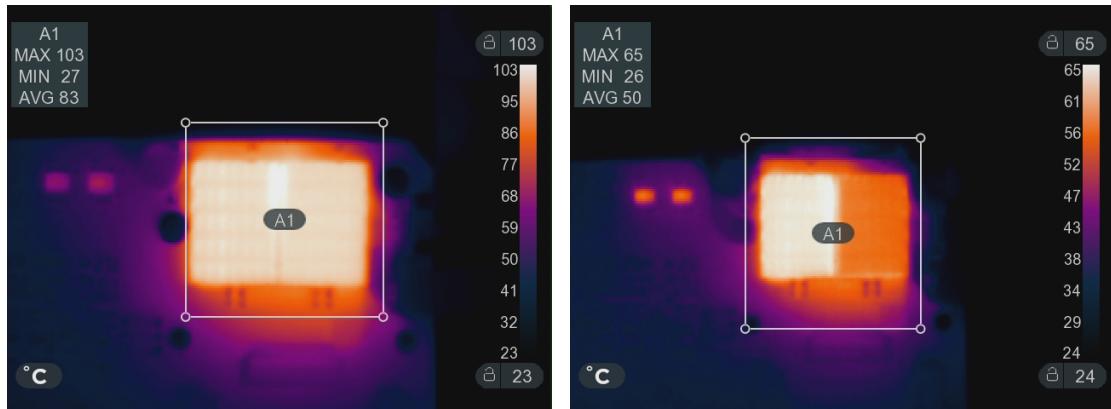

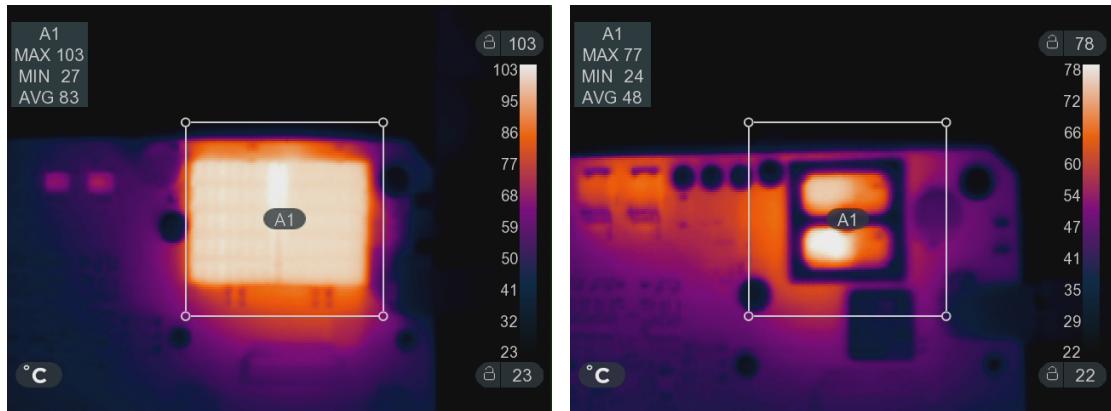

| B.3  | Left: A thermal photograph of the DC/DC modules at equilibrium temperature, with heatsinks fitted. Right: A thermal photograph of the DC/DC modules at equilibrium temperature, with both heatsinks and fan fitted. . . . .                                                                                                                                             | 56 |

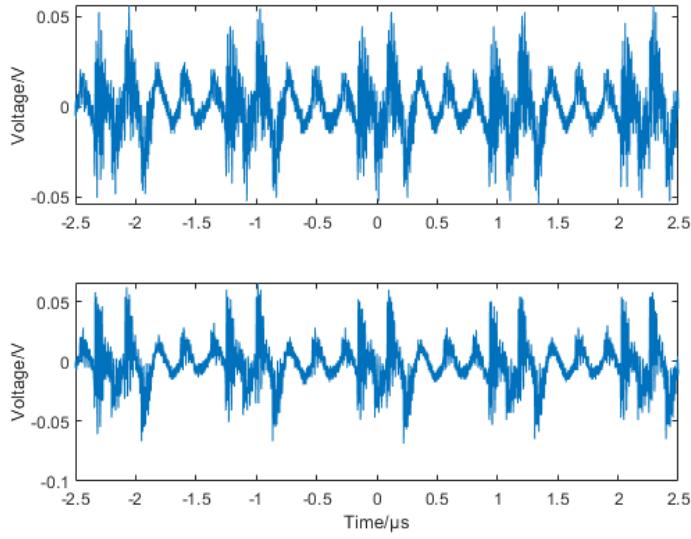

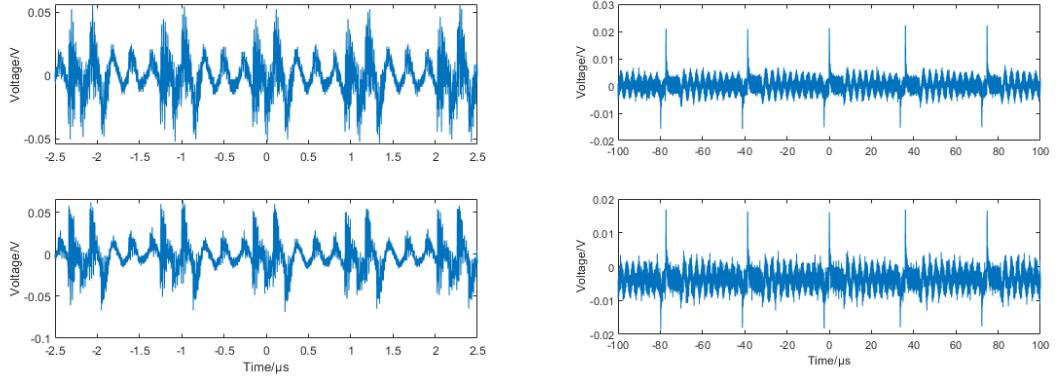

| B.4  | Oscilloscope capture of the noise on the $\pm 15\text{ V}$ supplies. . . . .                                                                                                                                                                                                                                                                                            | 57 |

| C.1  | Photograph of the block 2 ArC Neuro with FPGA module and daughter-board mounted. . . . .                                                                                                                                                                                                                                                                                | 59 |

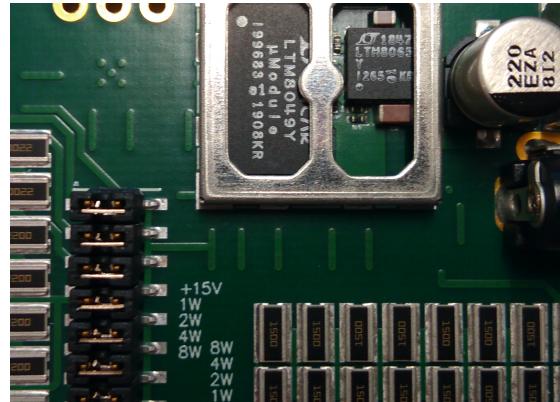

| C.2  | Photograph of the test PCB for the revised power supply circuitry, including load banks. The lid of the EMI shield has been removed to show the circuitry underneath. . . . .                                                                                                                                                                                           | 60 |

| C.3  | Left: A thermal photograph of the DC/DC modules at equilibrium temperature, with heatsinks fitted. Right: A thermal photograph of the revised power supply circuitry at equilibrium temperature. The lid of the EMI shield has been removed to allow for accurate thermography. . . . .                                                                                 | 60 |

| C.4  | Left: An oscilloscope capture of the noise on the $\pm 15\text{ V}$ supplies of the block 1. Right: An oscilloscope capture of the noise on the $\pm 15\text{ V}$ supplies of the block 2. . . . .                                                                                                                                                                      | 61 |

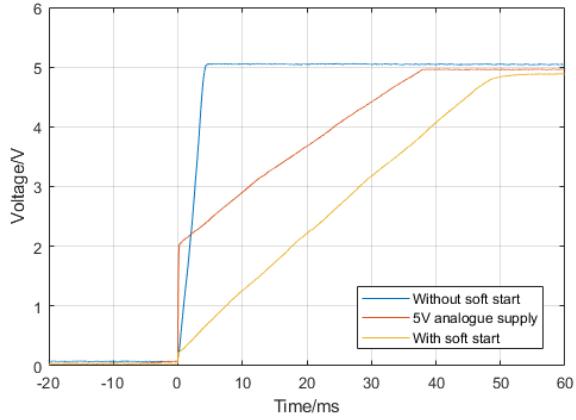

| C.5  | Oscilloscope capture of the startup curves of different FPGA supply solutions. . . . .                                                                                                                                                                                                                                                                                  | 61 |

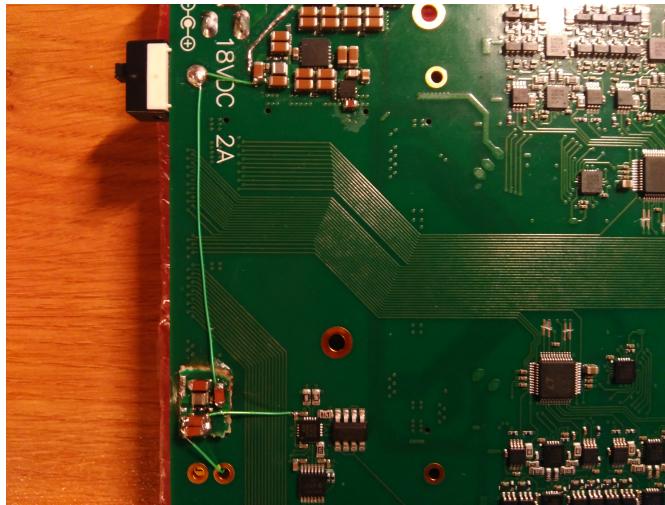

| C.6  | A photograph of a block 2 board that has been modified with a DC/DC module with soft start. . . . .                                                                                                                                                                                                                                                                     | 62 |

| D.1  | A photograph of the block 3 ArC Neuro with FPGA module, daughter-board, and power supply module mounted. . . . .                                                                                                                                                                                                                                                        | 63 |

|                                                                                                                                                                                                                             |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| D.2 A photograph showing a 4 mm supply module on the left and an 18 V <sub>DC</sub> module on the right. . . . .                                                                                                            | 64 |

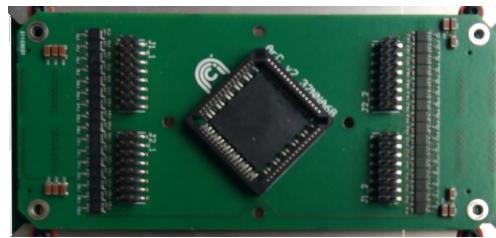

| E.1 A photograph of the 32NNA68 daughterboard. . . . .                                                                                                                                                                      | 65 |

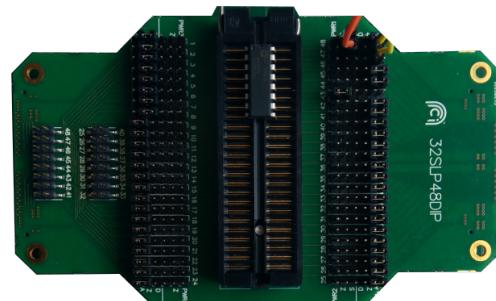

| E.2 A photograph of the 32SLP48DIP daughterboard. . . . .                                                                                                                                                                   | 65 |

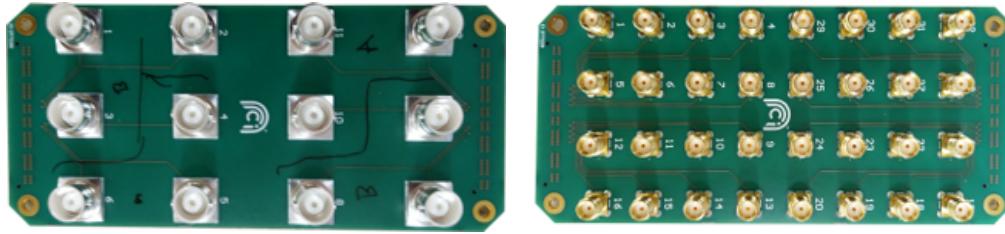

| E.3 Left: A photograph of the 32BNC12 daughterboard. Right: A photograph of the 32SMA32 daughterboard. . . . .                                                                                                              | 66 |

| E.4 A photograph of the 32NNA68VAR daughterboard. . . . .                                                                                                                                                                   | 66 |

| E.5 Top Left: A photograph of the resistor version of the PCB model of the TXL. Top Right: A photograph of the memristor version of the PCB model of the TXL. Bottom: A photograph of the TXL channel demonstrator. . . . . | 67 |

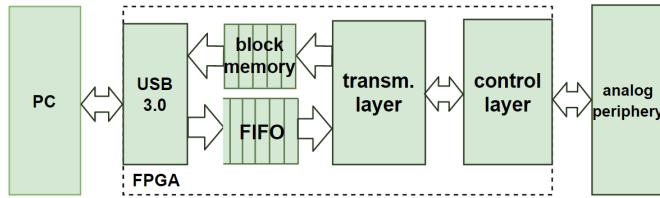

| F.1 A diagram of the architecture of the ArC TWO control system. . . . .                                                                                                                                                    | 69 |

# List of Tables

|     |                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | A table comparing non volatile memory technologies. . . . .                                                                                                                                                                                                                                                                                                                                              | 8  |

| 3.1 | Comparison between this instrument and its predecessor. . . . .                                                                                                                                                                                                                                                                                                                                          | 26 |

| 4.1 | Comparison of the TXL designs described in this chapter. . . . .                                                                                                                                                                                                                                                                                                                                         | 32 |

| 5.1 | Chart of transistor sizes in the three designs that were simulated. . . . .                                                                                                                                                                                                                                                                                                                              | 42 |

| 5.2 | Left: A chart of test energies at typical hit/miss voltages for several process corners. Note that the difference in hit/miss voltage between the circuit variants make this data less useful for comparing the variants. It is more intended to show the response of each circuit to process variation and temperature. Right: A chart of the maximum window width at several process corners . . . . . | 45 |

| F.1 | Chart of the ArC TWO instruction set. . . . .                                                                                                                                                                                                                                                                                                                                                            | 70 |

# Nomenclature

|            |                                                   |

|------------|---------------------------------------------------|

| ADC        | Analogue to Digital Converter                     |

| ASIC       | Application Specific Integrated Circuit           |

| CAM        | Content Addressable Memory                        |

| DAC        | Digital to Analogue Converter                     |

| DUT        | Device Under Test                                 |

| EMI        | Electro-Magnetic Interference                     |

| FeRAM      | Ferroelectric Random Access Memory                |

| FIFO       | First-In, First-Out                               |

| FPGA       | Field Programmable Gate Array                     |

| FWHM       | Full Width at Half Maximum                        |

| GPIO       | General Purpose Input/Output                      |

| IC         | Integrated Circuit                                |

| MOSFET     | Metal Oxide Semiconductor Field Effect Transistor |

| MRAM       | Magnetoresistive Random Access Memory             |

| NLTL       | Non-Linear Transmission Line                      |

| NMOS       | N channel MOSFET                                  |

| PCB        | Printed Circuit Board                             |

| PCM        | Phase Change Memory                               |

| PMOS       | P channel MOSFET                                  |

| RRAM/ReRAM | Resistive Random Access Memory                    |

| SEPIC      | Single Ended Primary Inductor Converter           |

| SMU        | Source Measurement Unit                           |

| SPI        | Serial-Parallel Interface                         |

| SPST       | Single Pole Single Throw                          |

| SRD        | Step Recovery Diode                               |

| TXL        | Template pixel                                    |

## Acknowledgements

I would like to offer thanks to Alex Serb, who has provided guidance and support throughout this project. Without his advice, this project would never have reached completion.

I would like to offer thanks to Jinqi Huang, who collaborated on the development of the ArC TWO, providing the configuration for the FPGA. The countless hours spent in the laboratory brought my creations to life. Her work is as much an accomplishment as anything found in this document.

I would like to offer thanks to Spyros Stathopoulos, who provided the software used to operate the ArC TWO and conduct every experiment in this project. Jinqi may have brought the system to life, but Spyros made it dance.

I would like to offer thanks to Themis Prodromakis, who brought us all together and provided the academic and administrative support required to make everything happen.

I would like to offer thanks to Christos Papavassiliou, who invited me to begin this project, and provided advice along the way.

I would like to offer thanks to Angela Westley, who coordinated the research group.

I would like to offer thanks to Kate Cooley, who picked up where Angela left off.

Lastly, I would like to offer thanks to my family, whose unconditional support made this possible.

# Chapter 1

## Introduction

### 1.1 Motivation

The monitoring of neuron activity is an important element of neurological medicine. By recording and analysing neuron impulses researchers can achieve a greater understanding of the human brain, allowing for better treatments of neurological disorders, and improve neuroprosthetics. The neural interfaces used in this manner can be broadly grouped into two categories: noninvasive interfaces that use electrodes placed externally on the body and invasive interfaces that use surgically implanted probes. The latter of these can provide far more detailed information, but existing systems require extensive pattern matching to sort neural activity from the different neurons in the vicinity of the probe[1]. This is typically done by amplifying the signals recorded by the probe, digitising those signals, and then sending them to an external computer for processing[2]. This processing cannot generally be done in-situ, as the waste heat from the power hungry processors risks damage to surrounding tissue[3]. Such processing often involves the sorting of spikes in the signal to determine the neuron of origin, tying all of the activity of a neuron to a single identity in the post-experiment analysis. As a result of the large bandwidth required to stream data from several hundred probe channels, many current systems fail to take advantage of the high channel count probes that currently exist[4]. If real-time spike sorting could be implemented in implanted hardware[5][6], the effective compression of the data at this stage would ease the reliance on external computation[7]. This would permit far more complex and capable implants, enabling more thorough research and treatment, possibly as far as sophisticated neuroprosthetics[8]. This is not the first attempt to solve this issue and sorting systems have been developed to address this issue[9], but most such attempts still process digital signals. This requires a power hungry analogue to digital converter between the amplifiers and filters and the sorting circuit. It may be possible to substantially reduce the power requirements of the spike sorting task by conducting the sorting and digitisation in the same step. This would

require the development of low power tunable analogue circuits. Adding digital to analogue converters for every tunable parameter would be wholly impractical, so any such circuit would inevitably require the inclusion of components which store information in their electrical properties, rather than in conventional digital memory. An example of such a device would be memristors, whose resistive state is a function of the current that has passed through the device. Memristors have been demonstrated in spike sorted applications, using the integrating behaviour of the such devices to compress unique spike shapes into corresponding step changes in resistance[10]. A further expansion on this concept produced an amplifier for neural signals that used memristors to tune a threshold detector[11]. An alternative approach added memristive devices to simple logic gates to provide low-power mixed-signal circuits[12]. This approach yielded flexible analogue-in, digital-out designs that have the potential to displace ADCs, and warrants further investigation. Using memristors to adjust the threshold of a circuit such as a window comparator would allow for an array of such comparators to be used in a spike sorting method such as a template matching system suitable for neural processing applications. This project develops and demonstrates at a proof-of-concept level a memristor tunable circuit for template matching of neural spikes with a competitive power dissipation below the  $80 \text{ mW cm}^{-2}$ [3] threshold for tissue damage.

## 1.2 Research Objectives

This research project seeks to demonstrate, at a proof-of-concept level, a template matching system suitable for use with neural spike signals. To achieve this, a window comparator with non-volatile tuning elements must be designed. As the operation of large numbers of such circuits is not possible with existing instruments, a new platform for conducting these experiments is also required. This gives rise to the following objectives:

- Develop an instrument to serve as a platform for characterising memristors, memristor crossbar arrays, and testing a wide range of memristor based designs.

- Design an analogue circuit to facilitate template matching tasks in the context of neural signals.

- Simulate the designed analogue circuit, assessing its suitability for further development with a focus on integration.

- Produce a model of the analogue circuit for testing with physical memristor devices.

- Demonstrate the analogue circuit in a template matching task.

### 1.3 Structure

This thesis is structured as follows:

Chapter 2 provides an overview of the subject of this research, covering the topic at hand and related subjects, such as spike detection and memristors.

Chapter 3 describes the development and testing of the instrumentation intended to act as the platform for this project.

Chapter 4 discusses the design of several circuits as candidates for further development.

Chapter 5 presents the selected circuit and experiments conducted with it, including integrated circuit simulations and tests with physical model.

Chapter 6 concludes the thesis and discusses the direction of future research

### 1.4 Contributions

The work described in Chapter 3 was presented at ISCAS 2020[13], and a more thorough paper written for Scientific Reports[14]. These papers present the instrument and analyse its performance in a variety of tasks.. In addition to this, the instrument is in a sufficiently complete state that units have already been sold, and several researchers are already using it in their projects. In some cases, specialised daughterboards were designed for their applications (appendix E).

A paper on the TXL circuit discussed in Chapter 5 as an isolated cell is in progress[15]. This paper will present the Split TXL circuit in isolation, showing simulations of the circuit in integrated circuit development tools, along with test of physical models using memristors. A paper on a split TXL based template matching channel is planned. This paper will present a demonstrator of the Split TXL based template matching channel, showing tests of a physical model on synthetic and recorded signals.

# Chapter 2

## Processing of Neuronal Spike Signals

### 2.1 Neural Signals

FIGURE 2.1: Diagram of a neuron with an implanted electrode and associated instrumentation.

Neural tissue is comprised of neurons, which are specialised cells with a dense array of dendrites branching from the soma and long axon insulated with a myelin sheath (Fig. 2.1). The ends of the dendrites are connected to the axons of other neurons in a structure called a synapse. When triggered by an electrochemical pulse called an action potential, the axon terminal of a neuron releases chemicals called neurotransmitters. These chemicals bind to receptors on the dendrite, which in turn open ion channels. The influx of ions changes the local membrane potential, which triggers voltage sensitive ion channels in the surrounding cell membrane. If enough receptors are stimulated, the

change in membrane potential triggers a critical mass of voltage sensitive ion channels, and the resulting wave of membrane potential and ion transport travels down the axon as an action potential. The movement of ions in and out of the intracellular medium causes a current that can be measured. This is done by inserting small electrodes[16] in to the area of interest and amplifying[17] the resulting output to a usable level. Amplification is necessary because the electrical signals involved in firing of a neuron are very low, typically below  $100 \mu\text{V}_{pk-pk}$ [18]. These spikes typically last around 2 ms[19] and occur at varying frequencies in different parts of the nervous system. The cerebral cortex is an area of high interest, as it is responsible for motor control and perception; it typically has spike rates of 30 – 80 Hz[20], although spike frequencies of up to 450 Hz[21] have been observed in human cortical samples. In addition to the spikes, electrodes can also detect electric fields caused by bulk current flow into or out of neurons as they spike and recover. These local field potentials typically have maximum frequencies at or below the firing rate of nearby neurons[22], and can be detected a significant distance away from the neurons contributing to the measured signal[23]. They are usually filtered out in applications focusing on the action potentials, as they are a much less local phenomenon and could otherwise interfere with detection and measurement of the spikes. The information collected from these spike signals can be used to control robotic prostheses, or map neurons for installation of neuroprosthetics, such as cochlear implants[24]. Before this can be done, the action potentials in neurons of interest must first be distinguished from the measurement noise and the action potentials of surrounding neurons.

## 2.2 Spike Detection and Sorting

The raw neural signals are usually recorded by the implant, and the task of picking the voltage spike of an action potential out from the surrounding noise is left to an external computer[25]. The computer will apply sorting methods to cluster recorded events, which can then be associated with a specific neuron. This approach requires that large quantities of data be streamed from the implant: an array of 100 probes[26] operating at sample rate of 20 kHz with a 12-bit resolution requires at least  $24 \text{ Mbit s}^{-1}$  of bandwidth. This can be reduced by using in situ methods of spike detection, such as voltage thresholds or nonlinear energy operators[27] to limit the transmitted data to only the spike events. However, any given neuron might be firing at up to 200 times per second, so energy savings are not guaranteed. Preferably, an in situ method of classifying neural signals would be used, but most systems still use many microwatts of power per channel[28].

### 2.2.1 Software Sorting

The software approach to spike sorting typically takes one of two forms: template matching or principal component analysis.

Template matching compares the recorded signals with an example spike. This comparison can be done by calculating the distance between the waveform and the template[29], but it can also be done by calculating the cross correlation[30]. Cross correlation or convolution can be very effective at detecting coincident spikes from different neurons.

Principal component analysis[31] considers samples captured from the waveform as a multidimensional array and processes this array with matrix transformations to find new variables in which the spikes of different neurons can be grouped. This is a more recent approach than template matching, as it requires significant computing power for any dataset that isn't trivially small.

Modern implementations of template matching and principal component analysis can achieve very high accuracy[32] with a wide range of waveforms, but their reliance on external computing makes them unsuited for achieving the goals of this project and as such they will not be considered going forwards.

### 2.2.2 Hardware Sorting

Amplitude alone can be used to detect spikes, but in a situation where two neurons are producing differently shaped spikes of similar amplitude the accuracy of this method suffers. A simple way around this is to use a time amplitude discriminator[33]. This is a circuit that returns a match if the input waveform falls within an amplitude window at a set time after the spike has passed an amplitude threshold.

A more sophisticated approach to in-hardware spike sorting is template matching, where a fixed number of samples are collected from the input waveform when an event is detected. The resulting values are then compared to a known pattern and the number of matching values used to determine if the waveform matches the template. This approach has two advantages: the circuit can sleep to reduce power consumption when not sampling and the same set of samples can be used as input to several sets of matching hardware where each is tuned to detect a different pattern. Since checking a sample for a match requires some sort of window comparator and many samples must be compared, the obvious path to improve on this approach is to reduce the power consumption and complexity of the window comparator. Simple window detection circuits, known as analogue content addressable memory, are a subject of current research[12][34], although the technology is not yet mature.

Another approach might be to implement one of the many spike sorting algorithms into a digital application specific integrated circuit (ASIC). As modern digital circuitry can operate at very low supply voltages, the power requirements of the sorting element of such a system can be very low. A system of this type was reported to have a dissipation of 64 nW[9], setting an ambitions standard to beat, although this is quoted for a signal that has already been digitised.

Neuromorphic sorting methods could be a better fit, as the crossbar structures common in two-terminal memory technologies lend themselves well not only to the matrix multiplications that are central to neuromorphic applications, but also to deconvolution tasks[35], and in memory computing[36]. Samples are collected in a similar manner as with the earlier example of template matching, but the samples are used to bias the wordlines of a crossbar array instead. The current in a given bitline can then be used to determine a match for the template set by the devices on that line. Cutting edge designs already show considerable improvement, cutting down both the power consumption and substrate area of the sorting system[37]. In 2020, a research group demonstrated a neural signal processing system based on a neural network implemented as a memristor crossbar array[38], for the purpose of detecting epilepsy-related neural signals. They report that their work used 1/400<sup>th</sup> the power of a contemporary CMOS ASIC system, without sacrifice in accuracy.

## 2.3 Memory

In all of the hardware sorting methods discussed the measured signal is being compared against information stored in the circuit, whether that be in a conventional databank, the configuration components of a template, or the weighting of a neural network. Thus the limits of spike sorting tools are defined by the memory technologies available. Higher density of suitable memory would allow for an expansion of spike sorting systems, highlighting the importance of selecting the right technology (Tab. 2.1).

|             | FLASH                 | PCM                   | MRAM                  | FeRAM                 | ReRAM                 | Molecular             |

|-------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| Data type   | Multi level[39]       | Multi level[40]       | Binary[41]            | Binary[42]            | Analogue[43]          | Multi level[44]       |

| Area        | 50 × 50 nm[45]        | 35 × 35 nm[46]        | 0.26 × 0.54 μm[47]    | 80 × 34 nm[42]        | 30 × 30 nm[48]        | 0.01 × 2 μm[44]       |

| Write Speed | 0.4 – 1.5 ms[39]      | 100 ns[49]            | 1 ns[47]              | 1 μs[50]              | 5 ns[51]              | 1 ms[52]              |

| Retention   | 10 <sup>4</sup> h[53] | 10 <sup>5</sup> h[49] | 10 <sup>5</sup> h[54] | 10 <sup>5</sup> h[55] | 10 <sup>5</sup> h[56] | 600 h[44]             |

| Endurance   | 10 <sup>6</sup> [57]  | 10 <sup>11</sup> [49] | 10 <sup>11</sup> [47] | 10 <sup>8</sup> [50]  | 10 <sup>8</sup> [51]  | 10 <sup>12</sup> [58] |

TABLE 2.1: A table comparing non volatile memory technologies.

The most common non volatile memory in use is flash, which operates by trapping charge on an electrically isolated gate between the gate and channel of an otherwise relatively conventional planar MOSFET. Developed from EEPROM in the 1980s[59], flash is by far the most mature memory technology covered in this chapter, with high densities of stacked triple level cells (cells capable of enough discreet levels for 3 bits

of information) being common in consumer products. While well established, flash has significant limitations. The mechanism for placing charge onto the floating gate requires high voltage supply, typically 12 V. Not only does this result in high write energies, subjecting the cell to such high voltages also causes the cell to fail with enough write-erase cycles. Flash ICs are typically rated for no more than 100,000 cycles, although the actual endurance is often higher[57].

Phase change memory (PCM) is a newer technology, comprised of a layer of chalcogenide glass between metal contacts. Passing current through the cell heats the glass, with different heating profiles allowing for the cell to set in amorphous or crystalline state, changing the resistance[60]. Most memory of this type only stores a binary state, but two level cells have been demonstrated[40]. Phase change memory offers vastly superior endurance to flash, with many millions of cycles being possible. As there are no trapped charges to escape, it also displays better retention, at least when ambient temperatures are at a reasonable level[49]. The downsides of this technology are that high current densities are required to achieve the necessary heating, and that the chalcogenide glass is not commonly found in integrated circuit fabrication processes, complicating its implementation.

Magnetoresistive memory (MRAM) uses a pair of ferromagnetic layers with a thin insulating layer between. When the magnetic fields in the ferromagnetic layers are aligned, the probability of an electron tunnelling across the insulator layer increases, effectively reducing the resistance of the cell[61]. Writing to MRAM is typically done using a grid of wires, running across the entire array along the horizontal and vertical cell rows[62]. Selecting the wires passing across a cell, and passing a current through them, forms a small magnetic field in the cell, altering the state of the ferromagnetic layers. While relatively simple, this method also subjects horizontally or vertically aligned cells to a smaller magnetic field, limiting the strength of the writing field. This is relevant because the retention of the cell is a function of the writing field strength. An alternative method of writing to MRAM is passing spin-aligned electrons through the cell. When electrons pass into a layer that forces them to change their spin, they transfer some of their angular momentum to the layer, altering its field[41]. This approach avoids the issues of the more conventional approach, allowing smaller cells, but must still make compromises between power, speed, and retention. MRAM endurance is limited by the breakdown of the thin tunnelling layer, but under typical operating conditions endurance can exceed many millions of cycles[63]. Both high temperatures and strong magnetic fields can compromise the retention of MRAM, but outside of such situations the retention is excellent. While the binary nature of MRAM makes it unsuited to the applications under consideration in this thesis, its characteristics make it a popular choice for non-volatile RAM research.

Ferroelectric (FeRAM) memory uses a layer of ferroelectric material between two plates to store information. The cell is written by applying a voltage across it, causing dipoles

within the ferroelectric material to align with the applied field[64]. To read the cell, a voltage is applied across it, much the same as when writing. If the read pulse is of the same orientation as the write pulse nothing will happen, but if it's the opposite direction, applying a voltage causes a small pulse of current as the dipoles change orientation. Unlike all the other technologies discussed in this review, this destroys the data stored in the cell. Because FeRAM uses ferroelectric material rather than ferromagnetic, resistance to magnetic fields is superior to MRAM. The endurance is substantially worse though, as the previous writes to a cell can cause it to develop a preferential polarisation. An alternative to FeRAM is FeFETs[42], which use the ferroelectric material in place of the gate insulator of a MOSFET. FeFETs operate in a very similar manner to flash cells, although they store their state as a dipole moment rather than static charge.

Molecular memory operates in a similar manner to FeFETs, but uses a chemical reaction instead of a ferroelectric layer to store the charge that controls the channel of the FET. This is the least explored of the memory technologies in this review but despite this, triple level cells have already been demonstrated[44] using  $\text{In}_2\text{O}_3$  nanowires coated with  $\text{Fe}^{2+}$  -terpyradine.

FIGURE 2.2: Diagram of a  $\text{TiO}_{2-x}$  memristor.

Memristors[65] (RRAM or ReRAM) are two terminal electrical devices with a non-linear current/voltage relationship that is dependant on the charge that has passed through the device. The memristor was first identified in theory in 1971[66] as a fourth fundamental circuit element, described by the equation  $M = \frac{d\phi}{dq}$ . A physical approximation of such a device was not identified as such until 2008[67], although the exact classification of this device is disputed[68]. This ReRAM device was constructed from a bi-layer of  $\text{TiO}_2$  and  $\text{TiO}_{2-x}$  (Fig. 2.2), and then exposed to high voltage to form conductive defects[69] such as metal filaments in a process called electroforming. The oxygen vacancies in the  $\text{TiO}_{2-x}$  layer act as p-type dopants, and drift in the applied electric field. This changes the thickness of the conductive and insulating layers, with the conductive layer acting on the filament in a similar manner to the wiper on a rheostat. Memristors based on other materials have been demonstrated[70], some of which remove the requirement to electroform the pristine devices[71]. The low power and high speed of switching, the high level of CMOS compatibility, and granularity of control, make them an attractive choice for low power memory and signal processing tasks. This type of memory is already finding applications in fields relevant to this project, such as a neural signal amplifier using memristors as integrating elements[11].

### 2.3.1 Crossbar Arrays

FIGURE 2.3: Diagram of a small memristor crossbar array.

Crossbar arrays are a topology used for high density array designs. Memory arrays with similar structures date back as far as 1947[72], but the fundamental concept behind the crossbar remains relevant today. In a crossbar array the devices are arranged in a grid, with the top electrode of each device connected to a horizontal line and the bottom electrode connected to a vertical line (Fig. 2.3). This allows for an array of  $x^2$  devices to be controlled by a system with  $x$  terminals, making the size of the device the limiting factor and permitting very high density arrays. As memristors are two terminal devices, with a fairly simple layered structure this topology is an obvious choice for memristor arrays, where the devices can be formed between two metallic layers using common processes. In addition to the obvious applications of non-volatile memory, this topology can also be used to implement vector-matrix multiplication. The voltage on horizontal lines act as the vector input, and the resistive state of the devices act as the matrix values, with the current on the vertical lines as the output. As vector matrix multiplication is a fundamental part of neural network operation, this makes crossbar arrays ideally suited for implementing neuromorphic systems[73]. While versatile, this topology has significant limitations, as the non-zero resistance of the access lines results in parasitic currents passing through unselected devices[74]. It is possible to mitigate these sneak currents by adding diodes or transistors that block these paths, but doing so comes at the cost of area, complexity, and voltage constraints.

## 2.4 Instrumentation

Measurement of memristor characteristics is usually done using an instrument called a source measurement unit (SMU). An SMU is an instrument that can set a precise voltage/current and measure a precise current/voltage at the same time. While the

state of a memristor should change as current passes through it, in practice a memristor will retain its state until the voltage or current passes a threshold[75]. This allows for the state of the device to be measured at low voltages/currents. This is not a novel requirement, and many other groups have designed systems to this end. Wust, D. et al. developed a field programmable gate array (FPGA) based memristor prototyping environment[76], but with a maximum theoretical resolution of 740pA, this system cannot deliver more detailed characterisation tasks. Berdan, R. et al. implemented a microcontroller-based advance testing system for memristor devices[77], but the parallelism is limited. Wang, Y. et al. presented a high-speed driving system for phase change memory devices[78], with pulse width as narrow as 500ns. However, this work only has a driver side. Other works such as Merced-Grafals, E. et al. applied commercially available device analysers[79], which have limited channel numbers as well as parallelism. Such a gap in capability calls for the development of a new instrument with the parallel SMU capacity to operate large numbers of memristors and multiple analogue circuits simultaneously.

## 2.5 Summary

The demands of modern neurological medicine are not yet met by the information processing systems currently available. This project seeks to develop a hardware template matching system suitable for use with neurological spike signals, using ReRAM devices. To this end, this project will also seek to develop an instrumentation platform to support this project and others.

# Chapter 3

## Mixed signal parallel instrumentation

### 3.1 Introduction

This chapter covers the development and performance of the instrument used in this project (Fig. 3.1). Section 3.2 discusses the problem of instrumentation. Section 3.3 covers the design history of the subject of this chapter. Section 3.4 outlines the requirements of the system. Section 3.5 then describes in detail the design of the circuitry, followed by experimental demonstration of its performance in sections 3.6.1, 3.6.2, 3.6.3, 3.6.4, and 3.6.5. Section 3.7 reviews the performance against the specification and the predecessor system.

### 3.2 Instrumentation