### University of Southampton

Faculty of Engineering and Physical Science School of Electronics and Computer Science Cyber Physical Systems Research Group

Doctor of Philosophy

Supervisor: Prof Geoff Merrett and Prof Jonathon Hare

Realising the Benefits of Dynamic DNNs on Reconfigurable Hardware

by Anastasios Dimitriou

April 29, 2025

### **Declaration of Authorship**

I declare that this thesis and the work presented in it is my own and has been generated by me as the result of my own original research.

#### I confirm that:

- 1. This work was done wholly or mainly while in candidature for a research degree at this University;

- 2. Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- 3. Where I have consulted the published work of others, this is always clearly attributed;

- 4. Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- 5. I have acknowledged all main sources of help;

- 6. Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- 7. Parts of this work have been published are listed under the Research Contribution.

| Signed: | Date: |  |

|---------|-------|--|

### Acknowledgements

I would like to express my deepest gratitude to all those who have contributed to the completion of this thesis. First and foremost, I would like to thank my supervisors, Prof. Geoff Merrett and Prof. Jonathon Hare, for their invaluable guidance, constant support, and encouragement throughout my PhD journey. Your expertise and insightful feedback have been invaluable.

I extend my gratitude to my sponsor, the Engineering and Physical Sciences Research Council (EPCRC), for the financial assistance which made this research possible.

To my numerous colleagues and friends, thank you for your friendship, motivation, and collaborative spirit. Your willingness to share knowledge and experiences has enhanced my learning and made my entire PhD experience enjoyable. I am particularly thankful to Joe Dib and Evangelos Panagiotou for their continuous support during challenging times.

Finally, I wish to express my heartfelt appreciation to my parents, Christo and Doxa, and my sister, Ioanna, for their love, understanding, and encouragement. Your enduring sacrifices and unshakable confidence in me have been my greatest motivations and the root of my success.

This journey would not have been possible without each and every one of you.

### University of Southampton

#### Abstract

Faculty of Engineering and Physical Science School of Electronics and Computer Science

### Doctor of Philosophy

#### Realising the Benefits of Dynamic DNNs on Reconfigurable Hardware

by Anastasios Dimitriou

Deep Neural Networks (DNNs) are increasingly capable of solving many cognitive problems, with countless everyday life applications such as autonomous driving, voice assistants, medical diagnoses, etc. Their increased computational, memory, and energy demands led to the widespread adoption of powerful GPU cloud servers for their execution. However, there is an increasing interest in moving the computation of DNNs to the edge. By processing data locally, the dependency on cloud infrastructure is reduced, thereby decreasing the data transmission load, improving privacy and security, and increasing the availability of networks in environments with limited internet connectivity. However, edge devices (IoT devices, mobile phones, etc.) are typically resource restricted in processing power, memory, and power consumption. This research aims to contribute towards enabling the deployment of complex DNNs on resource-restricted devices.

Field Programmable Gate Arrays (FPGAs) have been proven to be very effective in accelerating neural networks due to their configurability, parallelization capabilities, and low energy consumption. Nonetheless, attempting to map modern DNNs onto them without compression is not feasible. Dynamic DNNs are approaches that go beyond the limits of static model compression by tuning computational workload to the difficulty of inputs on a per-sample basis. This thesis first explores the challenges introduced by this DNN approaches when their FPGA implementation is targeted. Three limiting factors were identified: the lack of software libraries and frameworks, the lack of hardware modules and frameworks, and the dependencies on intermediate feature maps.

Having identified these challenges, the next contribution of this thesis is a first realisation of dynamic networks on FPGAs. The design followed the standard architecture and achieved a minimum of 3.2x faster execution over a Jetson embedded device and comparable latency to a CPU/GPU system while maintaining very low energy consumption (at least 1.8x less than the Jetson). This highlighted the feasibility and

efficiency of deploying the dynamic network on FPGAs. Nonetheless, FPGAs are inherently parallel devices, and leveraging that, the third contribution of the thesis is a second design approach that explores the simultaneous execution of the two main components of dynamic networks. It addressed two main challenges concerning the dependencies on intermediate feature maps and further accelerated the execution of the dynamic network by up to 23%.

Finally, targeting the versatility and reconfigurability of FPGAs, the last contribution of the thesis is the exploration of two confidence-controlled dynamic schemes. Utilising control values generated by dynamic networks, the first dynamically selects the location of the exit points within the network, and the second the applied quantisation level. Both approaches enhance the adaptability and performance of the early-exit dynamic DNN, achieving an 18% reduction in computations and up to a 21.9% reduction in latency, respectively, with minimal accuracy drops.

# **Contents**

| D  | eclara  | ation of Authorship                            | iii |

|----|---------|------------------------------------------------|-----|

| A  | cknov   | vledgements                                    | v   |

| Li | st of l | Figures x                                      | iii |

| Li | st of [ | Tables                                         | vii |

| A۱ | bbrev   | riations                                       | αix |

| 1  | Intro   | oduction                                       | 1   |

|    | 1.1     | Research Justification                         | 3   |

|    | 1.2     | Research Questions                             | 5   |

|    | 1.3     | Research Contributions                         | 5   |

|    | 1.4     | Thesis Structure                               | 7   |

| 2  | Bacl    | kground Theory                                 | 9   |

|    | 2.1     | Deep Neural Networks                           | 9   |

|    |         | 2.1.1 Convolutional Neural Networks            | 10  |

|    | 2.2     | Hardware Platforms for Inference               | 11  |

|    |         | 2.2.1 CPU and GPU                              | 12  |

|    |         | 2.2.2 Neural Processing Units                  | 13  |

|    |         | 2.2.3 Application-Specific Integrated Circuits | 14  |

|    |         | 2.2.3.1 Tensor Processing Units                | 15  |

|    |         | 2.2.4 Field Programmable Gate Arrays           | 16  |

|    |         | 2.2.4.1 Systolic Arrays of Process Elements    | 16  |

|    |         | 2.2.4.2 Dynamic Partial Reconfiguration        | 19  |

|    |         | 2.2.4.3 Toolflows for mapping DNNs on FPGAs    | 20  |

|    | 2.3     | Network Compression                            | 23  |

|    |         | 2.3.1 Quantisation                             | 23  |

|    |         | 2.3.2 Pruning                                  | 24  |

|    |         |                                                | 25  |

|    | 2.4     |                                                | 25  |

|    |         |                                                | 26  |

|    |         |                                                | 32  |

|    |         | •                                              | 34  |

|    |         | 8                                              | 34  |

|    |         |                                                | 36  |

X CONTENTS

|   | 2.5                                    | Dynan                                                                             | nic Hardware Architectures for DNNs                                                                                                                                                                                                                                                                                                                                                                                        | 37                                                                               |

|---|----------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|   |                                        | 2.5.1                                                                             | Diversity in Layers                                                                                                                                                                                                                                                                                                                                                                                                        | 38                                                                               |

|   |                                        | 2.5.2                                                                             | Hardware Design and Deployment                                                                                                                                                                                                                                                                                                                                                                                             | 39                                                                               |

|   | 2.6                                    | Resear                                                                            | ch Scoping and Discussion                                                                                                                                                                                                                                                                                                                                                                                                  | 41                                                                               |

|   |                                        |                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                  |

| 3 | Rea                                    | lising D                                                                          | ynamic DNNs on FPGAs                                                                                                                                                                                                                                                                                                                                                                                                       | 43                                                                               |

|   | 3.1                                    | Challe                                                                            | nges                                                                                                                                                                                                                                                                                                                                                                                                                       | 44                                                                               |

|   |                                        | 3.1.1                                                                             | Software Frameworks & Training                                                                                                                                                                                                                                                                                                                                                                                             | 45                                                                               |

|   |                                        | 3.1.2                                                                             | Hardware Design & Frameworks                                                                                                                                                                                                                                                                                                                                                                                               | 46                                                                               |

|   |                                        | 3.1.3                                                                             | Intermediate Feature Map Dependence                                                                                                                                                                                                                                                                                                                                                                                        | 47                                                                               |

|   | 3.2                                    | Advan                                                                             | cements                                                                                                                                                                                                                                                                                                                                                                                                                    | 48                                                                               |

|   | 3.3                                    | Early-I                                                                           | Exit Network FPGA Design                                                                                                                                                                                                                                                                                                                                                                                                   | 49                                                                               |

|   |                                        | 3.3.1                                                                             | Early-Exiting Approach                                                                                                                                                                                                                                                                                                                                                                                                     | 49                                                                               |

|   |                                        | 3.3.2                                                                             | Architecture                                                                                                                                                                                                                                                                                                                                                                                                               | 50                                                                               |

|   |                                        | 3.3.3                                                                             | Hardware Implementation                                                                                                                                                                                                                                                                                                                                                                                                    | 51                                                                               |

|   |                                        | 3.3.4                                                                             | Layer realisation                                                                                                                                                                                                                                                                                                                                                                                                          | 53                                                                               |

|   |                                        |                                                                                   | 3.3.4.1 Convolution Layer                                                                                                                                                                                                                                                                                                                                                                                                  | 53                                                                               |

|   |                                        |                                                                                   | 3.3.4.2 FC Layer                                                                                                                                                                                                                                                                                                                                                                                                           | 54                                                                               |

|   |                                        |                                                                                   | 3.3.4.3 Pooling Layer                                                                                                                                                                                                                                                                                                                                                                                                      | 54                                                                               |

|   |                                        | 3.3.5                                                                             | Design Overview                                                                                                                                                                                                                                                                                                                                                                                                            | 54                                                                               |

|   |                                        | 3.3.6                                                                             | Experimental Setup                                                                                                                                                                                                                                                                                                                                                                                                         | 55                                                                               |

|   |                                        | 3.3.7                                                                             | Design Validation and Evaluation                                                                                                                                                                                                                                                                                                                                                                                           | 56                                                                               |

|   | 3.4                                    | Discus                                                                            | sion                                                                                                                                                                                                                                                                                                                                                                                                                       | 59                                                                               |

|   |                                        |                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                  |

|   | _                                      |                                                                                   | 4 11 11 11 11 11 11 11 11 11 11 11 11 11                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                  |

| 4 |                                        |                                                                                   | the parallelisation capabilities of FPGAs to accelerate Early-Exit                                                                                                                                                                                                                                                                                                                                                         |                                                                                  |

| 4 | Dyr                                    | namic D                                                                           | NNs                                                                                                                                                                                                                                                                                                                                                                                                                        | 61                                                                               |

| 4 |                                        | n <b>amic D</b><br>Design                                                         | NNs<br>Approach                                                                                                                                                                                                                                                                                                                                                                                                            | <b>61</b>                                                                        |

| 4 | <b>Dyr</b> 4.1                         | namic D<br>Design<br>4.1.1                                                        | NNs Approach Designs Modelling                                                                                                                                                                                                                                                                                                                                                                                             | 61<br>62<br>63                                                                   |

| 4 | Dyr                                    | Design<br>4.1.1<br>Experi                                                         | NNs Approach Designs Modelling ment Setup                                                                                                                                                                                                                                                                                                                                                                                  | 61<br>62<br>63<br>65                                                             |

| 4 | <b>Dyr</b> 4.1                         | Design<br>4.1.1<br>Experi                                                         | NNs         Approach          Designs Modelling          ment Setup          Hardware Implementation                                                                                                                                                                                                                                                                                                                       | 61<br>62<br>63<br>65<br>65                                                       |

| 4 | <b>Dyr</b> 4.1                         | Design<br>4.1.1<br>Experi                                                         | NNs Approach Designs Modelling ment Setup Hardware Implementation 4.2.1.1 DNN Networks                                                                                                                                                                                                                                                                                                                                     | 61<br>62<br>63<br>65<br>65<br>66                                                 |

| 4 | Dyr<br>4.1<br>4.2                      | Design<br>4.1.1<br>Experi<br>4.2.1                                                | NNs Approach Designs Modelling ment Setup Hardware Implementation 4.2.1.1 DNN Networks 4.2.1.2 Datasets                                                                                                                                                                                                                                                                                                                    | 61<br>62<br>63<br>65<br>65<br>66<br>66                                           |

| 4 | <b>Dyr</b> 4.1                         | Design<br>4.1.1<br>Experi<br>4.2.1                                                | NNs Approach Designs Modelling ment Setup Hardware Implementation 4.2.1.1 DNN Networks 4.2.1.2 Datasets mental Results and Analysis                                                                                                                                                                                                                                                                                        | 61<br>62<br>63<br>65<br>65<br>66<br>66                                           |

| 4 | Dyr<br>4.1<br>4.2                      | Design<br>4.1.1<br>Experi<br>4.2.1<br>Experi<br>4.3.1                             | Approach Designs Modelling ment Setup Hardware Implementation 4.2.1.1 DNN Networks 4.2.1.2 Datasets mental Results and Analysis Design Validation and Evaluation                                                                                                                                                                                                                                                           | 61<br>62<br>63<br>65<br>65<br>66<br>66<br>66                                     |

| 4 | Dyr<br>4.1<br>4.2                      | Design<br>4.1.1<br>Experi<br>4.2.1<br>Experi<br>4.3.1<br>4.3.2                    | NNs Approach Designs Modelling ment Setup Hardware Implementation 4.2.1.1 DNN Networks 4.2.1.2 Datasets mental Results and Analysis Design Validation and Evaluation Evaluating pipeline vs parallel Approaches                                                                                                                                                                                                            | 61<br>62<br>63<br>65<br>65<br>66<br>66<br>66<br>71                               |

| 4 | Dyr<br>4.1<br>4.2                      | Design<br>4.1.1<br>Experi<br>4.2.1<br>Experi<br>4.3.1<br>4.3.2<br>4.3.3           | NNs Approach Designs Modelling ment Setup Hardware Implementation 4.2.1.1 DNN Networks 4.2.1.2 Datasets mental Results and Analysis Design Validation and Evaluation Evaluating pipeline vs parallel Approaches Effect of Decision Threshold on Performance                                                                                                                                                                | 61<br>62<br>63<br>65<br>66<br>66<br>66<br>66<br>71<br>74                         |

| 4 | Dyr<br>4.1<br>4.2                      | Design<br>4.1.1<br>Experi<br>4.2.1<br>Experi<br>4.3.1<br>4.3.2<br>4.3.3           | NNs Approach Designs Modelling ment Setup Hardware Implementation 4.2.1.1 DNN Networks 4.2.1.2 Datasets mental Results and Analysis Design Validation and Evaluation Evaluating pipeline vs parallel Approaches                                                                                                                                                                                                            | 61<br>62<br>63<br>65<br>65<br>66<br>66<br>66<br>71                               |

|   | Dyr<br>4.1<br>4.2<br>4.3               | Design<br>4.1.1<br>Experi<br>4.2.1<br>Experi<br>4.3.1<br>4.3.2<br>4.3.3<br>Discus | Approach Designs Modelling ment Setup Hardware Implementation 4.2.1.1 DNN Networks 4.2.1.2 Datasets mental Results and Analysis Design Validation and Evaluation Evaluating pipeline vs parallel Approaches Effect of Decision Threshold on Performance sion                                                                                                                                                               | 61<br>62<br>63<br>65<br>65<br>66<br>66<br>66<br>71<br>74<br>76                   |

| 5 | 4.1<br>4.2<br>4.3<br>4.4<br>Con        | Design<br>4.1.1<br>Experi<br>4.2.1<br>Experi<br>4.3.1<br>4.3.2<br>4.3.3<br>Discus | NNs Approach Designs Modelling ment Setup Hardware Implementation 4.2.1.1 DNN Networks 4.2.1.2 Datasets mental Results and Analysis Design Validation and Evaluation Evaluating pipeline vs parallel Approaches Effect of Decision Threshold on Performance sion  Based Dynamic Control of Early-Exit Networks                                                                                                             | 61<br>62<br>63<br>65<br>66<br>66<br>66<br>66<br>71<br>74<br>76                   |

|   | Dyr<br>4.1<br>4.2<br>4.3               | Experi: 4.3.1 4.3.2 4.3.3 Discus                                                  | NNs Approach Designs Modelling ment Setup Hardware Implementation 4.2.1.1 DNN Networks 4.2.1.2 Datasets mental Results and Analysis Design Validation and Evaluation Evaluating pipeline vs parallel Approaches Effect of Decision Threshold on Performance sion  Based Dynamic Control of Early-Exit Networks nic Early-Exit Placement                                                                                    | 61<br>62<br>63<br>65<br>66<br>66<br>66<br>71<br>74<br>76                         |

|   | 4.1<br>4.2<br>4.3<br>4.4<br>Con        | Experi- 4.3.1 4.3.2 4.3.3 Discus fidece B Dynam 5.1.1                             | Approach Designs Modelling ment Setup Hardware Implementation 4.2.1.1 DNN Networks 4.2.1.2 Datasets mental Results and Analysis Design Validation and Evaluation Evaluating pipeline vs parallel Approaches Effect of Decision Threshold on Performance sion  Based Dynamic Control of Early-Exit Networks nic Early-Exit Placement Methodology                                                                            | 61<br>62<br>63<br>65<br>65<br>66<br>66<br>66<br>71<br>74<br>76<br>77             |

|   | 4.1<br>4.2<br>4.3<br>4.4<br>Con        | Experiments A.3.1 4.3.2 4.3.3 Discuss Afidece B Dynam 5.1.1 5.1.2                 | NNs Approach Designs Modelling ment Setup Hardware Implementation 4.2.1.1 DNN Networks 4.2.1.2 Datasets mental Results and Analysis Design Validation and Evaluation Evaluating pipeline vs parallel Approaches Effect of Decision Threshold on Performance sion  Based Dynamic Control of Early-Exit Networks nic Early-Exit Placement Methodology Experimental Setup                                                     | 61<br>62<br>63<br>65<br>66<br>66<br>66<br>71<br>74<br>76<br>77<br>78<br>80       |

|   | 4.1<br>4.2<br>4.3<br>4.4<br>Con<br>5.1 | Experi: 4.3.1 4.3.2 4.3.3 Discus fidece E Dynam 5.1.1 5.1.2 5.1.3                 | NNs Approach Designs Modelling ment Setup Hardware Implementation 4.2.1.1 DNN Networks 4.2.1.2 Datasets mental Results and Analysis Design Validation and Evaluation Evaluating pipeline vs parallel Approaches Effect of Decision Threshold on Performance sion  Based Dynamic Control of Early-Exit Networks nic Early-Exit Placement Methodology Experimental Setup Results and Analysis                                | 61<br>62<br>63<br>65<br>66<br>66<br>66<br>66<br>71<br>74<br>76<br>77<br>80<br>82 |

|   | 4.1<br>4.2<br>4.3<br>4.4<br>Con        | Experi: 4.3.1 4.3.2 4.3.3 Discus fidece E Dynam 5.1.1 5.1.2 5.1.3                 | NNs Approach Designs Modelling ment Setup Hardware Implementation 4.2.1.1 DNN Networks 4.2.1.2 Datasets mental Results and Analysis Design Validation and Evaluation Evaluating pipeline vs parallel Approaches Effect of Decision Threshold on Performance sion  Based Dynamic Control of Early-Exit Networks nic Early-Exit Placement Methodology Experimental Setup Results and Analysis Exit Dynamic DNNs Quantisation | 61<br>62<br>63<br>65<br>66<br>66<br>66<br>71<br>74<br>76<br>77<br>80<br>82<br>83 |

|   | 4.1<br>4.2<br>4.3<br>4.4<br>Con<br>5.1 | Experiments A.3.1 4.3.2 4.3.3 Discuss Afidece B Dynam 5.1.1 5.1.2 5.1.3 Early-B   | NNs Approach Designs Modelling ment Setup Hardware Implementation 4.2.1.1 DNN Networks 4.2.1.2 Datasets mental Results and Analysis Design Validation and Evaluation Evaluating pipeline vs parallel Approaches Effect of Decision Threshold on Performance sion  Based Dynamic Control of Early-Exit Networks nic Early-Exit Placement Methodology Experimental Setup Results and Analysis                                | 61<br>62<br>63<br>65<br>66<br>66<br>66<br>66<br>71<br>74<br>76<br>77<br>80<br>82 |

*CONTENTS* xi

|    |       |         | 5.2.2.1 Experimental Results and Analysis                      | 86  |

|----|-------|---------|----------------------------------------------------------------|-----|

|    |       | 5.2.3   | Full-Network Quantisation                                      | 89  |

|    |       |         | 5.2.3.1 Experimental Results and Anaslysis                     | 90  |

|    | 5.3   | Confic  | lence Controlled Dynamic Quantisation of Early-Exit Networks . | 92  |

|    |       | 5.3.1   | Methodology                                                    | 93  |

|    |       | 5.3.2   | Experimental Results and Analysis                              | 96  |

|    | 5.4   | Discus  | ssion                                                          | 97  |

| 6  | Con   | clusion | s & Future Work                                                | 99  |

|    | 6.1   | Conclu  | asions                                                         | 99  |

|    | 6.2   | Future  | Work                                                           | 101 |

|    |       | 6.2.1   | Quantisation-Aware Training                                    | 102 |

|    |       | 6.2.2   | Introduce Dynamic Partial Reconfiguration to Dynamic DNN ac-   |     |

|    |       |         | celerators                                                     | 102 |

|    |       | 6.2.3   | Employ NAS techniques to better explore the FPGA design space  | 102 |

| Αı | openo | dix A   | Additional Figures                                             | 105 |

# **List of Figures**

| 1.1  | Number of deep neural network parameters. The x-axis is plotted on a log scale. Reprinted from B. Steiner et.al. [13]                       | 2  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Dynamic channel and spatial column pruning. Reprinted from J. Shen et.al. [33]                                                              | 4  |

| 2.1  | Deep Neural Network (DNN) example. Reprinted from M. Merenda et.al. [39]                                                                    | 10 |

| 2.2  | Architecture of AlexNet CNN model. Reprinted from A. Krizhevsky et.al. [1]                                                                  | 11 |

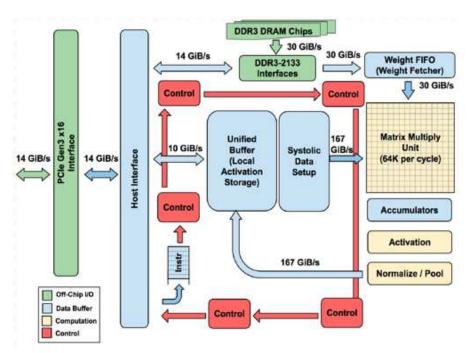

| 2.3  | Google's TPU block diagram. Reprinted from N. P. Jouppi et.al. [57]                                                                         | 15 |

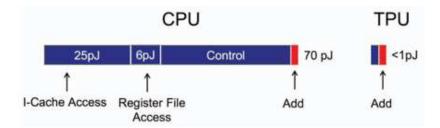

| 2.4  | Instruction fetch and execute energy consumption between a traditional CPU and a TPU. Reprinted from N. Jouppi et.al.[59]                   | 16 |

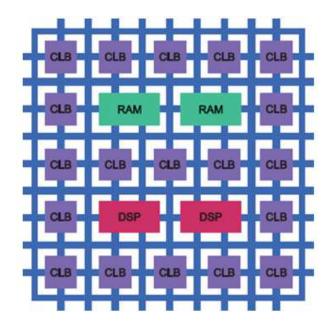

| 2.5  | Typical structure of a FPGA                                                                                                                 | 17 |

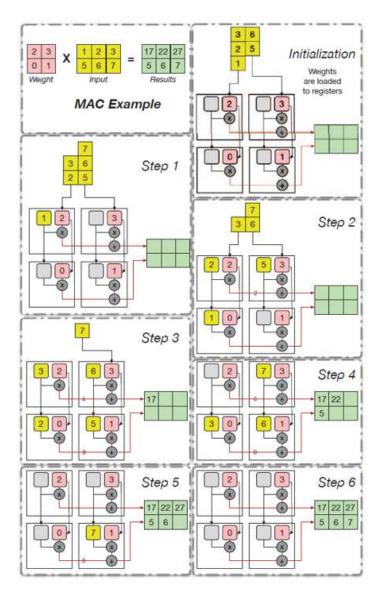

| 2.6  | Matrix-Multiplication on a Systolic Array. Reprinted from J. Zhang et.al. [62]                                                              | 18 |

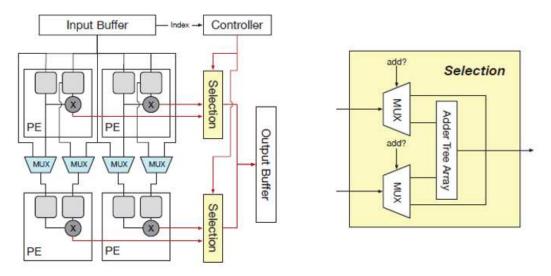

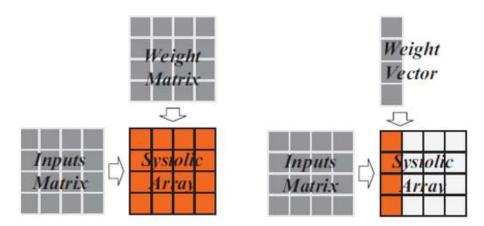

| 2.7  | Example of a modified systolic array's structure. Reprinted from J. Zhang et.al. [62]                                                       | 19 |

| 2.8  | Normal vs Depth-wise convolution when mapped on a SA. Reprinted from R. Xu et.al. [35]                                                      | 19 |

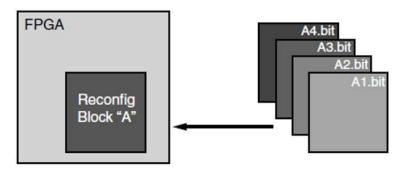

| 2.9  | Basic presumption of Dynamic Partial Reconfiguration. Reprinted from "Vivado Design Suite User Guide: Partial Reconfiguration (UG909)" [63] | 20 |

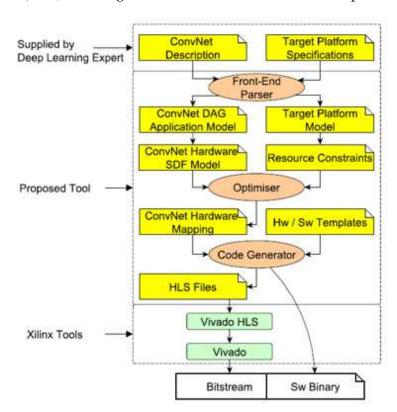

| 2.10 | fpgaConvNet processing flow. Reprinted from S. I. Venieris et.al. [67].                                                                     | 21 |

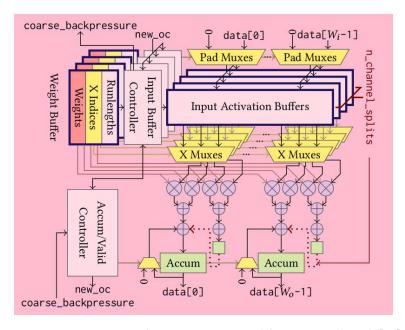

| 2.11 | HPIPE architecture. Reprinted from M. Hall et.al. [70]                                                                                      | 22 |

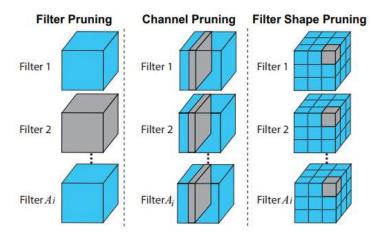

| 2.12 | Different structured pruning schemes. Reprinted from N. Liu et.al. [75].                                                                    | 24 |

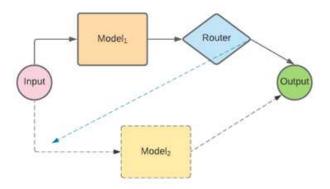

| 2.13 | Cascading of models                                                                                                                         | 26 |

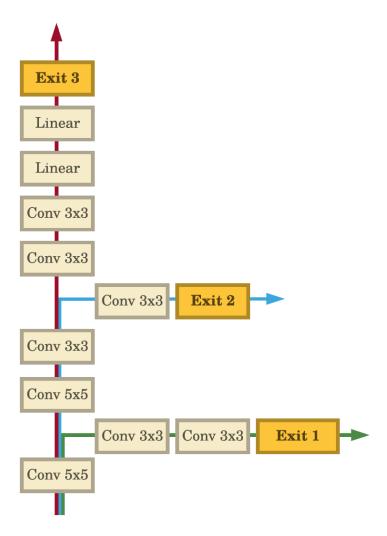

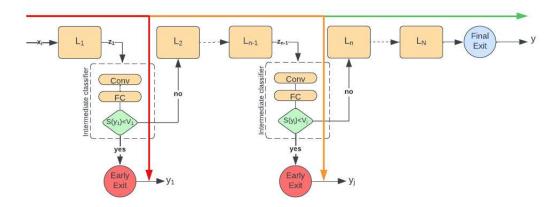

| 2.14 | Network with Intermediate Classifiers. Reprinted from S. Teerapittayanon et.al. [81]                                                        | 27 |

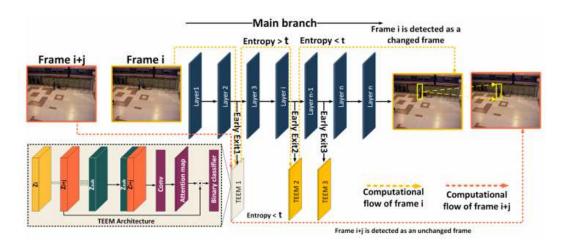

| 2.15 | Dynamic model that performs early exit based on the similarity of con-                                                                      |    |

|      | sequent video frames. Reprinted from A. Sabet et.al. [82]                                                                                   | 28 |

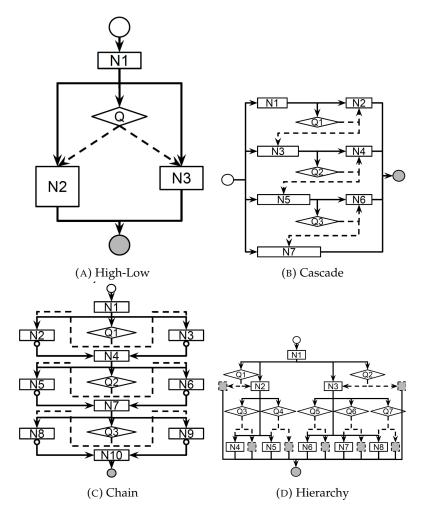

| 2.16 | Four different dynamic routing networks. Reprinted from L. Liu et.al. [85].                                                                 | 30 |

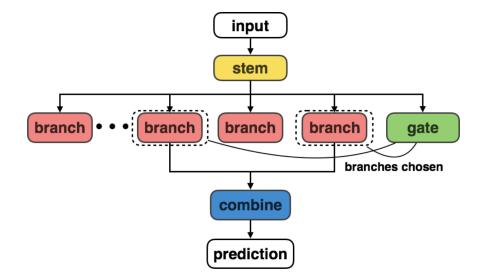

| 2.17 | HydraNet's architecture: consists of multiple branches specialized for                                                                      |    |

|      | different inputs, a gate that selects which of them will be executed and a                                                                  |    |

|      | combiner that aggregates their outputs to make a final prediction. Reprinted                                                                | Ĺ  |

|      | from R. T. Mullapudi et.al. [88]                                                                                                            | 31 |

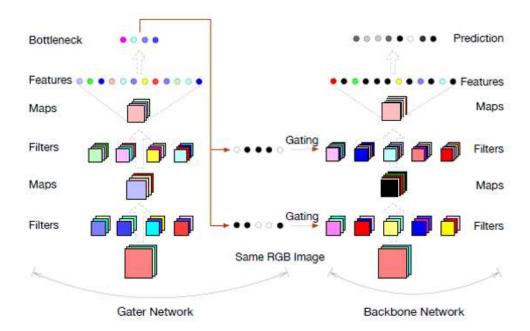

| 2.18 | GaterNet's model architecture. Reprinted from Z. Chen et.al. [28]                                                                           | 32 |

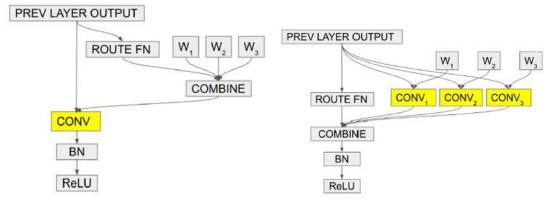

| 2.19 | (A) CondConv architecture with three n=3 Kernels vs. (B) Mixture of Ex-                                                                     |    |

|      | perts approach. There are two mathematically equivalent networks, but                                                                       |    |

|      | CondConv, with input-driven parameterization of convolutional kernels,                                                                      | _  |

|      | requires 2 fewer convolutions. Reprinted from B. Yang et.al. [30]                                                                           | 33 |

xiv LIST OF FIGURES

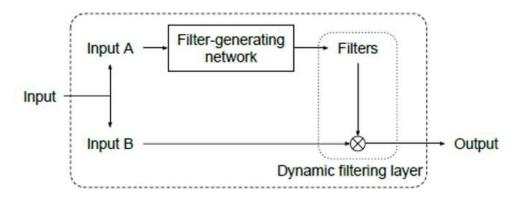

| 2.20 | Dynamic Filter Network (DFN) general architecture. Reprinted from B.                                                                      |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | D. Brabandere et.al. [90]                                                                                                                 | 34 |

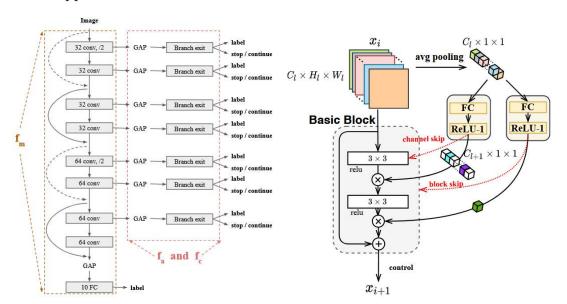

|      | Decision-Making Mechanisms' Architecture Examples                                                                                         | 35 |

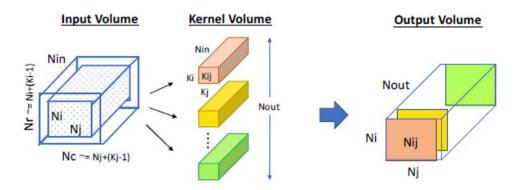

|      | Parameters of DNN layers. Reprinted from M. Putic et.al. [34]                                                                             | 38 |

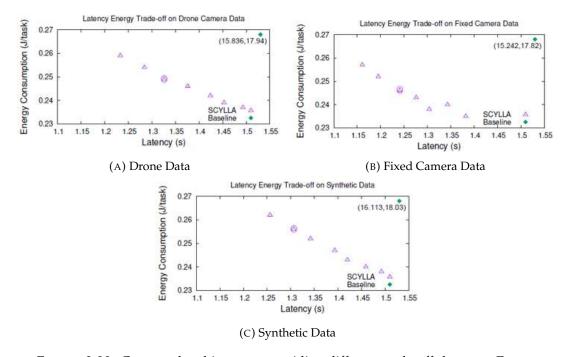

| 2.23 | Generated architectures providing different trade-offs between Energy                                                                     |    |

|      | Consumption and Latency. Reprinted from S. Jiang et.al. [111]                                                                             | 40 |

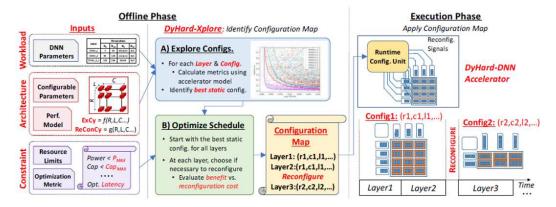

| 2.24 | DyHard-DNN methodology. Reprinted from B. D. Brabandere et.al. [90].                                                                      | 41 |

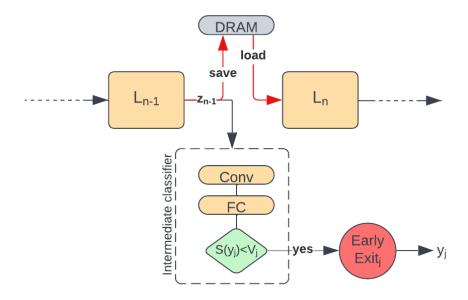

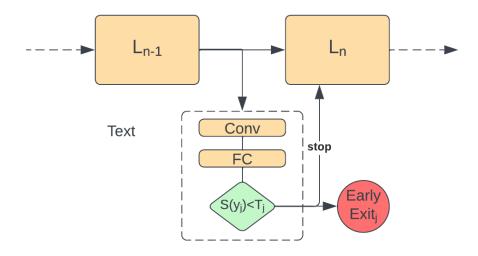

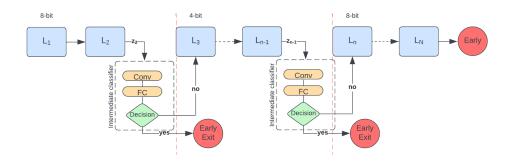

| 3.1  | Early-Exit Dynamic DNN architecture                                                                                                       | 45 |

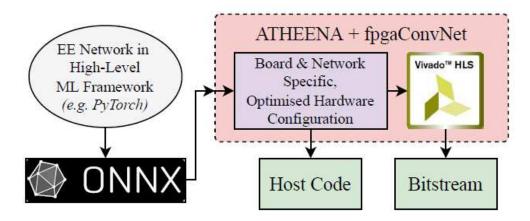

| 3.2  | High-level overview of the components of the ATHEENA framework. Reprinted from B. Biggs et.al. [121]                                      | 48 |

| 3.3  | AdaPEx workflow. Reprinted from G. Korol et.al. [122]                                                                                     | 49 |

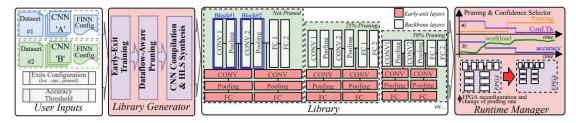

| 3.4  | The Early-Exit Dynamic DNN FPGA Design Approach                                                                                           | 50 |

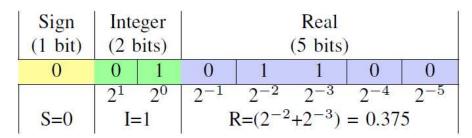

| 3.5  | Example of fixed-point representation of the real number 1.375                                                                            | 51 |

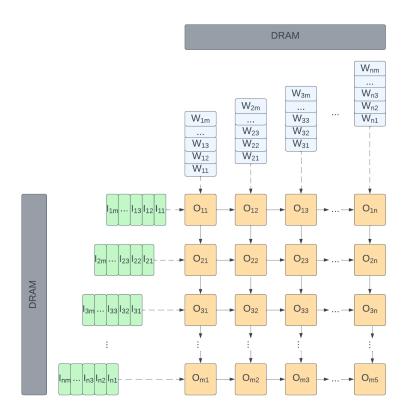

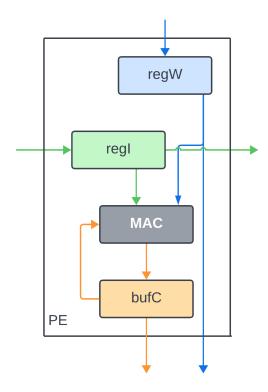

| 3.6  | The design of the systolic array following an Output Stationary data-flow.                                                                | 52 |

|      |                                                                                                                                           | 53 |

| 3.7  | The design of the processing element on our FPGA architectures                                                                            |    |

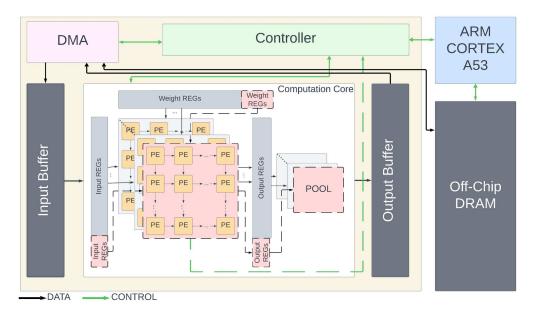

| 3.8  | Design Overview                                                                                                                           | 54 |

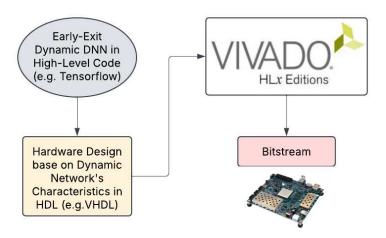

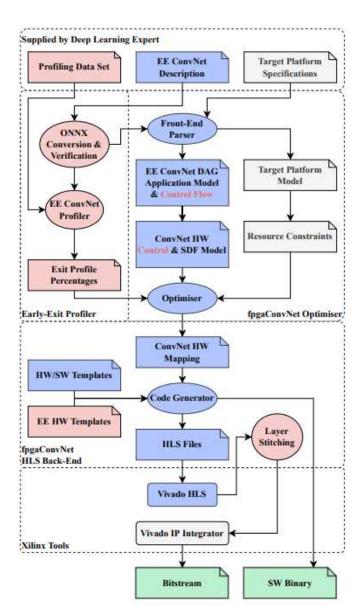

| 3.9  | Tooling Flow Diagram                                                                                                                      | 55 |

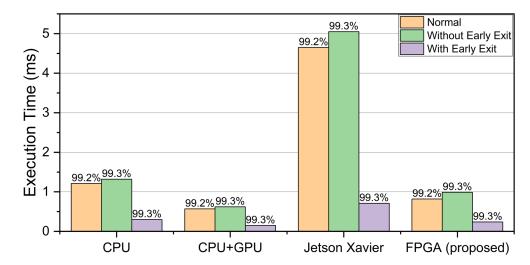

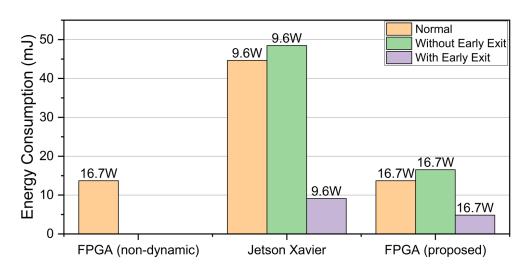

| 3.10 | Experimental results comparing average Execution Time per sample. Average values are calculated based on each exit point trigger rate     | 57 |

| 3.11 | Experimental results comparing average Energy Consumption per sample. Average values are calculated based on each exit point trigger rate | 58 |

| 4.1  | Parallel Approach.                                                                                                                        | 63 |

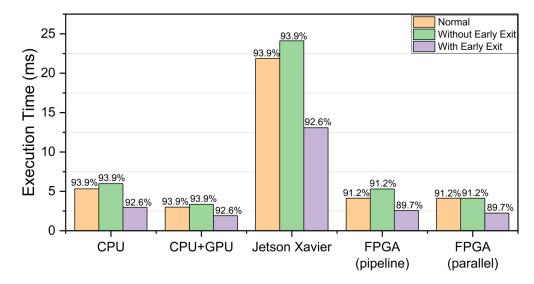

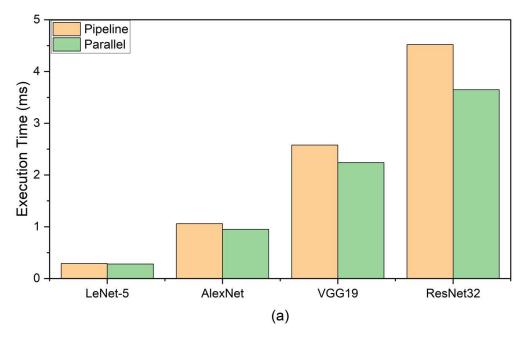

| 4.2  | Experimental results comparing average Execution Time per sample. Av-                                                                     | 00 |

| 7.2  | erage values are calculated based on each exit point trigger rate $(a_i)$                                                                 | 67 |

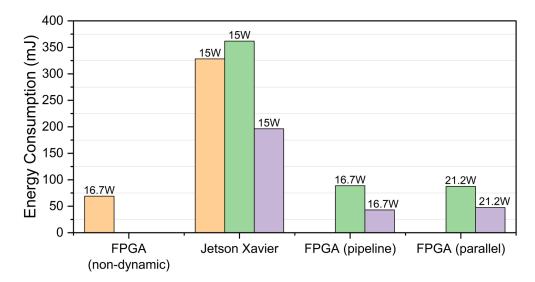

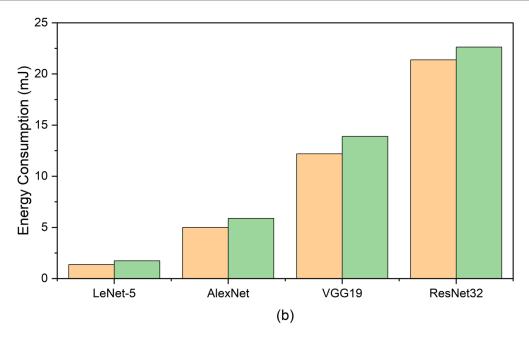

| 4.3  | Experimental results comparing average Energy Consumption per sam-                                                                        | ٠. |

| 1.0  | ple. Average values are calculated based on each exit point trigger rate                                                                  |    |

|      | $(a_i)$                                                                                                                                   | 68 |

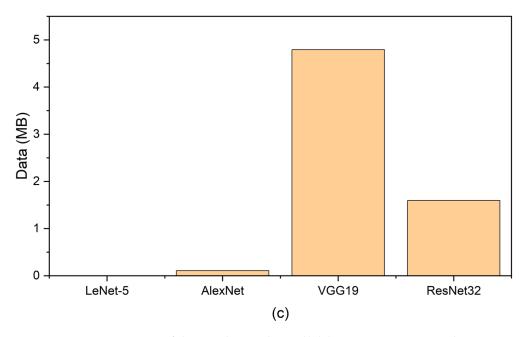

| 4.4  | Comparison of the <i>pipeline</i> and <i>parallel</i> designs over average execution                                                      |    |

|      | time across early-exit LeNet-5, AlexNet, VGG19 and ResNet32                                                                               | 71 |

| 4.5  | Comparison of the <i>pipeline</i> and <i>parallel</i> designs over average energy                                                         |    |

|      | consumption across early-exit LeNet-5, AlexNet, VGG19 and ResNet32.                                                                       | 72 |

| 4.6  | Comparison of the <i>pipeline</i> and <i>parallel</i> designs over average data move-                                                     |    |

|      | ment across early-exit LeNet-5, AlexNet, VGG19 and ResNet32                                                                               | 74 |

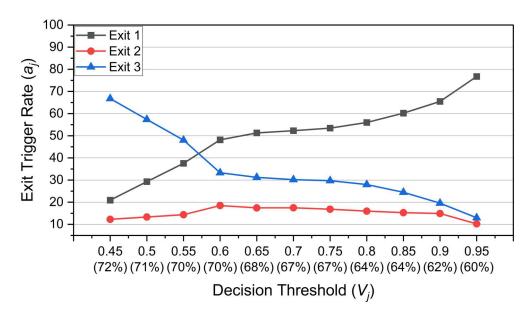

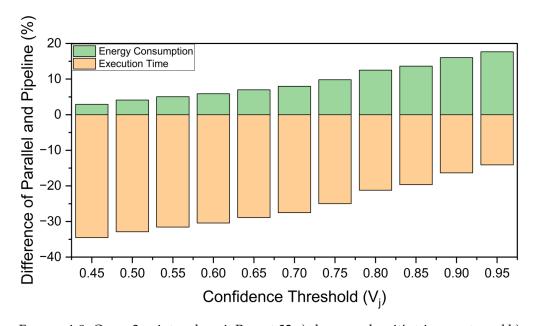

| 4.7  | On a 3 point early-exit Resnet-32 a) shows each exit's trigger rate and b)                                                                |    |

|      | the percentage difference of <i>parallel</i> over <i>pipeline</i> approaches over Energy                                                  |    |

|      | and Time for different Decision Thresholds                                                                                                | 74 |

| 4.8  | On an 3 point early-exit Resnet-32 a) shows each exit's trigger rate and b)                                                               |    |

|      | the percentage difference of <i>parallel</i> over <i>pipeline</i> approaches over Energy                                                  |    |

|      | and Time for different Decision Thresholds                                                                                                | 75 |

|      |                                                                                                                                           |    |

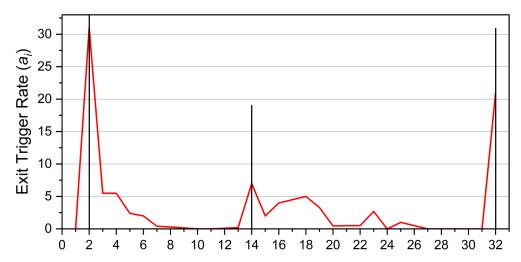

| 5.1  | The exit trigger rates $(a_i)$ of an early-exit ResNet-32 Dynamic DNN with                                                                |    |

|      | an intermediate classifier after every layer.                                                                                             | 80 |

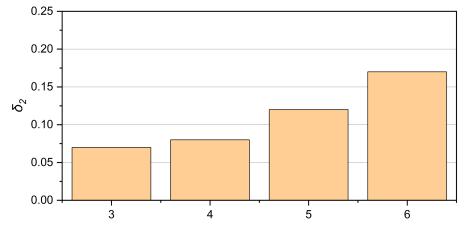

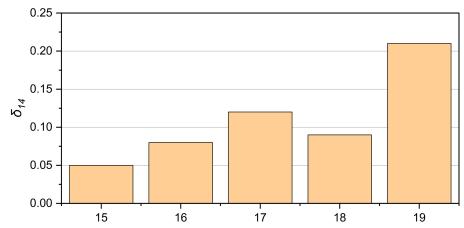

| 5.2  | Average $\delta_j$ for the input samples that failed to trigger exit points 2 and                                                         |    |

|      | 14 but achieved it at points 3 to 6 and 15 to 19 accordingly                                                                              | 82 |

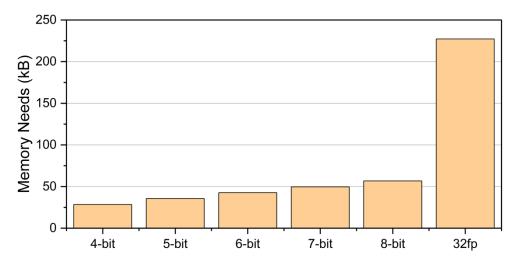

| 5.3  | Early-Exit Branches Memory Needs over different quantisation levels                                                                       | 86 |

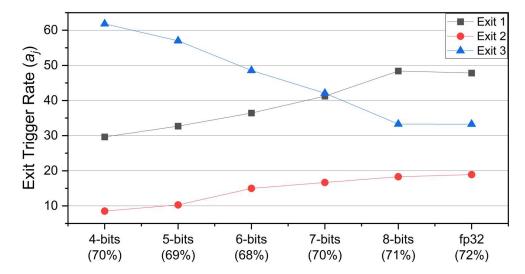

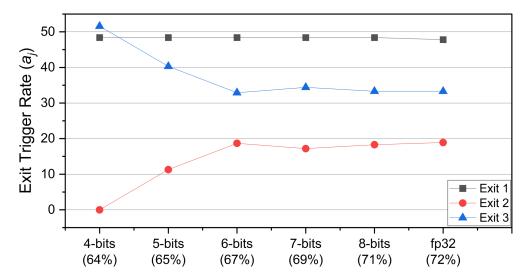

| 5.4  | Percentage of samples to trigger each exit point over different quantisa-                                                                 |    |

|      | tion levels of the exit branch.                                                                                                           | 87 |

LIST OF FIGURES xv

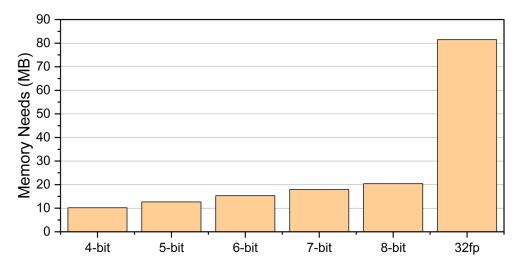

| 5.5  | Early-exit ResNet-32 memory needs over different quantisation levels                                 | 90  |

|------|------------------------------------------------------------------------------------------------------|-----|

| 5.6  | Percentage of samples to trigger each exit point over different quantisa-                            |     |

|      | tion levels of the early-exit network                                                                | 91  |

| 5.7  | Dynamic Quantisation Scheme for Early-Exit Dynamic DNNs                                              | 94  |

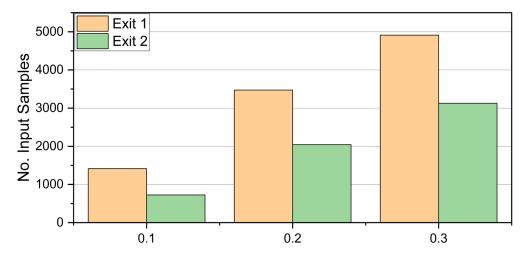

| 5.8  | The number of inputs for which $\delta \leq 0.1$ , $\delta \leq 0.2$ and $\delta \leq 0.3$ at Exit 1 |     |

|      | and Exit 2                                                                                           | 94  |

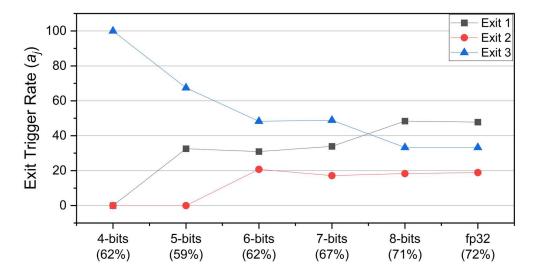

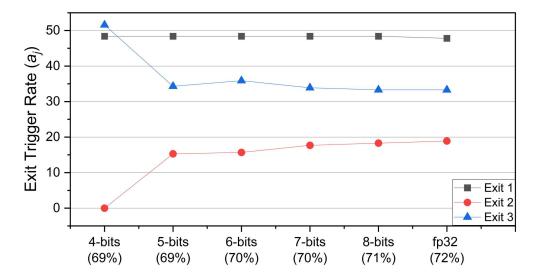

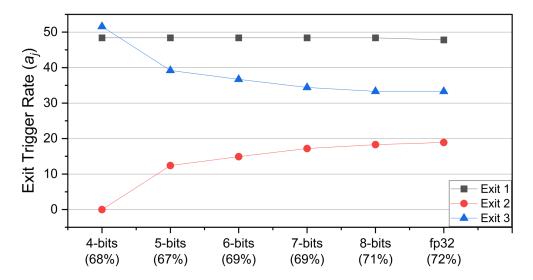

| 5.9  | Percentage of samples to trigger each exit point over different dynamic                              |     |

|      | quantisation levels when $\delta \leq 0.1.$                                                          | 95  |

| 5.10 | Percentage of samples to trigger each exit point over different dynamic                              |     |

|      | quantisation levels when $\delta \leq 0.2.$                                                          | 95  |

| 5.11 | Percentage of samples to trigger each exit point over different dynamic                              |     |

|      | quantisation levels when $\delta \leq 0.3.$                                                          | 96  |

|      | 1. A 1 I N . E (; 1 1 ; . ( N)); / FCF001 1                                                          | 105 |

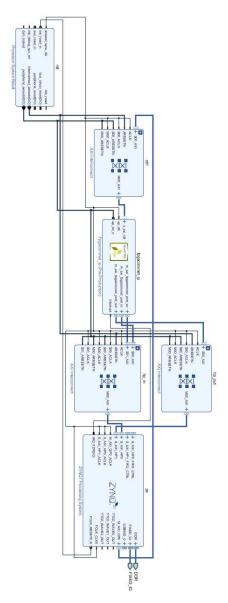

|      | endix A.1 LeNet-5 final design for Xilinx's ZC702 board                                              |     |

| App  | endix A.2 ATHEENA processing flow. Reprinted from B. Biggs et.al. [121]                              | 106 |

# **List of Tables**

| 2.1 | recognition DNN. Reprinted from M. Putic et.al. [34]                                                                              | 38 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | FPGA Resource Utilisation                                                                                                         | 53 |

| 3.2 | Execution Time (ms) of a static (Normal) and an early-exit dynamic LeNet-5 DNN                                                    | 58 |

| 3.3 | Energy Consumption (mJ), with (w/ EE) and without (w/o EE) early exits of a dynamic LeNet-5 DNN                                   | 58 |

| 4.1 | Resource Utilisation                                                                                                              | 66 |

| 4.2 | Execution Time (ms)                                                                                                               | 69 |

| 4.3 | Energy Consumption (mJ), with (w/ EE) and without (w/oEE) early exits                                                             | 70 |

| 4.4 | Performance Comparison With Existing Implementations                                                                              | 73 |

| 5.1 | Exit Trigger Rates (%)                                                                                                            | 82 |

| 5.2 | Execution Time (ms)                                                                                                               | 83 |

| 5.3 | Per Sample Execution Time (ms) of Early-Exit Dynamic ResNet-32 over Different Quantisation Levels of Intermediate Classifiers     | 88 |

| 5.4 | Per Sample Energy Consumption (mJ) of Early-Exit Dynamic ResNet-32 over Different Quantisation Levels of Intermediate Classifiers | 89 |

| 5.5 | Per Sample Execution Time (ms) of Early-Exit Dynamic ResNet-32 over Different Quantisation Levels                                 | 92 |

| 5.6 | Per Sample Energy Consumption (mJ) of Early-Exit Dynamic ResNet-32 over Different Quantisation Levels                             | 92 |

| 5.7 | Per Sample Execution Time (ms) of Early-Exit Dynamic ResNet-32 with                                                               | 96 |

# **Abbreviations**

| AI    | Artificial Intelligence                           |  |  |  |

|-------|---------------------------------------------------|--|--|--|

| ASIC  | Application-Specific Integrated Circuit           |  |  |  |

| BNN   | Binary Neural Network                             |  |  |  |

| BRAM  | Block RAM (Random Access Memory)                  |  |  |  |

| CAD   | Computer-Aided Design                             |  |  |  |

| CDFG  | Control and Data-Flow Graph                       |  |  |  |

| CLB   | Configurable Logic Block                          |  |  |  |

| CNN   | Convolutional Neural Network                      |  |  |  |

| CPU   | Central Processing Unit                           |  |  |  |

| DAG   | Directed Acyclic Graph                            |  |  |  |

| DDR   | Double Data Rate                                  |  |  |  |

| DNN   | Deep Neural Network                               |  |  |  |

| DPR   | Dynamic Partial Reconfiguration                   |  |  |  |

| DRAM  | Dynamic Random Access Memory                      |  |  |  |

| DRP   | Dynamically Reconfigurable Processor              |  |  |  |

| DSP   | Digital Signal Processor                          |  |  |  |

| FC    | Fully Connected (Layer)                           |  |  |  |

| FLOPs | Floating Point Operations Per Second              |  |  |  |

| FP32  | 32-bit Floating Point                             |  |  |  |

| FPGA  | Field-Programmable Gate Array                     |  |  |  |

| GPU   | Graphics Processing Unit                          |  |  |  |

| HLS   | High-Level Synthesis                              |  |  |  |

| IEEE  | Institute of Electrical and Electronics Engineers |  |  |  |

| IO    | Input/Output                                      |  |  |  |

| IoT   | Internet of Things                                |  |  |  |

| ILA   | Integrated Logic Analyzer                         |  |  |  |

| LSTM  | Long Short-Term Memory                            |  |  |  |

| LTE-M | Long-Term Evolution Machine                       |  |  |  |

| LUT   | Lookup Table                                      |  |  |  |

| MAC   | Multiply-Accumulate                               |  |  |  |

| ML    | Machine Learning                                  |  |  |  |

| NAS   | Neural Architecture Search                        |  |  |  |

XX ABBREVIATIONS

NPU Neural Processing Unit **Processing Element** PE RAM Random Access Memory Regular Iterative Algorithms **RIA** Register Transfer Level RTL SoC System on Chip TPU Tensor Processing Unit VHSIC Hardware Description Language **VHDL** Very High Speed Integrated Circuit VHSIC VLIW Very Long Instruction Word VPU Vision Processing Unit

## Chapter 1

### Introduction

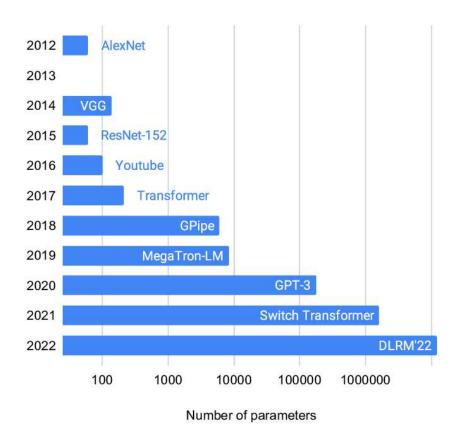

Deep Neural Networks (DNNs) have emerged to be a transformative and very effective technology, revolutionising various cognitive applications such as computer vision [1], [2], voice recognition [3], natural language processing [4] etc. Characterized by their ability to model complex patterns, modern DNNs, such as ResNet [2], DenseNet [5], VGG [6], GoogleNET [7] and Transformers [4] have achieved unprecedented performance, while recent research on Neural Architecture Search (NAS) [8], [9] enables easier and faster design of even more powerful and complex structures. Their success derives from many reasons, including advancements in computational power, availability of larger datasets, increased model depth and innovations in training. Figure 1.1 highlights the increase in parameter numbers of deep neural networks in the decade between 2012 and 2022.

This increase in complexity and depth leads to significantly higher computational demands. Traditional CPU platforms often fail to process deep neural network models at the speeds required for real-time tasks. GPUs, on the contrary, offer a viable solution in many cases by leveraging their vast parallel computing capabilities to accelerate matrix-vector operations, which are predominant in DNN computations. Most modern DNN applications are executed on powerful cloud servers containing hundreds of GPUs. More specifically, while initially deployed locally, they retrieve the data from devices like mobile phones or embedded platforms, upload them to the cloud, where inference is executed and then receive the output. These servers have immense processing power, but their operation is very expensive for both natural resources and energy needs. For example, the execution of the ChatGPT [10] language model requires 10000 GPUs and millions of dollars for their operation and cooling [11], [12].

However, there is an increasing interest in moving the execution of inference locally [14], [15], [16], not only reduces the cost of executing DNNs [17] but also can result in lower overall latency and energy consumption (including both computing and communication) compared to using cloud servers. This reduction in latency enhances user

FIGURE 1.1: Number of deep neural network parameters. The x-axis is plotted on a log scale. Reprinted from B. Steiner et.al. [13].

experience [18] and allows for meeting the strict timing demands of real-time applications, such as self-driving cars [19]. Furthermore, many of the data sent to the cloud are personal, e.g. audio clips for voice assistants, and keeping them locally helps to mitigate any potential privacy concerns [20]. Finally using the cloud servers requires accessing the internet, and despite recent advancements in wireless communication (e.g. 5G, LTE-M) there are multiple areas with limited or non-existent connectivity. Performing inference locally can eliminate this issue [21].

Moving the execution of DNNs locally mandated the deployment of the neural models on devices with very restricted resources, e.g. IoT devices, mobile phones, etc. For low-resource settings, custom hardware architectures can be specifically designed for DNNs, optimizing processing elements to meet the required computational characteristics. A device that is proven a strong candidate for accelerating neural network operations is Field-Programmable Gate Arrays (FPGAs) due to their flexibility and parallelization capabilities, all while maintaining very low power consumption. They consist of a flexible collection of logic elements and IP blocks that can be configured for a specific application. When designed efficiently, they can achieve higher power efficiency than GPUs and CPUs [22].

Nevertheless, large networks can require around 40 billion operations [6] and hundreds of millions of parameters to process even a single  $224 \times 224$  image. Despite the capabilities of FPGAs, they are devices with a restricted amount of resources, and the aforementioned DNN requirements render their deployment infeasible. To overcome that, the networks' compression is mandatory.

### 1.1 Research Justification

Typical approaches to reduce the inference workload and memory footprint of DNNs, which consequently translates to reduced energy consumption, primarily focus on parameter reduction. Quantization [23] entails lowering the precision of DNN weights and activations from the standard IEEE floating-point value, reducing the memory footprint and the complexity of the computations. Extreme quantization levels involve representing parameters as single bits or employing Binarised Neural Networks (BNNs) [24]. Pruning [25] is another approach through which a subset of the network's redundant or less significant parameters are removed, which greatly reduces the model's memory footprint. Nonetheless, this often entails computing large, sparse, and sometimes unstructured matrix multiplications. Also, removing certain connections or neurons may reduce the network's capacity to generalize across diverse datasets, leading to over-fitting or under-fitting in certain scenarios. Finally, Knowledge Distillation [26] has gained popularity as a technique to decrease the size of networks during training by incorporating the loss from larger capacity networks into smaller ones. All of these approaches result in more compact and efficient models, however they act in a static manner, permanently affecting the network which leads in the reduction of accuracy and representation power. To further enhance efficiency and performance, dynamic approaches are utilized.

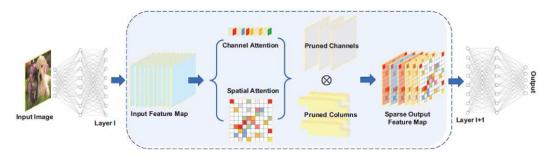

As opposed to static methods of compression, dynamic approaches generate DNN architectures that can adapt their characteristics to various variables, including network inputs, hardware resources, etc. They are able to strategically allocate computations on demand at run-time by selectively activating model components (e.g. layers [27], channels [28] or sub-networks [29]) which consequently leads to a reduction of computations spent on easy to recognise samples or less informative parts of an input. Furthermore, data-driven network architectures enhance DNNs by enabling a significantly enlarged parameter space and improving representation power. For example, by applying feature-conditioned attention weights on a convolution layer's kernel, the model's capacity can be boosted [30], [31]. The popular soft attention mechanism could also be integrated into the framework of dynamic networks, as different channels of

features are dynamically re-weighted or pruned at run-time (Figure 1.2). Finally, dynamism can also be driven by environmental hardware variables (i.e. available memory, power consumption constraints, etc.), giving them the ability to deal and adapt with different hardware platforms and varying computational budgets [32].

FIGURE 1.2: Dynamic channel and spatial column pruning. Reprinted from J. Shen et.al. [33].

Alongside dynamic network architectures, hardware-focused research on dynamic execution of DNNs aims to adapt the hardware platform to the model's characteristics. These approaches utilize the programmability and reconfigurability of FPGAs to adjust them to the layers' computational needs of the target DNN. While networks are getting deeper and more complex, their layers' types and characteristics are changing and have an increased variation [34]. For example, by altering the size of a systolic array of process elements, more efficient computation of depth-wise over normal convolution can be achieved [35]. This exploits even more the parallelism and acceleration potential of the FPGAs and makes them more appealing to deeper networks.

Although dynamic networks showcase great results, not only accelerating but also increasing the effectiveness, simplicity and adaptability of complex and computationally intensive networks, there is a gap between theoretical findings and real-world applications [36]. Dynamic networks are designed using libraries optimized for static models and evaluated on conventional CPU-GPU systems, resulting in inconsistency between anticipated and actual effectiveness. CPU performance still cannot meet the real-time processing requirements in embedded devices, and GPU power consumption is too high. On the contrary, FPGAs have already proven to be very effective at realising DNNs and maintaining very low energy demands. At the same time, the dynamic hardware approaches unlock further adaptability to modern networks' needs. Combining the hardware capabilities of FPGAs and the benefits of dynamic DNN architectures can be a vital contribution towards enabling the deployment of modern neural networks locally on edge devices, yet nobody has considered this to date.

### 1.2 Research Questions

Following the research justification above and the literature review in Chapter 2, this thesis investigates the benefits of realising a dynamic neural network in a custom hardware platform such as FPGAs. Dynamic DNNs have already been proven on a theoretical level to significantly reduce computational needs and, as a result, the energy needed to execute a neural network's inference. However, there aren't any practical results, so this thesis aims to further exploit their capabilities and accelerate and reduce their power needs with FPGAs. This platform has already been shown to offer enhanced capabilities to efficiently accommodate DNNs while achieving very low energy consumption, and its programmability and reconfigurability render it the perfect device for research. In summary, the three questions answered in this thesis are:

# Q1. What are the challenges Dynamic DNNs' architectural characteristics introduce to their implementation on FPGAs? Can Dynamic DNNs be implemented on FPGAs?

Research question **Q1** aims to investigate the feasibility of realising dynamic DNNs on FPGAs. As their architecture differs from static networks, they introduce limitations in deploying state-of-the-art libraries, tools and frameworks, making their implementation challenging. This question is answered in Chapter 3.

# Q2. How can the performance of Dynamic networks be enhanced with the parallelization capabilities of FPGAs?

FPGAs are very capable of parallelising computations. How can the dynamic approaches' computations be parallelised and produce more efficient hardware designs? This question is answered in Chapter 4.

# Q3. How the versatility/reconfigurability of FPGAs can be utilised to enable dynamic exit point placement and quantisation in dynamic DNNs?

FPGAs allow the use of custom data flows, representation resolutions, and even dynamic reconfiguration of the hardware design. How can this versatility and reconfigurability enhance the dynamic network effectiveness and lead to lower latency and energy consumption by dynamically controlling the depth of exit points and the quantisation level? This question is answered in Chapter 5.

### 1.3 Research Contributions

To address the above research questions, the contributions that have been made during this research are summarized as follows:

- C1. Study on the challenges of realising Dynamic DNNs on FPGAs. Chapter 3 highlights the differences in the dynamic networks' architecture and the limitations they introduce both to software design and to state-of-the-art hardware approaches, targeting the realisation of dynamic DNNs on FPGAs. This contribution partially answers Question 1.

- Anastasios Dimitriou, Benjamin Biggs, Jonathon Hare, Geoff V. Merrett. **FPGA** Acceleration of Dynamic Neural Networks: Challenges and Advancements. In *IEEE International Conference on Omni-Layer Intelligent Systems (COINS), London, UK*, 2024.

- C2. The first realisation of Dynamic DNNs on FPGAs Chapter 3 presents a first FPGA design that fully deploys early-exit dynamic DNNs on FPGAs. The design's experimental results showcased the capability of FPGAs to efficiently deploy and execute dynamic DNNs while achieving very low energy consumption. This contribution partially answers Question 1.

- Anastasios Dimitriou, Mingyu Hu, Jonathon Hare, Geoff V. Merrett. **Exploration of Decision Sub-Network Architectures for FPGA-based Dynamic DNNs.** *In Design Automation and Test in Europe (DATE) Conference, Antwerp, Belgium,* 2023.

- C3. Exploration on how the parallelisation capabilities of FPGAs can be leveraged to increase the efficiency of early-exit dynamic DNNs implementations Chapter 4 proposes a second design approach that, by utilising the parallelization capabilities of FPGAs, addresses two of the early-exit networks' implementation challenges. Additionally a first modelisation of the execution time and the energy consumption of early-exit dynamic DNNs inference on FPGAs is presented. This contribution answers Question 2.

- Anastasios Dimitriou, Lei Xun, Jonathon Hare, Geoff V. Merrett. **Realisation of Early-Exit Dynamic Neural Networks on Reconfigurable Hardware**. Submitted to IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), 2024.

- C4. Two dynamic approaches that utilise the confidence values of input samples that fail to trigger an early exit. Chapter 5 introduces two confidence-controlled dynamic schemes concerning the placement of intermediate classifiers and quantisation. Employing the versatility and reprogrammability of FPGAs, the dynamic schemes increase the efficiency and performance of the early-exit dynamic DNN designs with minimal accuracy drop. This contribution answers Question 3.

1.4. Thesis Structure 7

### 1.4 Thesis Structure

This thesis is divided into several chapters that address different aspects of realising dynamic DNNs on FPGA platforms. Chapter 2 provides an overview of the fundamentals and current state-of-the-art in deploying efficiently DNN models, as well as techniques for both software and hardware dynamic execution approaches of neural networks.

Chapter 3 focuses on answering (Q2). Initially, the architecture differences between static and dynamic networks and how they introduce limitations in their implementation on FPGAs are presented. More specifically, a thorough exploration of the architecture of early-exit dynamic networks and the challenges they introduce in software and hardware design are presented, alongside some recent advancements to resolve them . A first realisation of the early-exit dynamic networks is explored, and experimental results comparing CPU, CPU-GPU, embedded and FPGA platforms over execution time and energy consumption are discussed.

Chapter 4 extends this work and introduces a second design approach, leveraging the parallelisation capabilities of FPGAs and answers to the second research question (Q2). Experimental results are also discussed, while a thorough comparison between the two design approaches over execution time, energy consumption, memory footprint and decision threshold levels highlights which better fits different target applications. Furthermore, two equations are presented to model the energy demands and the execution time of the early-exit dynamic networks' inference on FPGAs, targeting both architectures.

Chapter 5 explores how the information from the input sample's confidence level, obtained by the intermediate classifiers, can be combined with the capabilities of the FP-GAs to enhance the performance of the early-exit networks. More specifically, this Chapter explored two different directions, answering research question 3 (Q3). The first focuses on a dynamic placement of the early-exit networks' intermediate classifiers scheme, taking advantage of the *parallel* design approach in order to further adapt the early-exiting architecture to the variety of the input samples. Following that, the second direction explores the quantisation of the early-exit dynamic DNNs initially applied only on the intermediate classifiers and then on the entirety of the dynamic network. Finally, it introduces a dynamic quantisation scheme, where different network parts have different quantisation levels, to reduce resource needs with minimal effects on early-exiting behaviour and accuracy.

Finally, Chapter 6 summarizes this thesis's key findings and discusses plans for future research in this area.

## **Chapter 2**

# **Background Theory**

Efficient deployment and execution of DNNs on mobile and embedded platforms are crucial for their widespread adoption [14]. However, this task presents many challenges [15], [16], as despite achieving state-of-the-art performance, deep neural networks (DNNs) are inherently both computationally and memory access intensive. This Chapter begins with an overview of modern DNNs in Section 2.1, followed by an exploration and comparison of the different hardware platforms targeting their deployment in Section 2.2, focusing on the FPGAs, which is the target device of this thesis. To achieve the deployment of DNNs in resource-restricted devices, however, their compression is necessary. Section 2.3 provides an overview of popular network compression methods and, finally, Section 2.4 and Section 2.5 presents a thorough review of current literature in dynamic deep neural networks, covering both software and hardware directions.

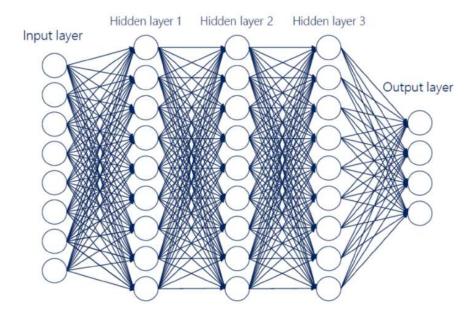

### 2.1 Deep Neural Networks

Deep Neural Networks (DNNs) are one of the foundation models of modern machine learning, inspired by the structure and function of the human brain. They consist of interconnected layers of artificial neurons that process data through a series of transformations. Unlike traditional neural networks, DNNs contain multiple hidden layers between the input and output layers (Figure 2.1), allowing them to learn and model intricate patterns and relationships within data. This depth and different model architectures enable DNNs to tackle highly complex tasks, such as convolutional neural networks [37] for image recognition and sequential models (e.g. LSTMs [38]) for natural language processing.

At the core of DNNs are neurons, which are the basic units that perform computations. Each neuron receives inputs, applies a set of weights, adds a bias, and then passes the

FIGURE 2.1: Deep Neural Network (DNN) example. Reprinted from M. Merenda et.al. [39].

result through an activation function. This process helps to introduce non-linearity into the model, enabling it to learn from errors and adjust the weights during training. The layers of neurons are typically organized into three main types: the input layer, which receives raw data; multiple hidden layers, where intermediate computations are carried out; and the output layer, which produces the final predictions or classifications.

However, before deploying DNNs, they have to be trained. Training a DNN involves optimizing the weights and biases using a process called backpropagation [40], which adjusts these parameters to minimize the error between the predicted output and the actual target. This is achieved through iterative algorithms such as stochastic gradient descent. The depth and complexity of DNNs allow them to capture high-level abstractions in data, making them particularly effective for tasks that require an understanding of hierarchical structures, such as recognizing objects in images or understanding the context in language.

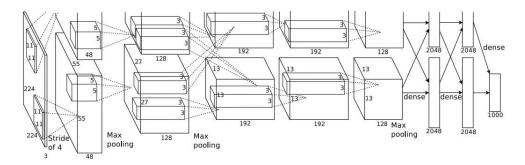

#### 2.1.1 Convolutional Neural Networks

Convolutional Neural Networks (CNNs or ConvNets) are a specialized class of deep neural networks designed primarily for processing structured grid-like data, such as images. Inspired by the visual cortex of the human brain, CNNs are particularly effective at capturing information in data through their unique architecture, which includes convolutional, pooling, and fully connected layers. This allows CNNs to automatically and adaptively learn spatial hierarchies of features, making them exceptionally powerful for tasks such as image classification, object detection, and segmentation.

FIGURE 2.2: Architecture of AlexNet CNN model. Reprinted from A. Krizhevsky et.al. [1].