## University of Southampton Research Repository

Copyright © and Moral Rights for this thesis and, where applicable, any accompanying data are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis and the accompanying data cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content of the thesis and accompanying research data (where applicable) must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holder/s.

When referring to this thesis and any accompanying data, full bibliographic details must be given, e.g.

Thesis: Sulaiman Sadiq (2025) "Efficient Deep Learning Inference at the Edge", University of Southampton, Faculty of Engineering and Physical Sciences, School of Electronics and Computer Science, PhD Thesis, 149pp.

Data: Sulaiman Sadiq (2025) Data for Efficient Deep Learning Inference at the Edge. URI [10.5258/SOTON/D3550]

### University of Southampton

Faculty of Engineering and Physical Sciences School of Electronics and Computer Science Cyber-Physical Systems Research Group MINDS Centre for Doctoral Training

# Efficient Deep Learning Inference at the Edge

DOI: 10.5258/SOTON/D3550

## by

## Sulaiman Sadiq

BE, National University of Sciences and Technology (2011) MSc, University of Engineering and Technology (2016) MSc, University of Southampton (2018)

ORCiD: 0000-0003-4959-4623

A thesis for the degree of Doctor of Philosophy

June 2025

#### University of Southampton

#### Abstract

Faculty of Engineering and Physical Sciences School of Electronics and Computer Science

#### Doctor of Philosophy

#### **Efficient Deep Learning Inference at the Edge**

by Sulaiman Sadiq

Deep Learning has found success in a variety of fields. At the same time, the number of connected Internet of Things (IoT) devices is seeing exponential growth. This has lead to the development of the field of TinyML which aims to perform deep learning inference locally on the resource constrained IoT devices. Realising this objective requires optimisation across the inference stack with design of efficient algorithms and inference systems. In the work carried out in this thesis, we explore techniques for efficient model design and deployment for various complexity constraints that are imposed by the resource constraints of the devices or the application scenarios.

The first contribution of this work is a gradient based approach to derive models of varying complexity using neural architecture search (NAS). This is achieved by combining multi-objective optimisation with NAS where we optimise the complexity of the model in addition to its quality. This method derives models of varying complexity without the need for manual heuristics or expensive hit and trial.

The second contribution of our work studies how inference software can effectively utilise device resources to enable design and deployment of efficient models. Whereas prior works typically focus on performing inference within internal memory constraints, we develop the TinyOps inference framework for MCUs which accelerates inference from external memories. TinyOps significantly lifts the ceiling of accuracy achievable with up to 1.4x-2.5x lower inference latency than previous approaches.

The final contribution of this work is an in-depth analysis of DNN deployment on MCUs to derive heuristics for model design and how inference can be adapted at runtime on MCUs for varying latency constraints. We study limitations of existing approaches and benchmark throughput of low-level operations on MCUs. Using our heuristics, we derive models which achieve state-of-the-art TinyML ImageNet classification when considering accuracy, latency and energy efficiency. The heuristics are also utilised in a super-network based approach to derive multiple models for different latency constraints. We show how an efficient accuracy-latency trade-off can be achieved at run-time with the TinyOps inference framework.

## **Contents**

| Li | st of ]                        | Figures | 3                                                  | ix   |  |  |  |  |

|----|--------------------------------|---------|----------------------------------------------------|------|--|--|--|--|

| Li | List of Tables xi              |         |                                                    |      |  |  |  |  |

| D  | Declaration of Authorship xiii |         |                                                    |      |  |  |  |  |

| D  | efinit                         | ions an | nd Abbreviations                                   | xvii |  |  |  |  |

| 1  | Intr                           | oductio | on                                                 | 1    |  |  |  |  |

|    | 1.1                            | Resear  | rch Justification                                  | 2    |  |  |  |  |

|    | 1.2                            | Resear  | rch Questions                                      | 4    |  |  |  |  |

|    | 1.3                            | Resear  | rch Contributions                                  | 5    |  |  |  |  |

|    | 1.4                            | Resear  | rch Output                                         | 7    |  |  |  |  |

|    | 1.5                            |         | s Outline                                          |      |  |  |  |  |

| 2  | Bacl                           | kgroun  | d and Related Work                                 | 11   |  |  |  |  |

|    | 2.1                            | Convo   | olutional Neural Networks                          | 11   |  |  |  |  |

|    |                                | 2.1.1   | Convolutional Layers                               | 12   |  |  |  |  |

|    |                                | 2.1.2   | Depthwise Separable Convolutions                   | 12   |  |  |  |  |

|    | 2.2                            | Mode    | l Design                                           | 13   |  |  |  |  |

|    |                                | 2.2.1   | Static Neural Networks                             | 14   |  |  |  |  |

|    |                                |         | 2.2.1.1 Manual Design                              | 14   |  |  |  |  |

|    |                                |         | 2.2.1.2 Neural Architecture Search                 | 15   |  |  |  |  |

|    |                                |         | 2.2.1.3 Differentiable Architecture Search (DARTS) | 17   |  |  |  |  |

|    |                                | 2.2.2   | Dynamic Neural Networks                            | 23   |  |  |  |  |

|    |                                |         | 2.2.2.1 Dynamic Structure                          | 23   |  |  |  |  |

|    | 2.3                            | Mode    | l Optimisation                                     | 24   |  |  |  |  |

|    |                                | 2.3.1   | Pruning                                            | 24   |  |  |  |  |

|    |                                | 2.3.2   | Quantisation                                       | 25   |  |  |  |  |

|    |                                |         | 2.3.2.1 Vector Quantisation                        | 26   |  |  |  |  |

|    |                                |         | 2.3.2.2 Scalar Quantisation                        | 26   |  |  |  |  |

|    |                                |         | 2.3.2.3 Linear Quantisation on MCUs                | 28   |  |  |  |  |

|    | 2.4                            | Mode    | l Deployment                                       | 30   |  |  |  |  |

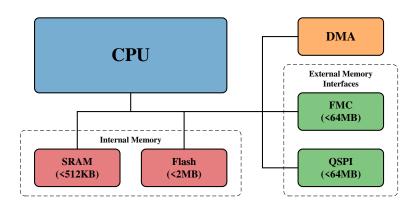

|    |                                | 2.4.1   | Hardware Characteristics                           | 30   |  |  |  |  |

|    |                                |         | 2.4.1.1 Instruction Set                            | 31   |  |  |  |  |

|    |                                |         | 2.4.1.2 Peripherals                                | 32   |  |  |  |  |

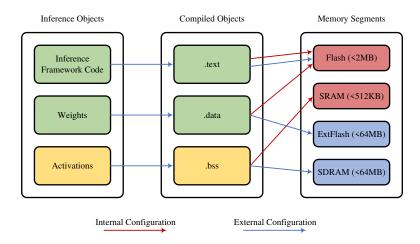

|    |                                | 2.4.2   | Inference Frameworks                               |      |  |  |  |  |

|    |                                |         | 2.4.2.1 Compiler Sections                          | 34   |  |  |  |  |

vi CONTENTS

|   |       |         | 2.4.2.2 Memory Usage                                       |

|---|-------|---------|------------------------------------------------------------|

|   |       | 2.4.3   | Kernels                                                    |

|   | 2.5   | Discus  | ssion                                                      |

| 3 | DEf   | f-ARTS  | S: Differentiable Efficient ARchiTecture Search 41         |

|   | 3.1   | Non-L   | inear Multi-Objective Bi-Level Optimisation Problem 42     |

|   |       | 3.1.1   | Compute Cost                                               |

|   |       | 3.1.2   | Performance Loss                                           |

|   |       |         | 3.1.2.1 Linear Combination                                 |

|   |       |         | 3.1.2.2 Non-Linear Transformation                          |

|   |       | 3.1.3   | Multi-Objective Bi-Level Optimisation                      |

|   | 3.2   | Result  | ,                                                          |

|   |       | 3.2.1   | Architecture Search                                        |

|   |       | 3.2.2   | Derived Cells                                              |

|   |       | 3.2.3   | Architecture Evaluation                                    |

|   | 3.3   | Discus  | ssion                                                      |

|   |       |         |                                                            |

| 4 | •     | _       | A New Model Design Space for MCUs  61                      |

|   | 4.1   |         | al vs External Memory                                      |

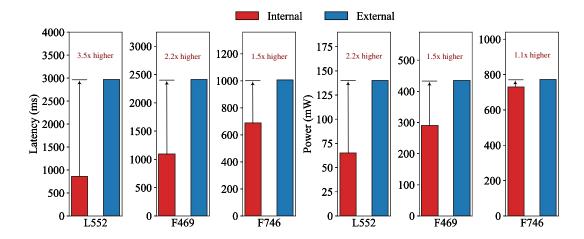

|   |       | 4.1.1   | Performance Evaluation                                     |

|   | 4.2   | U       | n of TinyOps                                               |

|   |       | 4.2.1   | Insights                                                   |

|   |       | 4.2.2   | Seamless Integration                                       |

|   |       | 4.2.3   | Operation Categorisation                                   |

|   |       | 4.2.4   | Overlaying Strategy                                        |

|   |       | 4.2.5   | Partitioning Scheme                                        |

|   |       |         | 4.2.5.1 NHWC Partitioning                                  |

|   |       |         | 4.2.5.2 Partitioning an Operation                          |

|   |       |         | 4.2.5.3 Limitations                                        |

|   |       | 4.2.6   | Partitioning the Inference Graph                           |

|   |       | 4.2.7   | Network Inference Pipeline                                 |

|   |       | 4.2.8   | Performance Analysis                                       |

|   | 4.3   | -       | iments and Results                                         |

|   |       | 4.3.1   | Overlaying Strategy                                        |

|   |       | 4.3.2   | Energy Consumption                                         |

|   |       | 4.3.3   | Adaptive Memory Usage                                      |

|   |       | 4.3.4   | Design Space Performance Comparison                        |

|   | 4.4   | Discus  | ssion                                                      |

| 5 | Effic | cient M | odel Design for MCUs 87                                    |

|   | 5.1   | Analy   | sis of Model Design on MCUs                                |

|   |       | 5.1.1   | The Mobile Search Space                                    |

|   |       | 5.1.2   | Studying the Pareto Frontier                               |

|   |       |         | 5.1.2.1 Design Limitations of Internal Memory              |

|   |       | 5.1.3   | Micro-Architecture Latency Analysis                        |

|   |       |         | 5.1.3.1 Operation Throughput Benchmarking 94               |

|   |       |         | 5.1.3.2 Effect of Hyper-parameter Scaling on Throughput 96 |

*CONTENTS* vii

|    |       | 5.1.4 Internal Memory vs TinyOps                             |                                                         |     |  |  |

|----|-------|--------------------------------------------------------------|---------------------------------------------------------|-----|--|--|

|    |       | 5.1.5 Discussion                                             |                                                         |     |  |  |

|    | 5.2   | Accuracy-Latency Trade-Off through Dynamic and Static Models |                                                         |     |  |  |

|    |       | 5.2.1                                                        | Dynamic DNNs via Early-Exiting                          | 10  |  |  |

|    |       |                                                              | 5.2.1.1 Deployment of EENNs                             | 1   |  |  |

|    |       |                                                              | 5.2.1.2 EENN Design                                     | 13  |  |  |

|    |       |                                                              | 5.2.1.3 Model Search and Training                       | 16  |  |  |

|    |       |                                                              | 5.2.1.4 Evaluation                                      | 17  |  |  |

|    |       | 5.2.2                                                        | Static Models for Accuracy-Latency Trade-Off            | 18  |  |  |

|    |       |                                                              | 5.2.2.1 Search and Evaluation                           | 19  |  |  |

|    |       | 5.2.3                                                        | Deployment Cost                                         | .1  |  |  |

|    | 5.3   | Discus                                                       | ssion                                                   | 2   |  |  |

| 6  | Con   | clusion                                                      | as 11                                                   | _   |  |  |

| 0  | 6.1   |                                                              | ary of Contributions                                    |     |  |  |

|    | 6.2   |                                                              | e Work                                                  |     |  |  |

|    | 0.2   | 6.2.1                                                        | Search Space for EENNs                                  |     |  |  |

|    |       | 6.2.2                                                        | Moving Away From CNNs                                   |     |  |  |

|    |       | 6.2.3                                                        | Improving MLOps Tools                                   |     |  |  |

|    |       | 6.2.4                                                        | Next-Generation of Hardware                             |     |  |  |

|    |       | 6.2.5                                                        | Applications in Other Architectures                     |     |  |  |

|    | 6.3   |                                                              | rch Impact                                              |     |  |  |

|    | 0.0   | resear                                                       | ten impact                                              |     |  |  |

| Ap | pend  | lix A                                                        | 12                                                      | .5  |  |  |

|    | App   | endix A                                                      | A.1 Linear Quantisation with Integer-Only Arithmetic 12 | 25  |  |  |

|    | App   | endix A                                                      | A.2 Sample Linker Command File                          | 6   |  |  |

|    |       | 1. D                                                         | 40                                                      |     |  |  |

| Ap | pend  |                                                              | 12                                                      |     |  |  |

|    |       | endix B                                                      | 11                                                      |     |  |  |

|    |       | endix B                                                      | 7.1                                                     |     |  |  |

|    | App   | endix B                                                      | 3.3 DEff-ARTS Architecture Training Hyper-Parameters 13 | 1   |  |  |

| Ar | pend  | lix C                                                        | 13                                                      | 3   |  |  |

| r  | _     |                                                              | C.1 Cell Based Search Space vs Manual Width Scaling 13  |     |  |  |

|    |       |                                                              | C.2 Data Structure for Partitioning Strategy            |     |  |  |

|    |       |                                                              | C.3 Architecture Training Hyper-Parameters              |     |  |  |

|    | rr    |                                                              |                                                         | _   |  |  |

| Ap | pend  | lix D                                                        | 13                                                      | 5   |  |  |

|    | App   | endix [                                                      | D.1 SuperNetwork Training Hyper-Parameters              | 5   |  |  |

| D^ | fores |                                                              | 10                                                      | , – |  |  |

| ve | feren | ices                                                         | 13                                                      | 1   |  |  |

## **List of Figures**

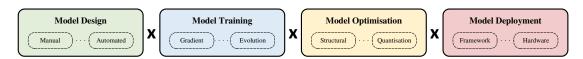

| 1.1  | Inference Components for Deep Neural Networks (DNN)                        | 2  |

|------|----------------------------------------------------------------------------|----|

| 1.2  | Overview of Research Contributions                                         | 6  |

| 1.3  | Overview of Thesis Structure                                               | 9  |

| 2.1  | Convolution Layer                                                          | 12 |

| 2.2  | Depthwise Separable Convolution                                            | 13 |

| 2.3  | Structure of a Mixed Operation                                             | 19 |

| 2.4  | Structure of a 2-Step Cell                                                 | 19 |

| 2.5  | Structure of Network                                                       | 21 |

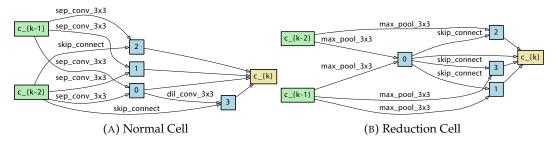

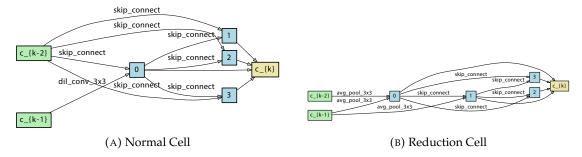

| 2.6  | Cells Discovered by DARTS                                                  | 22 |

| 2.7  | Linear Quantisation                                                        | 29 |

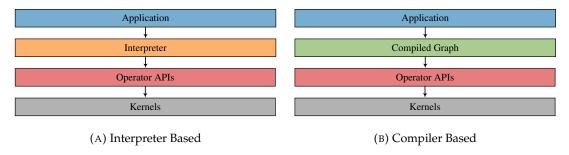

| 2.8  | Code-Generator vs Interpreter Runtime Execution Flow                       | 33 |

| 2.9  | Compiler Sections to Memory Segments                                       | 35 |

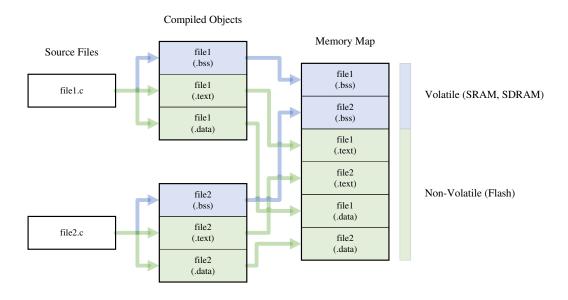

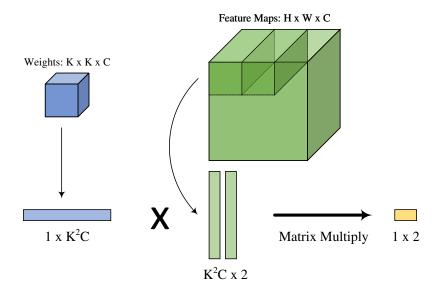

| 2.10 |                                                                            | 37 |

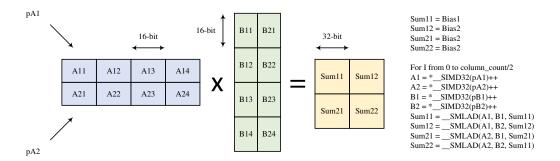

| 2.11 |                                                                            | 38 |

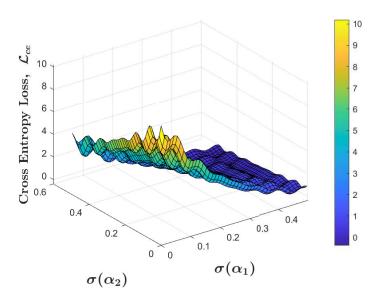

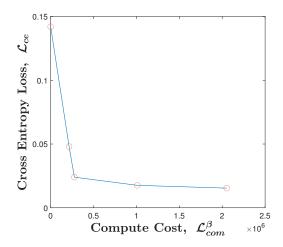

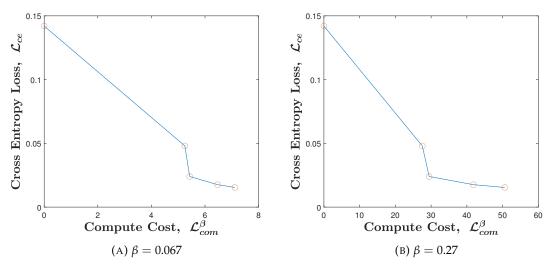

| 3.1  | Cross Entropy Loss Landscape Sketch                                        | 45 |

| 3.2  | Compute Cost with Linear Scaling and Resulting Performance Loss            | 46 |

| 3.3  | Compute Cost vs. Cross Entropy Loss                                        | 46 |

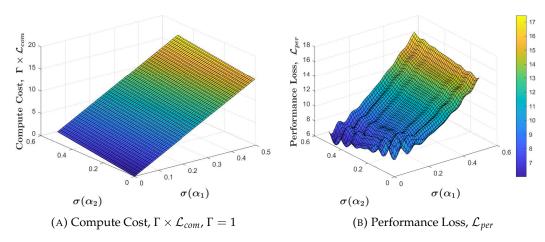

| 3.4  | Non-Linearly Transformed Compute Cost vs. Cross Entropy Loss               | 48 |

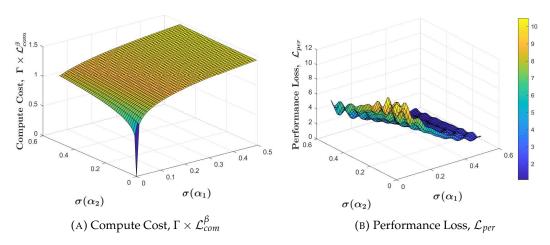

| 3.5  | Compute Cost and Performance Loss, $\Gamma = 1$ , $\beta = 0.135$          | 49 |

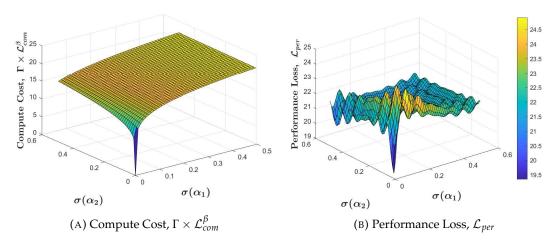

| 3.6  | Compute Cost and Performance Loss, $\Gamma = 15$ , $\beta = 0.135$         | 50 |

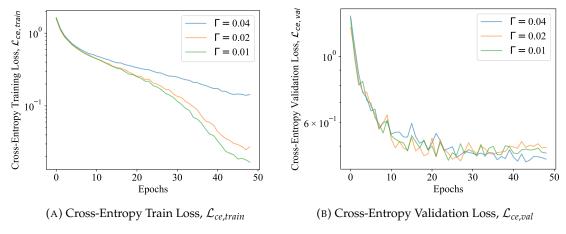

| 3.7  | Cross-Entropy Training and Validation Loss                                 | 53 |

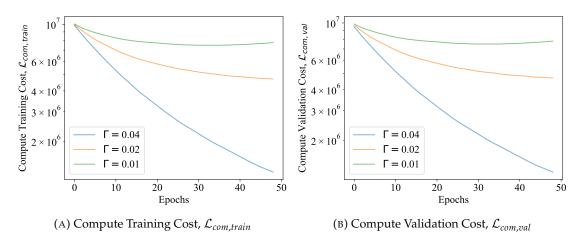

| 3.8  | Compute Training and Validation Cost                                       | 54 |

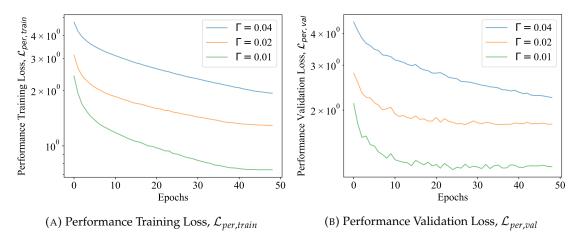

| 3.9  | Performance Training and Validation Loss                                   | 54 |

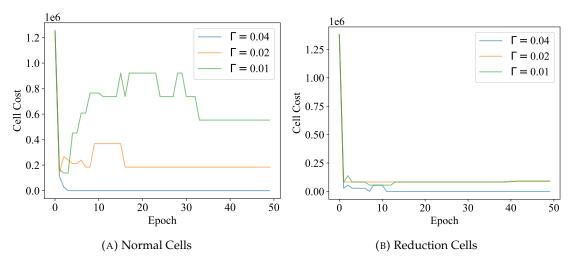

| 3.10 | Discretised Reduction and Normal Cell Costs                                | 55 |

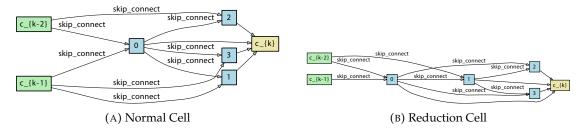

| 3.11 | DEff-ARTS Derived Cells, $\Gamma = 0.01$ , $\mathcal{L}_{com} = 1,010,688$ | 56 |

|      | DEff-ARTS Derived Cells, $\Gamma = 0.02$ , $\mathcal{L}_{com} = 276,480$   | 56 |

|      | DEff-ARTS Derived Cells, $\Gamma = 0.04$ , $\mathcal{L}_{com} = 0$         | 56 |

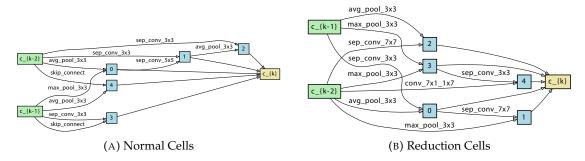

|      | AmoebaNet Cells                                                            | 57 |

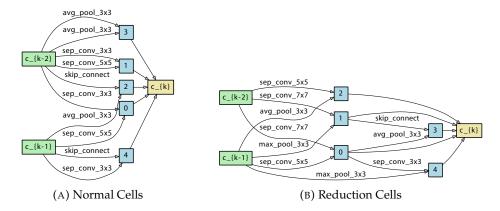

| 3.15 | NASNet Cells                                                               | 58 |

| 4.1  | Microcontroller (MCU) Architecture Block Diagram                           | 62 |

| 4.2  | Inference Frameworks Memory Configurations                                 | 64 |

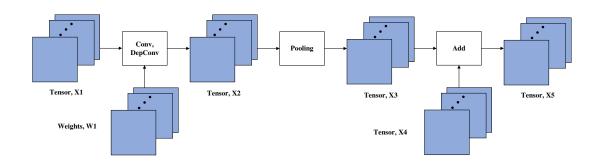

| 4.3  | Traditional Operation Execution                                            | 65 |

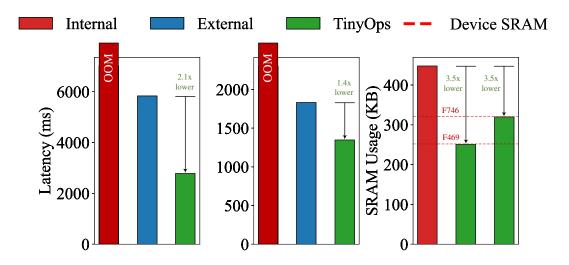

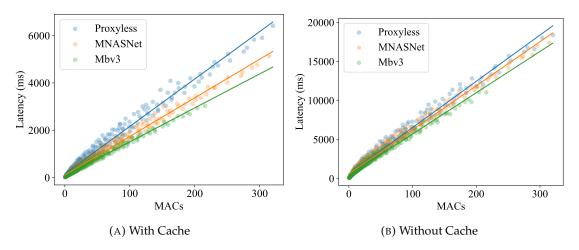

| 4.4  | Performance Comparison of Internal and External Memory                     | 68 |

| 4.5  | TinyOps Overview                                                           | 70 |

| 4.6  | Partitioning of NHWC Tensors Along H Dimension                             | 74 |

x LIST OF FIGURES

| 4.7  | TinyOps Operation Execution                                            | 78  |

|------|------------------------------------------------------------------------|-----|

| 4.8  | Overlaying Strategy Effect on Latency                                  | 82  |

| 4.9  | Adaptive Partitioning Strategy for Diverse Memory Budgets              | 84  |

| 5.1  | Mobile Inverted Conv Block Structure                                   | 89  |

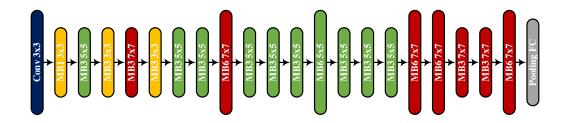

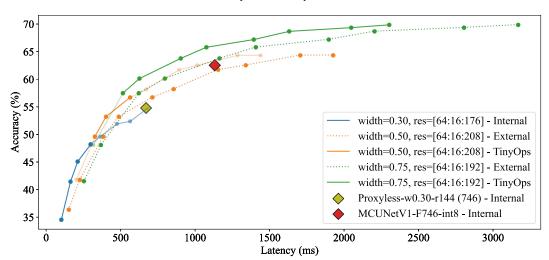

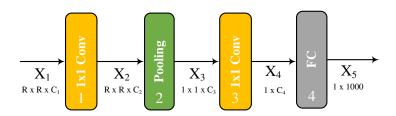

| 5.2  | ProxylessNAS Model Structure                                           | 90  |

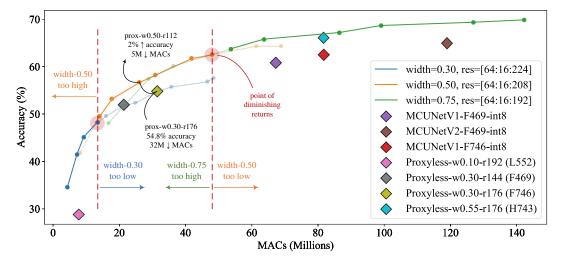

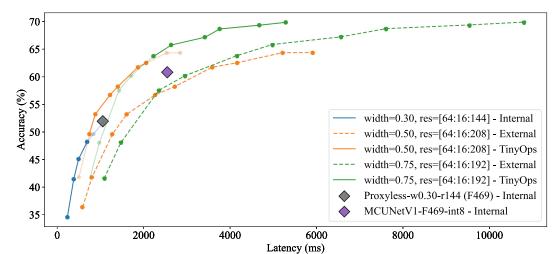

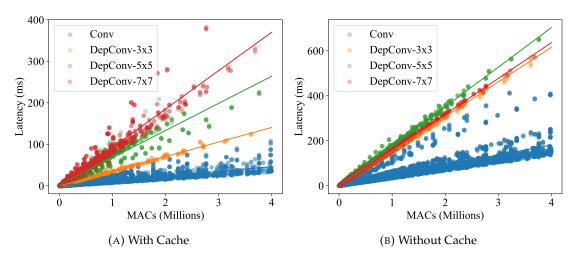

| 5.3  | Accuracy-MACs and Accuracy-Latency Pareto Frontiers                    | 91  |

| 5.4  | MCUNet vs ProxylessNAS Parameter and MACs distribution                 | 93  |

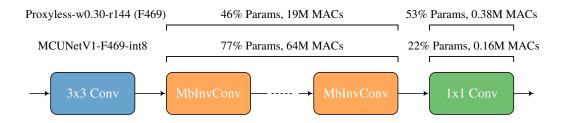

| 5.5  | Throughput of Operations in Mobile Search Space                        | 94  |

| 5.6  | Throughput Comparison of Different Backbone Networks                   | 96  |

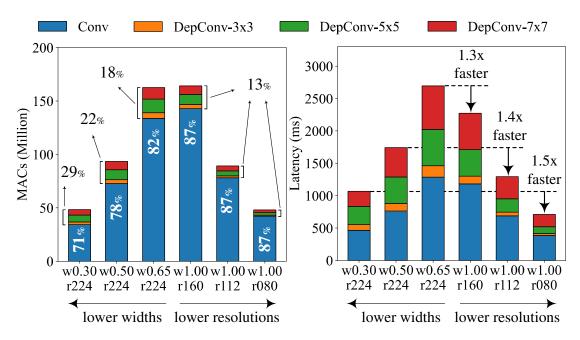

| 5.7  | Effect of Conventional Scaling on Computation and Latency Distribution | 97  |

| 5.8  | Structure of an Early-Exiting Neural Network (EENN)                    | 101 |

| 5.9  | Structure of Early-Exit Classifier                                     | 104 |

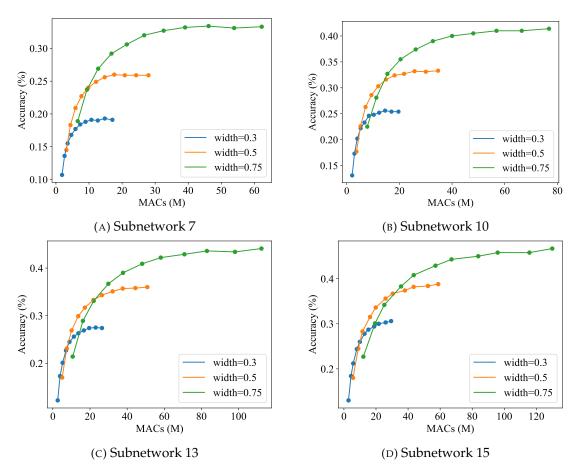

| 5.10 | Accuracy of EECs in the MobileNetV3 search space                       | 106 |

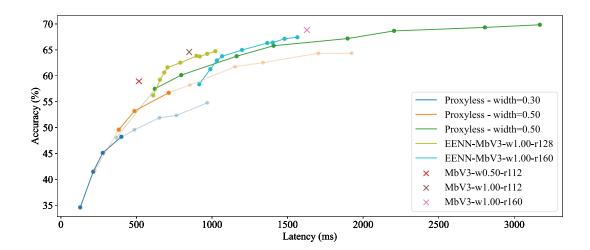

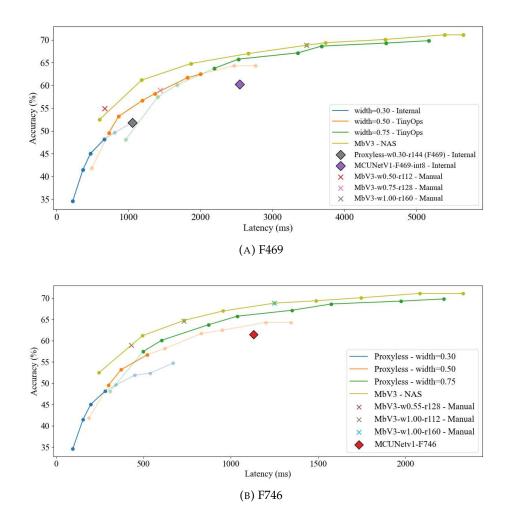

| 5.11 | Performance of EENNs                                                   | 108 |

| 5.12 | Static Models Derived via Light-Weight NAS                             | 110 |

| 6.1  | Summary of Contributions                                               | 116 |

## **List of Tables**

| 2.1 | Characteristics of Compute Platforms used for DNN Workloads        | 31  |

|-----|--------------------------------------------------------------------|-----|

| 3.1 | CPU Operation Costs, C64x+ (CPU Cycles)                            | 43  |

| 3.2 | Candidate Operation Costs                                          | 44  |

| 3.3 | Change in Cross-Entropy Loss w.r.t. Compute Cost                   | 47  |

| 3.4 | Performance Evaluation Of DEff-ARTS                                | 57  |

| 4.1 | Deployment Statistics of state-of-the-art CNNs                     | 65  |

| 4.2 | Specifications of Commercial Cortex-M Based Platforms              | 66  |

| 4.3 | Effect of Scaling Width and Resolution on Memory Requirement       | 67  |

| 4.4 | Sizes of Fast Buffers Used in TinyOps Overlaying Strategy          | 73  |

| 4.5 | Power Consumption of Memory Configurations and TinyOps             | 83  |

| 4.6 | High Accuracy and Low Inference Latency with TinyOps               | 85  |

| 5.1 | Performance Comparison of Internal Memory and TinyOps Design Space | 98  |

| 5.2 | Static Models Derived for a Range of Latency Constraints           | 110 |

| 5.3 | Compute Cost of Different NAS Approaches                           | 111 |

| Apr | pendix C.1 DEff-ARTS Architectures vs. Manual Width Scaling        | 133 |

### **Declaration of Authorship**

I declare that this thesis and the work presented in it is my own and has been generated by me as the result of my own original research.

#### I confirm that:

- 1. This work was done wholly or mainly while in candidature for a research degree at this University;

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- 3. Where I have consulted the published work of others, this is always clearly attributed;

- 4. Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- 5. I have acknowledged all main sources of help;

- 6. Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- 7. None of this work has been published before submission

| Signed: | Date: |

|---------|-------|

| O       |       |

To my parents,

## **Definitions and Abbreviations**

API Application Programming Interface

CNN Convolutional Neural Network

CPU Central Processing Unit

DMA Direct Memory Access

DNN Deep Neural Network

DSP Digital Signal Processor

DyNN Dynamic Neural Network

EEC Early Exit Classifier

EENN Early Exiting Neural Network

FC Fully Connected

FMC Flexible Memory Controller

GB Gigabyte

GPU Graphical Processing Unit ISR Interrupt Service Routine

IoT Internet of Things

KB Kilobyte

LSTM Long Short Term Memory MAC Multiply and Accumulate

MB Megabyte

MCU Microcontroller

NAS Neural Architecture Search

NN Neural Network

NPU Neural Processing Unit

PB Petabyte

QSPI Quad Serial Port Interface ReLU Rectified Linear Unit

RNN Recurrent Neural Network

SDRAM Synchronous Direct Random Access Memory

SIMD Single Instruction Multiple Data SRAM Static Random Access Memory

TFLM TensorflowLite-Micro TPU Tensor Processing Unit

## Chapter 1

## Introduction

Deep Neural Networks (DNNs) are a class of machine learning models that have recently found success in a variety of applications where there is an abundance of labelled data. The first major example of this can be found with the convolutional neural network (CNN), AlexNet (Krizhevsky et al., 2012), which achieved 10% higher accuracy than the second best entry in the 2012 ImageNet Large Scale Visual Recognition Challenge (ILSVRC) (Russakovsky et al., 2015). In part, this success was due to the usage of Graphical Processing Units, (GPUs), whose highly parallel architecture was well suited for efficient implementation of the Neural Network (NN) workload, composed of large linear algebraic operations (Chetlur et al., 2014; Jorda et al., 2019). The significant gains in performance achieved in ILSVRC 2012 initiated tremendous research effort into development of DNNs for a number of tasks. Since then, a significant amount of progress has been made and a variety of architectures including CNNs (He et al., 2016), AutoEncoders (Bank et al., 2023), LSTMs (Greff et al., 2016), RNNs (Salehinejad et al., 2017) and Transformers (Lin et al., 2022) have been proposed for a number of different tasks including image classification (Deng et al., 2009), natural language understanding (Hinton et al., 2012), machine translation (Vaswani et al., 2017), and gameplay (Silver et al., 2016; Vinyals et al., 2019) amongst others.

A trend that can be observed over the years, is that to achieve better performance across tasks these models have constantly been increasing in size and computational complexity (Villalobos et al., 2022). To keep up with the computational demands of these workloads, increasingly powerful GPUs have been developed over the past decade which offer an order of magnitude higher core count and memory size (Jeon et al., 2021; Dally et al., 2021), in addition to the development of deep learning accelerators such as Tensor Processing Units (TPUs) and Neural Processing Units (NPUs) (Silvano et al., 2023).

At the same time, with the proliferation of mobile phones, smart wearables and other sensor devices, low power Internet of Things (IoT) devices have been increasingly pervading society with recent forecasts estimating that there will be 41.6 billion connected

IoT devices by 2025 (Insights, 2022). Coupled with the success of DNNs there has been tremendous interest, in application of DNNs in areas such as smart cities (Zanella et al., 2014), health monitoring (Zazzaro et al., 2021; Gibbs et al., 2023) and industrial sensing (Khalil et al., 2021). However, the resource constrained IoT devices (Lin et al., 2020; Liberis et al., 2021; Banbury et al., 2021; Fedorov et al., 2022) have significantly different architectures and characteristics compared to traditional GPUs which DNN workloads are typically designed for. Whereas GPUs have GBs of memory, TBs or PBs of storage and thousands of cores for parallel processing, IoT devices which typically host MCUs have memory and storage in the MB range and a singular core for data processing (Lin et al., 2020). Similarly, these devices are often battery powered and deployed in the wild where they must adapt to the environment whilst adhering to real-time latency and energy constraints (Hong et al., 2020; Gog et al., 2022).

These resource constraints make it challenging to run compute and memory intensive DNN workloads onboard the edge device. Due to this, applications of DNNs in the IoT typically rely on the cloud computing paradigm (Samie et al., 2019) which utilises the low power IoT device itself for data collection and preprocessing with the major number crunching and processing being performed on the cloud providing GPU services. However, this is undesirable for a number of reasons including privacy, security, latency and cost associated with cloud based solutions (Premsankar et al., 2018). These limitations of cloud based solutions have lead to the development of the field of TinyML which investigates how data can be processed locally within the resource constraints of the MCU based edge devices. TinyML encompasses a vast array of specialist research looking to optimise the design and deployment of DNNs across a number of dimensions to optimise the accuracy, latency and energy efficiency within the resource constraints of the deployment platforms.

### 1.1 Research Justification

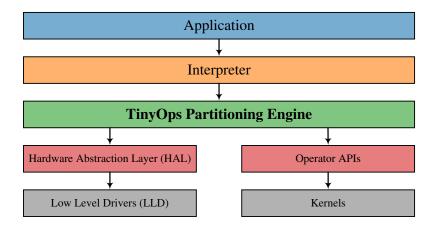

FIGURE 1.1: Inference Components for Deep Neural Networks (DNN)

The research conducted in the field of TinyML or more broadly efficient machine learning can be approximately categorised according to the inference components shown in Figure 1.1. While each of these components can be individually optimised for efficient inference, quite often these components are co-designed with each other. For example, models are often trained with specialised pruning or quantisation-aware training recipes which enables effective model optimisation strategies. In certain cases, such as where there is limited support for low-precision data types or sparse computation,

components can also be removed from the inference stack. We note that the components in inference do not have to be applied in a linear fashion, quite often iterative training methods are used where a feedback loop is established between the optimisation strategy and the training algorithm. Similar loops are often also established between the model deployment and design components. One of the fundamental components in inference is designing the model for a specific task, such as a CNN for an image processing task. Within model design there are two major approaches adopted. The traditional approach adopted for the default GPU platforms was to manually design models by selecting the hyper-parameters of the network such as depth, layer types, kernel sizes, filter sizes, etc to achieve high accuracy while meeting computational or memory constraints (Krizhevsky et al., 2012; Iandola et al., 2017; Sandler et al., 2018; Howard et al., 2017). These works rely on different heuristics for design of models and explore the trade-off between different dimensions of the model such as accuracy, latency, complexity and memory footprint. However, the applicability of these heuristics can vary depending on the underlying platform which often make a model designed for one platform unsuitable for deployment on another (Cai et al., 2020; Dudziak et al., 2020). As edge devices have such different characteristics, there is a need for study of the devices to derive efficient heuristics for the model design process.

A limitation of the manual approach to model design is that it is an involved, time consuming and costly process due to hit and trial involved in developing and trying different heuristics. Additionally, it requires expert human knowledge to apply these heuristics in the design process which is not always available. To alleviate these limitations, Neural Architecture Search (NAS) was proposed to automate the design of DNNs without human intervention in the process. These works (Zoph and Le, 2017; Liu et al., 2018; Real et al., 2019; Tan et al., 2019) utilise reinforcement learning, evolutionary optimisation or gradient based search to derive architectures from a given search space. However, these works focus on deriving the architectures with the highest performing accuracy from the search space. To meet complexity requirements, these models use manual heuristics to simplify a model derived from the search space (Cai et al., 2018; Tan et al., 2019) or simplify the entire search space (Wu et al., 2019). For battery powered edge devices, an accuracy-complexity trade-off is often required as these devices must be able to adapt to changing latency, compute and energy constraints (Xu et al., 2019; Hong et al., 2020; Navardi and Mohsenin, 2023). For such scenarios, it would be desirable to have efficient methods that can explore the accuracy and complexity trade-off in an automated manner. Such approaches would also benefit by using heuristics used in manual model design to inform search space design.

The model deployment scenario is closely related to the model design as the actual performance achieved by any given model depends on the characteristics of target hardware platforms and the ability of the inference framework to leverage the compute capability of the hardware. The field of TinyML typically considers platforms with less than 1W power consumption due to the deployment scenarios where the battery operated devices are energy constrained. DSPs and MCUs are good candidate platforms in the field due to their energy efficiency and instruction sets which support multiply, add or multiply accumulate operations frequently encountered in DNN workloads.

MLOps tools play a crucial role in development and deployment of large models in TinyML. These tools enable efficient management of different stages of the machine learning (ML) life-cycle including training, optimisation and inference in a collaborative, scalable and compliant manner. During training, they handle data versioning, experiment tracking, distributed resource orchestration, and monitoring, allowing teams to efficiently train massive models across multiple GPUs or nodes. For inference, MLOps platforms enable seamless and optimised model deployment with efficient inference frameworks, and monitor production models for drift or performance degradation. By integrating these capabilities into cohesive pipelines, MLOps reduces manual overhead, minimizes errors, and accelerates the end-to-end machine learning lifecycle. In the field of TinyML, the inference framework provides a light-weight run-time environment suitable for resource constrained edge devices that is typically responsible for loading a model, memory management, interpreting the inference graph, and lowlevel kernels which perform primitive operations (e.g. conv, matmul, add) by interfacing with the hardware through the instruction set. As such, it is important to optimise the performance of the inference framework to enable high throughput inference. Prior work to optimise inference in deployment has focused on generating light-weight code (Lin et al., 2020, 2021, 2022), developing efficient kernels (Lai et al., 2018; Rusci et al., 2018, 2020a) and graph optimisations (Liberis and Lane, 2020, 2022) to lower the memory footprint and latency of deployment. These approaches allow a larger model to be deployed within a smaller memory footprint to achieve higher accuracy and lower latency. While these approaches have been successful to varying degrees, a limitation of these works is that they assume a simplified architecture of the devices which consists of a CPU Core coupled with internal storage and memory. This assumption limits the size of the model design space and the achievable performance. On edge devices, where resources are already limited, it would be beneficial to develop inference frameworks that efficiently utilise the available resources such as external memory interfaces to extract the maximum performance from the devices.

### 1.2 Research Questions

Following the research justifications, in the work carried out in this research we look at how efficient inference across the accuracy complexity pareto frontier can be performed on edge devices. To study this we look at optimisations across the inference stack to enable efficient model design and deployment. The research addresses four main research questions

## RQ1. How can we derive models of varying complexity using automated methods according to varying requirements?

Several approaches have been proposed to derive models in an automated manner using the framework of Neural Architecture Search (NAS). However, prior works focused on deriving models with the highest accuracy and using manual heuristics to modify the models to meet complexity requirements. This research question aims to investigate how we can derive models across the accuracy-complexity pareto frontier directly from the search space without any manual intervention in the process. This question is addressed in Chapter 3 and Chapter 5.

- **RQ2.** How can inference software efficiently utilise external memories to enable design and deployment of efficient models? The majority of prior works have focused on designing models within the constraints of internal storage and memory on the device which limits the achievable performance. In this question we investigate how external memory interfaces available on the platform can be effectively utilised by inference frameworks to expand the design space of efficient DNNs on MCUs and achieve better performance. This question is addressed in Chapter 4.

- RQ3. What model design heuristics can we draw from study and analysis of DNN deployment on edge devices at the micro-architecture level to inform efficient model and search space design? The design of models using manual or automated search involves using heuristics to design either the search space for automated methods or the model definition itself for manual methods. While prior works have studied the computational complexity of DNNs at a model level granularity or for different hardware platforms, this research question focuses on performing an in-depth analysis of DNN deployment on MCUs at the micro-architecture level. This is addressed in Chapter 5.

- **RQ4.** How can we adapt inference at run-time to efficiently trade-off between accuracy and latency on edge devices? Edge devices have to adhere to real-time latency constraints in order to meet deadlines imposed by the application or environment. In the research question, we study how an application can efficiently trade-off the accuracy of the model with latency at run-time to meet latency constraints varying in real-time. This research question is addressed in Chapter 5.

#### 1.3 Research Contributions

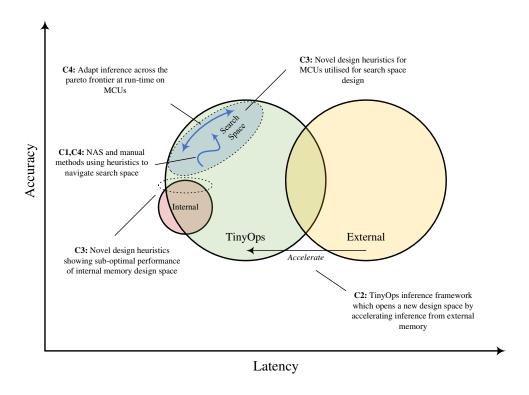

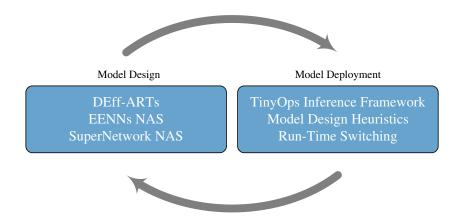

In addressing the research questions the major contributions made in this thesis are visualised in Figure 1.2. The contributions listed below make optimisations across the

FIGURE 1.2: Overview of Research Contributions

inference stack including design of efficient models and inference software to achieve high performance on the accuracy-latency pareto frontier.

## C1. An efficient gradient based search algorithm to automatically derive models of varying complexity.

While prior works utilised automated neural architecture search to derive architectures with high accuracy, we reframe the problem as a multi-objective optimisation problem to trade-off the accuracy and complexity. We formulated a closed form differentiable expression for the computational complexity of candidate models in the search space and successfully navigate the search space via gradient descent to derive models of varying complexity where the trade-off was controlled by a single hyper-parameter. This work directly addresses **RQ1** in Chapter 3 and was published in the Neural Information Processing and Systems (NeurIPS) Machine Learning for Systems workshop (Sadiq et al., 2020).

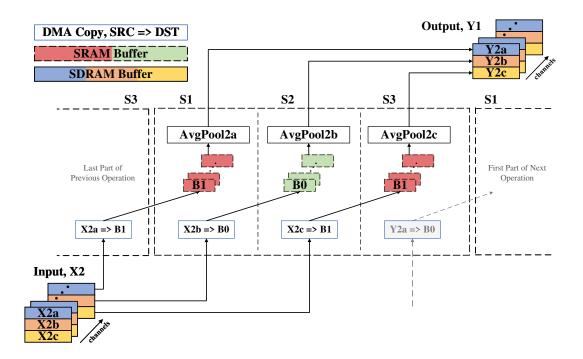

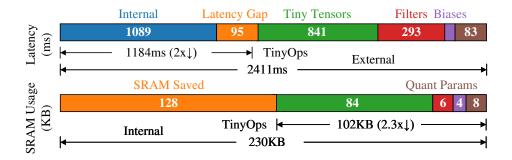

C2. The TinyOps inference framework that effectively utilises external memories on MCUs to open a new efficient design space for MCUs and speed up inference of large models in external memory by up to 2.5x to set the state of the art in TinyML ImageNet classification.

We study MCU architectures and analysed their capabilities in addition to how

current inference frameworks deploy DNNs onto MCUs. We highlight the limitations of using external memories with current inference frameworks and propose a partitioning and DMA based overlaying framework for MCU devices that combines advantages of external memory (size) and internal memory (speed) to open a new design space for MCUs which achieves state of the art ImageNet classification accuracy in TinyML. This work is reported in Chapter 4 and addresses **RQ2**. Initial findings were published at the Computer Vision and Pattern Recognition (CVPR), Efficient Computer Vision (ECV) workshop (Sadiq et al., 2022), and with incremental improvements in the IEEE Internet of Things Journal (IoTJ) (Sadiq et al., 2023). Additionally, this work was granted a US Patent (Sadiq et al., 2024) filed in collaboration with the industrial partner for this project, ARM.

C3. We derive novel design heuristics which are utilised to design efficient CNNs across the accuracy-latency pareto frontier on MCUs which achieve state-of-the-art ImageNet performance.

We performed an in-depth analysis of DNN deployment on MCUs at the micro-architecture level to derive heuristics and insights into model design for MCUs. We show that the internal memory design space used by prior works yields sub-optimal accuracy and latency. Further, we study the structure of state of the art models and throughput of low-level candidate operations (Conv, DepConv) to motivate model design for MCUs. Using insights from our latency analysis, we use efficient operations to derive models across the accuracy-latency pareto frontier to set the state-of-the-art in ImageNet classification. This work discussed in Chapter 5, addresses RQ3 with contributions published in IEEE IoTJ (Sadiq et al., 2023).

C4. We propose a supernetwork based neural architecture search method to derive models of varying complexity and an efficient framework to deploy and switch between the models based on latency constraints in real-time with zero switching overhead.

We propose a framework for how an accuracy-latency trade-off can be realised on MCUs for applications with real-time and varying latency constraints. We propose a light-weight super-network based NAS architecture with the search space motivated by our analysis in Chapter 5. We derive multiple models for a number of latency constraints and show that accuracy-latency trade-off can be achieved with zero-switching time at run-time using the TinyOps inference framework developed in Chapter 4. This work addresses **RQ4** and is reported in Chapter 5.

## 1.4 Research Output

The research described in this thesis appears in the following publications

- Sulaiman Sadiq, Partha Maji, Jonathan Hare, and Geoff Merrett. DEff-Arts: Differentiable Efficient Architecture Search. In Neural Information Processing Systems Workshop on Machine Learning for Systems, 2020

- Sulaiman Sadiq, Jonathon Hare, Partha Maji, Simon Craske, and Geoff Merrett.

Tinyops: Imagenet scale deep learning on microcontrollers. In *Proceedings of the IEEE Conference on Computer Vision and Pattern Recognition Workshop on Efficient Deep Learning for Computer Vision*, 2022

- Sulaiman Sadiq, Jonathon Hare, Simon Craske, Partha Maji, and Geoff Merrett.

Enabling ImageNet-scale deep learning on MCUs for accurate and efficient inference. In IEEE Internet of Things Journal, 2023

Part of the research performed in this thesis was also granted a US patent, which was filed in collaboration with the industrial partner for this research, ARM Ltd.

Sulaiman Sadiq, Jonathon Hare, Geoff Merrett, Partha Maji and Simon Craske.

Neural Network Memory Configuration. US Patent App. 17/813,396, 2024

#### 1.5 Thesis Outline

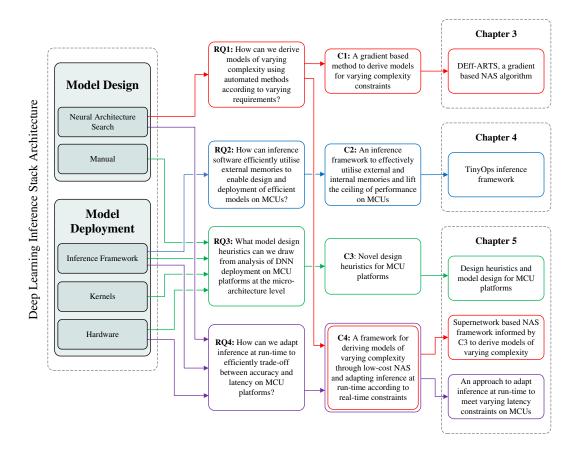

An overview of the research carried out in this thesis is shown in Figure 1.3. As shown, we make a number of contributions to the components of the inference stack involving efficient model design and deployment. The diagram also indicates which inference component each of the research questions (RQ1-4) and corresponding contributions are related to. A mapping of the contributions to each of the chapters is also shown. The remainder of this thesis is organised as follows

Chapter 2 begins by providing relevant background on design and deployment of CNNs. This includes model design through manual and automated methods, model optimisation techniques in addition to an overview of the hardware and inference frameworks used in deployment of the models. The limitations of the approaches adopted are also discussed.

Chapter 3 focused on efficient model design using automated methods and explores how we can derive models of varying complexity using gradient based NAS. We desribe DEff-ARTS, which utilises the machinery of DARTS (Liu et al., 2019) discussed in Section 2.2.1.3, to derive architectures of varying complexity. We describe our formulation of the problem as a multi-objective optimisation problem and how we combine the sub-objectives to derive models in an automated manner. This is followed by experimental evaluation of the proposed NAS algorithm.

1.5. Thesis Outline 9

FIGURE 1.3: Overview of Thesis Structure with RQ1-4 representing research questions and C1-4 representing contributions of the research

Chapter 4 presents the TinyOps framework developed to enable efficient model deployment on MCU platforms. We discuss the limitations of prior inference frameworks which do not effectively utilise the memory hierarchy and how this limits the performance achievable on MCU platforms. We describe how TinyOps employs a partitioning and overlaying scheme to combine the advantages of size and speed of external and internal memory. This is followed by experimental results to demonstrate how TinyOps lifts the ceiling of performance achievable on MCU platforms.

Chapter 5 describes our in-depth analysis of DNN deployment on MCU platforms at the micro-architecture level and derives heuristics to design efficient models for varying latency constraints. We show that operation agnostic approaches that focus on designing models within size constraints of fast internal memory suffer from low accuracy and high inference latency. We utilise the derived heuristics to propose a lightweight NAS approach to derive models of varying complexity. We further show how the inference can be adapted at run-time to meet varying real-time latency constraints. Finally, we perform experimental results to demonstrate the performance gained by using the design heuristics to derive models.

Finally, Chapter 6 concludes the thesis by summarising the contributions made by the work carried out in this thesis. Further, we discuss the open research challenges in the field and future avenues of work that can be explored for further performance gains on resource constrained devices.

## **Chapter 2**

## **Background and Related Work**

This chapter provides background and a review of current literature relevant to the work carried out in this thesis. In Section 2.1, we begin by discussing the Convolutional Neural Network (CNN) architecture and its building blocks, used extensively in deep learning for image processing and throughout this thesis. This is followed by prior work into efficient model design including static and dynamic neural networks derived through manual or automated methods in Section 5.1. In this section, we delve into deeper detail of the DARTS (Liu et al., 2018) algorithm, as we utilise this approach in Chapter 3. Next, in Section 2.3, we discuss approaches that are utilised in optimising a given model for deployment including pruning and quantisation approaches. We provide deeper detail for linear quantisation schemes as these are used on MCUs and are utilised in Chapter 4 and Chapter 5. Finally, in Section 2.4, we discuss the characteristics of the hardware considered in this thesis, in addition to the inference frameworks and kernels used for the hardware platforms.

#### 2.1 Convolutional Neural Networks

A number of different DNN architectures have been proposed for a variety of tasks. In this thesis, we focus on CNN architectures which are widely used for image based tasks including image classification, object detection and segmentation. A multi-layered CNN model sequentially performs operations on an input to produce an output representation. These operations are typically parametrised by some weights that can be learned by training the neural network. The operations that are typically used in constructing a neural network include operations such as convolutions, depthwise-separable convolutions, fully connected layers and activation functions. In a multi-layered model, these operations are also referred to as layers of the model.

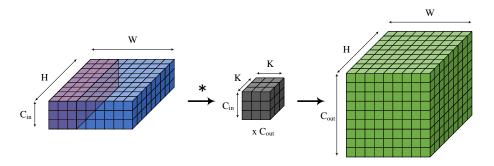

### 2.1.1 Convolutional Layers

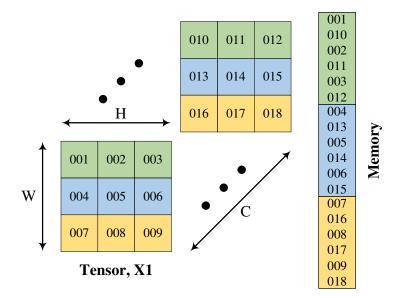

One of the main building blocks of CNNs is the convolution layer. These layers are applied to an input representation of size  $N \times H \times W \times C_{in}$ , where N is the batch size, and H, W and C are the height, width and number of channels of the representation. To apply a convolution layer to an intermediate representation, a filter of size  $K \times K$  with  $C_{in}$  input channels is convolved with the input representation as shown in Figure 2.1 to produce one output channel of the output representation. To produce an output representation with  $C_{out}$  channels,  $C_{out}$  filters are applied to the input representation. The resulting output representations of convolving  $C_{out}$  filters with the input representation are then concatenated together to produce the complete output representation with dimensions  $N \times H \times W \times C_{out}$ .

FIGURE 2.1: Convolution Layer

Convolutions are compute intensive operations where the computation can be calculated as below  $(K^2) \times C_{in} \times H_{out} \times W_{out} \times C_{out}$ . Similarly, the parameters in a convolution layer can be noted as  $(K^2) \times C_{in} \times C_{out}$ .

### 2.1.2 Depthwise Separable Convolutions

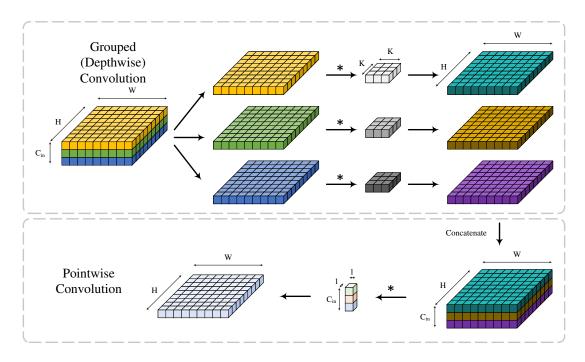

Depth-wise separable convolutions were proposed as a light-weight alternative to convolution operations. Depth-wise separable convolutions are applied in two stages where the first stage is a grouped convolution and the second part is a pointwise convolution.

**Grouped and Depthwise Convolution** In a grouped convolution the channels of a filter and input representation are separated into multiple groups where each group is performed as a regular convolution with the outputs being concatenated together in the channel dimension. A common approach employed is to have as many groups as there are channels in the filter or input representation and set the channels in the output equal to the number of groups. In this specific case, referred to as depthwise convolutions, each of the  $C_{in}$  channels of the input representation is independently

convolved with a  $K \times K$  kernel with the resulting outputs being concatenated together to produce an output with  $C_{out} = C_{in}$  channels as shown in Figure 2.2

The computation performed by a depthwise convolution can be computed as  $K^2 \times H_{out} \times W_{out} \times C_{in}$  with the parameters equal to  $K^2 \times C_{in}$ .

**Pointwise Convolution** A pointwise convolution is then applied to project the representation to the number of output channels,  $C_{out}$ . This is performed as a regular convolution with  $C_{out}$  filters which have unit kernel size. In this stage the computation and number of parameters can be calculated as  $H \times W \times C_{in} \times C_{out}$  and  $C_{in} \times C_{out}$  respectively. The application of a depth-wise separable convolution consisting of a grouped convolution followed by a pointwise convolution is shown in Figure 2.2.

FIGURE 2.2: Depthwise Separable Convolution. Adapted from Pandey (2024).

In total the computation for a depth-wise separable convolution comes out to be  $K^2 \times H_{out} \times W_{out} \times C_{in} + H \times W \times C_{in} \times C_{out}$  with the parameters equal to  $K^2 \times C_{in} + C_{in} \times C_{out}$ . Depthwise separable convolution are more parameter and compute efficient compared to vanilla convolutions.

## 2.2 Model Design

A number of approaches have been adopted to design efficient CNNs. These approaches aim to optimise the *quality* and *efficiency* of a model. The quality of a model would be indicated by the predictive performance of the model and measured with

metrics such as the accuracy, precision, recall. The efficiency would include metrics such as the parameter count, memory usage, computational complexity or latency. For any application, a practitioner would want the quality to be as high as possible for the best predictions. On the other hand, deployment on edge devices requires models to be designed within certain constraints of the hardware or application such as the memory or latency which requires increasing the efficiency of the model.

In practice, these two objectives to be optimised in CNN design are often conflicting and optimising one usually results in degradation of the other. As such, the objective of model design becomes to find a model that is pareto optimal when considering our quality and efficiency metrics. For applications that need to meet varying complexity constraints, the pareto frontier can be traversed using static or dynamic approaches.

#### 2.2.1 Static Neural Networks

Static Neural Networks have a fixed structure and weights during inference and would represent a single point on the pareto frontier. Meeting multiple latency constraints in this manner requires designing multiple models according to requirements.

#### 2.2.1.1 Manual Design

The traditional approach to developing efficient models relied on using manual heuristics to reduce the size and computational complexity. Szegedy et al. (2015) modified the number of filters, kernel sizes and depth via hit and trial to reduce the latency of inference while retaining accuracy. Iandola et al. (2017) developed CNNs which extensively utilised  $1 \times 1$  convolutions to reduce the parameter count of CNNs. Similarly, groupwise convolutions and depth-wise separable convolutions have been utilised in the design of CNNs to reduce the parameters and computational complexity (Zhang et al., 2018; Sandler et al., 2018; Howard et al., 2019). Howard et al. (2017), further proposed using two global hyper-parameters, a width and resolution multiplier to reduce the input image size and channels in convolution layers for a reduction in model size and complexity. Tan and Le (2019) added depth as an extra hyper-parameter and proposed a compound scaling rule to uniformly scale width, resolution and depth according to resource budgets. We note that these approaches often develop heuristics in a platform agnostic manner, or for more popular platforms such as mobiles or GPUs which would not necessarily carry over to MCUs. A limitation with manually designing models is the requirement of human-expert knowledge in selecting the various hyper-parameters of the model. Additionally, the hit and trial involved is a tedious process that requires significant compute resources.

#### 2.2.1.2 Neural Architecture Search

Neural Architecture Search (NAS) has emerged as a promising direction to bypass the challenges of manually designing models. NAS approaches remove the human out of the loop and automate the hit and trial process of sampling, evaluating and deriving architectures. A NAS algorithm is typically built from three main components which are the search space, the objective to maximise and the search method. Combining the three, models are derived by navigating the search space with a given method and finding the model that maximises the objective.

**Search Space:** The search space is defined to contain all the candidate architectures that could be evaluated during the search process. The size of the search space is defined by the degrees of freedom that are available in the model structure being derived. This would include the type of layer, hyper-parameters (e.g. channels, kernel size, stride) and the connectivity between layers.

In an extreme case, the most flexible search space could be represented as an arbitrary number of nodes in a graph which were freely assigned any layer type and connectivity. However, this would yield an extremely large search space that would be difficult to navigate.

As such, the majority of works constrain the search space using heuristics derived from manual design of models. A common method adopted is for the search space to resemble manually derived models (Cai et al., 2018, 2020; Banbury et al., 2021). In these cases, the search space can be seen as mutations to the base model architecture, which can modify the channel numbers, or kernel sizes but not the layer types. We note that the heuristics utilised in designing the search space are typically derived in a platform agnostic manner or for mobile or GPU platforms (Howard et al., 2019; Lin et al., 2020; Banbury et al., 2021).

Another commonly adopted approach is to search for the architecture of smaller blocks or *cells* (Shu et al., 2020; Ying et al., 2019; Mellor et al., 2021). This reduces the size of the search space to make the process tractable. After a cell has been derived, it is then stacked a number of times to produce a final model.

**Search Method:** The hit and trial approach of manually designing models can be thought of as manually traversing the search space guided by heuristics applied from human knowledge of CNNs. This process is automated in NAS algorithms as an optimisation problem where the architecture is derived from the search space by maximising an objective.

Gradient based optimisation is a commonly used approach (Liu et al., 2018; Cai et al., 2018; Xie et al., 2019; Xu et al., 2020) which employs a differentiable relaxation over the categorical selection of candidate operations to jointly learn the architecture and its weights.

Reinforcement Learning has also been used where a controller is trained to emit an architecture configuration using the objective as a reward signal (Zoph and Le, 2017; Zoph et al., 2018; Pham et al., 2018).

Similarly, evolutionary optimisation has been adopted where the architecture is represented as a genotype in a population (Real et al., 2017, 2019; Sun et al., 2019). During the search, each candidate in the population is trained and evaluated against the fitness criteria after which the next generation of candidates can be produced using a selection strategy such as tournament selection (Blickle, 2000).

**Objective:** The earlier approaches in NAS typically only optimised the quality metric of accuracy or the differentiable cross-entropy loss (Liu et al., 2018; Zoph et al., 2018; Real et al., 2019) in the search. While these approaches, were able to derive architectures with competitive accuracy, they typically suffered from high computational complexity as the objective did not account for the efficiency of the architecture. Subsequent works proposed to optimise the complexity of the architectures in addition to its predictive quality to derive efficient models. These approaches achieve the same accuracy with lower complexity as the objective is able to differentiate between models in the search space with the same quality but different efficiency.

However, these approaches do not explore an accuracy latency trade-off in an automated manner. After deriving a performant base model, these approaches typically scale the depth, width or input resolution of the model to meet varying efficiency requirements of applications (Tan et al., 2019; Wu et al., 2019; Cai et al., 2018). Later works dealt with this shortcoming by optimising the efficiency to search for models across the pareto frontier (Cai et al., 2020; Banbury et al., 2021).

Specialist works in TinyML quite often include the memory usage and model size in the objective to fit models within internal storage and memory constraints (Fedorov et al., 2019; Lin et al., 2020, 2021; Banbury et al., 2021; Liberis et al., 2021; Fedorov et al., 2022).

**Approximations:** The quality of the candidate model would ideally be measured as the accuracy of the trained model on the validation data. However, training sampled candidate models to completion in the search process becomes prohibitively expensive with such approaches requiring up to 40,000 GPU hours (Real et al., 2017; Zoph et al.,

2018; Cai et al., 2020). To alleviate this, search algorithms often take approximations to reduce the computational cost.

A common approach adopted is to train the candidate architectures for a limited number of epochs with shared weights to reduce training time (Pham et al., 2018). Similarly, the search is often carried out using lower input resolutions or on a smaller proxy dataset, with the model then being transferred to larger datasets (Zoph et al., 2018; Real et al., 2019; Lin et al., 2020). To avoid the computational cost of evaluating numerous candidate models on the validation dataset which can also be quite large, accuracy predictors are also utilised for evaluating models (Cai et al., 2020; Dudziak et al., 2020).

In a similar manner, the computational complexity is also often estimated using the MACs or latency predictors (Cai et al., 2020; Dudziak et al., 2020) as measuring ondevice latency for all target platforms and large search spaces with upto  $1.15 \times 10^{152}$  candidate architectures (Liberis et al., 2021) can become infeasible.

Early works in NAS typically jointly trained and navigated the search space to derive a model (Zoph et al., 2018; Cai et al., 2018; Real et al., 2019; Lin et al., 2020). This approach had the limitation that a single search required training the entire search space and deriving multiple models required training the search space from scratch.

To address this challenge, super-network based approaches have been used where the training of the search space, *i.e.* the super-network, is decoupled from the search (Cai et al., 2020; Wang et al., 2021a,b). In these approaches, a super-network is initialised which contains all the candidate architectures. The super-network is first trained with a specialised training strategy that trains candidate architectures. Once the training is complete, the search can be carried out, according to some objective with a low cost, as it only consists of sampling and evaluating models. Importantly, if the objective changes, the search can be performed on the super-networks without the need for any retraining in the search space. Such approaches often require specialised training recipes as training a large number of candidate architectures with shared weights results in interference between between the models.

#### 2.2.1.3 Differentiable Architecture Search (DARTS)

Differentiable Architecture Search utilises a gradient based approach to navigate the search space of architectures. This is done by employing a differentiable relaxation of the categorical selection of candidate architectures in the search space (Liu et al., 2018; Cai et al., 2018; Shin et al., 2018; Xie et al., 2019). This can be achieved through a Softmax or Gumbel-Softmax distribution over some architecture parameters. The target criterion, such as the validation loss can then be minimised with respect to the architecture parameters that parameterise the distribution over the architecture enabling the automatic discovery of architectures.

In the work carried out in this thesis, we build on the approach of DARTS (Liu et al., 2018). One of the limitations of their work was that they derive architectures that achieved the highest accuracy. In our work, we derive models of varying complexity in an automated manner from the search space in Chapter 3 by jointly optimising the predictive performance and complexity of the architectures. As we build on the machinery of DARTS, we go through the details of the original work in this section.

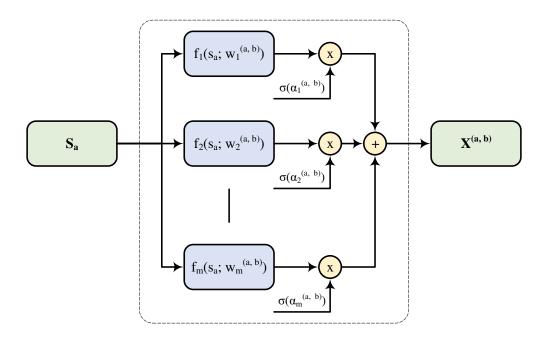

**Continuous Relaxation** In DARTS, the authors replace the categorical selection of an operation to a softmax distribution over all possible candidate operations. This approach combines the candidate operations to form a *mixed operation*. For a set of candidate operations ' $\mathcal{F}$ ' (e.g depth-wise separable convolutions, max pooling, skip connection), each candidate operation, j would be defined as a function of the form  $f_j(s_a; w_j)$ , parameterised by weights,  $w_j$  and applied to input  $s_a$ . The candidate operations in  $\mathcal{F}$  were then combined in a mixed operation,  $m_0$  to produce output,  $x^{(a,b)}$  as shown below

$$x^{(a,b)} = m_0\left(s_a; w_{0,j}, \alpha_{0,j}\right), \qquad \forall j \in \mathcal{F}$$

(2.1)

$$= \sum_{j \in \mathcal{F}} \sigma\left(\alpha_{0,j}\right) \times f_j\left(s_a; w_{0,j}\right) \tag{2.2}$$

$$x^{(a,b)} = \sum_{j \in \mathcal{F}} \frac{\exp\left(\alpha_{0,j}\right)}{\sum_{j' \in \mathcal{F}} \exp\left(\alpha_{0,j'}\right)} \times f_j\left(s_a; w_{0,j}\right)$$

(2.3)

where  $\alpha_{0,j}$ ,  $j \in \mathcal{F}$  is the architecture weight for the jth candidate operation in the 0th mixed operation and  $w_{0,j}$  are the weights that parameterise the jth candidate operation in the the 0th mixed operation. Note that if the mixed operation,  $m_0$  combined 'q' operations together, the architecture weights between representations  $s_a$  and  $x^{(a,b)}$  would be a q-dimensional vector,  $\vec{\alpha}_0$ . The working of a mixed operation that applies the mentioned transformation from  $s_a$  to  $x^{(a,b)}$  is also shown visually in Figure 2.3. As can be seen from Figure 2.3,  $x^{(a,b)}$  would be a weighted average of the outputs of the candidate operations due to the softmax operation on the architecture weights,  $\alpha_{0,j}$ ,  $\forall j \in \mathcal{F}$ .

It is important to note that every mixed operation on the input  $s_a$  would have its own architecture weight vector. For example, a second mixed operation,  $m_1(s_a; w_{1,j}, \alpha_{1,j}), \forall j \in \mathcal{F}$  performed on  $s_a$  to produce representation  $x^{(a,c)}$ , would have its own distinct architecture weights,  $\alpha_{i,j}, \forall j \in \mathcal{F}$ . In the DARTS algorithm, the magnitude of the architecture weight is used as a proxy for a candidate operations importance since it would be large for an operation that contributed more to the output representation,  $x^{(a,b)}$ . In the coming sections we detail how the mixed operations are grouped together into 'cells' which were stacked together to form more complex networks. We also show how the

Figure 2.3: Structure of a Mixed Operation applied to a representation,  $s_a$  to produce an output  $x^{(a,b)}$

magnitude of the softmax of the weights is used to select the best candidate operation and derive discrete cells.

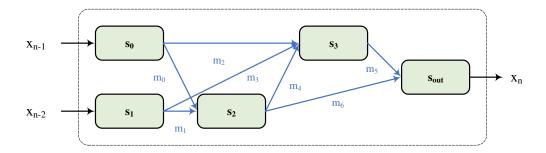

**Cell Structure** The search space for more complex networks is created by combining a number of mixed operations in a 'cell'. In the DARTS algorithm, the architecture search process actually comprises of searching for cells. More complex networks are created by stacking the discovered cells to a user specified depth which would depend on the complexity of the target task for which the network was being derived. This was done to keep the architecture search process tractable since the search space when searching for an entire network would be too large.

FIGURE 2.4: Structure of a 2-step Cell composed of 5 Mixed Operations

The structure of an N-step cell used in the DARTS approach is shown in Figure 2.4 where cell,  $C_n$  is a directed acyclic graph of an ordered sequence of N nodes discounting the output and two input nodes. An N-step cell,  $C_n$  would have N nodes where each node,  $s_k$  in the nth cell represents an intermediate representation (e.g. a feature map in a convolutional neural network). In the graph each node,  $s_k$  is connected to each of its predecessor nodes,  $s_i$  through an edge representing a mixed operation. The representations,  $s_k$  are then produced by carrying out mixed operations on each of the predecessor representations,  $s_i$  which are all concatenated together to produce,  $s_k$ . The output of the cell is then computed by concatenating all the intermediate representations in the cell except for the input representations in the cell. The concatenation operations are carried out in the channel dimension of the representations. The intermediate representations or output representation of an N-step cell are computed according to Eq. 2.4 and 2.5 respectively where  $\prod$  denotes the concatenation operation and  $P_k$  denotes the set of predecessor representations for any representation,  $s_k$ .

$$s_{k} = \prod_{i \in P_{k}} m_{i} \left( s_{i}; w_{i,j}, \alpha_{i,j} \right), \qquad \forall j \in \mathcal{F}$$

$$\underline{N}$$

(2.4)

$$s_{out} = \prod_{k=2}^{N} s_k \tag{2.5}$$

In the DARTS cell structure, the two input representations,  $s_0$  and  $s_1$  are passed in from the output of cells,  $C_{n-2}$  and  $C_{n-1}$  respectively with some pre-processing performed on them. One thing to note is that the numerous concatenation operations leads to the size of feature maps blowing up in deeper parts of the network. As concatenation is carried out in the channels dimension this results in larger filter sizes and more computational overhead. We discuss how DARTS deals with this issue through pre-processing and size reduction methods in the next section where we discuss how cells are stacked together to form more complex networks.

To control the complexity and representational capacity of a cell, the DARTS algorithm allows two degrees of freedom which are treated as hyper-parameters set according to the complexity of the task for which the architecture was being searched. The first hyper-parameter is the number of candidate operations used to produce a mixed operation. The second is the number of steps in the cell. As mentioned previously, the step size determines the number of intermediate representations within the cell which are connected by mixed operations in order to find the best operation during the architecture search process. For a step size of N > 0 the number of mixed operations required to connect each representation node to its predecessors could be simply calculated as shown in Eq. 2.6.

$$p = \sum_{i=2}^{N+1} (i) \tag{2.6}$$

If each of these p mixed operations had  $q = |\mathcal{F}|$  candidate operations the architecture weights for a cell would be contained in a  $p \times q$  matrix. Throughout the rest of this report we denote the architecture weight matrix as  $\alpha$ . In the notation we use from here on,  $\alpha_{i,j}$  can be understood to be the weight for the jth candidate operation in the ith mixed operation of a cell.

In their implementation the authors included the following 7 candidate operations in  $\mathcal{F}$ : 'Skip Connection', '3 × 3 Average Pooling', '3 × 3 Max Pooling', '3 × 3 and 5 × 5 Separable Convolutions' and '3 × 3 and 5 × 5 Dilated Separable Convolutions'. The authors used the Conv-BatchNorm-ReLU processing order for convolution operations in order to stabilise the training process similar to Zoph and Le (2017) and Real et al. (2017). Similarly, all 3 × 3 and 5 × 5 separable convolutions were applied twice and dilated convolutions were always applied with a dilation of 2. To keep the spatial resolution of output representations of candidate operations the same, padding was carried out where necessary.

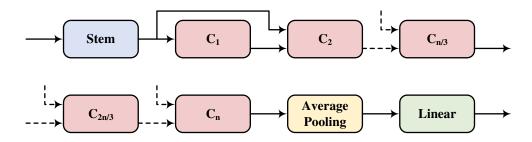

**Network Structure** A network is created by stacking together multiple cells to the depth required. This is shown in Figure 2.5 where each cell,  $C_n$  has two inputs, which are the output of cells,  $C_{n-1}$  and  $C_{n-2}$ , except for the first cell where the input is simply fed in twice. The depth of the network is treated as a hyper-parameter dictated by the difficulty of the task to be learned.

FIGURE 2.5: Structure of Network Composed by Stacking Together Multiple Cells

As mentioned previously, the output representation of a cell was obtained by concatenating all the intermediate representations in the cell (excluding the input feature maps). With cells being consecutively stacked together the representations would become very large due to the successive concatenation operations. To deal with this problem, reduction cells are deployed in the network. In the reduction cells, the operations performed on the input representations are performed with a stride of two. Additionally the pre-processing performed on the input representations of the cell is carried out differently. For normal cells the pre-processing is carried out as a Conv-BatchNorm-ReLU operation with stride 1, while for reduction cells it is applied with a stride of 2.

This approach requires searching for two cells, a normal cell and a reduction cell. In DARTS the cells,  $C_{n/3}$  and  $C_{2n/3}$  at 1/3rd and 2/3rd of the depth of a network with n cells were designated as reduction cells.

When searching for cells, the architecture weights for mixed operations between two representations are shared between cells. However, the weights that parameterised the candidate operations within the mixed operations in each cell are distinct. This is true for both normal and reduction cells. So the process of architecture search requires finding the best architecture weights,  $\alpha^{normal}$  and  $\alpha^{reduce}$  for normal and reduction cells which was used to create a complex network.

Coming back to the network structure, the authors employ a stem processing block which consists of a Conv-RELU operation which controls the number of channels that are input to the first cell. At the end of the network an adaptive average pooling layer is placed to reduce the size of the output representation of cell,  $C_n$  before it is fed to the final linear layer.

**Deriving Discrete Architectures** By searching for architectures for a number of epochs the architecture weights,  $\alpha^{normal}$  and  $\alpha^{reduce}$  could be obtained. We defer discussion of the training process for architecture search to the next chapter where we discuss our multi-objective formulation of the problem and show its compatibility with the training scheme of the DARTS work.

In order to discretize the architecture, the best candidate operation in a mixed operation between representations  $s_a$  and  $s_b$  is obtained by simply selecting the candidate operation with the largest weight. Once all the mixed operations are discretised to the best operations, the top-k strongest operations that produced a representation were retained with the rest being dropped. In the DARTS algorithm k was chosen as 2, similar to prior works. The structure of the cells derived by the DARTS algorithm is shown in Figure 2.6.

FIGURE 2.6: Cells Discovered by DARTS

# 2.2.2 Dynamic Neural Networks

As opposed to static Neural Networks, Dynamic Neural Networks (DyNNs) are able to adapt their structures and parameters during inference. This allows DyNNs to perform inference more efficiently in addition to enabling the models to adaptively trade-off accuracy and efficiency depending on resource constraints.

#### 2.2.2.1 Dynamic Structure

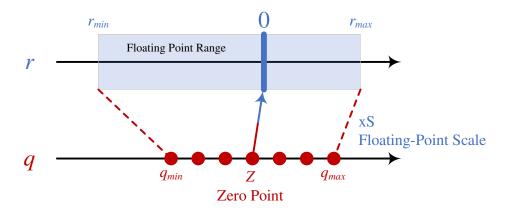

A common approach to realising dynamicism in an NN is to adapt the structure at run-time. According to requirements, a sub-network within the base network can be activated which is used to perform inference. The task of designing the DyNN thus requires designing a network which contains suitable sub-networks which share weights. These approaches leverage the insight that an entire network is not needed to classify all examples. The structure of the sub-networks is typically derived by trimming the base network in three dimensions below