# Towards precise trimming and programming of photonic integrated circuits

April M. Logan, Xia Chen, Xingshi Yu, Weihong Shen, Xingzhao Yan, Weiwei Zhang, Goran Z. Mashanovich, Graham T. Reed, David J. Thomson

Optoelectronics Research Centre, University of Southampton, Southampton SO17 1BJ, UK

aml4g19@soton.ac.uk

Abstract— Methods to achieve a high-resolution phase trimming within silicon waveguides incorporating Ge implanted sections are investigated. The trimming is performed electrically using on-chip microheaters. The average resolution of phase change per voltage pulse achieved by this work was approximately  $0.0007\pi$  radians.

Keywords—programmable, phase trimming, phase tuning, ion implantation, CMOS compatible, post-fabrication trimming

## I. INTRODUCTION

The ability to permanently change the refractive index of regions within silicon photonic circuits after fabrication allows for the production of low power programmable photonic integrated circuits and the trimming of photonic device characteristics. Programmable photonic circuits offer a platform for producing versatile chips in very large volumes (low cost) that can be later programmed for a specific application or function. Trimming of silicon photonic devices can allow for the correction of typical fabrication imperfections that shift the performance of device and circuits, without the need of power-hungry tuning elements. Over the last 15 years we have pioneered a Ge ion implantation and annealing approach to provide this functionality with a number of device demonstrations [1] – [7]. This technique is viable wafer-scale trimming on an industrial scale [8].

When Ge ions are implanted into silicon, they cause lattice disorder, increasing the refractive index of silicon in that region. Increasing the dose of implantation causes a larger change in refractive index until the silicon reaches close to 100% damaged, at which point the silicon has become amorphous. At the point of amorphization, the silicon will have a refractive index of 3.96 [7]. Annealing the amorphous silicon at temperatures over 450°C will begin to recrystallize it, thus the original refractive index of the crystalline silicon (3.48) is recoverable. By partially annealing the Ge implanted silicon using temperatures lower than 600°C [6], it is possible to tune

the effective index that the mode propagating through the implanted waveguide is experiencing to a range of values.

This approach can be used in components such as MZIs (Mach-Zehnder Interferometers), RRs (Ring Resonators) and DCs (Directional Couplers) to create circuits where the routing of optical signals can be permanently tuned after fabrication [7]. The approach is CMOS compatible and after annealing, the Ge implanted region of waveguide will stay at the refractive index it was tuned to, thus components can maintain their state without a requirement for a constant power supply.

Annealing can be carried out with lasers (using a specialised set up) or electrically. In this work, annealing was carried out electrically via the use of microheaters layered over the sections of Ge implanted waveguides. Applying a current to the microheater leads to an increase in temperature of the filament due to Joule heating. This can be carried out post-packaging of the photonic chips, which cannot be done with laser annealing. Electrical annealing also benefits from the ability that multiple Ge implanted sections can be annealed in parallel. For large scale circuits this is ideal as the time taken to program the whole circuit can be reduced.

To accurately trim devices or optimally route the light with minimal loss, it is essential to have high resolution of phase control within each individual component. To provide this resolution, we have developed a method of phase tuning silicon waveguides with Ge implanted regions via short voltage pulses applied across microheaters.

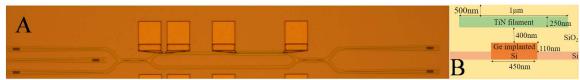

The method has been developed using MZIs as shown in Fig. 1, where one arm has a  $12\mu m$  length of its waveguide implanted with Ge ions with a microheater fabricated over this region. A second microheater also exists to thermally set the MZI to quadrature to allow accurate phase measurement.

# II. ELECTRICAL ANNEALING METHOD AND RESULTS

When electrically annealing the Ge implanted region of the MZIs described above, it has been observed that annealing

Figure 1: a) Microscope image of the MZI design. The two pads on the left are connected to a filament that runs above the Ge implanted section of waveguide. The two pads on the right are connected to filament which is used for thermally tuning the MZI. MMIs are use as splitters and combiners for the two inputs and two outputs respectively. b) A cross-sectional diagram of the implanted section of waveguide.

begins after a power of 35mW is reached and ends at 110mW. Voltage pulses were used for annealing rather than a constant current, firstly to allow examination of the change in optical transmission due to annealing separate from the thermo-optic effect. Secondly, voltage pulses can also provide a higher resolution of phase change than a constant voltage as power will be applied across the microheater for less time.

To trim the devices whilst maintaining a high resolution of phase control, it is necessary to start with a low power being supplied to the microheater, and gradually increase so that higher temperatures can be reached. To do this, a voltage step between successive pulses was used. Various approaches were investigated into how much the voltage should set up between successive pulses. It was found that the most effective method was to change the size of the voltage step depending on the phase change brought about by previous voltage pulses. The different ranges of phase change used to dictate the voltage step are shown in Table 1 alongside the corresponding step used.

TABLE I. PHASE DEPENDANT VOLTAGE STEPS

| Average phase change from previous three pulses, Δφ (radians) | Next voltage step |

|---------------------------------------------------------------|-------------------|

| $\Delta \phi > 0.012$                                         | -1.2mV            |

| $0.012 > \Delta \varphi > 0.006$                              | 0mV               |

| $0.006 > \Delta \varphi > 0.001$                              | 0.6mV             |

| $0.001 > \Delta \varphi$                                      | 10mV              |

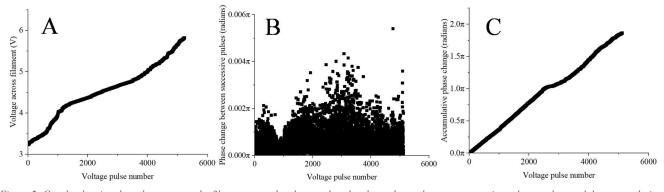

A step of 0.6mV was the smallest voltage step possible with the equipment being used in this experiment. To further increase the resolution when annealing, electrical resistors were put in series with the microheater used for annealing. The microheater had a resistance of approximately  $280\Omega$ , and the resistors had a combined resistance measured as  $438\Omega$ . This meant the filament of the microheater was being provided with approximately 40% of the voltage pulse. Fig. 2a shows the voltage measured over the filament of the microheater at each pulse.

Fig. 2b shows for each pulse the amount a phase change produced and Fig. 2c shows the accumulated change in phase with each pulse applied to the microheater. Over the entire range the phase shift per pulse is maintained below  $0.006\pi$  radians.

## III. CONCLUSION

A method has been put forward for that offers high resolution post-fabrication trimming of waveguide devices. The devices use Ge implanted waveguides and electrical annealing to make them trimmable, meaning they are both non-volatile and CMOS compatible. The method involved applying short voltage pulses with a phase dependent step between successive pulses. Over a tuning range of  $2\pi$ , the largest phase change measured was  $0.0054\pi$ , and an average resolution of phase trimming of  $0.0007\pi$  was achieved.

## ACKNOWLEDGMENTS

We acknowledge funding for HORIZON-EIC-2023 Pathfinder project DOLORES (101130178). D. J. Thomson acknowledges funding from the Royal Society for his University Research Fellowship (UF150325).

### REFERENCES

- Loiacono, R., Reed, G. T., Mashanovich, G. Z., Gwilliam, R., Henley, S. J., Hu, Y., Feldesh, R., & Jones, R., "Laser erasable implanted gratings for integrated silicon photonics", Optics Express, Vol.19, No.11, May 2011

- [2] Topley R., Martinez-Jimenez G., O'Faolain L., Healy N., Mailis S., Thomson D. J., Gardes F. Y., Peacock A. C., Payne D. N. R., Mashanovich G. Z., & Reed G. T., "Locally Erasable Couplers for Optical Device Testing in Silicon on Insulator", Journal of Lightwave Technology, Vol.32, No.12, June 2014

- [3] Chen, X., Milosevic, M. M., Thomson, D. J., Khokhar, A. Z., Franz, Y., Runge, A. F. J., Mailis, S., Peacock, A. C., & Reed, G. T., "Post-fabrication phase trimming of Mach Zehnder interferometers by laser annealing of germanium implanted waveguides", Photonics Research, Vol.5, No.6, December 2017

- [4] Milosevic, M. M., Chen, X., Cao, W., Runge, A. F. J., Franz, Y., Littlejohns, C. G., Mailis, S., Peacock, A. C., Thomson, D. J., & Reed, G. T., "Ion Implantation in Silicon for Trimming the Operating Wavelength of Ring Resonators", IEEE Journal of Selected Topics in Quantum Electronics, Vol.24, No.4, August 2018

- [5] Chen, X., Milosevic, M. M., Runge, A. F. J., Yu, X., Khokhar, A. Z., Mailis, S., Thomson, D. J., Peacock, A. C., Saito, S., & Reed, G. T., "Silicon erasable waveguides and directional couplers by germanium ion implantation for configurable photonic circuits", Optics Express, Vol.28, No.12, June 2020

- [6] Yu, X., Chen, X., Milosevic, M. M., Yan, X., Saito, S., & Reed, G. T., "Electrically Erasable Optical I/O For Wafer Scale Testing Of Silicon Photonic Integrated Circuits", IEEE Photonics Journal, Vol.12, No.5, October 2020

- [7] Yu, X., Chen, X., Milosevic, M. M., Shen, W., Topley, R., Chen, B., Yan, X., Cao, W., Thomson, D. J., Saito, S., Peacock, A. C., Muskens, O. L., Reed, G. T., "Ge Ion Implanted Photonic Devices and Annealing for Emerging Applications", Micromachines, Vol.13, No.291, February 2022

- [8] Jayatilleka, H., Frish, H., Kumar, R., Heck, J., Ma, C., Sakib, M., Huang, D., & Rong, H., "Post-Fabrication Trimming of Silicon Photonic Ring Resonators at Wafer-Scale", Journal of Lightwave Technology, Vol.39, No.15, August 2022

Figure 2: Graphs showing the voltage across the filament at each voltage pulse, the phase change between successive voltage pulses and the accumulative phase change after each voltage pulse (A, B and C respectively).