Received 22 February 2025, accepted 7 April 2025, date of publication 16 April 2025, date of current version 25 April 2025.

Digital Object Identifier 10.1109/ACCESS.2025.3561458

## **RESEARCH ARTICLE**

# **Differential and Common-Mode Model-Based Controller for a Grid-Tied Three-Phase NPC Converter**

GERARDO ESCOBAR<sup>10</sup>, (Senior Member, IEEE), JORGE L. LOPEZ-SARABIA<sup>1</sup>, (Member, IEEE), ANDRES A. VALDEZ-FERNANDEZ<sup>102</sup>, (Senior Member, IEEE), EDGAR D. SILVA-VERA<sup>®1</sup>, (Member, IEEE), JESUS E. VALDEZ-RESENDIZ<sup>1</sup>, (Senior Member, IEEE), AND JONATHAN C. MAYO-MALDONADO<sup>®</sup>, (Senior Member, IEEE)

Corresponding author: Andres A. Valdez-Fernandez (andres.valdez@ieee.org)

**ABSTRACT** This paper introduces a controller designed for transformerless inverters connected to the grid via an inductor-capacitor-inductor (LCL) output filter. The controller incorporates a virtual ground (VG) connection, providing a straightforward solution to mitigate common-mode current (CMC), i.e., to reduce the leakage ground current issue. Specifically, the focus is on a three-level, three-phase NPC inverter with split DC-link capacitors. The VG is established by connecting the star point of the LCL filter capacitors to the midpoint of the DC-link. This topology presents specific challenges, including voltage imbalances in the DC-link capacitors and resonances in the homopolar components of the signals within the LCL filter. The proposed controller not only addresses the goal of current injection but also ensures, on average, the balance of DC-link capacitor voltages (or equivalently, the regulation of the neutral point). Additionally, it provides the necessary damping for the homopolar components of the LCL filter signals. The performance of the proposed control scheme has been experimentally tested in a 2 kW three-phase NPC inverter prototype.

**INDEX TERMS** Photovoltaic power systems, leakage currents, dc-ac power convertors, control nonlinearities.

#### I. INTRODUCTION

In photovoltaic (PV) power generation systems, transformerless PV inverters are becoming the preferred choice due to their high efficiency, reduced cost, as well as lower volume and weight. However, by removing the transformer, the galvanic isolation between the PV panel and the grid disappears, causing a leakage (ground) current issue [1], [2]. In particular, in PV panel arrays, due to their physical construction, stray capacitors arise between the PV cell terminals and the grounded PV metal frame and therefore transformerless topologies allow a direct electrical connection between the PV cell terminals and the ground path through the stray capacitors. The interaction between stray capacitors and the

The associate editor coordinating the review of this manuscript and approving it for publication was Jahangir Hossain.

usually high frequency common-mode voltage (CMV) results in an undesirable high-frequency leakage ground current (LGC) flowing to the ground path [3]. Recall that the CMV is intrinsically generated by the switching process in a voltage-sourced inverter (VSI) [4].

Unfortunately, LGCs are one of the main problems in transformerless PV systems as they can compromise safety, increase total harmonic distortion (THD) of the grid-side current, increase energy losses, and may also create additional electromagnetic interference (EMI) [5]. The international standards IEC 62109-2 [6] and VDE V0126-1-1 has fixed 300 mA as an upper limit for the LGC, indicating that a PV system must be disconnected from the grid if the LGC exceeds such a value for more than 0.3 seconds [7]. In recent years, various strategies have been proposed in the literature to address the issue of CMV, focusing on

<sup>&</sup>lt;sup>1</sup>School of Engineering and Sciences, Tecnológico de Monterrey, Monterrey, Nuevo Leon 64849, Mexico <sup>2</sup>School of Sciences, Universidad Autónoma de San Luis Potosi (UASLP), San Luis Potosi 78000, Mexico

<sup>&</sup>lt;sup>3</sup>Department of Electronic and Electrical Engineering, The University of Sheffield, S10 2TN Sheffield, U.K.

reducing LGC and enhancing the performance of photovoltaic (PV) systems. These strategies (or a combination of them [8]) can be grouped into the following three categories: (*i*) improved switching strategies [3], [4], [9], [10], (*ii*) topological solutions [11], [12], and (*iii*) advanced control methods [5], [13].

Traditional switching strategies have been mainly used to reduce CMV in multi-level inverter-based PV systems. The idea behind them consists in avoiding certain switching control vectors producing CMV or, at least, to keep it as constant as possible. In [14], it is shown that inverters with an odd number of levels can generate zero common-mode voltage by switching among a reduced set of available states. However, since the switching states are restricted, it is no longer possible to guarantee voltage balance of the capacitors, even when battery systems are used [4]. To overcome this issue, some authors have proposed the insertion of a fourth leg to handle the DC-link voltage balance [12]. In fact, if the PV system is working in open-loop, then the capacitor voltage balancing (or neutral point balancing) and CMV cancellation cannot be simultaneously achieved without hardware modifications. This has been observed in [12] where the CMV issue is addressed by reducing the number of switching states, and a fourth leg is introduced to guarantee the voltage balance, whose main disadvantages are the increase of cost, weight, volume and computational effort. Improved switching strategies have been reported in [9] combining discontinuous PWM and the reference voltage decomposition method. This strategy required zero-sequence voltages and neutral-point current information for the control implementation to simultaneously solve the capacitor voltage balancing problem and the CMV reduction.

Alternatively, modifications to traditional topologies using the concept of VG have also been studied in recent years [5], [11], [13], [15]. The VG connection consists in splitting the DC-link capacitors and linking their midpoint of connection to the network's neutral point [8], which offers the possibility to solve the CMV issue. Following this hardware modification, the three-phase inverter can be managed as three separate single-phase subsystems. However, this adjustment requires an additional control strategy to maintain balanced capacitor voltages and thus ensuring that they remain at the same level. This requirement serves as the motivation for the present study. In [15], the authors analyze a singlephase grid-transformerless photovoltaic (PV) system based on a two-level full-bridge inverter with an inductor-capacitorinductor (LCL) output filter. They achieve a reduction in LGC by implementing a mitigation method that connects the star point of the LCL output filter capacitors to the midpoint of the DC-link capacitors. This connection is facilitated through an additional inductor filter, which helps bypass the common-mode current (CMC) in the ground leakage loop. In [13], a comparative study is conducted on single-phase transformerless topologies, focusing on a twolevel full-bridge inverter and a three-level full-bridge NPC inverter, both incorporating a VG connection. The study demonstrates that for both topologies, regardless of the load current, the LGC is significantly reduced, meeting the DIN VDE 0126-1-1 standard (less than 300 mA). However, this reduction comes at the expense of redirecting the CMC through an alternative path linked to the VG connection, which involves the switching devices. In [5], a controller based on the differential-mode and common-mode models is proposed for a single-phase H-bridge NPC (HB-NPC) inverter grid connected through modified LCL filters plus a VG connection and ground path. In this case, the capacitor of the LCL filter is split in two capacitors that are then connected to the positive and negative terminals of the DC-link. The authors show that this modification considerably alleviates the LGC.

Another critical challenge in PV multilevel inverters is to ensure proper voltage balance control of the DC-link capacitors. Uneven voltage levels in these capacitors lead to improper operation of the PV system, as these levels are crucial to reconstruct the injected voltage. This issue is particularly significant in grid-connected applications that use LCL filters. Furthermore, when a VG connection is present, additional resonance problems may occur between the zero-sequence components of the LCL filter signals and the imbalance state of the DC-link, as highlighted in previous studies such as [13] and [16]. Recently, a controller for a single-phase HB-NPC inverter grid-tied through an LCL filter was proposed and experimentally validated in [17]. The extension of this control structure to the three-phase multilevel inverter HB-NPC, which is not a simple task, is the main contribution of this work. As in [17], the three-phase topology under study includes a ground path established between the PV terminals connected to the ground through stray capacitors and the neutral point of the grid to allow the circulation of a LGC powered by the CMV generated by the VSI, which is referred to as the ground path. The three-phase topology also includes a particular VG connection with the aim of reducing the LGC induced through the stray capacitors. The main difference is that in the present work we consider the particularities of the three-phase case, which involves transformations to a fixed reference frame, where interesting and useful structures and definitions of variables arise. For this, as an initial step, the mathematical model of the three-phase HB-NPC multilevel inverter is developed. Next, the control is designed based on the model structure leading to a two-loop feedback configuration comprising (i) current tracking and (ii) voltage balance loops.

Therefore, in the present work, it is possible to identify the following specific contributions related more to the three-phase versions of the modeling and control design of the HB-NPC multilevel inverter:

- 1. A complete mathematical model in (fixed-frame)  $\alpha\beta\gamma$ -coordinates is presented to highlight the system structural properties that facilitate the control design process.

- **2.** It is shown that, the mathematical model can be split in two completely decoupled subsystems: a *first subsystem*

associated with the differential-mode part involving the fixed-frame coordinates of LCL filter signals plus the sum of the DC-link capacitors voltages; and a *second subsystem* associated with the common-mode part involving the zero-sequence component of the LCL signals, the difference of the DC-link capacitors voltages and the stray capacitors voltage.

**3.** A solution to guarantee the balance of DC-link capacitor voltages involving the homopolar (or zero sequence) component of the control input.

#### **II. SYSTEM DESCRIPTION**

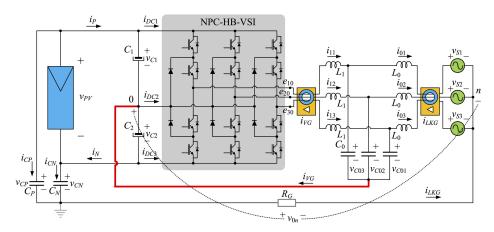

Fig. 1 shows the three-phase NPC inverter tied to the grid through an LCL filter considered in the present work. The inverter takes energy from a PV array that produces a voltage  $v_{PV}$  and is injected to the grid represented by voltage supplies  $v_{S1}$ ,  $v_{S2}$  and  $v_{S3}$ . Notice that the circuit includes a ground path established from the star connection point n of the grid source that is normally grounded upstream, and to the stray capacitors  $C_P$  and  $C_N$  that appear between the PV cells and the PV frame that is locally grounded. The ground impedance due to the distance between both grounds is represented by  $R_G$  through which the current  $i_{LKG}$  flows. The LCL filter includes the inductors  $L_0$ , on the grid-side, with associated current signals  $i_{01}$ ,  $i_{02}$  and  $i_{03}$ ; output filter capacitors  $C_0$  with their voltage signals  $v_{C01}$ ,  $v_{C02}$  and  $v_{C03}$ ; inductors  $L_1$ , on the inverter-side, with associated current signals  $i_{11}$ ,  $i_{12}$  and  $i_{13}$ . The DC-link includes capacitors  $C_1$  and  $C_2$  with associated voltages  $v_{C1}$  and  $v_{C2}$ , respectively.

In this application, the star point connection of the LCL filter capacitors m is connected to the midpoint 0 of the DC-link capacitors forming the VG connection, where the current  $i_{VG}$  flows. This connection is aimed to cope with the LGC  $i_{LKG}$  caused by the CMV inherently generated by the switching action of the NPC VSI. In fact, such a VG connection creates an alternative path for the circulation of high-frequency harmonic components of the CMC, this new created current is referred to as the VG current  $i_{VG}$ . As a result,  $i_{LKG}$  is considerably reduced.

Although not implemented in this study, the proposed topology enables maximum utilization of the DC-link voltage. Notably, there is no direct connection between the neutral point "n" and the inverter (commonly linked to the midpoint of the DC-link capacitors), aside from the ground path. This configuration establishes a three-wire connection. As a result, techniques such as third-harmonic reference injection or space vector modulation (SVM) can be employed to virtually extend the effective use of the DC-link voltage, potentially leading to significant efficiency improvements.

#### A. MATHEMATICAL MODEL

In the proposed approach, the controller design is based on the averaged version of the system model. In this case, the switching sequence vector  $\boldsymbol{\delta} = [\delta_1, \delta_2, \delta_3]^{\top}$  ( $\delta_i \in \{-1, 0, 1\}$ ,  $i \in \{1, 2, 3\}$ ) is replaced, in the model equations, by the corresponding vector of duty ratios  $\mathbf{u} = [u_1, u_2, u_3]^{\top}$  ( $-1 \le u_i \le 1$ ,

$i \in \{1, 2, 3\}$ ). This is based on the assumption that the switching frequency is sufficiently high as compared to the grid fundamental frequency, and that the LCL filter has been properly designed to filter out the switching harmonics. In consequence, the dynamics of the circuit in Fig. 1 can be described by means of an average mathematical model with enough accuracy, and thus the control design can now focus on the design of such duty ratios, while a separate modulation algorithm is still necessary to reconstruct the switching sequences out of the duty cycles. Additionally, to facilitate the modeling process and analysis, voltage  $v_{PV}$  is considered as a known constant value, while  $C_1 = C_2 = C$ ,  $C_P = C_N = C_L$ , and the set of passive elements  $L_1$ ,  $L_0$ ,  $C_0$  is considered equal on each phase.

Using Kirchhoff's laws and based on previous assumptions, the exact mathematical model of system shown in Fig. 1, in original coordinates, is given by

$$L_0 \dot{\hat{\mathbf{i}}}_0 = \mathbf{v}_{C0} - \mathbf{v}_S + \nu_{0n} [1 \ 1 \ 1]^\top, \tag{1}$$

$$C_0 \dot{\mathbf{v}}_{C0} = \mathbf{i}_1 - \mathbf{i}_0, \tag{2}$$

$$L_1 \dot{\hat{\mathbf{i}}}_1 = \mathbf{e} - \mathbf{v}_{C0},\tag{3}$$

$$C_L(\dot{v}_{CP} + \dot{v}_{CN}) = -[1\ 1\ 1]\mathbf{i}_0,$$

(4)

$$C(\dot{v}_{C1} - \dot{v}_{C2}) = [1\ 1\ 1]\mathbf{i}_0 - i_{DC1} - i_{DC2},\tag{5}$$

$$C(\dot{v}_{C1} + \dot{v}_{C2}) = i_P + i_N - i_{DC1} + i_{DC3}, \tag{6}$$

where  $\mathbf{i}_0 = [i_{01}, i_{02}, i_{03}]^{\top}$  and  $\mathbf{i}_1 = [i_{11}, i_{12}, i_{13}]^{\top}$  are the grid-side and inverter-side currents vectors, respectively;  $\mathbf{v}_{C0} = [v_{C01}, v_{C02}, v_{C03}]^{\top}$  is the capacitor voltages vector;  $\mathbf{v}_S = [v_{S1}, v_{S2}, v_{S3}]^{\top}$  is the grid voltages vector;  $v_{0n}$  is the voltage measured at point 0 and referred to point n, which, according to Fig. 1, is given by

$$v_{0n} = v_{C2} + v_{CN} + R_g i_{LKG}; (7)$$

$\mathbf{e} = [e_{10}, e_{20}, e_{30}]^{\mathsf{T}}$  is the injected voltage vector, that is, the vector of voltages generated by the inverter, which is calculated as

$$\mathbf{e} \triangleq \frac{v_{C1} - v_{C2}}{2} [u_1^2, u_2^2, u_3^2]^\top + \frac{v_{C1} + v_{C2}}{2} \mathbf{u}, \tag{8}$$

where  $\mathbf{u} = [u_1, u_2, u_3]^{\top}$  represent the switch positions of the three legs of the NPC inverter,  $u_i \in \{-1, 0, 1\}$  ( $i \in \{1, 2, 3\}$ ).  $v_{CP}$  and  $v_{CN}$  are the stray capacitors voltages;  $v_{C1}$  and  $v_{C2}$  are the DC-link capacitors voltages;  $i_{DC1}$  and  $i_{DC2}$  are the inverter DC-side currents, which can be calculated as

$$i_{DC1} = \left[ \frac{1 + u_1}{2} u_1, \ \frac{1 + u_2}{2} u_2, \ \frac{1 + u_3}{2} u_3 \right] \mathbf{i}_1, \tag{9}$$

$$i_{DC2} = [(1 - u_1^2), (1 - u_2^2), (1 - u_3^2)] \mathbf{i}_1.$$

(10)

$$i_{DC3} = \left[\frac{u_1 - 1}{2}u_1, \frac{u_2 - 1}{2}u_2, \frac{u_3 - 1}{2}u_3\right]\mathbf{i}_1, \tag{11}$$

In this document, bold typeface characters denote vectors or matrices, whereas regular typeface characters represent scalars. Notice that, the grid-side dynamics (1)-(4) and the capacitor voltage dynamics (5)-(6) are coupled and depend on the voltage  $v_{0n}$ , which is not accessible. Therefore, in the next

FIGURE 1. Equivalent circuit of a three-level NPC inverter grid connected through an LCL filter with a leakage ground path and a virtual ground connection.

section, a more convenient representation of the mathematical model is proposed to facilitate the controller design and to reduce the expressions of the model.

#### **B. MODEL TRANSFORMATION**

According to (5)-(6) and (8), the two natural variables that simplify the model representation are the sum and the difference of the capacitor voltages in the DC-link, that is,

$$v_{PV} = v_{C1} + v_{C2}, (12)$$

$$x_2 \triangleq v_{C1} - v_{C2}.\tag{13}$$

where the sum of the capacitor voltages turns out to be equal to the DC supply voltage  $v_{PV}$ , which is considered either constant or that changes much more slowly with respect to the dynamics of the system. Recall that, in a practical implementation, voltage  $v_{PV}$  is regulated towards a voltage reference fixed by a MPPT method whose sampling time is considerably larger than the sampling time of the control system. Therefore, the dynamics of the sum of capacitors voltages (6) can be reduced to the following algebraic restriction:

$$C(\dot{v}_{C1} + \dot{v}_{C2}) = 2i_{PV} - i_{DC1} + i_{DC3} = 0$$

(14)

where  $i_P + i_N = 2i_{PV} + i_{CN} - i_{CP}$ , and since  $C_P = C_N$  and  $v_{PV}$  is a constant, then  $\dot{v}_{CN} = \dot{v}_{CP}$ , and thus  $i_{CN} = i_{CP}$ .

The difference of capacitor voltages  $x_2$  is a new variable that reflects the capacitors voltage balance and is associated to the common-mode voltage of the DC-link capacitors.

Now, the inverter voltage  $\mathbf{e}$  can be rewritten, by direct substitution of (12) and (13) in (8), as follows:

$$\mathbf{e} = \frac{x_2}{2} [u_1^2, u_2^2, u_3^2]^\top + \frac{v_{PV}}{2} \mathbf{u}.$$

(15)

As usual, it is very convenient to express the model in terms of variables in (fixed-frame)  $\alpha\beta\gamma$ -coordinates, where the  $\gamma$ -coordinate represents the homopolar or zero-sequence component. Along the paper, the use  $\gamma$  instead of the usual "0" is preferred to avoid confusion with respect to the output variables where this subindex is already in use. Expressing the

model in this new set of variables emphasizes the structural properties of the system, which are particularly advantageous for the control design process. The transformation from the original three-phase coordinates to fixed-frame coordinates is achieved using the power-preserving Clarke transformation as follows:

$$\mathbf{x}_{\alpha\beta\gamma} = \begin{bmatrix} x_{\alpha} \\ x_{\beta} \\ x_{\gamma} \end{bmatrix} = \sqrt{\frac{2}{3}} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \\ \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} & \frac{1}{\sqrt{2}} \end{bmatrix} \begin{bmatrix} x_{1} \\ x_{2} \\ x_{3} \end{bmatrix}.$$

(16)

To facilitate the controller design, it is proposed to split the model (1)-(6) in two subsystems. A first subsystem associated with the differential-mode part, and a second subsystem associated with the common-mode part. The control design of both subsystems is treated separately as, under some practical assumptions to be discussed later, they become decoupled from one another.

The first subsystem involves the  $\alpha\beta$  components of the LCL filter signals and the dynamics of the sum of DC-link capacitor voltages (in this case, a simple algebraic restriction), that is,

$$L_0 \dot{\hat{\mathbf{i}}}_{0\alpha\beta} = \mathbf{v}_{C0\alpha\beta} - \mathbf{v}_{S\alpha\beta}, \tag{17}$$

$$C_0 \dot{\mathbf{v}}_{C0\alpha\beta} = \mathbf{i}_{1\alpha\beta} - \mathbf{i}_{0\alpha\beta},\tag{18}$$

$$\overset{\cdot}{L_1}_{1\alpha\beta} = \mathbf{e}_{\alpha\beta} - \mathbf{v}_{C0\alpha\beta}, \tag{19}$$

$$i_{\text{PV}} = (\mathbf{u}_{\alpha\beta}^{\top} \mathbf{i}_{1\alpha\beta} + u_{\gamma} i_{1\gamma})/2 \tag{20}$$

where  $\mathbf{i}_{0\alpha\beta} = [i_{0\alpha}, i_{0\beta}]^{\top}$ ,  $\mathbf{i}_{1\alpha\beta} = [i_{1\alpha}, i_{1\beta}]^{\top}$ , are the grid-side and inverter-side currents vectors in  $\alpha\beta$ -coordinates, respectively;  $\mathbf{v}_{C0\alpha\beta} = [v_{C0\alpha}, v_{C0\beta}]^{\top}$  is the capacitor voltages vector in  $\alpha\beta$ -coordinates;  $\mathbf{v}_{S\alpha\beta} = [v_{S\alpha}, v_{S\beta}]^{\top}$  is the grid voltages vector in  $\alpha\beta$ -coordinates;  $\mathbf{e}_{\alpha\beta} = [e_{\alpha}, e_{\beta}]^{\top}$  is the injected voltage vector in  $\alpha\beta$ -coordinates;  $i_{1\gamma}$  and  $i_{1\gamma}$  and  $i_{1\gamma}$  are the zero-sequence components of the inverter-side current and duty ratio vectors, respectively;  $i_{1\gamma}$  and  $i_{1\gamma}$  are the LCL filter grid-side and inverter-side inductances, and output capacitance, respectively.

The duty ratios vector in  $\alpha\beta$ -coordinates is represented by  $\mathbf{u}_{\alpha\beta} = [u_{\alpha}, u_{\beta}]^{\top}$ , which, based on (15), is related to the vector of injected voltages  $\mathbf{e}_{\alpha\beta}$  as follows:

$$\mathbf{e}_{\alpha\beta} = \frac{x_2}{2\sqrt{3}} \begin{bmatrix} \frac{u_{\alpha}^2 - u_{\beta}^2}{\sqrt{2}} 2u_{\alpha}u_{\gamma} \\ \sqrt{2}u_{\alpha}u_{\beta} + 2u_{\beta}u_{\gamma} \end{bmatrix} + \frac{v_{PV}}{2} \mathbf{u}_{\alpha\beta}. \tag{21}$$

It is noteworthy that the injected voltage vector  $\mathbf{e}_{\alpha\beta}$  is taken as the actual control input of subsystem (17)-(19) instead of the duty ratios vector  $\mathbf{u}_{\alpha\beta}$ .

Remark 1: Notice that the structure of the first subsystem (17)-(21) is very similar to that of the conventional two-level converter model [18], except for the first vector term on the right-hand side of (21) that can be considered as a disturbance. Therefore, it is proposed to use a similar controller design approach as that followed in the conventional two-level converter. Thus, in the next section, the subsystem composed of (17)-(19) will be used to achieve the *current tracking control objective*.

The second subsystem includes the description of the  $\gamma$ -coordinate (zero-sequence component) of the LCL filter signals plus the difference of the DC-link capacitors voltages (also referred to as the capacitors voltage balance or the common-mode voltage of the DC-link capacitors), and the stray capacitors voltage, that is,

$$\dot{L_0}_{00} = -3R_g i_{0\gamma} + v_{C0\gamma} + \sqrt{3}v_{CL} - \frac{\sqrt{3}}{2}x_2, \qquad (22)$$

$$C_0 \dot{v}_{C0\gamma} = i_{1\gamma} - i_{0\gamma}, \tag{23}$$

$$\dot{L_1} \dot{i}_{1\gamma} = \frac{x_2}{2\sqrt{3}} (u_\alpha^2 + u_\beta^2 + u_\gamma^2) + \frac{v_{PV}}{2} u_\gamma - v_{C0\gamma}, \quad (24)$$

$$C\dot{x}_{2} = \sqrt{3}i_{0\gamma} - \frac{2}{\sqrt{3}} \left( \mathbf{u}_{\alpha\beta}^{\top} \mathbf{i}_{1\alpha\beta} \right) u_{\gamma}$$

$$- \frac{1}{\sqrt{6}} \left[ u_{\alpha}^{2} - u_{\beta}^{2}, -2u_{\alpha}u_{\beta} \right] \mathbf{i}_{1\alpha\beta}$$

$$- \frac{1}{\sqrt{3}} \left( u_{\alpha}^{2} + u_{\beta}^{2} + u_{\gamma}^{2} \right) i_{1\gamma}, \tag{25}$$

$$2C_L \dot{\mathbf{v}}_{CL} = -\sqrt{3}i_{0\gamma},\tag{26}$$

where  $i_{0\gamma}$ ,  $v_{C0\gamma}$  and  $i_{1\gamma}$  are the homopolar (or zero-sequence) components of the grid-side current, capacitor voltage and inverter-side current of the LCL filter, respectively;  $v_{CL}$  represents the CMV of the stray capacitors, which is defined as

$$v_{CL} \triangleq \frac{v_{CP} + v_{CN}}{2}; \tag{27}$$

and  $u_{\gamma}$  is the zero-sequence component of the duty ratio vector that represents the actual control input of subsystem (22)-(26). In the next section, this subsystem will be used to achieve the *voltage balance control objective*.

Remark 2: Notice that the zero-sequence of the grid voltage source does not appear in the second subsystem, as it is assumed that  $v_{sa} + v_{sb} + v_{sc} = 0$ , and thus  $v_{sy} = 0$ .

Fig. 1 shows that, on the grid-side, a four-wire connection is established as the neutral point has been grounded,

providing a path through which the LGC can flow and, therefore, the following holds:

$$i_{0\nu} = -i_{LKG}/\sqrt{3}$$

. (28)

### **III. CONTROLLER DESIGN**

This section outlines the design of the proposed controller, which consists of two control loops corresponding to the previously described subsystems: the current tracking loop and the voltage balance loop. The current tracking loop addresses the differential-mode ( $\alpha\beta$ ) signals of the LCL filter, while the voltage balance loop manages the common-mode (homopolar or zero-sequence) signals of the LCL filter, the DC-link capacitor voltage difference, and the stray capacitor voltages. Additionally, practical modifications are introduced at the end of this section to enhance the controller's implementation.

#### A. CURRENT TRACKING CONTROL

This part of the control design considers the first subsystem, composed by (17)-(19), where a current tracking controller is proposed to guarantee grid power injection with a given power factor. The design is based on the following assumptions:

- Currents on the inverter-side  $\mathbf{i}_{1\alpha\beta}$  and grid voltages  $\mathbf{v}_{S\alpha\beta}$  are the only variables measured.

- LCL filter parameters  $L_1$ ,  $L_0$  and  $C_0$  are known constants.

- The system fundamental frequency  $\omega_0$  is assumed to be a known constant or may vary slowly, and can be available through an external PLL.

- The power to be injected to the grid  $P_0$  (which is extracted from the photovoltaic array) is a known constant.

- The grid voltage signal  $\mathbf{v}_{S\alpha\beta}$  mainly comprises a fundamental component plus a slight harmonic distortion.

Based on the above considerations, the *current tracking* control objective consists in designing an  $\mathbf{e}_{\alpha\beta}$  such that the grid-side current  $\mathbf{i}_{0\alpha\beta}$  follows its reference  $\mathbf{i}_{0\alpha\beta}^*$ , i.e.,

$$\mathbf{i}_{0\alpha\beta} \to \mathbf{i}_{0\alpha\beta}^* \quad \text{as} \quad t \to \infty.$$

(29)

To facilitate the presentation, power injection with a unitary power factor has been considered; however, the result can be extended relatively easily to a non-unitary power factor. In this particular case, the current reference  $\mathbf{i}_{0\alpha\beta}^*$  is defined as

$$\mathbf{i}_{0\alpha\beta}^* = \frac{P_0}{||\mathbf{v}_{S\alpha\beta}||^2} \mathbf{v}_{S\alpha\beta}^{+1},\tag{30}$$

where  $P_0$  is the desired active power;  $\mathbf{v}_{S\alpha\beta}^{+1}$  is the grid voltage positive sequence fundamental component, which can be obtained, for instance, using a vector extension of the band-pass filter (BPF) in [19], which is discussed in detail later; and  $||\mathbf{v}_{S\alpha\beta}||$  is the euclidean norm of the voltage vector  $\mathbf{v}_{S\alpha\beta}$ .

Nevertheless, as above stated, only the inverter-side currents  $\mathbf{i}_{1\alpha\beta}$  are available from measurement, and thus the control objective must be recast to, first, force the inverter-side current  $\mathbf{i}_{1\alpha\beta}$  to follow a reference  $\mathbf{i}_{1\alpha\beta}^*$ , which must indirectly guarantee tracking of the grid-side current  $\mathbf{i}_{0\alpha\beta}$  towards its reference  $\mathbf{i}_{0\alpha\beta}^*$ , that is,

$$\mathbf{i}_{1\alpha\beta} \to \mathbf{i}_{1\alpha\beta}^* \quad \Rightarrow \quad \mathbf{i}_{0\alpha\beta} \to \mathbf{i}_{0\alpha\beta}^* \quad \text{as} \quad t \to \infty.$$

(31)

For this, the construction of reference  $\mathbf{i}_{1\alpha\beta}^*$  is calculated based on the model (17)-(19), which yields

$$\mathbf{i}_{1\alpha\beta}^* = (1 - \omega_0^2 C_0 L_0) \mathbf{i}_{0\alpha\beta}^* + \frac{C_0 \omega_0}{2} \varphi_{S\alpha\beta}^{+1},$$

(32)

where  $\varphi_{S\alpha\beta}^{+1}$  is the quadrature companion, or square phase component of  $\mathbf{v}_{S\alpha\beta}^{+1}$ , i.e.,  $\varphi_{S\alpha\beta}^{+1}$  is a vector that has the same magnitude as  $\mathbf{v}_{S\alpha\beta}^{+1}$  but exhibits a phase shift of 90 degrees ahead, which is an available signal available in the extended version of the BPF in [19].

Based on the structure of subsystem (17)-(19), and according to [18], the following proportional plus resonant (PR) conventional controller is considered:

$$\mathbf{e}_{\alpha\beta} = k_p \tilde{\mathbf{i}}_{1\alpha\beta} + \begin{bmatrix} \frac{\lambda s}{s^2 + \omega_0^2} & 0\\ 0 & \frac{\lambda s}{s^2 + \omega_0^2} \end{bmatrix} \tilde{\mathbf{i}}_{1\alpha\beta} - \mathbf{v}_{S\alpha\beta}, \tag{33}$$

where  $\tilde{\mathbf{i}}_{1\alpha\beta} \triangleq \mathbf{i}_{1\alpha\beta} - \mathbf{i}_{1\alpha\beta}^*$  is the error of the current vector;  $k_p$  is the proportional gain;  $\lambda$  is the resonant gain that settles the speed of response of the resonant controller. Notice that  $\mathbf{v}_{S\alpha\beta}$  has been inserted in the control expression as a feedforward term to cancel out such a disturbance. Recall that, in this PR controller, the proportional action provides damping to the system, while the resonant effect guarantees zero steady-state tracking error. Moreover, based on (21), it is proposed to reconstruct  $\mathbf{u}_{\alpha\beta}$  as follows, which is referred to as the normalization:

$$\mathbf{u}_{\alpha\beta} = 2\mathbf{e}_{\alpha\beta}/v_{PV} \tag{34}$$

#### **B. VOLTAGE BALANCE CONTROL**

One of the main interests in the present work is to guarantee the balance of the DC-link capacitor voltages. In this case, the *voltage balance control objective* consists in designing an  $u_{\gamma}$  such that the DC-link capacitors voltages difference is asymptotically driven to zero, i.e.,

$$x_2 \to 0$$

as  $t \to \infty$ . (35)

To facilitate the control design, it is assumed that the averaged closed loop dynamics of the zero-sequence components of the LCL filter variables  $i_{0\gamma}$ ,  $v_{C0\gamma}$  and  $i_{1\gamma}$ ; the capacitors voltage balance  $x_2$ ; and the CMV of the stray capacitors  $v_{CL}$  described in (22)-(26) evolve much slower than the  $\alpha\beta$ -coordinates of the LCL filter (differential-mode) signals described in (17)-(19). Therefore, from the viewpoint of subsystem (22)-(26), it can be assumed that signals  $\mathbf{i}_{0\alpha\beta}$ ,

$\mathbf{i}_{1\alpha\beta}$  and  $\mathbf{v}_{C0\alpha\beta}$  have practically reached their references, that is,

$$\mathbf{i}_{0\alpha\beta} \approx \mathbf{i}_{0\alpha\beta}^* = \frac{P_0}{||\mathbf{v}_{S\alpha\beta}||^2} \mathbf{v}_{S\alpha\beta}^{+1},\tag{36}$$

$$\mathbf{i}_{1\alpha\beta} \approx \mathbf{i}_{1\alpha\beta}^* = C_0 \dot{\mathbf{v}}_{C0\alpha\beta}^* + \mathbf{i}_{0\alpha\beta}^*, \tag{37}$$

$$\mathbf{v}_{C0\alpha\beta} \approx \mathbf{v}_{C0\alpha\beta}^* = L_0 \widehat{\mathbf{i}}_{0\alpha\beta}^* + \mathbf{v}_{S\alpha\beta}, \tag{38}$$

$$\mathbf{e}_{\alpha\beta}^* \approx L_1 \widehat{\mathbf{i}}_{1\alpha\beta}^* + \mathbf{v}_{C0\alpha\beta}^*, \tag{39}$$

$$\mathbf{u}_{\alpha\beta} \approx \mathbf{u}_{\alpha\beta}^* = \frac{2\mathbf{e}_{\alpha\beta}^*}{v_{\text{PV}}}.$$

(40)

where  $||\mathbf{v}_{S\alpha\beta}||^2 = \mathbf{v}_{S\alpha\beta}^{\top} \mathbf{v}_{S\alpha\beta}$ . All these approximations and definitions are used to reduce the right-hand-side (RHS) of the model expressions (22)-(26) as explained next.

First, the second term on the RHS of (25) can be reduced as follows:

$$\mathbf{u}_{\alpha\beta}^{\top} \mathbf{i}_{1\alpha\beta} \approx (\mathbf{u}_{\alpha\beta}^*)^{\top} \mathbf{i}_{1\alpha\beta}^* = \frac{2\mathbf{e}_{\alpha\beta}^{*\top} \mathbf{i}_{1\alpha\beta}}{v_{PV}} = \frac{2(P_0 + \phi_{2\omega})}{v_{PV}}, \quad (41)$$

where  $\phi_{2\omega}$  represents the sum of powers dissipated on each LCL filter element, that is,

$$\phi_{2w} = L_1 \left( \dot{\hat{\mathbf{i}}}_{1\alpha\beta}^* \right)^{\top} \mathbf{i}_{1\alpha\beta}^* + C_0 \left( \dot{\mathbf{v}}_{C0\alpha\beta}^* \right)^{\top} \mathbf{v}_{C0\alpha\beta}^*$$

$$+ L_0 \left( \dot{\hat{\mathbf{i}}}_{0\alpha\beta}^* \right)^{\top} \mathbf{i}_{0\alpha\beta}^*, \tag{42}$$

which are mainly composed by second order harmonics. It should be noted that, in normal operation,  $P_0 \gg \phi_{2\omega}$ , and thus  $\phi_{2\omega}$  can be neglected.

Second, based on the fact that  $\mathbf{u}_{\alpha\beta}$  is a vector of sinusoidal signals maintaining a quadrature phase difference, then the third term on the RHS of (25) will be mainly composed by a third order harmonic, that is,

$$-\frac{1}{\sqrt{6}} \left[ u_{\alpha}^2 - u_{\beta}^2 - 2u_{\alpha}u_{\beta} \right] \mathbf{i}_{1\alpha\beta}^* = \phi_{3w}. \tag{43}$$

Notice that  $\phi_{3w}$  is inherent to the three-phase three-level selected topology, and will propagate to all state variables of subsystem (22)-(26) and, in particular, to  $u_{\gamma}$ .

Finally, the first term on the RHS of (24) and the fourth term on the RHS of (25) can also be reduced based on the following definition:

$$u_{\alpha}^2 + u_{\beta}^2 = \mathbf{u}_{\alpha\beta}^{\top} \mathbf{u}_{\alpha\beta} \triangleq k \quad k > 0,$$

(44)

After the above simplifications, subsystem (23)-(26) can be rewritten as

$$\begin{bmatrix} L_0 & 0 & 0 & 0 & 0 \\ 0 & C_0 & 0 & 0 & 0 \\ 0 & 0 & L_1 & 0 & 0 \\ 0 & 0 & 0 & C/2 & 0 \\ 0 & 0 & 0 & 0 & 2C_L \end{bmatrix} \begin{bmatrix} \dot{i} \\ i \\ 0 \gamma \\ \dot{v}_{C0\gamma} \\ \dot{i} \\ i \\ 1\gamma \\ \dot{x}_2 \\ \dot{v}_{CL} \end{bmatrix}$$

$$=\begin{bmatrix} -\sqrt{3}R_g & 1 & 0 & -\frac{\sqrt{3}}{2}\sqrt{3} \\ -1 & 0 & 1 & 0 & 0 \\ 0 & -1 & 0 & \frac{k+u_\gamma^2}{2\sqrt{3}} & 0 \\ \frac{\sqrt{3}}{2} & 0 & -\frac{k+u_\gamma^2}{2\sqrt{3}} & 0 & 0 \\ -\sqrt{3} & 0 & 0 & 0 & 0 \end{bmatrix} \begin{bmatrix} i_{0\gamma} \\ v_{C0\gamma} \\ i_{1\gamma} \\ x_2 \\ v_{CL} \end{bmatrix} + \begin{bmatrix} 0 \\ 0 \\ \frac{v_{P\gamma}}{2} \\ -\frac{P_0}{\sqrt{3}v_{P\gamma}} \\ 0 \end{bmatrix} u_\gamma + \begin{bmatrix} 0 \\ 0 \\ 0 \\ \frac{1}{4} \\ 0 \end{bmatrix} \phi_{3w}. \tag{45}$$

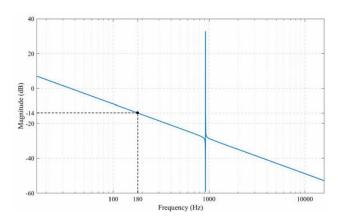

Notice that  $R_g$  is the only element adding damping in subsystem (45). In fact, the uncontrolled system, i.e., considering  $u_{\gamma}=0$  in (45), turns out to be a simple integrator plus a resonant filter, and is perturbed by a third-order harmonic  $\phi_{3w}$ . Fig. 2 shows the Bode diagram of the transfer function  $\phi_{3w} \rightarrow x_2$  of subsystem (45), which has been linearized at the equilibrium point  $[\bar{i}_{0\gamma}, \bar{\nu}_{C0\gamma}, \bar{i}_{1\gamma}, \bar{x}_2, \bar{\nu}_{CL}] = [0, 0, 0, 0, 0]$ , and assuming  $\bar{u}_{\gamma}=0$ , which is the case, as its design involves a linear combination of states. Notice that the third harmonic perturbation  $\phi_{3w}$ , located at 180 Hz, experiences an attenuation of approximately -14 dB, and is far to be affected by the closest resonance peak located at about 900 Hz. Therefore, in what follows, to simplify the control design, the effect of the term  $\phi_{3w}$  is neglected.

**FIGURE 2.** Bode diagram (only magnitude) of the transfer function  $\phi_{3w} \rightarrow x_2$  of subsystem (45) (x-axis in hertz and y-axis in decibels).

The control design follows the Lyapunov approach, which considers the following energy storage function:

$$H = \frac{1}{2} \begin{bmatrix} i_{0\gamma} \\ v_{C0\gamma} \\ i_{1\gamma} \\ x_2 \\ v_{CL} \end{bmatrix}^{\top} \begin{bmatrix} L_0 & 0 & 0 & 0 & 0 \\ 0 & C_0 & 0 & 0 & 0 \\ 0 & 0 & L_1 & 0 & 0 \\ 0 & 0 & 0 & C/2 & 0 \\ 0 & 0 & 0 & 0 & 2C_L \end{bmatrix} \begin{bmatrix} i_{0\gamma} \\ v_{C0\gamma} \\ i_{1\gamma} \\ x_2 \\ v_{CL} \end{bmatrix}.$$

(46)

Its time derivative along the trajectories of (45) is given by

$$\dot{H} = -\sqrt{3}R_g i_{0\gamma}^2 - \left(\frac{P_0}{\sqrt{3}v_{PV}}x_2 - \frac{v_{PV}}{2}i_{1\gamma}\right)u_{\gamma},\tag{47}$$

which can be made negative semi-definite by selecting

$$u_{\gamma} = R_d \left( \frac{P_0}{\sqrt{3}v_{PV}} x_2 - \frac{v_{PV}}{2} i_{1\gamma} \right),$$

(48)

where  $R_d > 0$  is a design parameter to insert additional damping.

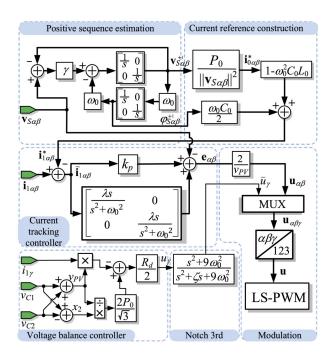

Summarizing, the controller vector  $\mathbf{u}_{\alpha\beta\gamma}$ , whose components are derived from (33), (34), and (48), achieves the control objectives (on average) while ensuring the stability of the overall system. The control objectives include (differential-mode) current tracking (to guarantee grid power injection) and DC-link capacitor voltage balancing while maintaining zero-sequence components of the LCL filter bounded. The block diagram of the proposed overall controller is shown in Fig. 3.

FIGURE 3. Block diagram of proposed controller the fundamental component estimation, the current reference construction, the current tracking and voltage balance loops, the notch filter, and the reconstruction of the duty ratios used in the PWM algorithm.

#### IV. IMPLEMENTATION

As described in (30), the design of the current reference  $\mathbf{i}_{0\alpha\beta}^*$  requires the fundamental positive sequence component  $\mathbf{v}_{S\alpha\beta}^{+1}$ , while the design of  $\mathbf{i}_{1\alpha\beta}^*$  in (32) requires, in addition, its quadrature component  $\boldsymbol{\varphi}_{S\alpha\beta}^{+1}$  (most of all, in case of reactive power injection), which has to be extracted from the grid-measured voltage  $\mathbf{v}_{S\alpha\beta}$ . For this, it is proposed to use a vector extension of the BPF presented in [19], that is,

$$\mathbf{v}_{S\alpha\beta}^{+1} = \operatorname{diag}\left\{\frac{\gamma s}{s^2 + \gamma s + \omega_0^2}, \frac{\gamma s}{s^2 + \gamma s + \omega_0^2}\right\} \mathbf{v}_{S\alpha\beta}. \tag{49}$$

This extraction mechanism is necessary because the grid signal may contain some harmonic distortion, and the controller does not include a harmonic compensation mechanism.

As shown in (45), the system is perturbed by a 3rd harmonic of the fundamental, which propagates to all state variables and, in consequence, the control objectives can only be guaranteed on average. Moreover, as described in (48), controller  $u_{\gamma}$  depends on the states; therefore, to avoid the reinjection of such a disturbance through  $u_{\gamma}$ , it is suggested to introduce a notch filter tuned at 3rd harmonic, as shown in Fig. 3, where  $\gamma_1 > 0$  is a design parameter. Out of this, a signal  $\tilde{u}_{\gamma}$  free of the 3rd harmonic disturbance can be obtained. The control input  $\tilde{u}_{\gamma}$  can now be incorporated to  $\mathbf{u}_{\alpha\beta}$  to complete the control vector  $\mathbf{u}_{\alpha\beta\gamma} = [\mathbf{u}_{\alpha\beta}^{\mathsf{T}}, u_{\gamma}]^{\mathsf{T}}$ . Finally, the vector in original coordinates  $\mathbf{u} = [u_1, u_2, u_3]$  is obtained by applying the inverse Clarke's transformation (16) to vector  $\mathbf{u}_{\alpha\beta\gamma}$ , and  $\mathbf{u}$  can now be used as a reference in the modulation algorithm to obtain the switching sequences.

#### **V. EXPERIMENTAL RESULTS**

This section presents the experimental evaluation of the proposed control scheme (shown in Fig. 3) in a 2 kW NPC inverter prototype grid-tied through an LCL filter. The NPC inverter is constructed with twelve IRG4PC50UD IGBTs and six RURG3060 ultra-fast diodes. The controller has been programmed in a Texas Instrument TMS320F28379D DSP control board. Stray capacitors  $C_P$  and  $C_N$  were emulated with 25 nF MKP capacitors connected to a resistor  $R_g$  of 10  $\Omega$  emulating the ground path impedance. The PV source was emulated by a Keysight n8935a DC power supply providing  $v_{pv}$  of 200 V. The three-phase grid is performed with a regenerative grid simulator Chroma model 61830 of 35 kW, which provides a  $v_s$  of 60 V at 60 Hz. The values of the prototype parameters are collected in Table 1.

**TABLE 1.** Parameters of the experimental prototype.

| Parameter           | Value                               | Parameter   | Value       |

|---------------------|-------------------------------------|-------------|-------------|

| $\overline{v_{pv}}$ | 200 V                               | $L_1$       | 3 mH        |

| $C_1 = C_2$         | $2200~\mu F$                        | $L_0$       | 2 mH        |

| $v_s$               | $60 \text{ V}_{RMS}, 60 \text{ Hz}$ | $C_0$       | $4.7 \mu F$ |

| $f_{sw}$            | 24 kHz                              | $C_P = C_N$ | 25 nF       |

| $f_s$               | 48 kHz                              | $R_g$       | $10 \Omega$ |

### A. STEADY STATE RESPONSES

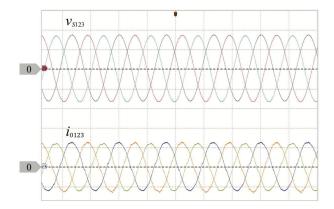

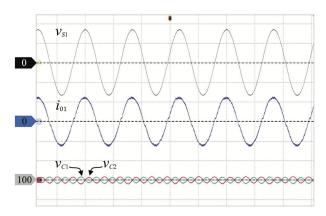

Fig. 4 shows the steady state response of the grid voltages  $v_{S1}$ ,  $v_{S2}$  and  $v_{S3}$ , and the grid-side currents  $i_{01}$ ,  $i_{02}$  and  $i_{03}$  due to a power demand of 800 W. Notice that the grid voltages are balanced and the injected currents have a sinusoidal shape and are in phase with the grid voltages. That means that in steady-state the power factor is approximately one.

Fig. 5 shows the steady-state response of the grid voltage  $v_{S1}$ , the grid-side current  $i_{01}$ , and the voltages of the DC-link capacitors  $v_{C1}$  and  $v_{C2}$ . It is noteworthy that both DC-link voltages exhibit a common DC offset of 100 V and are perturbed by a 3rd harmonic of the fundamental. Hence, the voltage balance control perfectly maintains the capacitor voltages at the same DC offset. The perturbations

**FIGURE 4.** Steady-state response of (top) grid voltages  $v_{S1}$ ,  $v_{S2}$  and  $v_{S3}$  (y-axis 50 v/div), and (bottom) grid-side currents  $i_{01}$ ,  $i_{02}$  and  $i_{03}$  (y-axis 5 A/div) (in all plots x-axis 10 ms/div).

at high order frequencies are out of the scope of the proposed controller, which only focus on guaranteeing DC-link capacitor voltages balance in average.

**FIGURE 5.** Steady-state response of (**from top to bottom**) the grid voltage  $v_{S1}$  (y-axis 50 v/div), the grid-side current  $i_{01}$  (y-axis 5 A/div), and (**two traces on the bottom**) the DC-link capacitors voltages  $v_{C1}$  and  $v_{C2}$  (in all plots x-axis 10 ms/div).

# B. TRANSIENTS RESPONSES AFTER STEP-WISE CHANGES IN THE INJECTED ACTIVE POWER REFERENCE

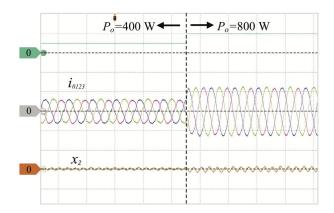

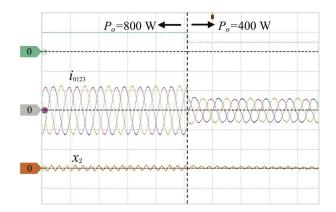

Fig. 6 and Fig. 7 shows the power reference  $P_0$ , the grid-side currents  $i_{01}$ ,  $i_{02}$  and  $i_{03}$ , and the DC-link voltage balance  $x_2$  after a step change in the power reference from 400 W to 800 W and back. It can be observed that the currents change their amplitude according to the demanded reference power in a relatively short period of time. This implies that the tracking controller ensures flawless tracking, regardless of step changes in the reference signal. Furthermore, it is also observed that the change in power demand does not affect the DC-link voltages balance (in average), but only the amplitude of the remaining third harmonic, as the latter depends on the magnitude of the current delivered by the inverter. In fact, the proposed balance controller is not affected by any change in the magnitude of the injected current.

**FIGURE 6.** Transient response during a reference power step-change going from  $P_0 = 400$  W to  $P_0 = 800$  W of (from top to bottom) the injected power reference  $P_0$  (y-axis 800 W/div), grid-side currents  $i_{01}$ ,  $i_{02}$  and  $i_{03}$  (y-axis 5 A/div), and (trace below) the differential mode of the DC-link capacitors voltages  $x_2$  (y-axis 2 v/div) (in all plots x-axis 20 ms/div).

**FIGURE 7.** Transient response during a reference power step-change going from  $P_0=800$  W to  $P_0=400$  W of (from top to bottom) the injected power reference  $P_0$  (y-axis 800 W/div), grid-side currents  $i_{01}$ ,  $i_{02}$  and  $i_{03}$  (y-axis 5 A/div), and (trace below) the common-mode of the DC-link capacitors voltages  $x_2$  (y-axis 2 v/div) (in all plots x-axis 20 ms/div).

### C. TRANSIENT RESPONSES AFTER ENABLING THE VG CONNECTION

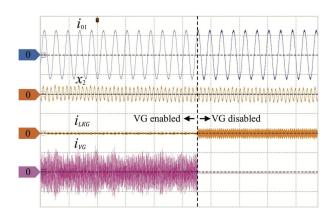

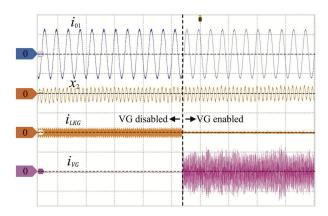

Fig. 8 and Fig. 9 show the transient responses of (from top to bottom) the grid-side current  $i_{01}$ , the balance of the DC-link capacitor  $x_2$ , the leakage ground current  $i_{LKG}$  and the virtual ground current  $i_{VG}$  after enabling and disabling the virtual ground path, respectively. Notice that, after enabling the VG connection, the leakage ground current i<sub>LKG</sub> reduces its RMS value to less than 300 mA, which is the maximum RMS value imposed by the Germany standard VDE-0126-1-1. An additional benefit of this modification is that the grid-side current reduces its THD because its CMC component now circulates through the VG connection. Note also that the voltage balance variable  $x_2$  does not experience any noticeable effect after enabling or disabling the VG connection. Therefore, the proposed CM controller could also be useful in applications without VG connection.

**FIGURE 8.** Transient response after disabling the VG connection of (**from top to bottom**) the grid-side current  $i_{01}$  (y-axis 5 A/div), the common-mode of the DC-link capacitors voltages  $x_2$  (y-axis 2 V/div), the leakage ground current  $i_{LKG}$  (y-axis 1 A/div), and the vitual ground current  $i_{VC}$  (y-axis 50 V/div), (in all plots x-axis 20 ms/div).

**FIGURE 9.** Transient response after enabling the VG connection of (**from top to bottom**) the grid-side current  $i_{01}$  (y-axis 5 A/div), the common-mode of the DC-link capacitors voltages  $x_2$  (y-axis 2 V/div), the leakage ground current  $i_{LKG}$  (y-axis 1 A/div), and the vitual-ground current  $i_{VG}$  (y-axis 50 V/div), (in all plots x-axis 20 ms/div).

# D. TRANSIENT RESPONSES AFTER DISABLING AND ENABLING THE CM CONTROL COMPONENT

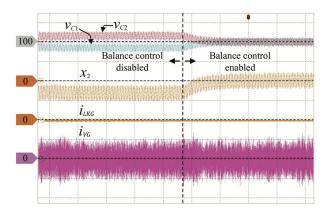

Fig. 10 shows the transient response of (from top to bottom) the voltages of the DC-link capacitors  $v_{C1}$  and  $v_{C2}$ , the DC-link voltages balance  $x_2$ , the leakage ground current  $i_{LKG}$  and the virtual ground current  $i_{VG}$  before and after enabling the balance controller. Notice that, before enabling the CM controller, the voltage of each capacitor  $v_{C1}$  and  $v_{C2}$  is different, and thus their difference  $x_2 \neq 0$ , indicating an unbalanced situation. This can be caused by asymmetries in the losses in the converter semiconductors or the DC-link capacitance values, or in the passive components attached to their terminals. Once the proposed CM control is enabled, the difference between the capacitor voltages  $x_2$  reaches zero (on average) in approximately 150 ms. Furthermore, the action of the CM controller does not exhibit a perceivable effect on the responses of  $i_{VG}$  and  $i_{LKG}$ , which is explained by the difference in time scales between the average control, dealing with relatively low frequency components, and the

**FIGURE 10.** Transient response after enabling the CM controller part  $\mathbf{e}_{\gamma}$  of **(from top to bottom)** DC-link capacitors voltages  $v_{C1}$  and  $v_{C2}$  (y-axis 2 V/div), the common-mode of the DC-link capacitors voltages  $x_2$  (y-axis 2 V/div), the leakage ground current  $i_{LKG}$  (y-axis 1 A/div) and the virtual ground current  $i_{VG}$  (y-axis 1 A/div), (in all plots x-axis 100 ms/div).

VG connection realized as a hardware modification and dealing with high frequency components.

#### VI. CONCLUSION

This paper presented the controller design for a three-phase three-level inverter connected to the grid through an LCL filter featuring a VG connection. The proposed controller guaranteed voltage balance of the DC link capacitors and, in addition, effectively injected the required damping to attenuate higher (mainly third) order harmonics, all these on average, and thus dealing with low-frequency components of signals. A relatively simple expression was derived for this part of the controller, relying on readily available signals, which considerably facilitated its implementation. As expected, the VG connection represented an excellent solution for reducing the leakage ground current at the expense of increasing the current called virtual current. This recirculating current keeps a constant magnitude, as it depends on the DC link voltage magnitude and the stray capacitors, and thus becomes negligible for higher power applications. Moreover, since the VG connection reduced the common-mode currents component, then the high frequency ripple observed in the grid-side current, and associated to such a common-mode component, is also reduced. It was observed that the VG connection and the proposed balancing controller did not affect each other as they deal with signals with quite different time scale, that is, while the proposed average controller deals with relatively slow signals, the VG connection is a hardware modification focusing on signals with high frequency components. The controller design was further validated through both mathematical and experimental results, demonstrating its effectiveness in maintaining stability and improving the overall performance of the inverter system under various operating conditions. Additionally, it is important to remark the simplicity of the proposed controller structure that allows an easy integration of existing schemes for harmonic compensation,

v.gr., repetitive control, learning control, among others. It is also important to remark that the VG connection respects the three-wire connection towards the grid; therefore, guaranteeing the maximum utilization of the DC-link voltage, which allows over-modulation using, for instace, the 3rd harmonic injection technique and SVM, among others. These topics are under study at the moment, and the results will be reported in the near future.

#### **REFERENCES**

- [1] J. Hassan, V. Minambres-Marcos, F. Barrero-Gonzalez, and A. A. Alvi, "An improved three-phase transformerless neutral point clamped inverter topology for common mode voltage reduction," in *Proc. IEEE 17th Int. Conf. Compat., Power Electron. Power Eng. (CPE-POWERENG)*, Jun. 2023, pp. 1–6.

- [2] H. K. Jahan, M. Sarhangzadeh, J. F. Ardashir, and F. Blaabjerg, "A symmetric switched-capacitor-based basic inverter unit for grid-connected PV systems," *IEEE Trans. Power Electron.*, vol. 37, no. 12, pp. 15594–15604, Dec. 2022.

- [3] J. Qiu, Y. He, C. Lei, Q. Jiao, and J. Liu, "An improved LMSVM method for leakage current suppression and neutral-point voltage control in transformerless NPC three-level inverters," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 10, no. 3, pp. 3100–3113, Jun. 2022.

- [4] Z. Li, X. Xing, C. Du, X. Li, C. Liu, and R. Zhang, "Leakage current suppression for Dual-DC-Port DC-AC converter in PV-battery hybrid system," *IEEE Trans. Power Electron.*, vol. 40, no. 5, pp. 7315–7328, May 2025.

- [5] S. Iturriaga-Medina, P. R. Martinez-Rodriguez, G. Escobar, C. A. Soriano-Rangel, D. Langarica-Cordoba, G. Vazquez-Guzman, and J. Lopez-Sarabia, "A control design for a photovoltaic transformerless HB-NPC inverter with leakage-ground current reduction," *Int. J. Electr. Power Energy Syst.*, vol. 146, Mar. 2023, Art. no. 108724.

- [6] U. A. Khan, A. A. Khan, F. Akbar, and J.-W. Park, "Single-stage single-phase H6 and H8 non-isolated buck-boost photovoltaic inverters," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 10, no. 4, pp. 4865–4878, Aug. 2022.

- [7] X. Guo, N. Wang, B. Wang, Z. Lu, and F. Blaabjerg, "Evaluation of three-phase transformerless DC-bypass PV inverters for leakage current reduction," *IEEE Trans. Power Electron.*, vol. 35, no. 6, pp. 5918–5927, Jun. 2020.

- [8] J. Lee, D. Lee, and J.-I. Ha, "Control and modulation methods of singlethree-phase PWM converter for suppressing leakage current," *IEEE Trans. Power Electron.*, vol. 40, no. 7, pp. 9137–9152, Jul. 2025.

- [9] Z. Xie, L. Peng, S. Zhao, S. Yang, and X. Zhang, "An improved reference voltage decomposition method based on three-level NPC converters with neutral-point voltage balancing and common-mode voltage reduction," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 11, no. 5, pp. 4618–4629, Oct. 2023.

- [10] M. Akbari, S. A. Davari, R. Ghandehari, F. Flores-Bahamonde, and J. Rodriguez, "Reduction of calculations virtual voltage vectors-based predictive control for 3-level NPC inverters with constant common-mode voltage," in *Proc. IEEE Int. Conf. Predictive Control Electr. Drives Power Electron. (PRECEDE)*, Jun. 2023, pp. 1–6.

- [11] F. Akbar, A. Elkhateb, H. F. Ahmed, A. A. Khan, H. Cha, and J.-W. Park, "Single-phase virtual-ground transformerless Buck–Boost inverters," *IEEE Trans. Power Electron.*, vol. 38, no. 9, pp. 11585–11600, Sep. 2023.

- [12] A. von Jouanne, S. Dai, and H. Zhang, "A multilevel inverter approach providing DC-link balancing, ride-through enhancement, and commonmode voltage elimination," *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 739–745, Aug. 2002.

- [13] G. Escobar, P. R. Martinez-Rodriguez, S. Iturriaga-Medina, J. C. Mayo-Maldonado, J. Lopez-Sarabia, and O. M. Micheloud-Vernackt, "Mitigation of leakage-ground currents in transformerless grid-tied inverters via virtual-ground connection," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 8, no. 3, pp. 3111–3123, Sep. 2020.

- [14] F. Wang, A. K. Wallace, S. Dai, A. Von Jouanne, and H. Zhang, "Multilevel inverter modulation schemes to eliminate common-mode voltages," *IEEE Trans. Ind. Appl.*, vol. 36, no. 6, pp. 1645–1653, Jun. 2000.

- [15] A. Khan, A. Iqbal, and M. B. Shadmand, "Novel LCL filter for non-isolated photovoltaic inverters with CM current trapping capability for weak grids," in *Proc. IECON-44th Annu. Conf. IEEE Ind. Electron. Soc.*, Oct. 2018, pp. 6128–6132.

- [16] A. Khan, S. D'silva, M. Hosseinzadehtaher, M. B. Shadmand, and H. Abu-Rub, "Differential and common mode active resonance damping control for shunt-less LCL filter based grid-connected PV inverters," in Proc. IEEE Power Energy Conf. Illinois (PECI), Feb. 2019, pp. 1–8.

- [17] J. Lopez-Sarabia, G. E. Valderrama, P. R. Martinez-Rodriguez, S. Iturriaga-Medina, J. C. Mayo-Maldonado, and D. d. Puerto-Flores, "DC-link capacitors' voltage balance in an HB-NPC five-level grid-tied inverter via the common-mode control component," *IEEE J. Emerg. Sel. Topics Power Electron.*, vol. 10, no. 3, pp. 3242–3255, Jun. 2022.

- [18] G. Escobar, P. R. Martinez-Rodriguez, C. N. M. Ho, and J. M. Sosa, "Design of an inverter-side current reference and controller for a singlephase LCL-based grid-connected inverter," *Int. Trans. Electr. Energy Syst.*, vol. 28, no. 1, p. e2476, Jan. 2018.

- [19] A. A. Valdez-Fernandez, G. Escobar, P. R. Martinez-Rodriguez, J. M. Sosa, D. U. Campos-Delgado, and M. J. Lopez-Sanchez, "Modelling and control of a hybrid power filter to compensate harmonic distortion under unbalanced operation," *IET Power Electron.*, vol. 10, no. 7, pp. 782–791, Jun. 2017.

ANDRES A. VALDEZ-FERNANDEZ (Senior Member, IEEE) received the Ph.D. degree in control and dynamical systems from Potosi Institute of Scientific and Technological Research (IPICyT), Mexico, in 2009. From 2008 to 2012, he was a full-time Professor-Researcher with the National Technological Institute of Mexico, Technological Institute of Superior Studies of Irapuato (TecNM-ITESI), Mexico. He is currently a full-time Professor-Researcher with the School

of Sciences, Autonomous University of San Luis Potosi (UASLP), Mexico. His research interests include analysis, modeling, and control design and fault diagnosis of active power filters, inverters, rectifiers, renewable energy systems, and e-mobility systems. He is a member of the National Research Fellows System level 2 (SNI-2), CONAHCyT, Mexico.

**EDGAR D. SILVA-VERA** (Member, IEEE) received the M.Sc. degree in electronics engineering from the Technological Institute of Superior Studies of Irapuato (ITESI), Irapuato, Mexico, in 2019, and the Ph.D. degree in electrical engineering from the Tecnológico de Monterrey, Monterrey, Mexico, in 2024. His research interests include the design, modeling, and control of power converters applied to renewable energy and storage systems, inverters, dc-dc converters, multilevel converters, batteries, and electrical drives.

**GERARDO ESCOBAR** (Senior Member, IEEE) received the Ph.D. degree in automatic control from the Laboratory of Signals and Systems (LSS)-SUPELEC, Université de Paris XI, France, in 1999. From 2008 to 2012, he was a Principal Scientist with the Power Electronics Group, ABB Switzerland Ltd., Zürich, Switzerland. He is currently a Professor-Researcher with the School of Engineering and Sciences, Tecnológico de Monterrey, Nuevo Leon, Mexico. His research

interests include modeling, analysis, and control design of power electronic systems, and their applications. He is a member of the National Research Fellows System level 3 (SNI-3), CONAHCyT, Mexico. He was an Associate Editor (AE) of IEEE Transactions on Industrial Electronics from 2007 to 2016. He has been an AE of IEEE Transactions on Power Electronics since 2013.

JESUS E. VALDEZ-RESENDIZ (Senior Member, IEEE) received the M.Eng. degree in electrical engineering from the Instituto Tecnológico de Ciudad Madero, Madero, Mexico, in 2011, and the Ph.D. degree in electronics engineering from the Centro Nacional de Investigación y Desarrollo Tecnológico, Cuernavaca, Mexico, in 2016. From 2016 to 2017, he was a Postdoctoral Fellow with the Tecnológico de Monterrey, Monterrey, Mexico, where he is currently an Assistant Pro-

fessor of electrical engineering. His research interests include power electronics, energy management, energy conversion, and electric vehicles. He is a member of the National Research Fellows System level 1 (SNI-1), CONAHCyT, Mexico. He is also an Associate Editor of the *Mathematical Problems in Engineering* and the *International Transactions on Electrical Energy Systems* and the Chair of the professional chapter of IEEE Power Electronics Society (PELS) in the Monterrey section.

JORGE L. LOPEZ-SARABIA (Member, IEEE) received the degree in mechatronics engineering from Universidad Modelo, Merida, Yucatan, Mexico, in 2018, and the M.Sc. degree in energy engineering and the Ph.D. degree in engineering sciences from Tecnológico de Monterrey, Monterrey, Nuevo Leon, Mexico, in 2019 and 2024, respectively. His research interests include modeling, analysis, and control of power electronic systems, and their applications in renewable energy systems.

JONATHAN C. MAYO-MALDONADO (Senior Member, IEEE) received the Ph.D. degree in electrical and electronic engineering from the University of Southampton, U.K., in 2015. He is currently a Lecturer of electrical machines and drives with The University of Sheffield, U.K. His research interests include system and control theory and power electronics and their applications in distribution networks and renewable energy integration. He is a member of the National

Research Fellows System in Mexico. He was awarded with the Doctoral Control and Automation Dissertation Prize 2015 by the Institute of Engineering and Technology (IET), for his thesis entitled Switched Linear Differential Systems.

• •