## University of Southampton Research Repository

Copyright © and Moral Rights for this thesis and, where applicable, any accompanying data are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis and the accompanying data cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content of the thesis and accompanying research data (where applicable) must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holder/s.

When referring to this thesis and any accompanying data, full bibliographic details must be given, e.g.

Thesis: Zhang Yue (2025) "Advancing Logic Locking: A New Strategy Combining Dynamic and Zero-Knowledge Techniques", University of Southampton, name of the University Faculty or School or Department, PhD Thesis, pagination.

Data: Zhang Yue (2025)

# Research Thesis: Declaration of Authorship

Print name: Yue Zhang

Title of thesis: Advancing Logic Locking: A New Strategy Combining Dynamic and Zero-Knowledge Techniques

I declare that this thesis and the work presented in it is my own and has been generated by me as the result of my own original research.

I confirm that:

1. This work was done wholly or mainly while in candidature for a research degree at this University;

2. Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

3. Where I have consulted the published work of others, this is always clearly attributed;

4. Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

5. I have acknowledged all main sources of help;

6. Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

7. Parts of this work have been published as:

Y. Zhang, B. Halak and H. Wang, ZeKi: A Zero-Knowledge Dynamic Logic Locking Implementation with Resilience to Multiple Attacks, 2024 IEEE 37th International System-on-Chip Conference (SOCC), Dresden, Germany, 2024, pp. 1-6, doi: 10.1109/SOCC62300.2024.10737800.

Signature:

Date: 2026-02-02

UNIVERSITY OF SOUTHAMPTON

# **Advancing Logic Locking: A New Strategy Combining Dynamic and Zero-Knowledge Techniques**

by

Zhang Yue   ORCID: 0009-0002-9275-1989

Supervisor: Dr Basel Halak

A thesis submitted in partial fulfillment for the

degree of Doctor of Philosophy

in the

Faculty of Engineering, Science and Mathematics

School of Electronics and Computer Science

January 2026

## Abstract

The IC industry's growth has heightened attention to hardware security, particularly in the last decade. Major IC companies, aiming to cut costs, have begun outsourcing parts of their supply chain instead of managing it entirely in-house. This cost-saving strategy increases vulnerability to malicious attacks. To counter this, various defence mechanisms like logic locking have been proposed, offering protection against unauthorized IP access and supply chain threats with minimal design flow alterations.

Despite logic locking's many advantages in hardware defence, it confronts two major challenges. Firstly, significant efforts in the field have aimed at extracting secret keys from encrypted designs, particularly to clone IP. The SAT attack [1] notably undermines the efficacy of logic locking. To mitigate this, various techniques like point function-based logic locking (PFB) [2, 3, 4] have emerged, balancing SAT attack resilience with minimal product overhead. However, PFB's fixed mechanism inherently exposes specific properties, making it vulnerable to targeted attacks. [5, 6] Secondly, traditional logic locking presumes the design house's trustworthiness. However, internal malicious actors are a real threat in practice, against which current logic locking methods are ineffective.

This thesis introduces Dynamic Logic Locking (DLL), a new logic locking strategy to address the aforementioned security concerns. DLL's dynamic mechanism, unlike traditional methods, uses randomly generated locking blocks to counter SAT and other logic locking attacks. Its unique mechanism for each design eliminates structural vulnerabilities, unlike conventional fixed-mechanism blocks. Moreover, DLL's random block generation allows for zero-knowledge implementation by designers, who need not know the block's structure or secret key details. This makes DLL robust even against internal malicious attacks within the design house.

This thesis also introduces DLL-se, a sequential variant of DLL, expanding its application to sequential circuits for increased utility. Additionally, it presents a Python-based logic locking tool capable of integrating various logic locking types, including DLL, into Verilog netlists and simulating attacks on logic locking. With its clear GUI, the tool is accessible to designers and students and is suitable for hardware design and educational research.

# Contents

|                         |                                                            |           |

|-------------------------|------------------------------------------------------------|-----------|

| <b>Acknowledgements</b> | <b>13</b>                                                  |           |

| <b>1</b>                | <b>Introduction</b>                                        | <b>1</b>  |

| 1.1                     | Problem Statement . . . . .                                | 2         |

| 1.1.1                   | Hardware Security Threats and Defence Techniques . . . . . | 2         |

| 1.1.1.1                 | Watermarking and fingerprinting . . . . .                  | 3         |

| 1.1.1.2                 | Camouflaging . . . . .                                     | 3         |

| 1.1.1.3                 | Split Manufacturing . . . . .                              | 4         |

| 1.1.1.4                 | Logic Locking . . . . .                                    | 4         |

| 1.1.2                   | Basic Working Principle of Logic Locking . . . . .         | 7         |

| 1.1.3                   | Threat Model in Attacks on Logic Locking . . . . .         | 7         |

| 1.1.4                   | Existing Challenges . . . . .                              | 8         |

| 1.1.4.1                 | Limitation of Single Locking Mechanism . . . . .           | 8         |

| 1.1.4.2                 | Insider Threat . . . . .                                   | 8         |

| 1.1.4.3                 | Easy-to-use Simulation Tool . . . . .                      | 9         |

| 1.2                     | Motivation . . . . .                                       | 9         |

| 1.3                     | Research Objectives . . . . .                              | 10        |

| 1.4                     | Contributions of This Project . . . . .                    | 11        |

| 1.5                     | General Structure of the Thesis . . . . .                  | 11        |

| 1.6                     | Publication during PhD . . . . .                           | 13        |

| <b>2</b>                | <b>Literature Review</b>                                   | <b>15</b> |

| 2.1                     | Introduction . . . . .                                     | 15        |

| 2.2                     | Pre-SAT Logic Locking and sensitisation Attack . . . . .   | 16        |

| 2.2.1                   | Random Logic Locking(RLL) . . . . .                        | 16        |

| 2.2.2                   | Fault-analysis based logic locking(FLL) . . . . .          | 17        |

| 2.2.3                   | sensitisation attack . . . . .                             | 18        |

| 2.2.4                   | Strong Logic Locking . . . . .                             | 20        |

| 2.3                     | SAT Attack . . . . .                                       | 21        |

| 2.3.1                   | SAT Attack Background Knowledge . . . . .                  | 21        |

| 2.3.1.1                 | Boolean Satisfiability (SAT) problem . . . . .             | 21        |

| 2.3.1.2                 | Miter Circuit . . . . .                                    | 21        |

| 2.3.2                   | Working Principle of SAT Attack . . . . .                  | 21        |

| 2.3.2.1                 | Attack Algorithm . . . . .                                 | 22        |

| 2.3.2.2                 | An Simple Example of SAT Attack . . . . .                  | 24        |

| 2.3.2.3                 | SAT Attack Discussion . . . . .                            | 24        |

| 2.4                     | Post-SAT Logic Locking Strategies . . . . .                | 25        |

|          |                                                                                                        |           |

|----------|--------------------------------------------------------------------------------------------------------|-----------|

| 2.4.1    | Point-Function Based Logic Locking . . . . .                                                           | 25        |

| 2.4.1.1  | SARLock . . . . .                                                                                      | 26        |

| 2.4.1.2  | Anti-SAT . . . . .                                                                                     | 27        |

| 2.4.1.3  | ANDTree . . . . .                                                                                      | 29        |

| 2.4.1.4  | TTLock . . . . .                                                                                       | 31        |

| 2.4.1.5  | SFLL . . . . .                                                                                         | 32        |

| 2.4.2    | FSM/Sequential Logic Locking . . . . .                                                                 | 33        |

| 2.4.2.1  | Working Principle . . . . .                                                                            | 33        |

| 2.4.2.2  | Advantages . . . . .                                                                                   | 34        |

| 2.4.2.3  | Disadvantages . . . . .                                                                                | 35        |

| 2.4.2.4  | Corresponding Attacks . . . . .                                                                        | 35        |

| 2.4.2.5  | Summary . . . . .                                                                                      | 35        |

| 2.4.3    | Cyclic-based Logic Locking . . . . .                                                                   | 35        |

| 2.4.3.1  | Working Principle . . . . .                                                                            | 35        |

| 2.4.3.2  | Advantages . . . . .                                                                                   | 36        |

| 2.4.3.3  | Disadvantages . . . . .                                                                                | 36        |

| 2.4.3.4  | Corresponding Attacks . . . . .                                                                        | 36        |

| 2.4.3.5  | Summary . . . . .                                                                                      | 36        |

| 2.4.4    | Routing-based logic locking . . . . .                                                                  | 37        |

| 2.4.4.1  | Working Principle . . . . .                                                                            | 37        |

| 2.4.4.2  | Advantages . . . . .                                                                                   | 37        |

| 2.4.4.3  | Disadvantages . . . . .                                                                                | 38        |

| 2.4.4.4  | Corresponding Attacks . . . . .                                                                        | 38        |

| 2.4.4.5  | Summary . . . . .                                                                                      | 38        |

| 2.4.5    | Scan Chain Logic Locking . . . . .                                                                     | 38        |

| 2.4.6    | Other Logic Locking Techniques . . . . .                                                               | 40        |

| 2.4.6.1  | Working Principle . . . . .                                                                            | 40        |

| 2.5      | ML-Based Attacks . . . . .                                                                             | 43        |

| 2.6      | Summary . . . . .                                                                                      | 44        |

| 2.6.1    | Logic Locking Strategies Comparison . . . . .                                                          | 44        |

| <b>3</b> | <b>ZeKi: A Zero-Knowledge Dynamic Logic Locking Implementation with Resilience to Multiple Attacks</b> | <b>47</b> |

| 3.1      | Motivation . . . . .                                                                                   | 48        |

| 3.1.1    | Logic Locking Strategies Comparison . . . . .                                                          | 49        |

| 3.1.1.1  | Vulnerability of PFB . . . . .                                                                         | 50        |

|          | Untrusted Insider . . . . .                                                                            | 53        |

| 3.2      | Contribution . . . . .                                                                                 | 53        |

| 3.3      | Working Principle of Zeki . . . . .                                                                    | 54        |

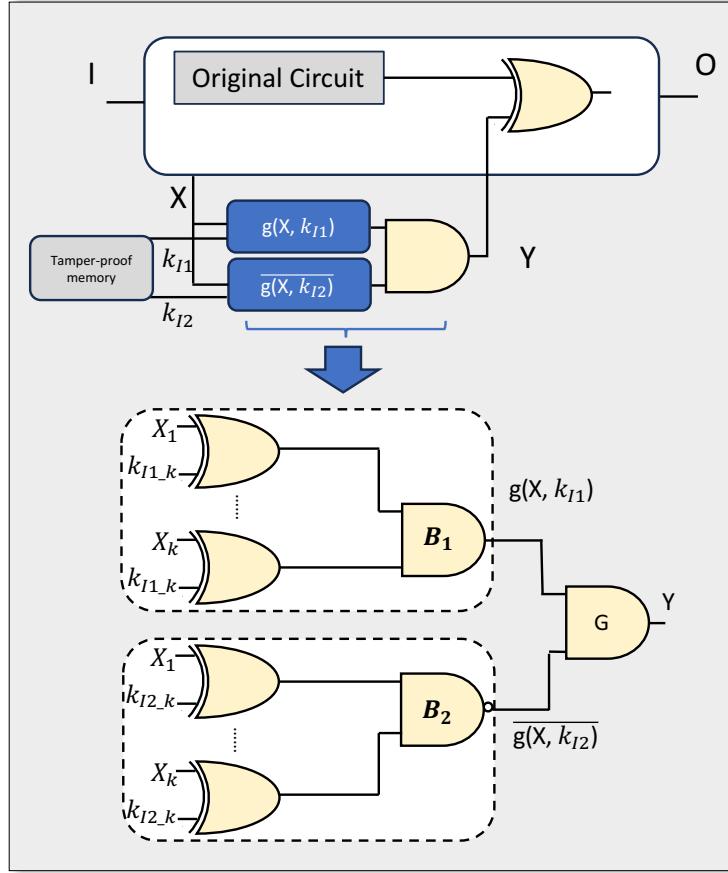

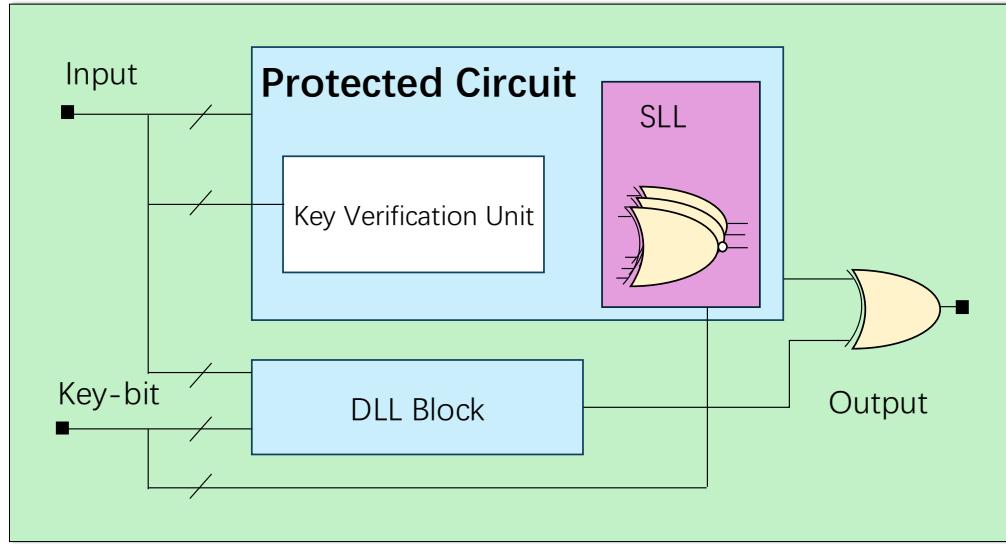

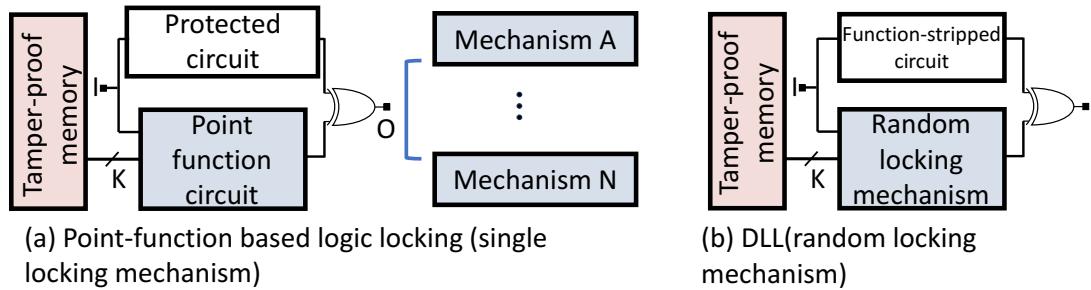

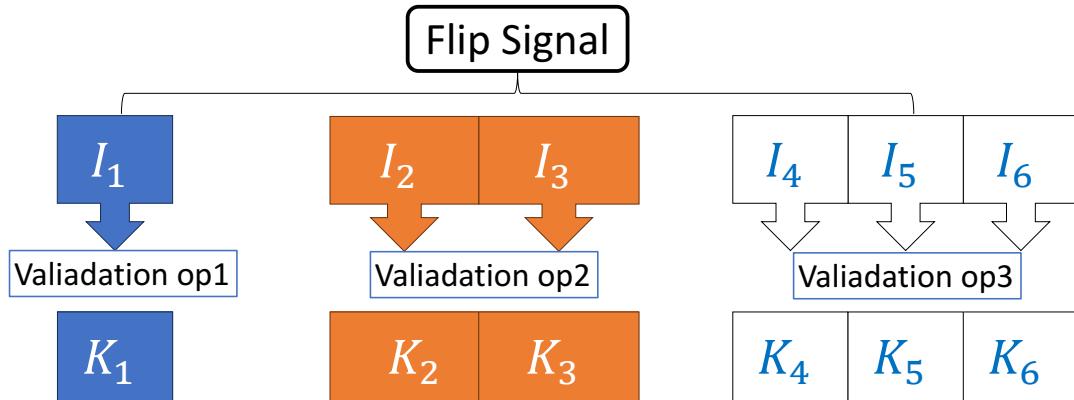

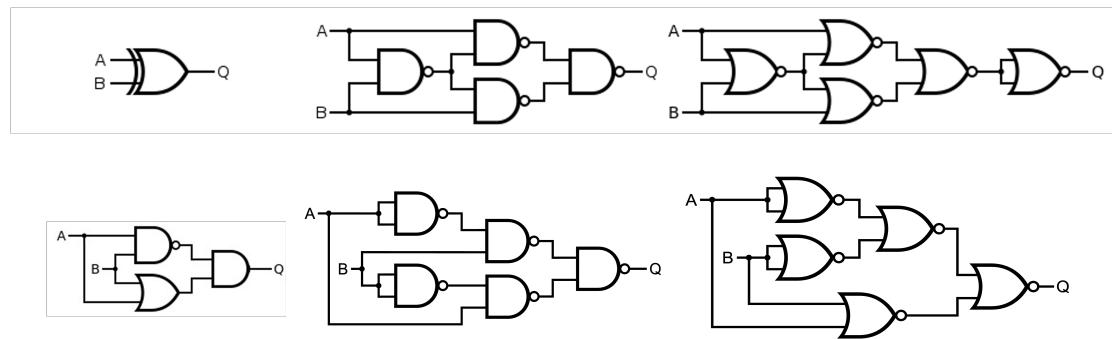

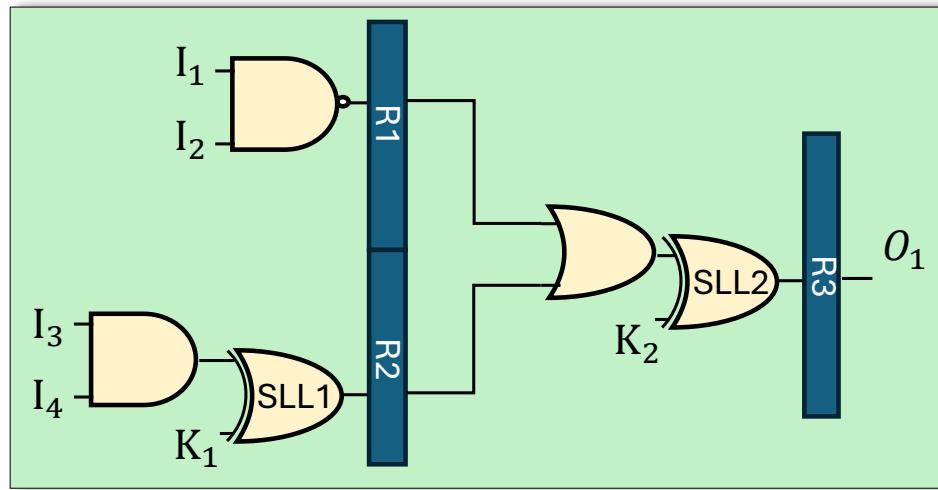

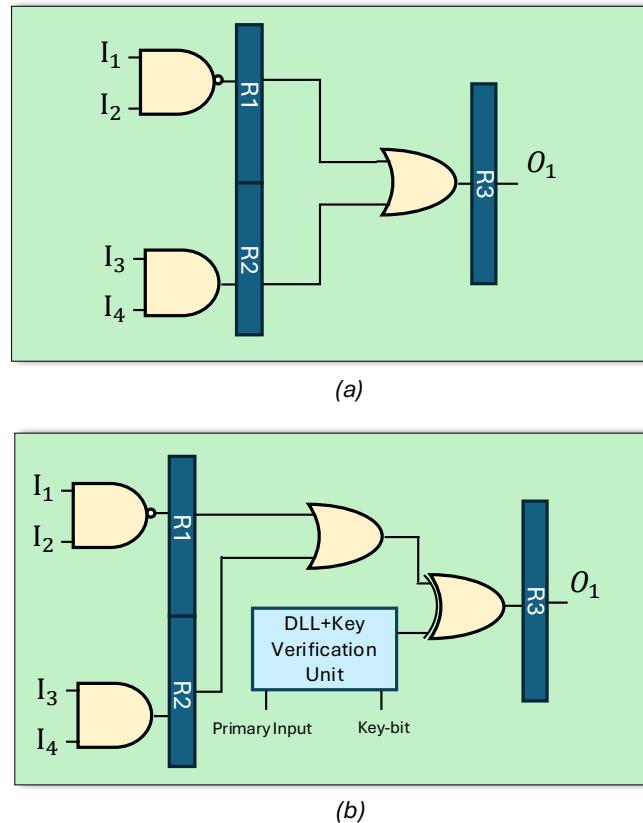

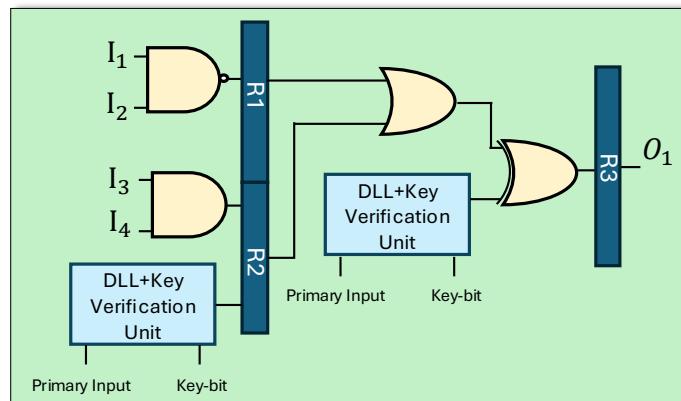

| 3.3.1    | Dynamic Logic Locking . . . . .                                                                        | 55        |

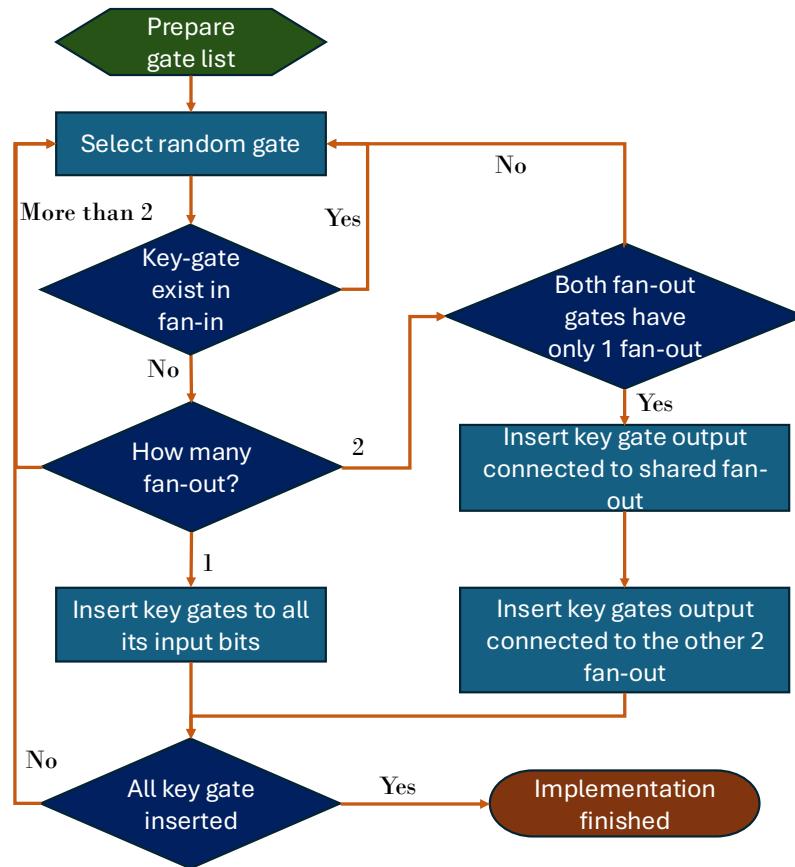

| 3.3.2    | Strong Logic Locking (SLL) Insertion . . . . .                                                         | 59        |

| 3.3.3    | Key Verification Unit . . . . .                                                                        | 60        |

| 3.3.4    | Zero-Knowledge Locking Strategy . . . . .                                                              | 62        |

| 3.4      | Implementation of Zeki . . . . .                                                                       | 63        |

| 3.4.1    | Parameter Input . . . . .                                                                              | 63        |

| 3.4.2    | Implementation Flow of Zeki . . . . .                                                                  | 63        |

| 3.5      | Experiment Results and Discussion . . . . .                                                            | 65        |

|          |                                                                          |            |

|----------|--------------------------------------------------------------------------|------------|

| 3.5.1    | Experimental Setup . . . . .                                             | 65         |

| 3.5.2    | Resilience Against Multiple Attacks . . . . .                            | 65         |

| 3.5.2.1  | SAT attack resilience . . . . .                                          | 66         |

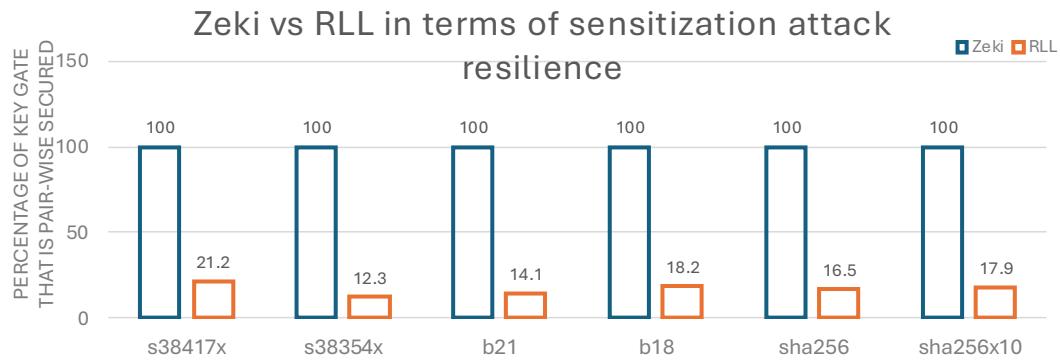

| 3.5.2.2  | Sensitisation attack resilience . . . . .                                | 68         |

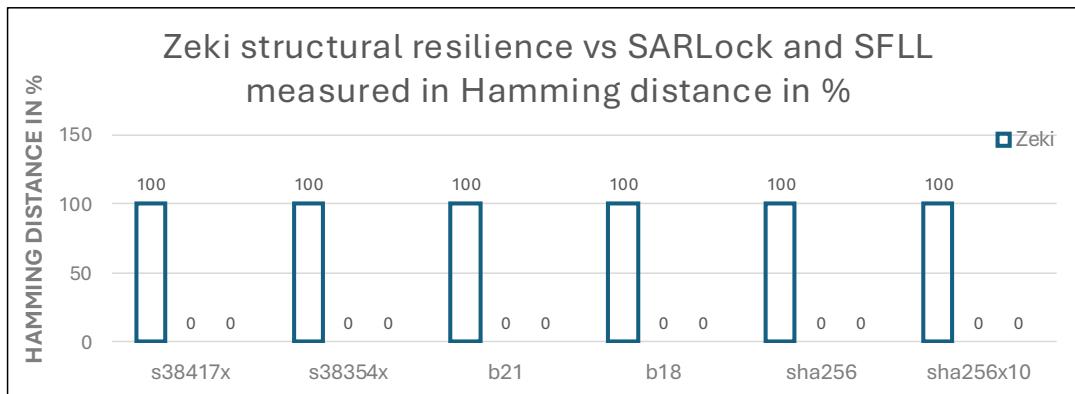

| 3.5.2.3  | Structural attack resilience. . . . .                                    | 70         |

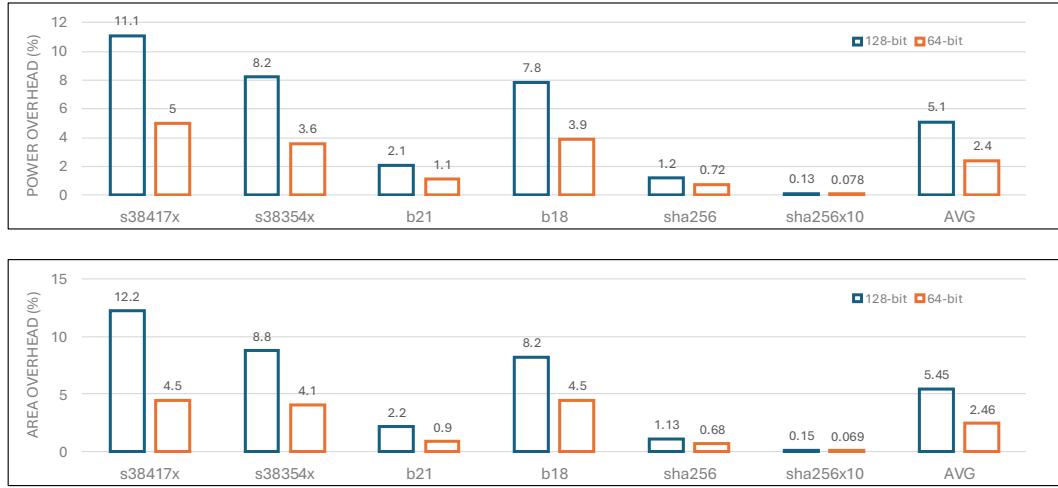

| 3.5.3    | Power, Delay, and Area overhead . . . . .                                | 71         |

| 3.6      | Summary . . . . .                                                        | 72         |

| <b>4</b> | <b>ZeKi: The Sequential version</b>                                      | <b>75</b>  |

| 4.1      | Implementation of SLL . . . . .                                          | 76         |

| 4.2      | ZekiA: Implement Zeki in Sequential Circuit in Single Stage . . . . .    | 77         |

| 4.3      | ZekiB: Implement Zeki in Sequential Circuit in Multiple Stages . . . . . | 80         |

| 4.4      | Power, Delay, and Area overhead . . . . .                                | 83         |

| 4.5      | Summary . . . . .                                                        | 85         |

| <b>5</b> | <b>LockLab</b>                                                           | <b>87</b>  |

| 5.1      | Contributions . . . . .                                                  | 88         |

| 5.2      | Introduction to LockLab . . . . .                                        | 89         |

| 5.3      | Netlist Parsing . . . . .                                                | 91         |

| 5.4      | Verilog-CNF Transformation . . . . .                                     | 92         |

| 5.4.1    | CNF transfer . . . . .                                                   | 93         |

| 5.4.2    | Tseitin Transformation . . . . .                                         | 94         |

| 5.5      | Locked circuit Self-test . . . . .                                       | 95         |

| 5.6      | Implementation of logic locking strategies . . . . .                     | 97         |

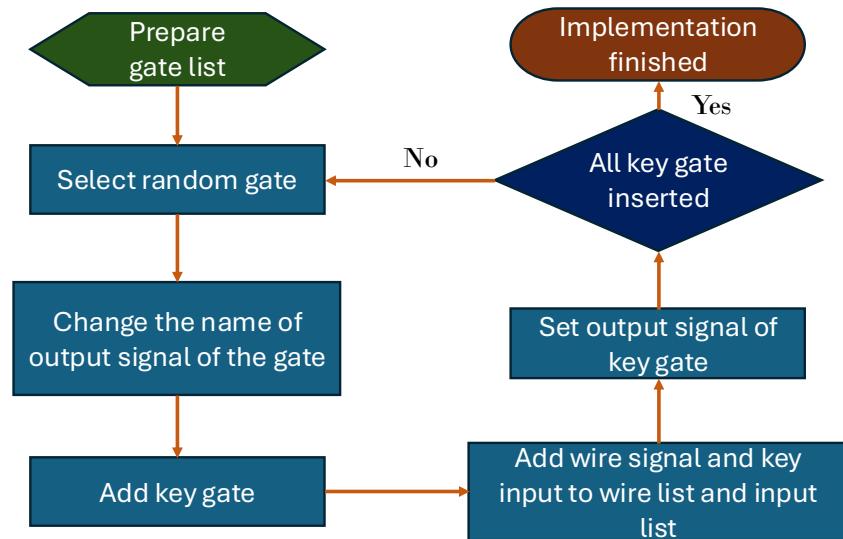

| 5.6.1    | Random Logic Locking (RLL) . . . . .                                     | 97         |

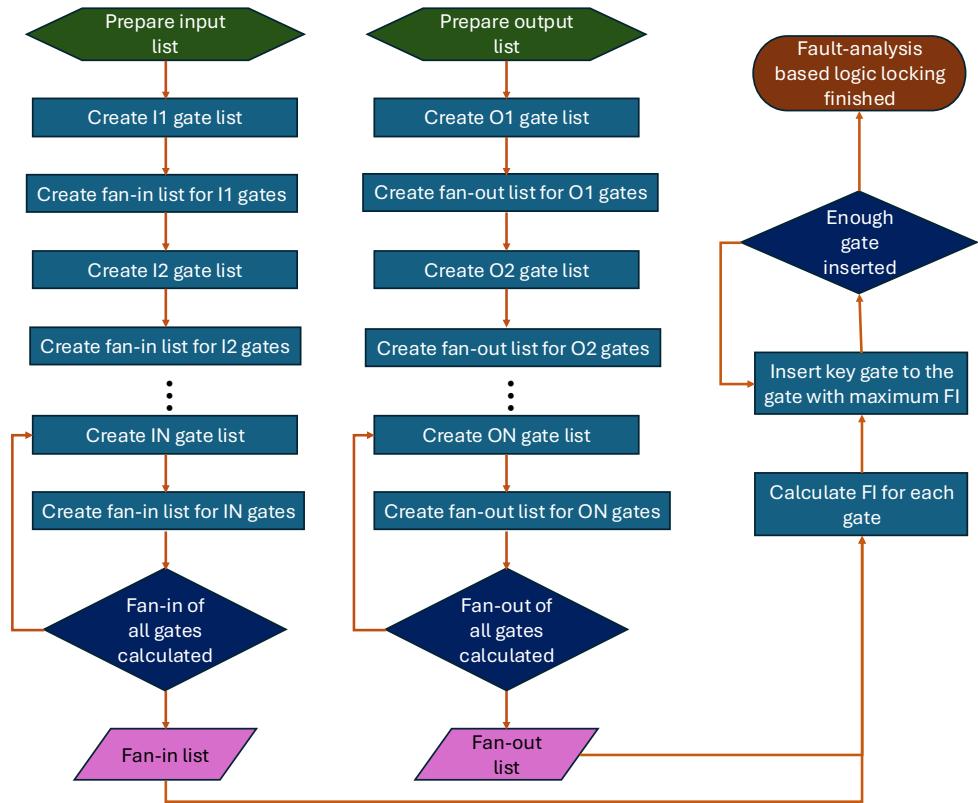

| 5.6.2    | Fault-based Logic Locking (FLL) . . . . .                                | 98         |

| 5.6.3    | Strong Logic Locking (SLL) . . . . .                                     | 100        |

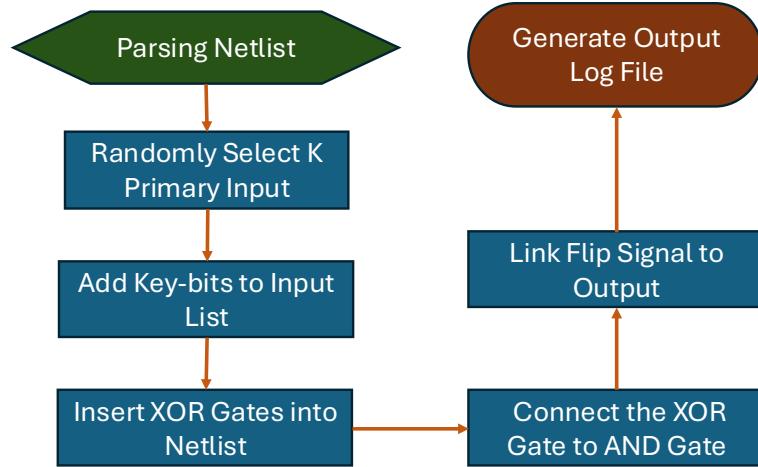

| 5.6.4    | SARLock . . . . .                                                        | 102        |

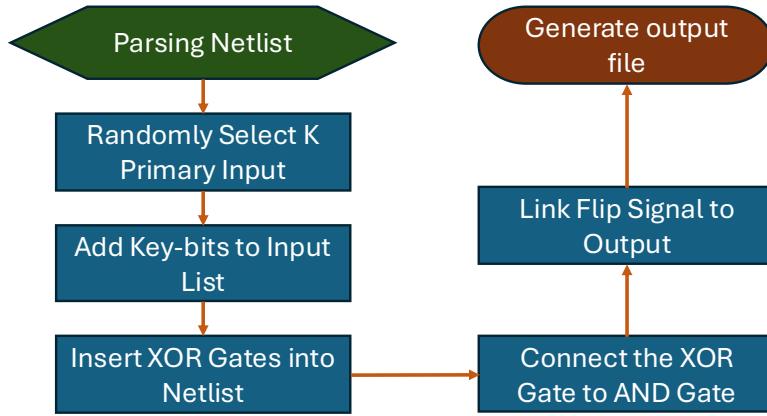

| 5.6.5    | AntiSAT . . . . .                                                        | 104        |

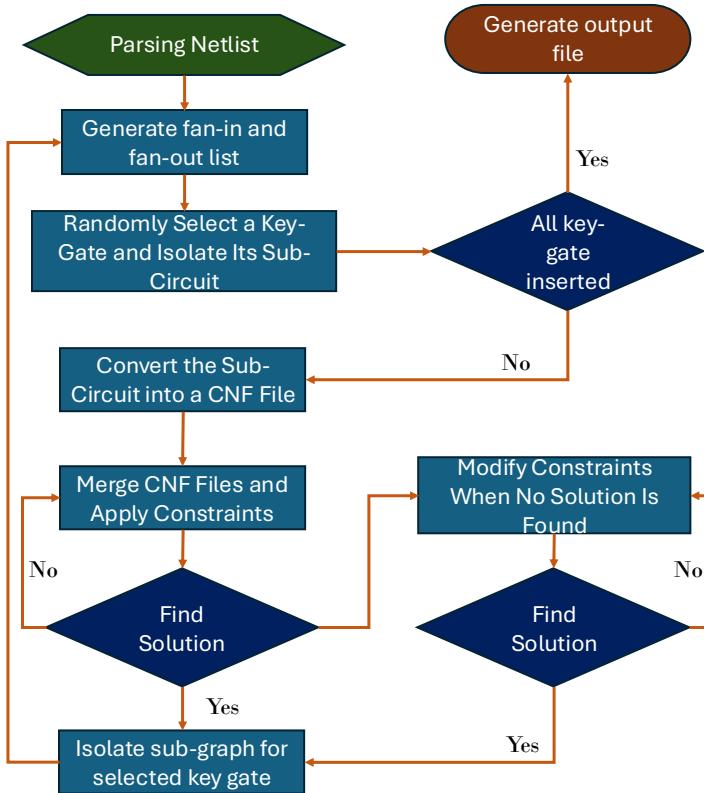

| 5.6.6    | SAT attack . . . . .                                                     | 105        |

| 5.6.6.1  | SAT-solver and Output File . . . . .                                     | 105        |

| 5.6.6.2  | Working Flow of SAT Attack . . . . .                                     | 105        |

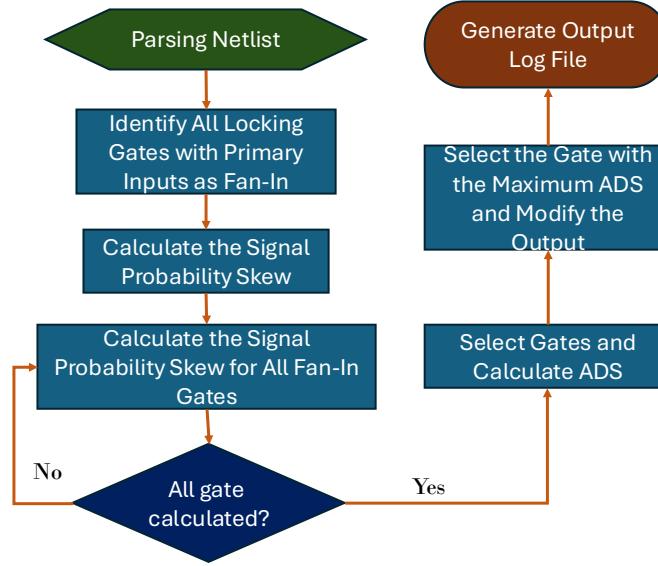

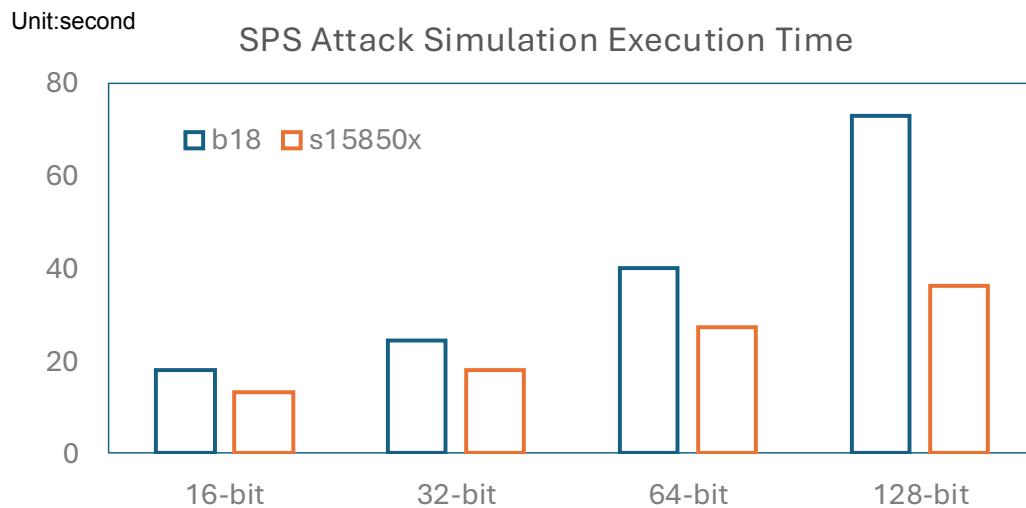

| 5.6.7    | SPS (Signal Probability Skew) Attack . . . . .                           | 107        |

| 5.6.8    | Sensitization Attack . . . . .                                           | 109        |

| 5.6.9    | AI-based Attack Evaluation . . . . .                                     | 110        |

| 5.6.10   | Zeki implementation . . . . .                                            | 112        |

| 5.7      | Summary . . . . .                                                        | 112        |

| <b>6</b> | <b>Conclusions</b>                                                       | <b>115</b> |

| 6.1      | Reflective Summary . . . . .                                             | 115        |

| 6.2      | Main Contributions . . . . .                                             | 116        |

| 6.2.1    | Chapter 3 . . . . .                                                      | 116        |

| 6.2.2    | Chapter 4 . . . . .                                                      | 116        |

| 6.2.3    | Chapter 5 . . . . .                                                      | 117        |

| 6.3      | Limitations and Future Work . . . . .                                    | 117        |

| 6.4      | Achievement of Objectives . . . . .                                      | 118        |

| 6.5      | Final Remarks and Broader Impact . . . . .                               | 119        |

|                                 |            |

|---------------------------------|------------|

| <b>A Source code of LockLab</b> | <b>121</b> |

| <b>Bibliography</b>             | <b>135</b> |

# List of Figures

|      |                                                                                                                                                                                                                                                                |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1  | Different Threat Models at Different Stages of IC Design Flow [7] . . . . .                                                                                                                                                                                    | 3  |

| 1.2  | IC Supply Chain, Threat Modelling, and Logic Locking Engagement (Injecting in Netlist and Activating after Fabrication) . . . . .                                                                                                                              | 4  |

| 1.3  | Logic Locking Examples at Different Levels of Abstraction: (a) Layout-level Key-based Routing, (b) Transistor-level Key-based Basic Gates, (c) Key-based Logic/Routing Gate-level, (d) RTL-level Keybased FSM, (e) HLS-level Key-based Shift Register. . . . . | 6  |

| 1.4  | Basic working principle of logic locking. . . . .                                                                                                                                                                                                              | 7  |

| 2.1  | Basic working principle of logic locking . . . . .                                                                                                                                                                                                             | 17 |

| 2.2  | sensitisation Attack . . . . .                                                                                                                                                                                                                                 | 19 |

| 2.3  | Strong logic locking . . . . .                                                                                                                                                                                                                                 | 20 |

| 2.4  | Miter Circuit . . . . .                                                                                                                                                                                                                                        | 22 |

| 2.5  | SAT attack flow chart [8] . . . . .                                                                                                                                                                                                                            | 23 |

| 2.6  | Circuit Sample for SAT Attack . . . . .                                                                                                                                                                                                                        | 23 |

| 2.7  | SARLock locking strategy . . . . .                                                                                                                                                                                                                             | 27 |

| 2.8  | Original circuit with Anti-SAT block and An instance of Anti-SAT circuit                                                                                                                                                                                       | 29 |

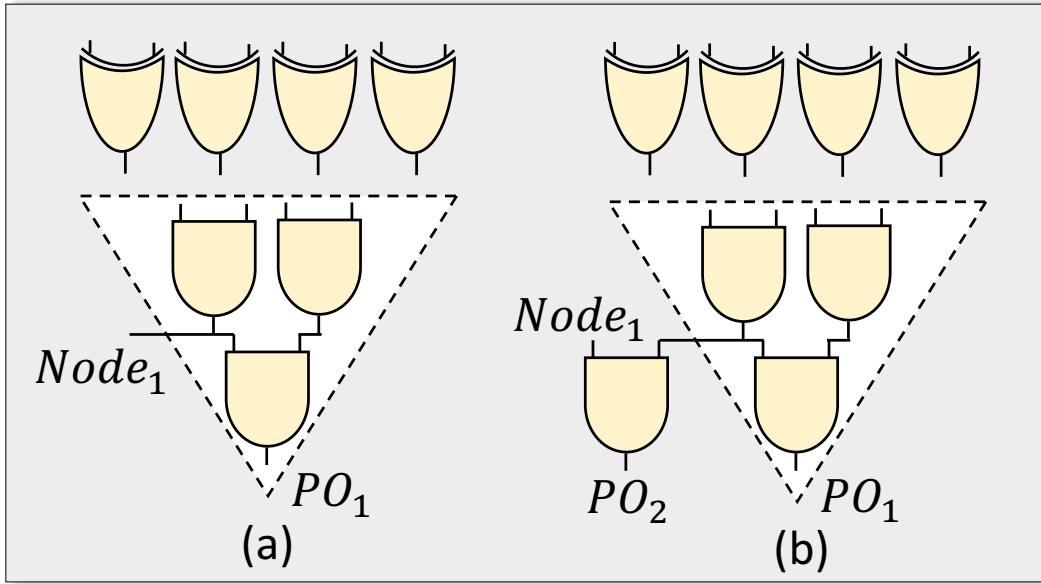

| 2.9  | (a) non-decomposable ANDTree (b) decomposable ANDTree . . . . .                                                                                                                                                                                                | 30 |

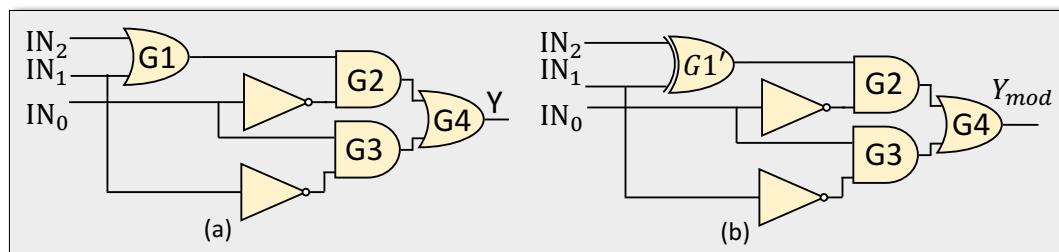

| 2.10 | (a) Original logic cone. (b) Modified logic cone . . . . .                                                                                                                                                                                                     | 31 |

| 2.11 | TTLock architecture and corresponding truth table . . . . .                                                                                                                                                                                                    | 32 |

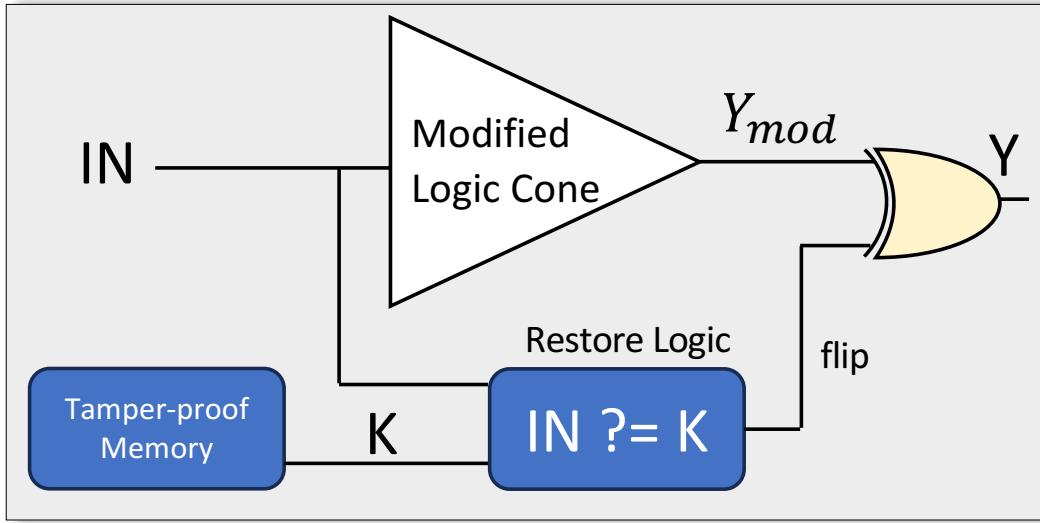

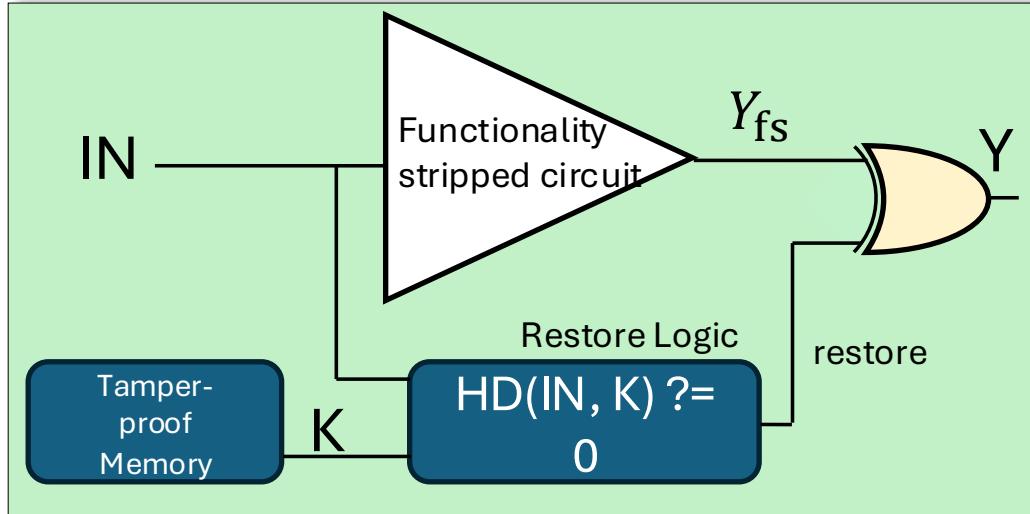

| 2.12 | SFLL architecture . . . . .                                                                                                                                                                                                                                    | 33 |

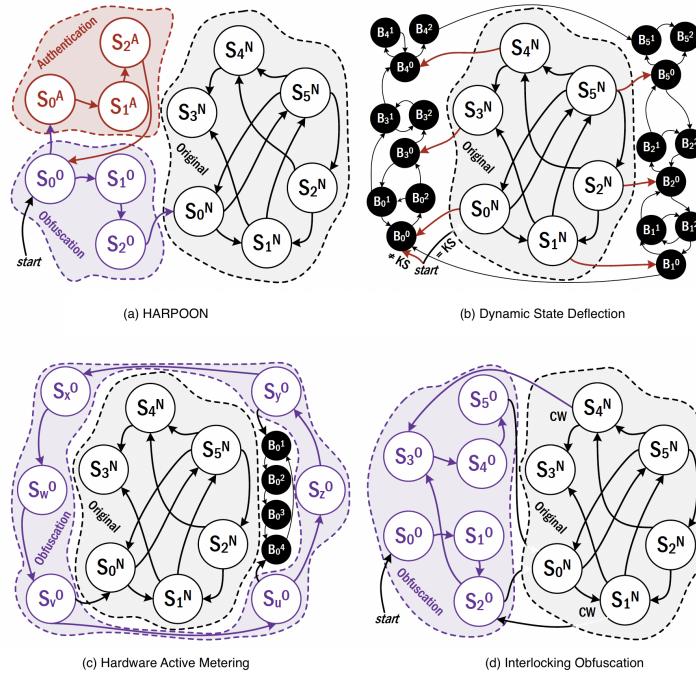

| 2.13 | Examples of FSM-based logic locking strategies [7] . . . . .                                                                                                                                                                                                   | 34 |

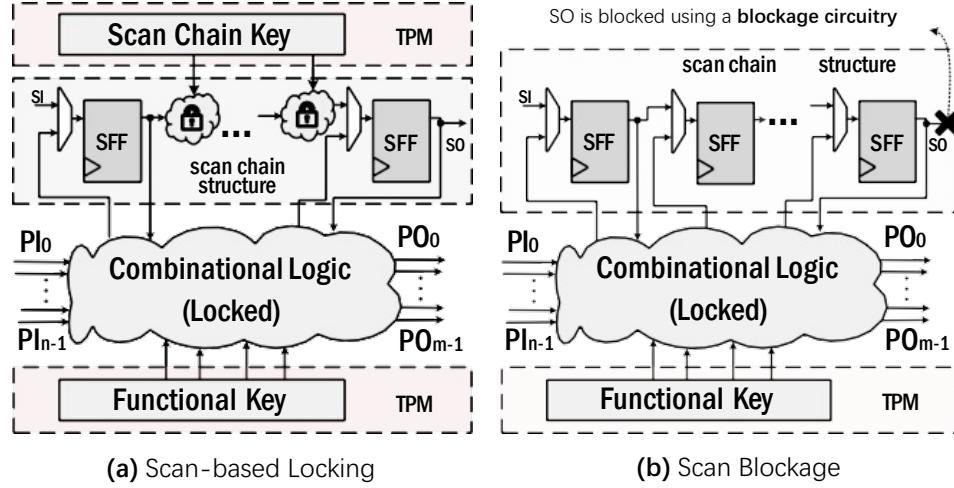

| 2.14 | LUT-based logic locking [7] . . . . .                                                                                                                                                                                                                          | 37 |

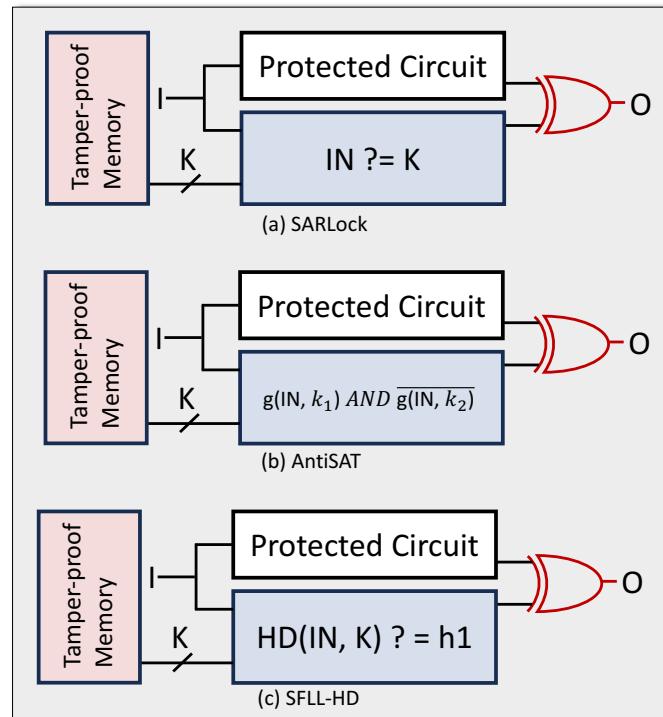

| 2.15 | An illustration of Scan Chain Logic Locking . . . . .                                                                                                                                                                                                          | 39 |

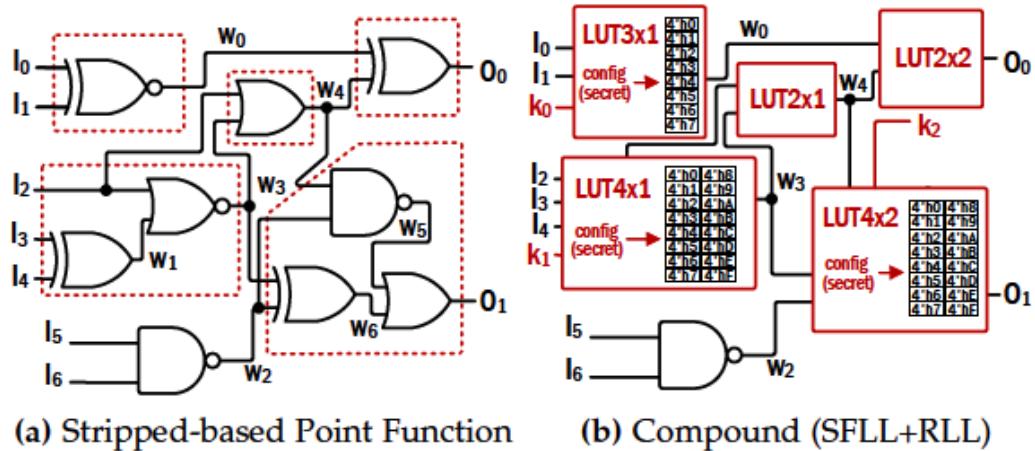

| 3.1  | PFB locking with Different Validation Mechanisms . . . . .                                                                                                                                                                                                     | 51 |

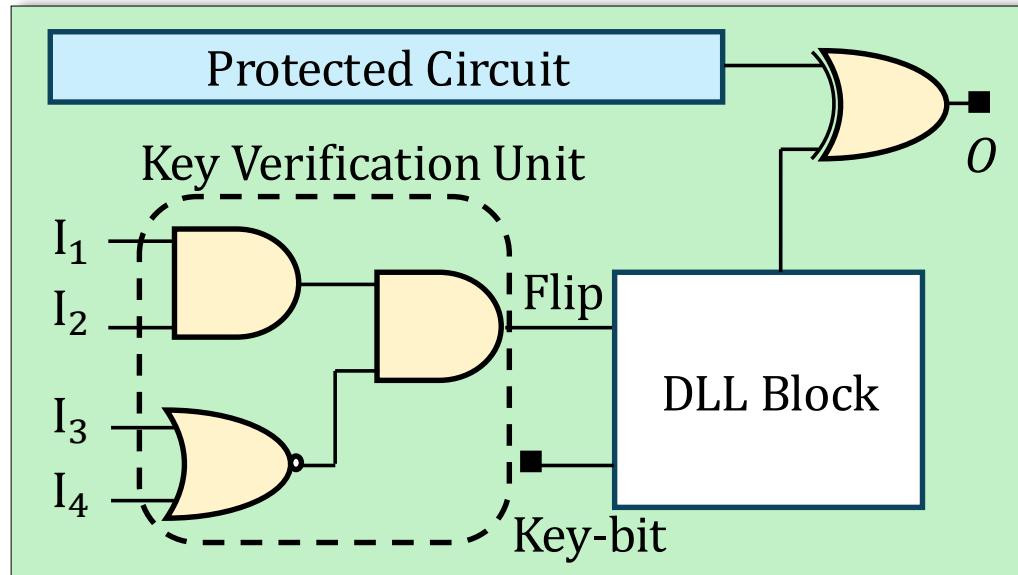

| 3.2  | Main Architecture of Zeki . . . . .                                                                                                                                                                                                                            | 55 |

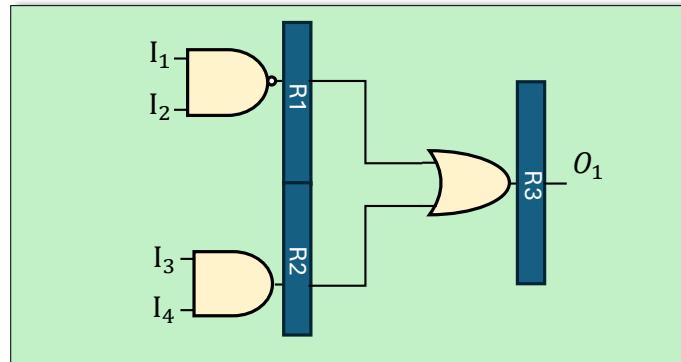

| 3.3  | Conventional PFB locking(a) vs DLL(b) . . . . .                                                                                                                                                                                                                | 55 |

| 3.4  | DLL breaks input/key sequence into chunks and assigns different validation operations to them. . . . .                                                                                                                                                         | 58 |

| 3.5  | Different implementation for XOR operation . . . . .                                                                                                                                                                                                           | 58 |

| 3.6  | Key Verification Unit . . . . .                                                                                                                                                                                                                                | 61 |

| 3.7  | DLL Block of Key Verification Unit . . . . .                                                                                                                                                                                                                   | 61 |

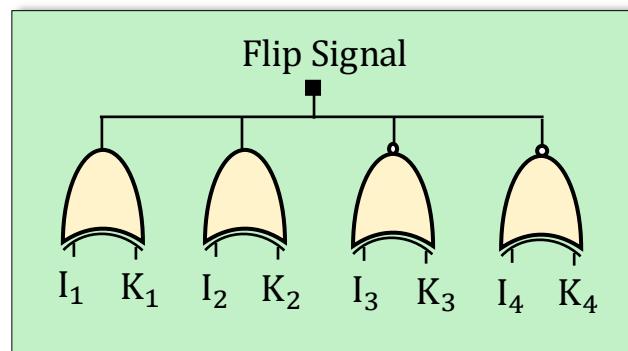

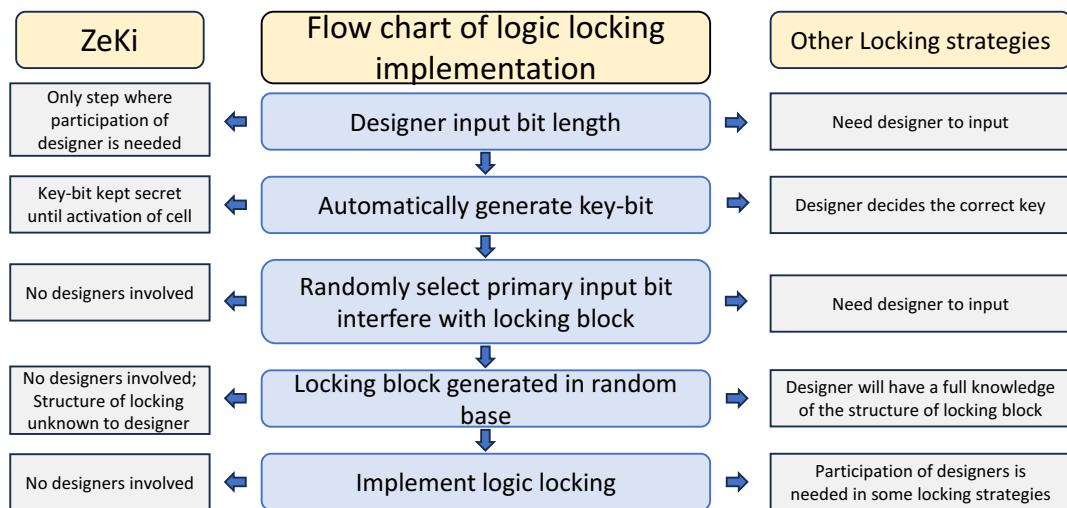

| 3.8  | Implementation flow: ZeKi versus Other Logic Locking . . . . .                                                                                                                                                                                                 | 62 |

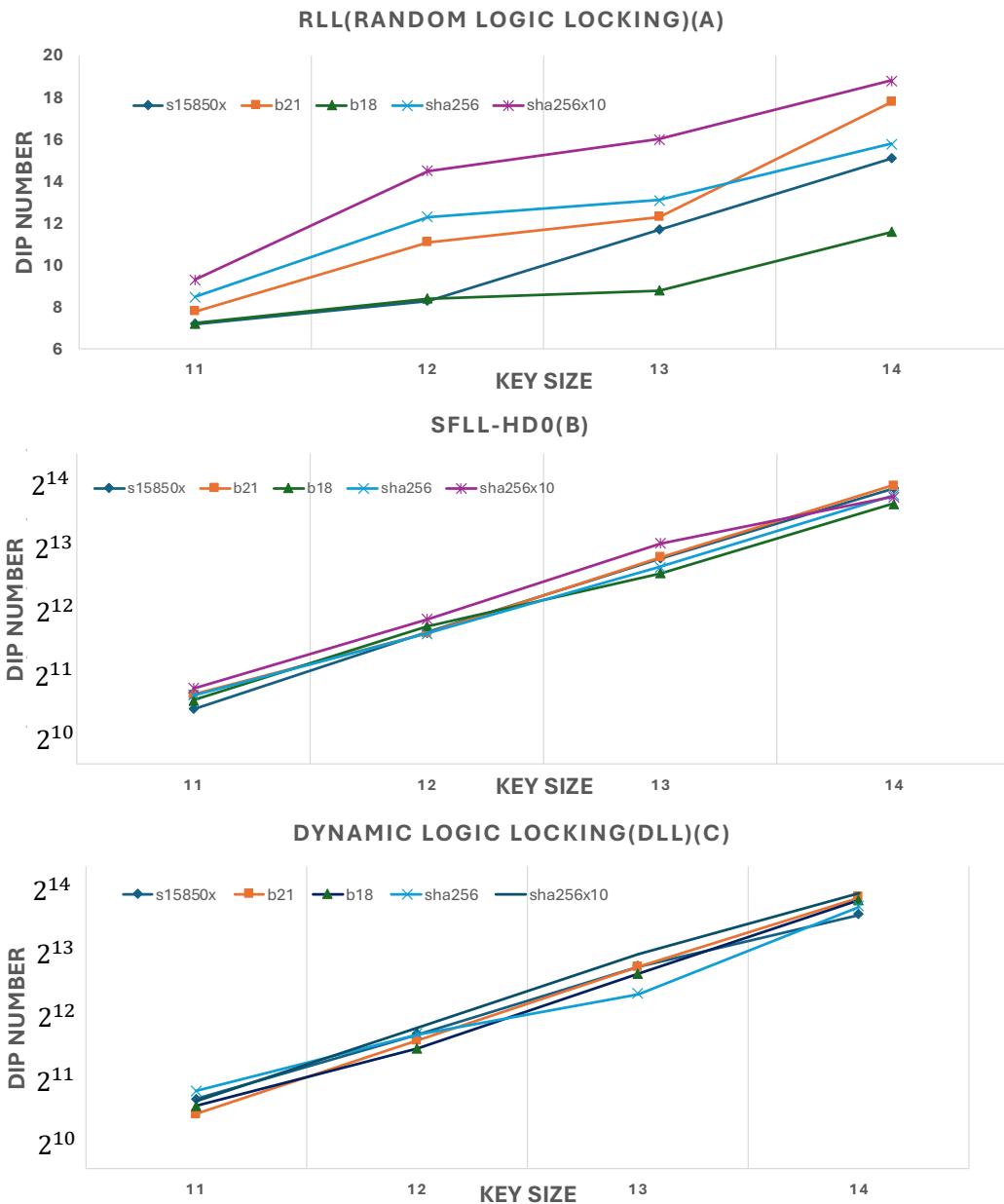

| 3.9  | SAT attack simulation on design locked with (a) RLL[9], (b) SFLL[3], (c)ZeKi's DLL. . . . .                                                                                                                                                                    | 66 |

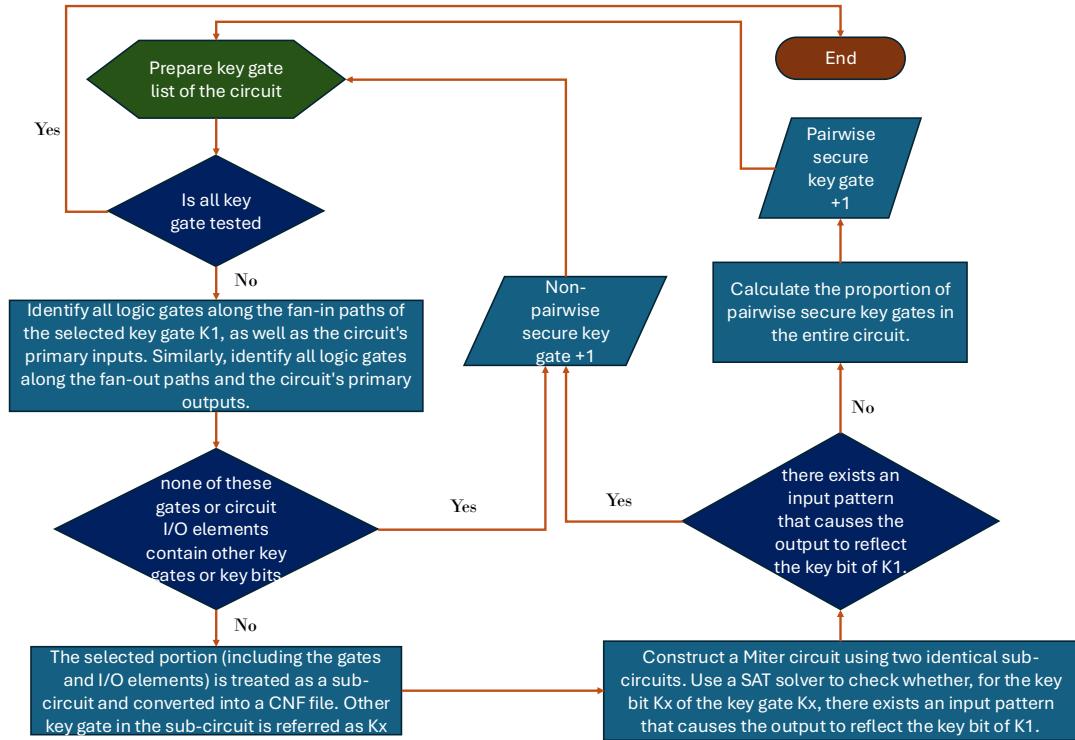

| 3.10 | Process diagram of sensitisation attack resilience simulation . . . . .                                                                                                                                                                                        | 69 |

| 3.11 | ZeKi sensitisation attack resilience vs RLL[9] . . . . .                                                                                                                                                                                                       | 70 |

|      |                                                                                                                                                                                             |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.12 | ZeKi structural attack resilience comparison with SARLock[4] and SFLL[3]                                                                                                                    | 71  |

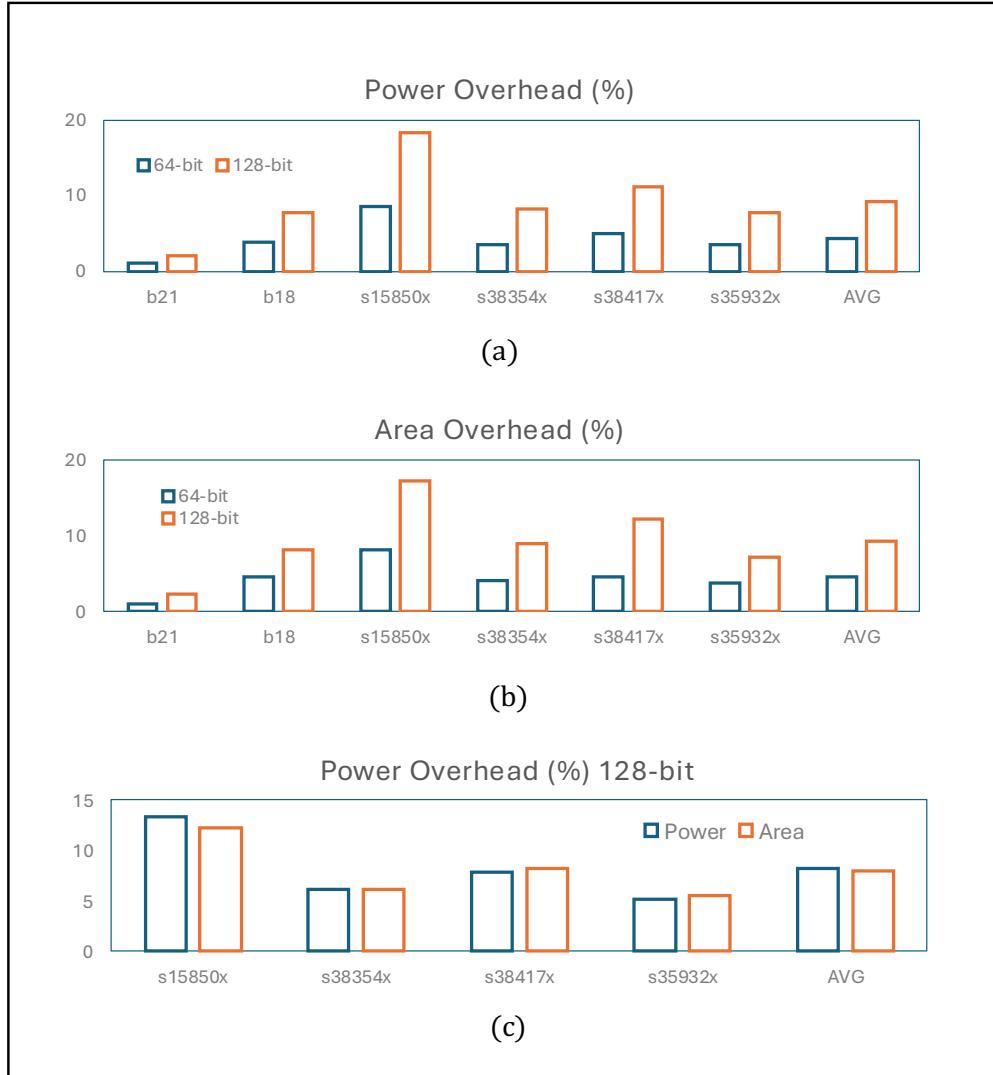

| 3.13 | Power, and Area overhead of DLL protected circuit with 64-bit and 128-bit key . . . . .                                                                                                     | 72  |

| 4.1  | Add SLL(strong logic locking) to Sequential Circuit . . . . .                                                                                                                               | 77  |

| 4.2  | (a) Original Circuit; (b) Circuit Locked with ZekiA . . . . .                                                                                                                               | 79  |

| 4.3  | (a) Original Circuit; (b) Circuit Locked with ZekiB . . . . .                                                                                                                               | 82  |

| 4.4  | Power, and Area overhead of DLL protected circuit with 64-bit and 128-bit key: (a) Power Overhead; (b) Area Overhead; (c) Power and Area Overhead of ZekiB Implemented Benchmarks . . . . . | 84  |

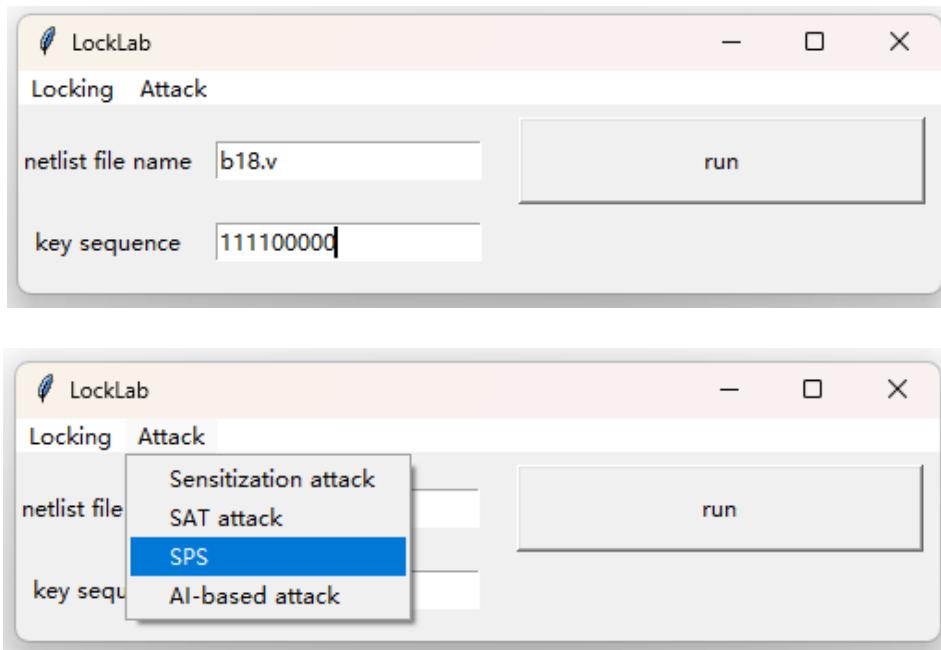

| 5.1  | GUI of LockLab . . . . .                                                                                                                                                                    | 90  |

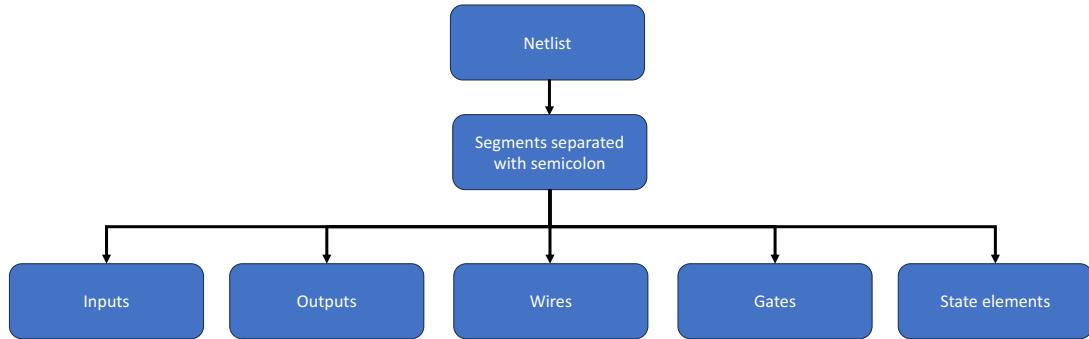

| 5.2  | Parsing process of the netlist [10] . . . . .                                                                                                                                               | 93  |

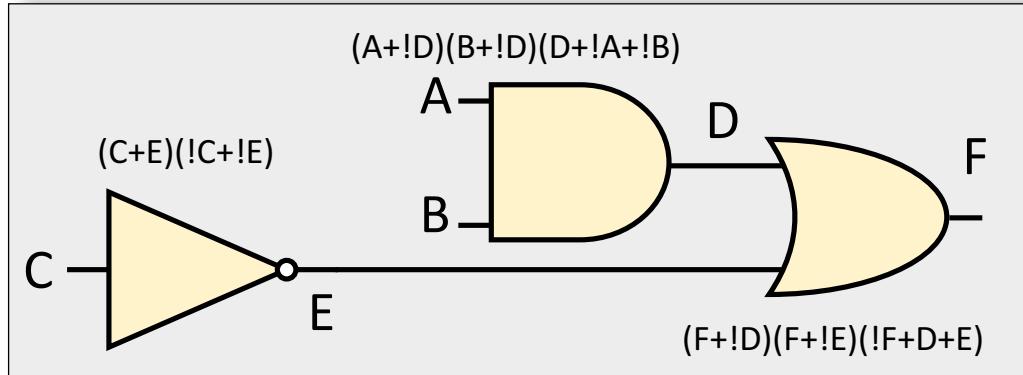

| 5.3  | Application of the Tseitin transformation to a circuit with three gates . . . . .                                                                                                           | 95  |

| 5.4  | Working Flow of RLL in LockLab . . . . .                                                                                                                                                    | 97  |

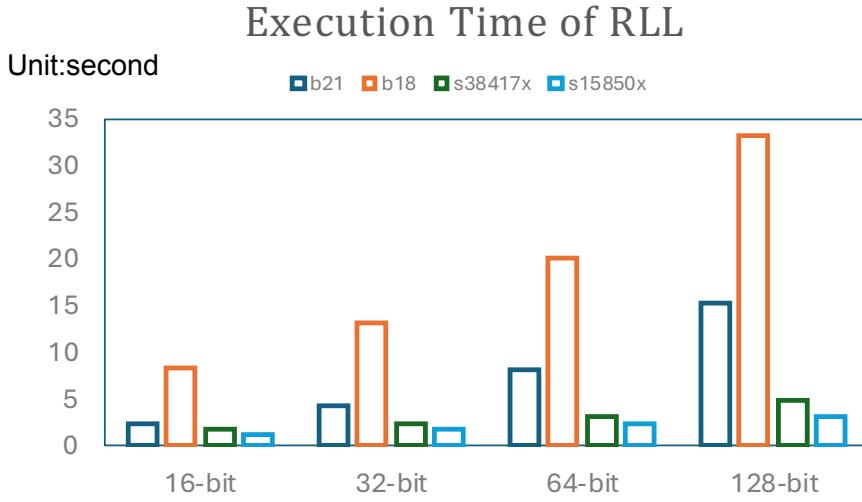

| 5.5  | Execution Time of RLL . . . . .                                                                                                                                                             | 98  |

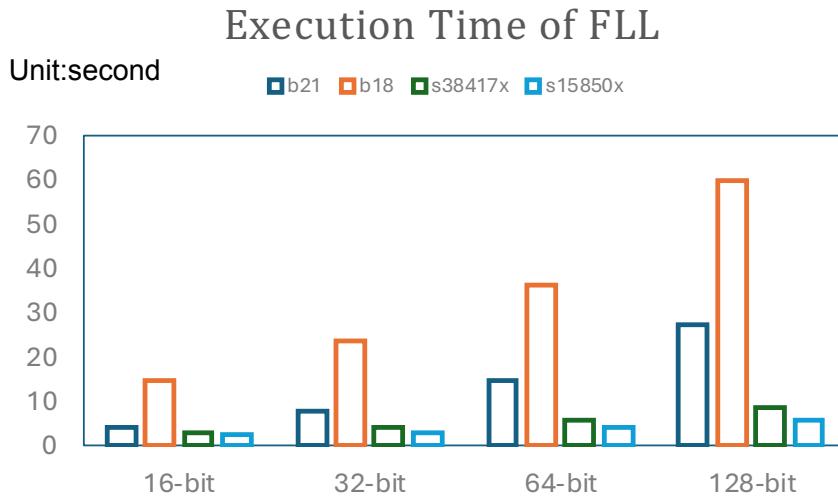

| 5.6  | Working Flow of FLL in LockLab . . . . .                                                                                                                                                    | 99  |

| 5.7  | Execution Time of FLL . . . . .                                                                                                                                                             | 100 |

| 5.8  | Working Flow of SLL in LockLab . . . . .                                                                                                                                                    | 101 |

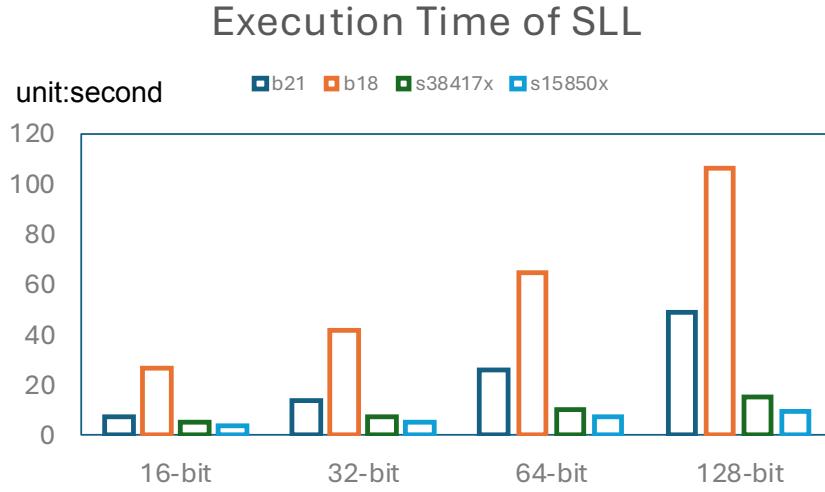

| 5.9  | Execution Time of SLL . . . . .                                                                                                                                                             | 102 |

| 5.10 | Working Flow of SARLock Simulation in LockLab . . . . .                                                                                                                                     | 103 |

| 5.11 | Execution Time of SARLock Simulation in LockLab . . . . .                                                                                                                                   | 103 |

| 5.12 | Working Flow of Anti-SAT Simulation in LockLab . . . . .                                                                                                                                    | 104 |

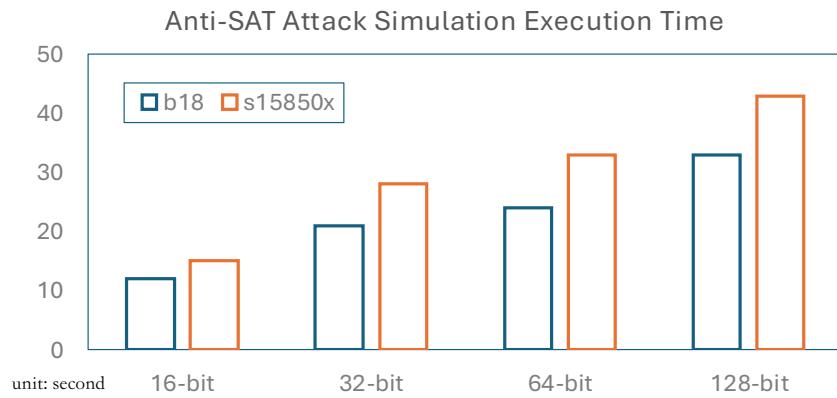

| 5.13 | Execution Time of Anti-SAT Simulation in LockLab . . . . .                                                                                                                                  | 104 |

| 5.14 | Working Flow of SPS Attack Simulation in LockLab . . . . .                                                                                                                                  | 108 |

| 5.15 | Execution Time of SPS Attack Simulation in LockLab . . . . .                                                                                                                                | 108 |

| 5.16 | Working Flow of Sensitization Attack Simulation in LockLab . . . . .                                                                                                                        | 109 |

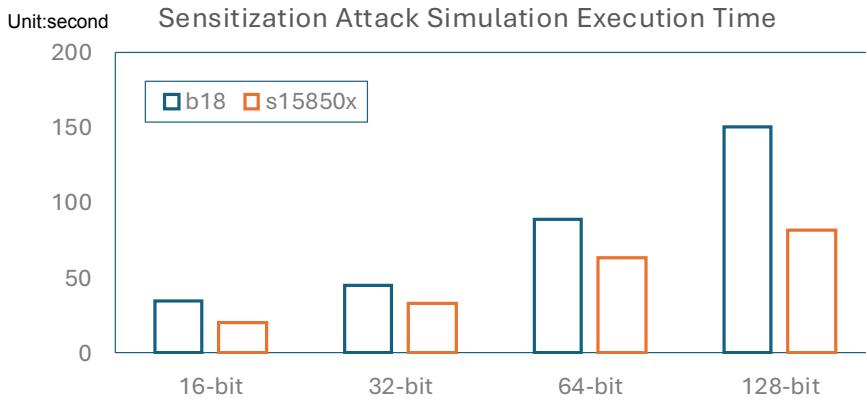

| 5.17 | Execution Time of Sensitization Attack Simulation in LockLab . . . . .                                                                                                                      | 110 |

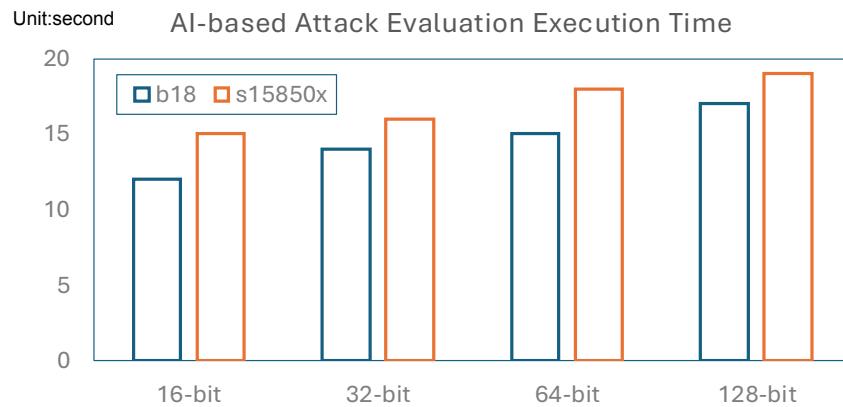

| 5.18 | Execution Time of AI-based Attack Evaluation in LockLab . . . . .                                                                                                                           | 111 |

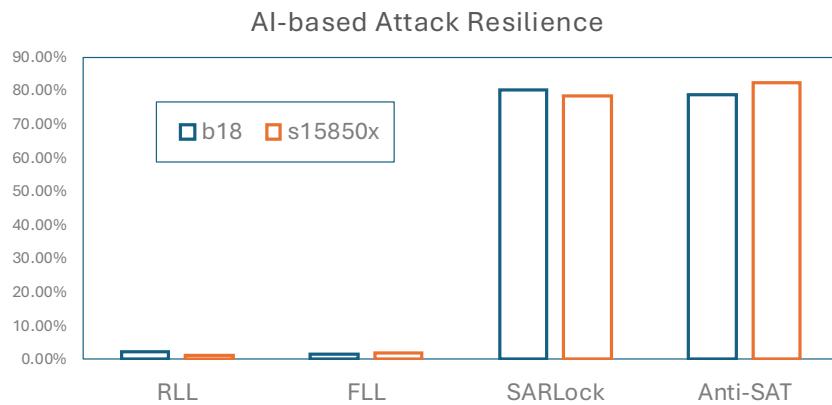

| 5.19 | AI-based Attack resilience of RLL, FLL, SARLock, and Anti-SAT . . . . .                                                                                                                     | 111 |

# List of Tables

|     |                                                                                                                               |     |

|-----|-------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.1 | Hardware defence strategies comparison                                                                                        | 5   |

| 2.1 | Output of circuit in Figure 2.1(3) with different key-bit when the input bit $x_1=0$ , $x_2=1$                                | 17  |

| 2.2 | SAT attack example (K0-K7 represent all the key bit combination (000, ..., 111) of the three key-bits, K1-K2-K3, combination) | 24  |

| 2.3 | TTlock truth table                                                                                                            | 31  |

| 2.4 | Merits and Drawbacks of Locking Strategies                                                                                    | 45  |

| 3.1 | Merits and Drawbacks of Locking Strategies                                                                                    | 50  |

| 3.2 | Benchmarks and corresponding time consumption to implement Zeki                                                               | 65  |

| 3.3 | Benchmarks and corresponding SAT-solver Running Time                                                                          | 67  |

| 4.1 | Area and Power Overhead                                                                                                       | 84  |

| 5.1 | CNF formulas for AND, NAND, OR, NOR, INV, BUFFER gates generated using the Tseitin transformation [8]                         | 94  |

| 5.2 | Benchmarks and corresponding time consumption to implement Zeki                                                               | 112 |

## **Acknowledgements**

I would like to begin by expressing my deepest gratitude to my supervisor, Dr. Basel, whose guidance, understanding, and constant support were instrumental in the completion of this PhD project. His mentorship has been invaluable, and I truly believe he is one of the best mentors in the world.

I am also immensely grateful to my parents for their endless love, which has been my driving force throughout this journey. I sincerely hope they continue to enjoy good health and live strong and happy lives.

I would like to give special thanks to my dear friend and brother, Dr. Wang Haoyu, who generously helped me in rewriting parts of my dissertation. His assistance, encouragement, and belief in me were pivotal to my progress.

Lastly, I would like to take a moment to acknowledge myself. Despite the challenges, I made it to the finish line. Only I truly understand the significance of this achievement. I am proud of the journey and the person I have become. Keep pushing forward.

# Chapter 1

## Introduction

Since the beginning of the 21st century, the Integrated Circuit (IC) supply chain has undergone significant transformations. These changes are reflected in various aspects: the rising cost and complexity of IC manufacturing, increasing operational and troubleshooting expenses of chip factories, the market's growing demand for rapid response, acceleration of supply chain processes, the involvement of multiple third-party Intellectual Property (IP) providers, the introduction of cutting-edge technologies, and the influence of maintaining a leading position in the semiconductor market [11]. These factors have collectively driven the horizontal development of the IC supply chain, where different entities are responsible for the design, manufacturing, testing, packaging, and integration stages, forming a globalised supply chain.

In this context of a globalised supply chain, to cope with the complexity of designing key chip components, design teams increasingly acquire third-party IPs from numerous owners to expedite product launches. Furthermore, considering the total cost of manufacturing, wafer sorting, cutting, packaging, and package testing, along with the necessity of employing the latest technologies, many design companies opt to complete these stages in overseas facilities. The involvement of outsourcing and multiple stakeholders not only reduces the cost of chips but also shortens their time to market.

Since the beginning of the 21st century, the rapid expansion of the chip market has led to a significant growth of semiconductors industry, while also dramatically increasing the market value of major manufacturers such as TSMC, UMC, and SMIC [11]. The surge in demand has driven Original Equipment Manufacturers (OEMs) to continuously

advance their technologies in design, implementation, manufacturing, and testing in order to remain competitive. At the same time, global collaboration has deepened significantly. The acceleration of globalisation has made the supply chain more open and efficient, improving overall productivity.

While globalisation of the supply chain has brought benefits, it has also increased risks. The involvement of multiple entities, lack of trust, and insufficient monitoring have decreased the control of original manufacturers and IP owners/suppliers over the supply chain, leading to various hardware security threats such as IP piracy, overproduction of ICs, and counterfeiting[12, 13]. Hardware security issues have become increasingly serious, thereby attracting growing attention in this field. There is much work to be done in this field to ensure that IC products are not plagiarized or attacked by malicious entities.

To counter the upcoming hardware threats, the academic community has proposed various design trust countermeasures, ranging from passive to active strategies, such as watermarking, IC metering, IC camouflaging, and hardware obfuscation[12, 13]. Particularly, *logic locking*, as an active IP protection technique, has garnered widespread attention over the past two decades, with robust solutions developed at various levels of abstraction.

The structure of this thesis is organised as follows: Section 1.1 presents the problem statement of this research. Section 1.2 outlines the motivation behind the study. Section 1.3 presents the main research objectives. Section 1.4 summarises the key contributions of this work. Section 1.5 provides an overview of the overall thesis structure. Finally, Section 1.6 lists the papers published by the author during this doctoral research.

## 1.1 Problem Statement

### 1.1.1 Hardware Security Threats and Defence Techniques

In today's complex integrated circuit (IC) supply chains, a wide range of security threats have emerged, creating significant challenges for both industry stability and technological integrity. The rapid expansion of these supply chains has introduced numerous security vulnerabilities. Key threats include intellectual property (IP) piracy [14], overbuilding

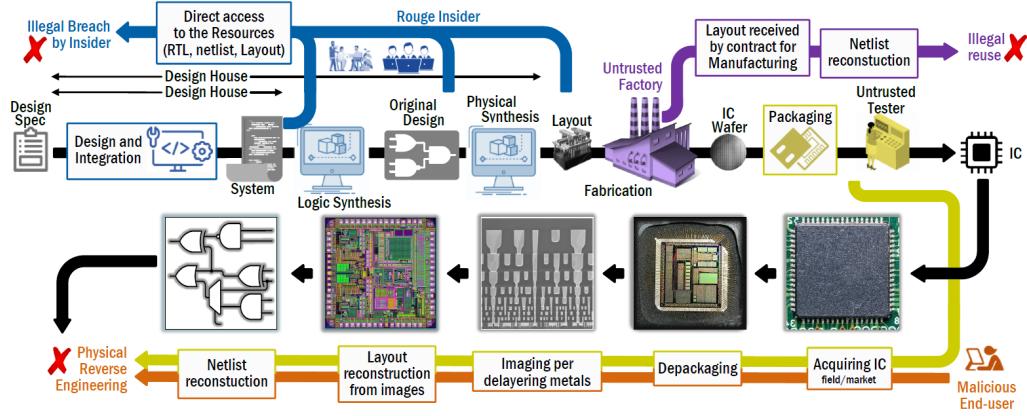

[15], hardware Trojans [16, 17, 18, 19], reverse engineering [20, 21], and counterfeiting [22, 23], whose potential threat is labeled in the supply chain shown in figure 1.1.

FIGURE 1.1: Different Threat Models at Different Stages of IC Design Flow [7].

In order to thwart emerging hardware security threats, various defence techniques have been developed, including watermarking and fingerprinting [24, 25], camouflaging [26], split manufacturing [27], and logic locking [9].

### 1.1.1.1 Watermarking and fingerprinting

Watermarking is a defence technique where the designer inserts a digital signature into the circuit; this signature could be a design constraint [24]. In fingerprinting, the user's digital signature is also embedded in the design, along with the designer's signature. Techniques like watermarking and fingerprinting are referred to as passive techniques, which can only detect malicious operations on the hardware but cannot protect the circuitry from malicious attacks [25]. Both techniques are employed at the logic design and physical design stages of the design flow.

### 1.1.1.2 Camouflaging

Camouflaging, as its name, in selected part of the circuitry, designer replaces the gates with their camouflaged counterparts. Compared to normal logic gates, camouflaged gates are much harder for the reverse engineering attackers to tell their function. With a trusted foundry, camouflage is able to protect the circuit from reverse engineering in certain level [26].

### 1.1.1.3 Split Manufacturing

In order to address the issue of an untrusted foundry, split manufacturing divides the manufacturing of the product into two stages: back-end-of-the-line (BEOL) and front-end-of-the-line (FEOL). The two parts of the product are then manufactured separately in two different foundries to ensure that no single foundry has full access to the design [28, 29, 30, 31, 32].

Split manufacturing and camouflaging are both layout-level techniques that are applied to the product after the physical design stage.

### 1.1.1.4 Logic Locking

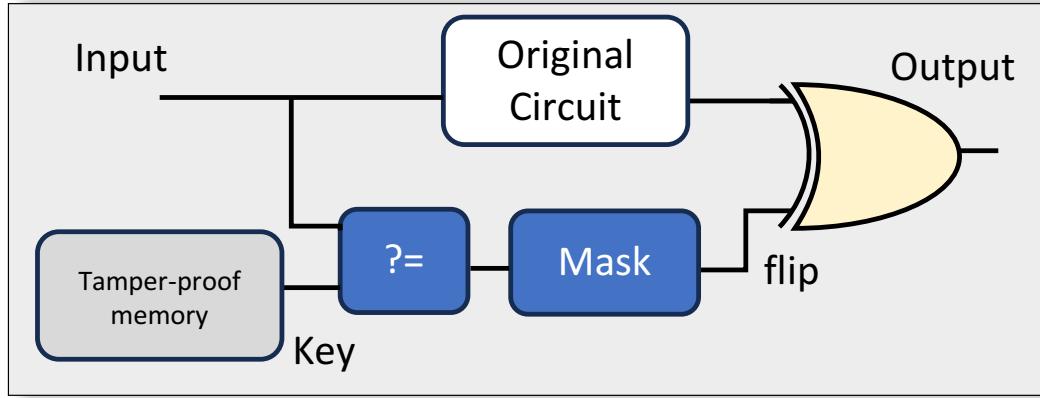

Logic locking refers to the ability to introduce post-fabrication programmability through additional gates, known as key-gates, which are controlled by a secret key. These key-gates enable the locking of the circuit's functionality, ensuring that the circuit behaves correctly only when the correct key is provided. In other words, hardware designers of logic locking will implant a series of logic gates [9] or other structures such as eFPGA [14, 33, 34], which will cause primary output of the protected circuit to distort. The only way for the protected circuit to perform functional correctness is to input a preset key sequence which only hardware designer has access to and is used to activate the product after fabrication. The correct key sequence is then stored in a tamper-proof memory in the system.

FIGURE 1.2: IC Supply Chain, Threat Modelling, and Logic Locking Engagement (Injecting in Netlist and Activating after Fabrication)

In the standard design flow, locking gates are implanted in the chip during the logic synthesis stage, as depicted in figure 1.2, and only the designer knows the correct key. This mechanism ensures that even if a malicious foundry obtains the design in the

subsequent stages, the attacker cannot make the chip function correctly without the right key. The chip is activated by the secret key after the design flow is completed, and the key is stored in tamper-proof memory, ensuring that malicious attackers cannot access it. This logic locking mechanism ensures the design’s security throughout the design flow and at the end-user stage. Compared to other defence strategies, as shown in table 1.1, logic locking offers a broader range of protection across the supply chain.

TABLE 1.1: Hardware defence strategies comparison

| DfTr technique      | SoC integrator | Foundry | Test facility | End-user |

|---------------------|----------------|---------|---------------|----------|

| Watermarking        | N              | N       | N             | N        |

| Camouflaging        | N              | N       | N             | Y        |

| Split manufacturing | N              | Y       | N             | N        |

| Logic Locking       | Y              | Y       | Y             | Y        |

One of the critical challenges in logic locking is enabling effective functional verification without disclosing the secret key to potentially untrusted parties involved in the design or testing process. To address this issue, several practical and secure strategies have been developed. The most widely adopted approach involves the use of **encrypted simulation modules** compliant with the *IEEE 1735* [35] standard for IP encryption. By encrypting the key-related modules and controlling access rights through license-based restrictions, third-party verification teams are able to simulate the design and verify functionality without accessing the actual RTL or the embedded key. In addition, commercial EDA tools such as Synopsys VCS, Cadence Xcelium, and Mentor Questa provide support for encrypted RTL simulation, enabling secure key encapsulation throughout the verification flow.

Another secure alternative is the use of **formal equivalence checking** tools such as *Cadence Conformal* or *Synopsys Formality*, which allow designers to verify the equivalence between the locked and unlocked versions of the circuit using symbolic representations of the key. In this setting, the key remains an abstract symbolic variable during verification, thereby preventing its exposure. These approaches collectively ensure that robust design verification can be conducted without compromising the confidentiality of the secret key—an essential requirement for secure hardware IP delivery and validation.

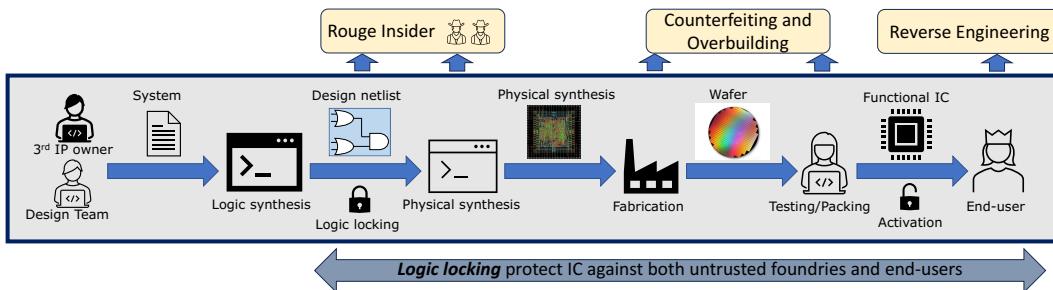

Hardware designers can implement logic locking at various levels of abstraction. Figure 1.3 illustrates a simple example of logic locking across different abstraction levels. For instance, at the layout level, as shown in Figure 1.3, the metal-insulator-metal

(MIM) structure, which connects two adjacent metal layers, can be used as a key-based programmable unit for routing-based locking [36]. Compared to other abstract levels, Gate-level logic locking technique is often the easiest to implement, and cause acceptable overhead.

Currently, most existing logic locking techniques are implemented at the gate-level, typically as a post-synthesis operation on the synthesized gate-level netlist in the supply chain. In this Phd project, all the work, including Zeki and Locklab, is focused on gate-level logic locking.

FIGURE 1.3: Logic Locking Examples at Different Levels of Abstraction: (a) Layout-level Key-based Routing, (b) Transistor-level Key-based Basic Gates, (c) Key-based Logic/Routing Gate-level, (d) RTL-level Keybased FSM, (e) HLS-level Key-based Shift Register.

### 1.1.2 Basic Working Principle of Logic Locking

Logic locking[9] stands out for its ability to safeguard the supply chain and end-users with minimal design flow modifications.

Logic locking protects a chip by inserting locking gates, typically XOR/XNOR gates. The chip with implanted locking gates requires the user to input a correct secure key to function properly; otherwise, it will produce incorrect outputs.

Figure 1.4 shows why this is the case.

FIGURE 1.4: Basic working principle of logic locking.

### 1.1.3 Threat Model in Attacks on Logic Locking

The threat models for attacks on logic locking are usually divided into two categories: oracle-guided and oracle-less, where the oracle refers to a functional IC (or golden model) that provides correct input–output pairs. The work of this project is focused on oracle-guided threat model.

In the threat model for oracle-guided attacks, it is assumed that attackers have access to two critical entities:

1. **A functional IC:** Attackers can readily acquire a functional IC from the market. During the attack process, this functional IC provides valid input/output pairs as golden references;

2. **A gate-level netlist file of the locked circuit:** This file is obtained through reverse engineering or from an untrusted foundry.

### 1.1.4 Existing Challenges

#### 1.1.4.1 Limitation of Single Locking Mechanism

Logic locking is a widely adopted hardware security technique due to its ease of implementation and relatively low overall hardware cost. It offers broad protection for integrated circuits (ICs) and other hardware products. However, its development has faced significant challenges, particularly from attacks designed specifically to bypass logic locking mechanisms or extract the secret key. One such attack, the SAT attack [1], involves converting a locked circuit's netlist into an SAT(satisfiability) problem and then using specialised SAT solvers to efficiently break the protection, making the attack process quick and effective.

In response to SAT attacks, numerous defence-oriented logic locking techniques have been proposed. Among them, Point-Function Based (PFB) logic locking [4, 2, 37, 3] provides relatively balanced performance: acceptable overhead and resilience against malicious attacks. However, since each PFB locking strategy relies on a single locking mechanism, it has inherent structural vulnerabilities. Once these vulnerabilities are published, they become exposed to attackers. If an attacker identifies these weaknesses, any circuit protected by that particular PFB strategy becomes susceptible to attacks.

#### 1.1.4.2 Insider Threat

Compared to other hardware security techniques, logic locking provides extensive protection throughout the entire IC design flow. Typically, its protection spans from post-synthesis all the way to the product's market deployment. To enhance the security of the implementation, the secret key used to activate the product is typically introduced after the fabrication phase. However, this approach still carries potential risks. Insider threats may steal information about the locking block structure or the positioning of key-gates, as personnel must intervene during the insertion of locking gates or blocks.

If the locking mechanism of a locked product is leaked, malicious attackers may exploit the structural characteristics of the corresponding locking block to develop targeted attacks that compromise the circuit's protection. For example, sensitization attacks [5]

have been designed specifically against SFLL [3], while SPS attacks [6] target Anti-SAT [2]. Furthermore, the leakage of other information—such as the location of key gates or the arrangement of key bits—can significantly lower the difficulty for attackers attempting to break the locking scheme.

This necessity for human intervention introduces the possibility of leakage, creating a security vulnerability for the protected product. This risk is especially concerning given that nearly all logic locking strategies rely on a single locking mechanism. If the information regarding the locking mechanism leaks, the entire design flow becomes susceptible to threats, severely compromising the integrity of the protection.

#### 1.1.4.3 Easy-to-use Simulation Tool

The rapid development of the IC industry in the 21st century has led to an increasing demand for hardware security technologies. However, while logic locking stands out as a key player in hardware security, its development has not kept pace with the industry's growth. One of the reasons for this slower progress is the lack of a simple, easy-to-use, and comprehensive simulation tool. This gap in tools hampers the broader adoption and refinement of logic locking techniques, limiting their effectiveness in meeting the growing security demands of the industry.

## 1.2 Motivation

To address the challenges outlined above, this project introduces a novel logic locking strategy, Zeki, and presents a related paper, Zeki: A Zero-Knowledge Dynamic Logic Locking. Compared to traditional logic locking techniques, Zeki introduces two key innovations. First, it employs a dynamic logic locking mechanism that randomly generates a locking block for each product based on different locking mechanisms. This approach avoids the inherent structural vulnerabilities present in single-locking mechanisms, which attackers could exploit to break the circuit's defences.

Second, unlike single-locking mechanisms, Zeki ensures that even if one product is compromised, all other products using the same locking strategy remain secure. Although the same locking mechanism is used for different chips within the same product line,

Zeki generates unique locking blocks for different products. This ensures that an attacker who successfully cracks one product's defence cannot apply the same method to other products protected by Zeki.

Additionally, the dynamic locking mechanism prevents insider involvement in the logic locking implementation, enabling the realization of zero-knowledge locking. Zeki is the first locking strategy to achieve zero-knowledge locking, significantly reducing internal participation and thus mitigating the risk of insider attacks or leaks.

In response to the current lack of effective automatic simulation tools in the logic locking field, I developed LockLab, an automated tool for simulating logic locking and associated attacks. LockLab provides a convenient and efficient platform for researchers and learners in the logic locking domain, greatly enhancing research productivity by enabling fast simulations of various locking strategies and corresponding attacks.

### 1.3 Research Objectives

The primary objective of this research is to enhance the security and robustness of logic locking strategies in the face of increasingly sophisticated hardware attacks. In light of the limitations of existing single-mechanism logic locking approaches and the practical risks posed by insider threats and structural vulnerabilities, this project aims to address these gaps through both theoretical development and practical tooling. The specific objectives are as follows:

- To design and implement a novel logic locking strategy, that leverages dynamic and randomized locking mechanisms to eliminate structural vulnerability caused by single mechanism and enable zero-knowledge protection.

- To develop a secure framework in which the locking process is resistant to insider threats by minimizing designer involvement during the locking phase.

- To ensure that the proposed method provides strong resilience against a broad range of attacks, including SAT-based, sensitization-based, and AI-based attacks.

- To develop an easy-to-use, automated simulation platform, which is capable of modelling various logic locking strategies and attacks, thereby accelerating research and enabling comparative evaluation.

- To evaluate the effectiveness, scalability, and robustness of the logic locking strategy and simulation platform developed in this work through extensive experiments using industry-standard benchmarks.

## 1.4 Contributions of This Project

The contributions of this project are listed below:

1. The introduction of the first zero-knowledge locking strategy significantly reduces the involvement of internal designers in the logic locking implementation, thereby minimizing the risk of internal attacks and information leaks. This reduction in insider participation enhances the overall security of the product by preventing potential malicious exploitation and safeguarding sensitive product information.

2. The proposed locking strategy, Zeki, employs a dynamic locking mechanism. Unlike traditional single-locking mechanisms, dynamic locking inherently avoids the structural vulnerabilities present in static locking blocks. Additionally, it prevents the issue where, once a product is compromised, all other products protected by the same mechanism can be attacked using the same exploited vulnerability.

3. Extensive simulations were conducted to evaluate Zeki's resilience against various types of attacks. The simulation results demonstrate that Zeki provides strong defence capabilities against a wide range of attacks targeting logic locking.

4. Furthermore, the LockLab tool was developed as an automated simulation platform for logic locking strategies and related attack simulations. LockLab is user-friendly and significantly enhances the efficiency of researchers and learners in the logic locking field. It supports simulations for multiple locking strategies, including RLL, FLL, SLL, Zeki, SFLL, Anti-SAT, and SARLock, as well as simulations for various attacks such as SAT, SPS, sensitization, and AI-based attacks. These simulations validate LockLab's effectiveness in practical applications.

## 1.5 General Structure of the Thesis

The structure of the remaining chapters in this thesis is as follows:

- **Chapter 2: Literature Review**

This chapter provides a detailed examination of various logic locking strategies and the associated attack techniques targeting logic locking. Special emphasis will be placed on SAT attacks and the different types of PFB (Point-Function Based) logic locking, as these techniques have been extensively studied in the field of logic locking. Moreover, they are fundamental to understanding the core principles of this project, particularly in relation to Zeki's operational framework. Other logic locking strategies and corresponding attacks will also be discussed, providing a comprehensive overview of the current landscape in this area of research.

- **Chapter 3: Zeki**

This chapter focuses on the Zeki technique, detailing the motivation behind its design and its contributions to the field. A thorough explanation of Zeki's mechanism will be presented, followed by a comparison with other PFB logic locking techniques that rely on a single locking mechanism. Additionally, simulations using various benchmarks will be conducted to demonstrate Zeki's resilience against different attacks, providing empirical evidence of its effectiveness. Furthermore, this chapter will explore Zeki's role as the first zero-knowledge logic locking technique, highlighting its advantages in defending against insider threats compared to other locking mechanisms.

- **Chapter 4: Zeki for Sequential Circuits**

This chapter introduces the sequential version of Zeki, addressing the fact that, in the IC market, sequential circuits are more prevalent than combinational ones. While Zeki was originally designed for combinational circuits, its adaptability to sequential circuits will be discussed in this chapter. The implementation process of applying Zeki to sequential circuits will be explained, demonstrating how the technique can be used in a broader range of IC designs.

- **Chapter 5: LockLab and Lockit**

This chapter presents an in-depth discussion of LockLab and Lockit, two automation tools for implementing logic locking. These tools significantly simplify the workflow for logic locking implementation, allowing designers to more easily integrate logic locking into their work or conduct experiments with various gate-level locking strategies. Additionally, LockLab proves to be an excellent educational

tool, making it a valuable resource for teaching hardware security and logic locking concepts.

- **Chapter 6: Conclusion**

The final chapter will summarize all the work presented in this thesis, including the key contributions and findings. It will also discuss the limitations of the current research and outline potential future directions for further exploration in the field of logic locking and hardware security.

## 1.6 Publication during PhD

Zhang Y, Halak B, Wang H. ZeKi: A Zero-Knowledge Dynamic Logic Locking Implementation with Resilience to Multiple Attacks[C]//2024 IEEE 37th International System-on-Chip Conference (SOCC). IEEE, 2024: 1-6.

Kajtez N, Zhang Y, Halak B. Lockit: A Logic Locking Automation Software[J]. Electronics, 2021, 10(22): 2817.

# Chapter 2

## Literature Review

### 2.1 Introduction

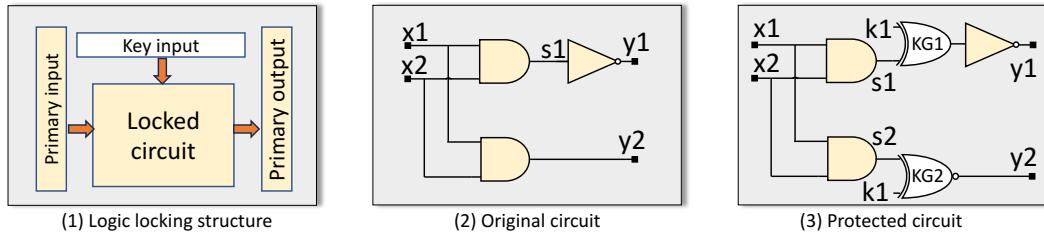

Logic locking has evolved into one of the most prominent hardware security techniques for protecting integrated circuits (ICs) against a wide spectrum of threats, including IP piracy, overproduction, counterfeiting, and reverse engineering. Over the past decade, the research community has proposed numerous locking schemes and corresponding attacks, leading to a highly dynamic arms race between defenders and adversaries. In particular, the emergence of the SAT attack has fundamentally reshaped the design goals of logic locking, shifting the focus from simple output corruption towards rigorous SAT-resilient constructions.

This chapter provides a structured review of existing logic locking strategies and their associated attack methodologies. It begins with pre-SAT (section 2.2) schemes such as Random Logic Locking (RLL), Fault-analysis-based Logic Locking (FLL), and Strong Logic Locking (SLL), together with early attacks like the sensitisation attack. It then introduces SAT-based attacks and explains how they exploit distinguishing input patterns to recover the secret key efficiently in section 2.3. Subsequently, Point-Function based (PFB) locking schemes, including SARLock, Anti-SAT, ANDTree, TTLock, and SFLL are discussed as representative post-SAT countermeasures in section 2.4. The section will also introduce advanced approaches such as FSM/sequential locking, cyclic-based and routing-based locking, scan-chain locking, and higher-level or timing-based techniques,

as well as eFPGA-based IP-level locking. After that, recent machine-learning-based attacks are reviewed in section 2.5. In section 2.6 merits and drawbacks of different logic locking approaches are given and compared to show that Point-function based logic locking provides the most balanced performance. This literature review establishes the technical context and motivates the need for the new locking strategy and automation framework proposed in this thesis.

This chapter reviews the main developments in logic locking and related attack techniques. It first discusses pre-SAT logic locking schemes and early attacks, then explains the working principle of the SAT attack as a key turning point in the field. Afterwards, it surveys post-SAT logic locking strategies, including point-function-based locking, FS-M/sequential locking, cyclic-based and routing-based approaches, scan chain locking, and other advanced techniques. Finally, recent machine-learning-based attacks are reviewed. The chapter concludes with a comparative discussion of the merits and limitations of these strategies, highlighting why point-function-based logic locking offers a relatively well-balanced solution and thereby motivating the choice of this family of techniques as the basis for the new strategy proposed in this thesis.

## 2.2 Pre-SAT Logic Locking and sensitisation Attack

Before the advent of SAT-based attacks, logic locking techniques were mainly designed to introduce functional corruption under incorrect key values. Early schemes such as Random Logic Locking (RLL) and Fault-analysis-based Logic Locking (FLL) focused on inserting XOR/XNOR key-gates to maximise output corruption, while Strong Logic Locking (SLL) was later proposed to resist sensitisation attacks. This section reviews these pre-SAT techniques and the first generation of attack against them, providing the historical background for the later shift towards SAT-resilient designs.

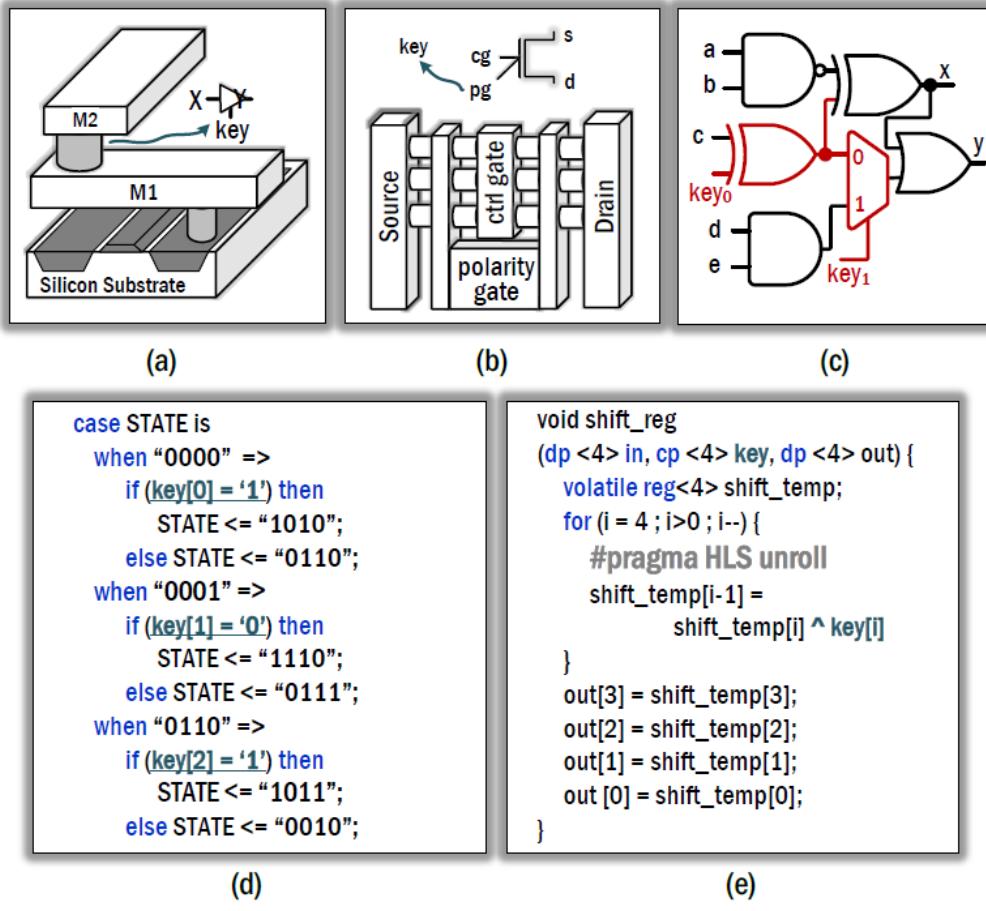

### 2.2.1 Random Logic Locking(RLL)

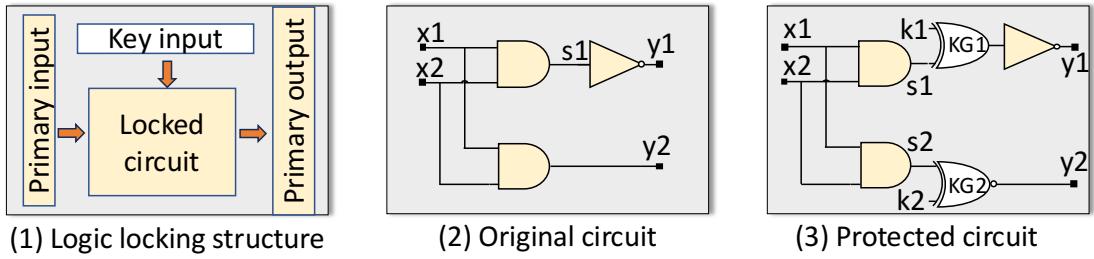

The original version of logic locking was introduced by [9] to protect IC products from threats such as overproduction, counterfeiting, and other malicious attacks. The concept of basic logic locking is illustrated in Figure 2.1. In this scheme, XOR/XNOR gates are

TABLE 2.1: Output of circuit in Figure 2.1(3) with different key-bit when the input bit  $x1=0, x2=1$

| gray!50 [x1,x2] | k1 | k2 | y1 | y2 |

|-----------------|----|----|----|----|

| 01              | 0  | 0  | 1  | 1  |

| gray!50 01      | 0  | 1  | 1  | 0  |

| 01              | 1  | 0  | 0  | 1  |

| 01              | 1  | 1  | 0  | 0  |

embedded into the circuit to obscure its functionality. For example, when an XOR key-gate (KG) is inserted into the protected circuit (see Figure 2.1(3)), if the K1 bit is 0, KG1 functions as a simple wire. If K1 is set to 1, KG1 behaves as an inverter. In the case of XNOR gates, the logic is reversed.

FIGURE 2.1: Basic working principle of logic locking

This mechanism enables the integration of  $N$  key-gates, comprising a mix of XOR and XNOR gates, to effectively generate a  $N$ -bit security key. The circuit will only function correctly when the correct key sequence is applied.

Table 2.1 presents an example of the input/output combinations for the circuit depicted in Figure 2.1, where the primary input pattern  $[x1, x2]$  is set to '01'. The correct key for this circuit is '01', and the corresponding output is '10', which is highlighted in gray in the table. As shown, injecting an incorrect key leads to output distortion, emphasizing the security provided by the locking mechanism.

In this original logic locking approach, the locking gates (XOR and XNOR) are inserted randomly into the circuit, a technique known as Random Logic Locking (RLL).

### 2.2.2 Fault-analysis based logic locking(FLL)

RLL inserts key gates randomly into the circuit; as a result, the inserted key gates' impact on the output has significant uncertainty. Ideally, 50% of the output bits should exhibit output corruption when an incorrect key is applied to the circuit. This metric can

be expressed as the Hamming distance (the bitwise difference) between the output bits produced with the correct and incorrect keys. A 100% output corruption is effectively equivalent to 0% at some level, since each bit can only be either 1 or 0. Based on this principle, 75% output corruption provides similar protection to 25%, while 50% offers the highest possible level of protection. For RLL, the output corruption rate is uncontrollable, and in the case of small circuits, this value may be relatively low.

Rajendran *et al.* suggest that the impact of an incorrect key is similar to a stuck-at fault, where a signal is stuck at '0' or '1'. FLL (Fault-analysis-based Logic Locking) aims to increase the output corruption caused by an incorrect key by inserting key gates at locations with the largest *fault impact* [38, 39]. A concept of a *fault impact metric* was proposed in [38, 39] to determine the optimal key gate insertion locations. Here, fault impact refers to the degree to which a selected location can propagate a detectable fault from the input to the output.

$$\begin{aligned} \text{FaultImpact} = & (\text{No.of.TestPatterns}_{s-a-0} * \text{No.of.Outputs}_{s-a-0}) \\ & + (\text{No.of.TestPatterns}_{s-a-1} * \text{No.of.Outputs}_{s-a-1}) \end{aligned} \quad (2.1)$$

According to the fault impact metric defined in [38], the fault impact of a certain location in the circuit is the sum of the products of the number of test patterns that detect a stuck-at fault and their corresponding output bit numbers. In the process of FLL insertion, the hardware designer computes the fault impact of the logic gates in the circuit to identify the insertion spots with the highest fault impact. The key gates are then inserted at those selected positions.

Compared to RLL, fault-analysis-based logic locking achieves a higher level of output corruption for incorrect key values. The Hamming distance (the bitwise difference) between the correct and corrupted outputs is approximately 50% when using the FLL algorithm.

### 2.2.3 sensitisation attack

sensitisation attack is the first powerful attack against logic locking. The threat model for sensitisation attack is also used for simulation of other attacks strategies against logic locking. [40, 41, 42]

1. The hardware designer is trusted.

2. End-user and the foundry is no trusted.

3. The attacker has access to a functional product, which can be bought from the market.

4. The attacker has access to the netlist of locked circuit of the product.

FIGURE 2.2: sensitisation Attack

Instead of applying brutal force decryption, the attackers in a sensitisation attack tries to sensitise the key bit to output, in another word, the key bit will be propagated to the output with no corruption.

Take the circuit in Figure 2.2 above as an example, when the input pattern of  $I_1$ ,  $I_2$ , and  $I_3$  is 110, the output of  $G_1$ ,  $G_3$  is 1, 0, and the XOR key gate works as wire, hence the output of key gate 1 is key bit  $K_1$ . Also, the output of  $G_4$  is 0, so the  $G_6$ 's output is key bit  $K_1$ . Such attack is achievable since the attacker has access of functional IC and locked netlist of the product (able to deduce the input pattern needed for sensitise attack).

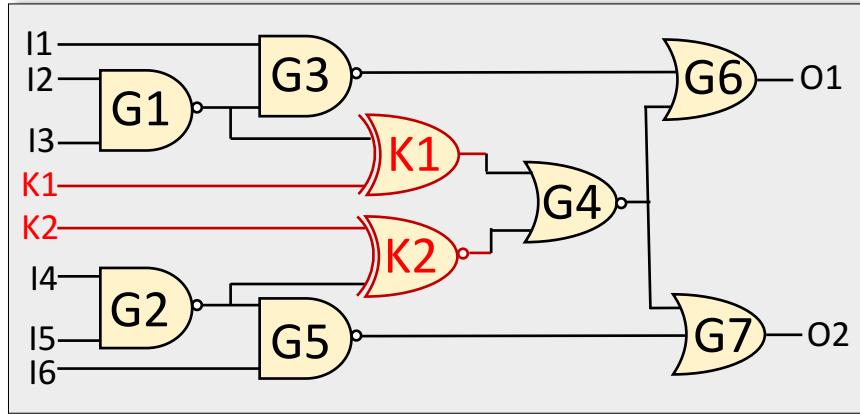

### 2.2.4 Strong Logic Locking

In response to the sensitisation attack, Strong Logic Locking (SLL) was developed. When a circuit is secured using the SLL algorithm, an attacker cannot sensitise a single key bit to the output without accessing other key bits [40, 41].

FIGURE 2.3: Strong logic locking

In SLL, the sensitisation of a key gate is obstructed by the presence of other key gates, a mechanism known as pairwise security. If the inserted key gates are pairwise secured, an attacker attempting a sensitisation attack cannot propagate a key bit to the primary output simply by controlling the primary input. They would also need to control the output of the pairwise-secured key gate, which in turn also requires access to its corresponding secured key.

For example, in Figure 2.3, to sensitise key bit K1, the attacker must ensure that the output of key gate 2 is '0'. However, without access to key bit K2, which is securely stored in tamper-proof memory, the attacker cannot manipulate the output of key gate 2. Similarly, other key bits cannot be sensitised to the primary output. In this way, the inserted key gates not only protect the circuit but also reinforce one another, making malicious attacks significantly more difficult.

In summary, prior to the development of SAT attacks, logic locking techniques predominantly focused on inserting individual key gates into the protected circuit. Various insertion strategies were explored to maximize output corruption or to enhance resilience against sensitisation attacks.

## 2.3 SAT Attack

This section provides a brief introduction to the SAT attack. The SAT attack is a game changer in logic locking, where a SAT-solver, a specialised software tool, is used for extracting the correct key bits efficiently. In an SAT attack, the SAT-solver is employed to iteratively refine the key search space, which requires access to a functional product. As such, the attack is referred to as an *oracle-guided* attack, with the term *oracle* representing the functional IC sample that the attacker obtains from the market. All logic locking strategies developed before the emergence of the SAT attack are easily broken by it, and SAT resilience has become the primary objective for subsequent countermeasures [1].

### 2.3.1 SAT Attack Background Knowledge

#### 2.3.1.1 Boolean Satisfiability (SAT) problem

Boolean satisfiability (SAT) problem determines the satisfiability of a Boolean formula, in another word, whether there is any assignment to the Boolean formula variables which make it equal to 1 [43]. For example assignment  $(a, b, c) = (0, 0, 1)$  makes Boolean formula  $((a + !b) \& c)$  equal to 1.

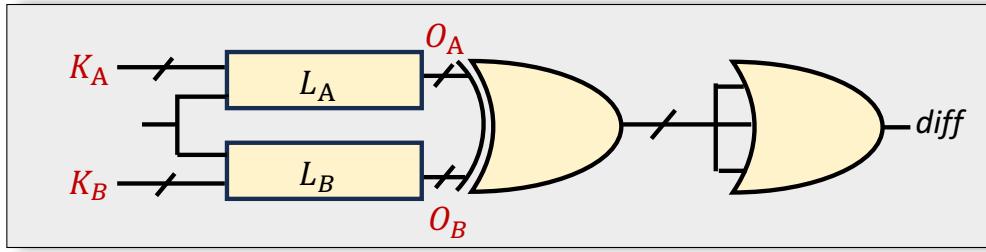

#### 2.3.1.2 Miter Circuit

In SAT attack, attackers transfer the problem into circuit equivalent checking, which is accomplished by a Miter circuit. The Miter circuit contains the two circuits whose equivalence is checked, and xors all the output bits of the two circuits. The outputs of all the XOR gates will be presented as input to an OR gate, and inputs of both circuits are the same [44]. If all the output bits of both circuits are the same, OR gate will produce 0, otherwise 1.

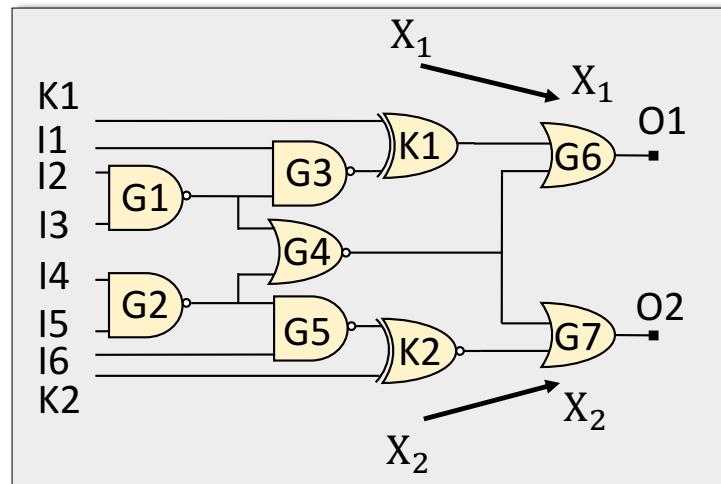

### 2.3.2 Working Principle of SAT Attack

During an SAT attack, the process is carried out on a Miter circuit, as illustrated in the figure 2.4. The Miter circuit operates by applying identical input patterns to two

FIGURE 2.4: Miter Circuit

circuits while using different key values. If the outputs of the two circuits match, the 'diff' signal outputs a 0; otherwise, it outputs a 1.

In the SAT attack procedure, the netlist file of the Miter circuit undergoes a Tseitin transformation, converting it into CNF form, which represents a SAT problem. Once in CNF form, the 'diff' output is used as a constraint, where a value of 1 indicates a mismatch between the circuits' outputs.

If the SAT solver identifies an input pattern that satisfies the constraint (i.e., where the 'diff' output is 1), the input pattern is classified as a distinguishing input pattern (DIP). Distinguishing input patterns (DIPs) are the core of SAT attack. DIP refers to an input pattern, with whom there is at least one pair of different key values cause the circuit to produce different output. Take figure 2.4 as an example, with input pattern I1 and two different key values  $K_A$  and  $K_B$  applied to the Miter circuit, if the circuit produces 1 as output, I1 is a DIP of the circuit.

### 2.3.2.1 Attack Algorithm

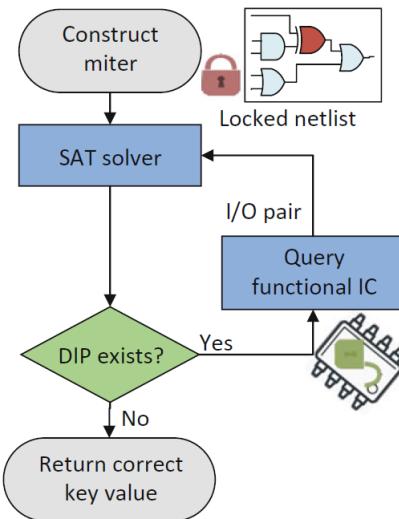

SAT attack is an iterative process, the procedure of which is shown in figure 2.5 and explained below:

- Attacker feeds the CNF of Miter circuit to SAT solver to get DIP which will later be fed to the functional IC to get the correct corresponding output.

- And then DIP and the corresponding output is served as a constraint of locked circuit CNF.

- The SAT solver will then eliminate wrong key values that does not produce correct output of this DIP.

The eliminated incorrect key value will be added as a constraint for further SAT solver execution. This procedure will be repeated until no more DIP can be found which means that all the wrong keys have been ruled out.

FIGURE 2.5: SAT attack flow chart [8]

FIGURE 2.6: Circuit Sample for SAT Attack

TABLE 2.2: SAT attack example (K0-K7 represent all the key bit combination (000, ..., 111) of the three key-bits, K1-K2-K3, combination)

| abc | Y | K0 | K1 | K2 | K3 | K4 | K5 | K6 | K7 | Incorrect keys identified |

|-----|---|----|----|----|----|----|----|----|----|---------------------------|

| 000 | 0 | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1  |                           |

| 001 | 0 | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1  |                           |

| 010 | 0 | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1  | iter3: other wrong keys   |

| 011 | 1 | 1  | 1  | 1  | 1  | 0  | 1  | 1  | 1  |                           |

| 100 | 0 | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1  |                           |

| 101 | 1 | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  |                           |

| 110 | 1 | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | iter1: k2                 |

| 111 | 1 | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | iter2: k1                 |

### 2.3.2.2 An Simple Example of SAT Attack

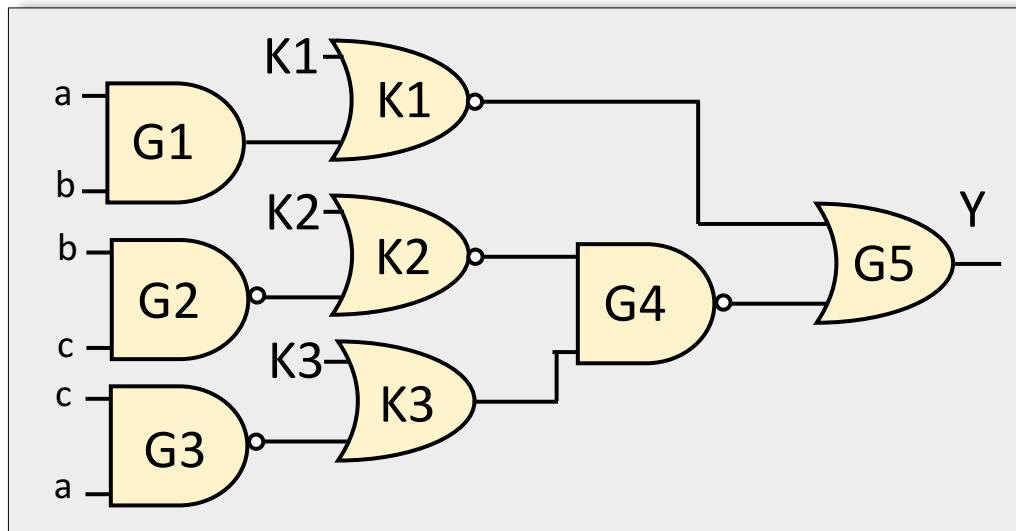

The circuit in figure 2.6 is used as the attacked circuit in the example SAT attack. Table 2.2 represents the attack procedure, K0 to K7 represent all the key bit combination (000, ..., 111) of the three key inputs, column Y stands for output bit of the circuit and abc stands for the input pattern.

In the first iteration DIP 110 is applied to the circuit, and the correct output bit produced by functional IC is 1. Among all the key values only K2(010) produces incorrect output, hence K2(010) is eliminated in this iteration. In iteration 2, DIP 111 is applied to the circuit, and K1(001) is eliminated. In the third iteration 010 is served as DIP and ruled out all the remaining incorrect keys. As there is no more DIPs (only 1 key value left), the SAT attack is successfully achieved.

### 2.3.2.3 SAT Attack Discussion