University of Southampton Research Repository

ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

**UNIVERSITY OF SOUTHAMPTON**

FACULTY OF ENGINEERING AND APPLIED SCIENCES

DEPARTMENT OF ELECTRONICS AND COMPUTER

SCIENCE

**Towards an Integrated Atom Chip**

By

**Gareth Neil Lewis**

A thesis submitted for the degree of Doctor of Philosophy

March 2009

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF ENGINEERING AND APPLIED SCIENCES

DEPARTMENT OF ELECTRONICS AND COMPUTER SCIENCE

Doctor of Philosophy

TOWARDS AN INTEGRATED ATOM CHIP

by Gareth Neil Lewis

The field of atom chips is a relatively new area of research which is rapidly becoming of great interest to the scientific community. It started out as a small branch of cold atom physics which has quickly grown into a multidisciplinary subject. It now encompasses topics from fundamental atomic and quantum theory, optics and laser science, to the engineering of ultra sensitive sensors. In this thesis the first steps are taken towards a truly integrated atom chip device for real world applications. Multiple devices are presented that allow the trapping, cooling, manipulation and counting of atoms. Each device presents a new component required for the integration and miniaturisation of atom chips into a single device, capable of being used as a sensor.

Initially, a wire trap was created capable of trapping and splitting a cloud of Bose Einstein condensate (BEC) for use in atom interferometry. Using this chip a BEC has been successfully created, trapped and coherent splitting of this cloud has been achieved.

Subsequently, the integration and simplification of the initial trapping process was approached. In all the experiments to date, atoms are initially collected from a warm vapour by a magneto-optical trap (MOT). This thesis presents a new approach in which microscopic pyramidal MOTs' are integrated into the chip itself. This greatly reduces the number of optical components and helps to simplify the process significantly.

Also presented is a method for creating a planar-concave micro-cavity capable of single atom detection. One such cavity consists of a concave mirror fabricated in silicon and the planar tip of an optical fibre. The performance of the resonators is highly dependent on the surface roughness and shape profile of the concave mirrors therefore a detailed study into the fabrication technique and its effects on these parameters was undertaken. Using such cavities single atom detection has been shown to be possible. These cavities have also been successfully integrated into an atom wire guide.

Finally a co-sputtered amorphous silicon/titanium (a-Si/Ti) nanocomposite material was created and studied for its use as a novel structural material. This material is potentially suitable for integrated circuitry (IC)/Micro-electro-mechanical-systems (MEMS) integration. The material's electrical and structural properties were investigated and initial results suggest that a-Si/Ti has the potential to be a compelling structural material for future IC/MEMS integration.

To build all of these devices, a full range of standard microfabrication techniques was necessary as well as some non standard processes that required considerable process development such as the electrochemical deposition.

This thesis presents a tool box of fabrication techniques for creating various components capable of different tasks that can be integrated into a single device. Each component has been successfully demonstrated in laboratory conditions. This represents a significant step toward a real world atom chip device.

# Content

|                                                              |           |

|--------------------------------------------------------------|-----------|

| <b>Chapter 1.....</b>                                        | <b>1</b>  |

| <b>Introduction .....</b>                                    | <b>1</b>  |

| 1.1. Motivation and approach.....                            | 2         |

| 1.2. Aims of this thesis .....                               | 3         |

| 1.3. Summary of the main achievements .....                  | 3         |

| 1.4. Thesis structure .....                                  | 4         |

| <b>Chapter 2.....</b>                                        | <b>6</b>  |

| <b>Literature Review.....</b>                                | <b>6</b>  |

| 2.1. Interferometry.....                                     | 6         |

| 2.1.1. Atom interferometry and gyroscopes.....               | 8         |

| 2.2. Atom chips .....                                        | 10        |

| 2.2.1. History of atom guides .....                          | 10        |

| 2.2.1.1. Superconducting atom chips .....                    | 19        |

| 2.3. Optical elements on atom chips .....                    | 19        |

| 2.4. Vacuum on chip .....                                    | 25        |

| 2.5. Overview of fabrication techniques for atom chips ..... | 26        |

| 2.5.1. Resist coating .....                                  | 26        |

| 2.5.2. Spin coating.....                                     | 27        |

| 2.5.3. Spray coating.....                                    | 28        |

| 2.5.4. Electrochemical deposition of photoresist .....       | 29        |

| 2.5.5. Electrochemical deposition of metals .....            | 34        |

| 2.5.5.1. Throwing power .....                                | 38        |

| 2.5.5.2. Stress .....                                        | 39        |

| 2.5.5.3. Plating parameters .....                            | 40        |

| 2.6. Summary .....                                           | 42        |

| <b>Chapter 3.....</b>                                        | <b>43</b> |

| <b>Atom Guides .....</b>                                     | <b>43</b> |

| 3.1. Design.....                                             | 43        |

| 3.1.1. Mirror magneto optical trap .....                     | 43        |

| 3.1.2. Trapping atoms.....                                   | 44        |

| 3.1.3. Trap configurations .....                             | 45        |

| 3.1.4. Creating an atom guide .....                          | 45        |

|                                                                                  |                                                  |            |

|----------------------------------------------------------------------------------|--------------------------------------------------|------------|

| 3.1.5.                                                                           | Creating an atom trap .....                      | 50         |

| 3.1.6.                                                                           | Trapping issues.....                             | 52         |

| 3.1.7.                                                                           | Practical limits.....                            | 54         |

| 3.2.                                                                             | Fabrication of microwires for atom guiding ..... | 56         |

| 3.2.1.                                                                           | Electrochemical deposition into a mould .....    | 57         |

| 3.2.2.                                                                           | Results .....                                    | 59         |

| 3.2.2.1.                                                                         | Solution stirring.....                           | 59         |

| 3.2.2.2.                                                                         | Temperature .....                                | 60         |

| 3.2.3.                                                                           | Current crowding.....                            | 64         |

| 3.2.4.                                                                           | Current density .....                            | 67         |

| 3.2.5.                                                                           | Atom guide fabrication.....                      | 71         |

| 3.2.6.                                                                           | Ion beam milling .....                           | 75         |

| 3.2.7.                                                                           | Wet etching .....                                | 78         |

| 3.3.                                                                             | Results .....                                    | 78         |

| 3.3.1.                                                                           | Profile measurements .....                       | 78         |

| 3.3.2.                                                                           | Resistance measurements.....                     | 81         |

| 3.4.                                                                             | Conclusion.....                                  | 84         |

| <b>Chapter 4.....</b>                                                            | <b>85</b>                                        |            |

| <b>Pyramidal Micro-mirrors.....</b>                                              |                                                  | <b>85</b>  |

| 4.1.                                                                             | Design.....                                      | 86         |

| 4.1.1.                                                                           | Silicon etch properties .....                    | 86         |

| 4.1.2.                                                                           | Chip design.....                                 | 88         |

| 4.1.3.                                                                           | Optical properties .....                         | 92         |

| 4.1.4.                                                                           | Magnetic field properties .....                  | 95         |

| 4.2.                                                                             | Fabrication.....                                 | 97         |

| 4.3.                                                                             | Results .....                                    | 107        |

| 4.4.                                                                             | Device characterisation .....                    | 109        |

| 4.4.1.                                                                           | Magnetic field measurements.....                 | 109        |

| 4.4.2.                                                                           | Wire load tests.....                             | 111        |

| 4.4.3.                                                                           | Optical properties .....                         | 113        |

| 4.5.                                                                             | Conclusion.....                                  | 114        |

| <b>Chapter 5.....</b>                                                            | <b>117</b>                                       |            |

| <b>Fabrication of Hemispherical Micro-cavities for Single Atom Detection....</b> |                                                  | <b>117</b> |

| 5.1.                                                                             | Design.....                                      | 117        |

|                                                                               |            |

|-------------------------------------------------------------------------------|------------|

| 5.2. Fabrication.....                                                         | 119        |

| 5.2.1. Fabrication of silicon micro-cavities integrated into atom chips ..... | 122        |

| 5.3. Fabrication results .....                                                | 126        |

| 5.3.1. Shape Results .....                                                    | 127        |

| 5.3.1.1. 2D opening.....                                                      | 127        |

| 5.3.1.2. 2D Profiles.....                                                     | 135        |

| 5.3.1.3. 3D shape.....                                                        | 139        |

| 5.3.2. Surface Roughness .....                                                | 142        |

| 5.3.3. Optical properties .....                                               | 147        |

| 5.3.4. Atom experiments .....                                                 | 149        |

| 5.4. Conclusion.....                                                          | 150        |

| <b>Chapter 6.....</b>                                                         | <b>152</b> |

| <b>Sputtered Si/Ti Films .....</b>                                            | <b>152</b> |

| 6.1. Introduction .....                                                       | 152        |

| 6.2. Fabrication.....                                                         | 153        |

| 6.3. Results .....                                                            | 156        |

| 6.4. Discussion .....                                                         | 162        |

| 6.5. Conclusion.....                                                          | 163        |

| <b>Chapter 7.....</b>                                                         | <b>165</b> |

| <b>Conclusion.....</b>                                                        | <b>165</b> |

| 7.1. Future work .....                                                        | 167        |

| <b>Appendix 1 .....</b>                                                       | <b>169</b> |

| <b>Appendix 2 .....</b>                                                       | <b>170</b> |

| <b>References .....</b>                                                       | <b>173</b> |

# List of Figures

|                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

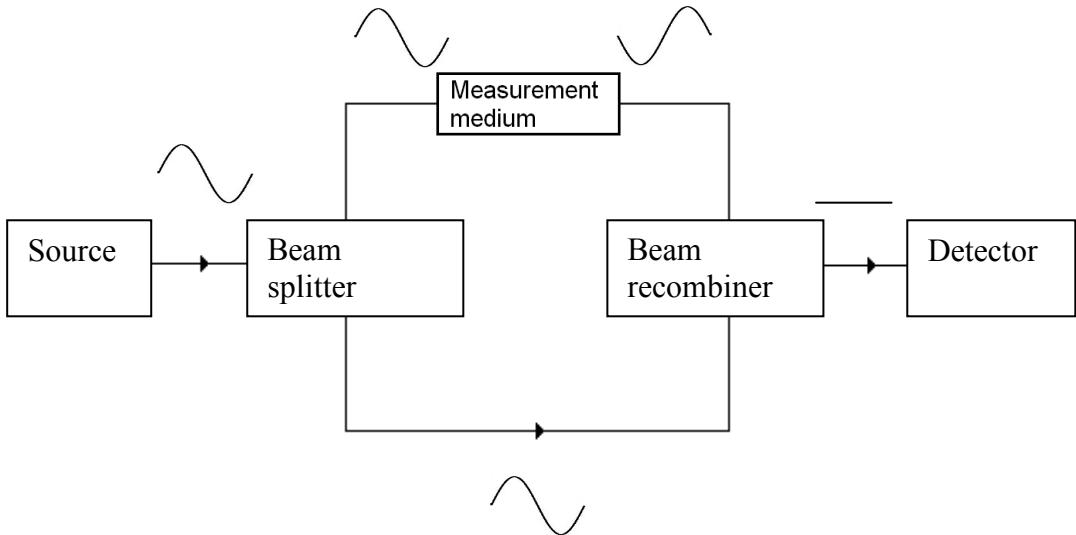

| <b>Figure 1:</b> A generic interferometer. A single phase source is used as an input. This beam is then split and one path experiences a different condition such as going through a medium and the phase is changed. Both beams are then recombined and interference occurs which is measured by the detector.....                                                                                               | 7  |

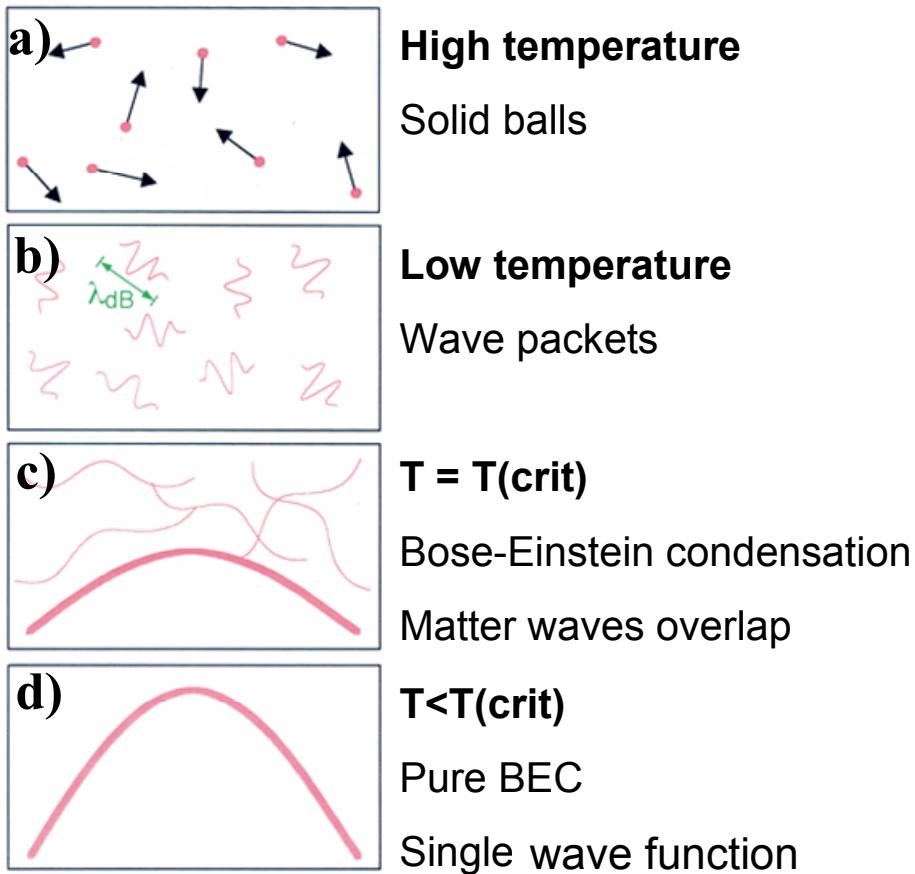

| <b>Figure 2:</b> Image showing the formation of a Bose-Einstein condensation as atoms undergo increasingly low temperatures (Taken from ref [20])......                                                                                                                                                                                                                                                           | 8  |

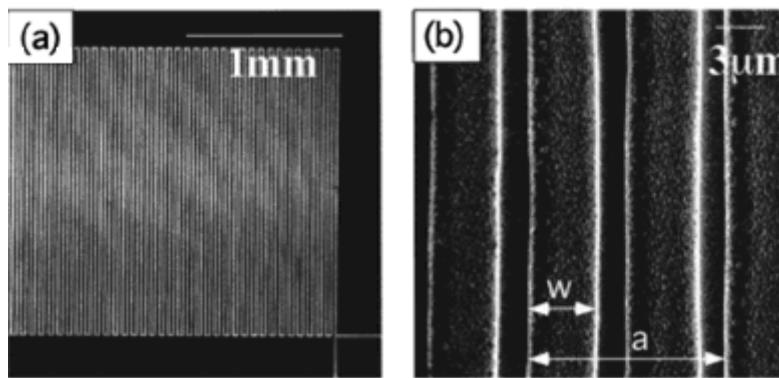

| <b>Figure 3:</b> SEM images of micro-electromagnets with geometries suggested in [36] created by Drndic et al. [37]. This was the first ‘atom chip’ to use microwires for trapping atoms. a) shows the microwires while b) shows a close up of these wires. .                                                                                                                                                     | 12 |

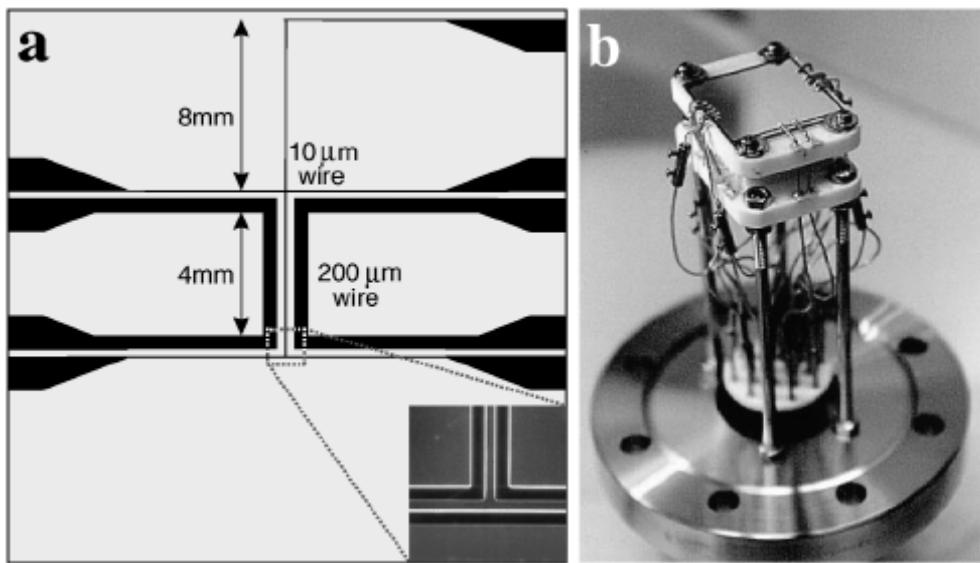

| <b>Figure 4:</b> A schematic and photograph of the atom chip created by Folman et al. [25]. The wide wires are 200 mm wide while the thin wires are 10 mm wide. The inset shows an electron microscope image of the surface and its 10 $\mu$ m wide etchings defining the wires. Part b shows the mounted chip before it is introduced into the vacuum chamber. ..                                                | 14 |

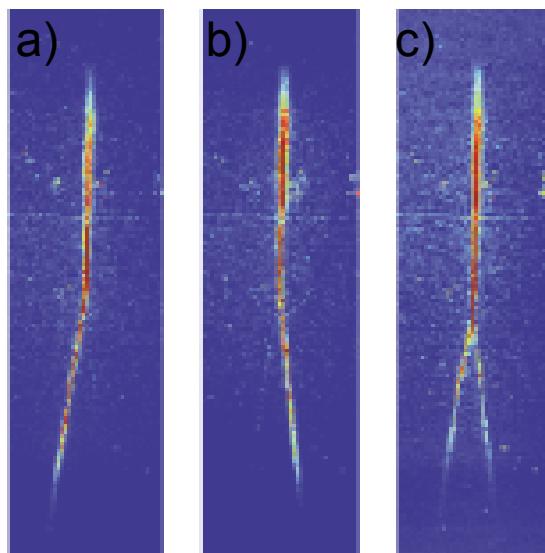

| <b>Figure 5:</b> Demonstration of a beam splitter on a chip. The image shows fluorescence images of guided atoms. a) Showing current driven through the left side and therefore guiding the atoms to the left, b) showing current driven through the right side and therefore guiding the atoms to the right and c) current split equally to both paths therefore splitting the cloud (Taken from ref [50])...... | 16 |

| <b>Figure 6:</b> Photograph of the atom interferometer glued onto a copper holder. The chip is 5 x 2 cm (Taken from ref [14])......                                                                                                                                                                                                                                                                               | 17 |

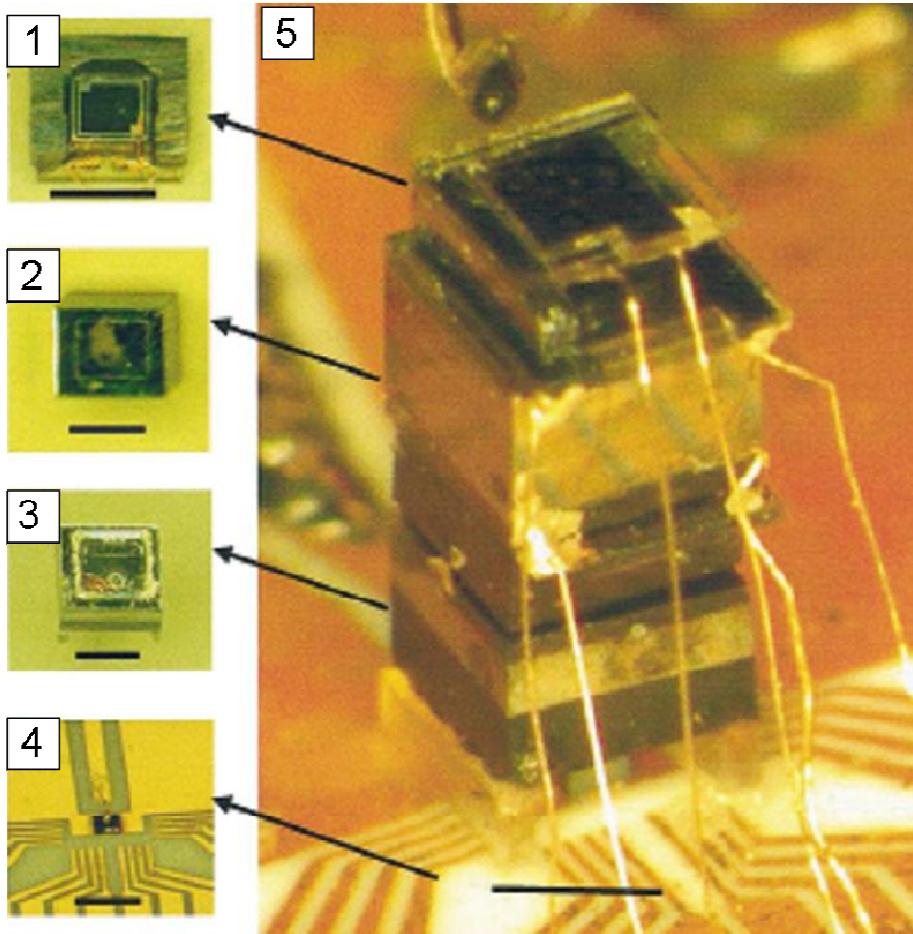

| <b>Figure 7:</b> ‘The microfabricated atomic clock physics package. Photographs: (1) photodiode assembly, (2) cell assembly, (3) optics assembly, (4) laser assembly, and (5) the full atomic clock physics package realized as a microchip. The black line in the photographs indicate 1 mm. (Adapted from ref[51]). .....                                                                                       | 18 |

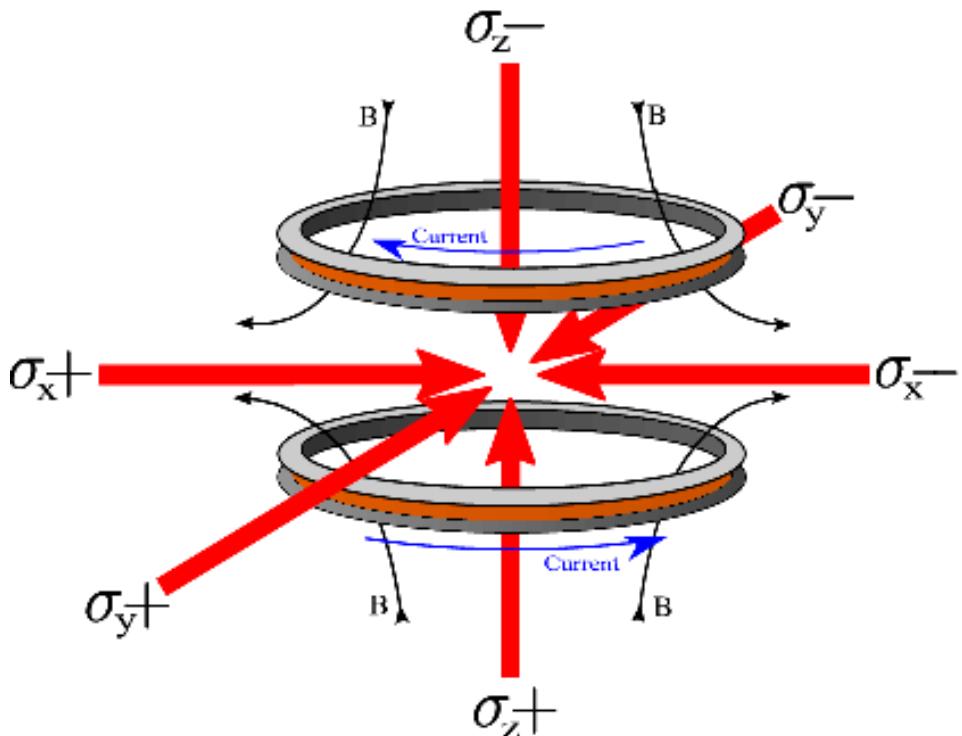

| <b>Figure 8:</b> Configuration of the laser beams in a standard MOT. Six incoming beams create the optical component while the magnetic field is produced using two counter propagating coils of wire (Taken from ref [58]). .....                                                                                                                                                                                | 20 |

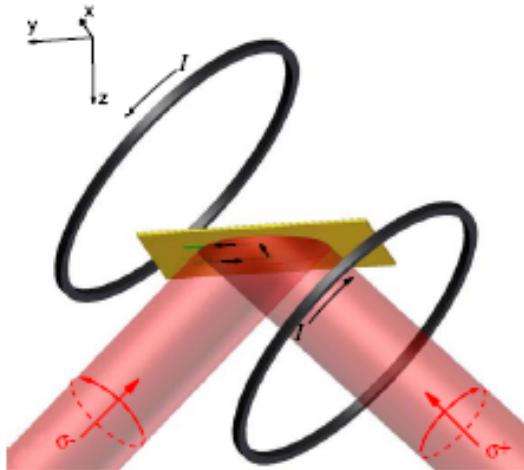

| <b>Figure 9:</b> Schematic of a mirror MOT. The black rings represent large coils of current carrying wires while the yellow surface represents the reflective mirror used to create the mirror MOT. Two beams shown in the yz plane reflect on the chip surface                                                                                                                                                  |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| while the other two beams (not pictured for clarity) propagate along the x axis parallel to the chips surface (Taken from ref [59]). .....                                                                                                                                                                                                                                                                           | 21 |

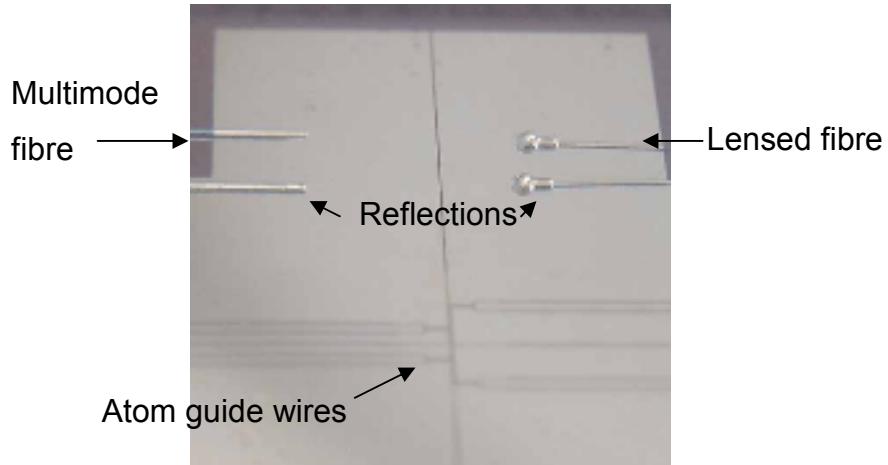

| <b>Figure 10:</b> Configuration of the optical fibres. The lensed fibre is coupled to the laser and the multimode fibre takes the light into a photo-detector. The “fibres” on the bottom are reflections from the mirrored surface. The dark lines on the surface are the contours of etched wires. The separation between the fibers and the height are 4.5 mm and 0.6 mm respectively (Taken from ref[69]). ..... | 23 |

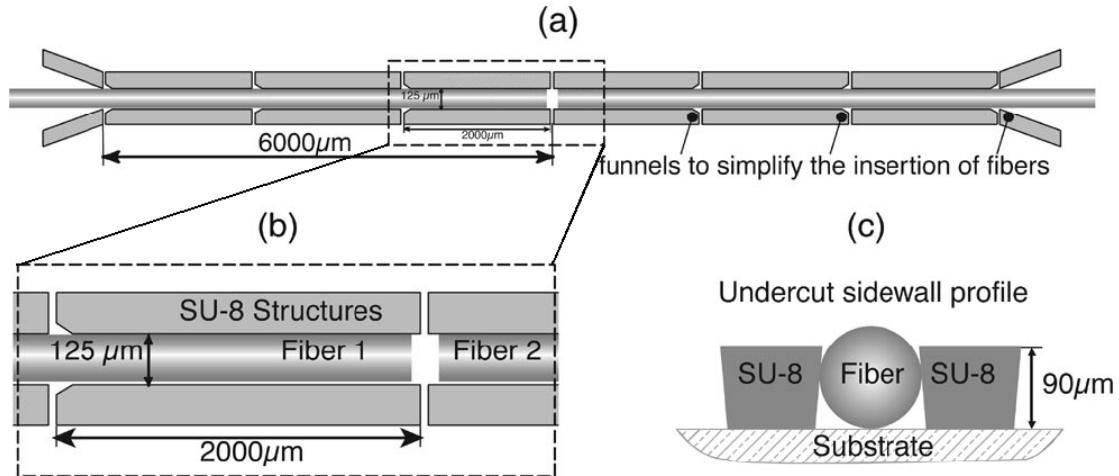

| <b>Figure 11:</b> Diagram of the structure created in SU8 (a) shows the channel the fibre is placed into (b) showing the structure in more detail (c) showing the cross section view (Taken from ref [70]). .....                                                                                                                                                                                                    | 24 |

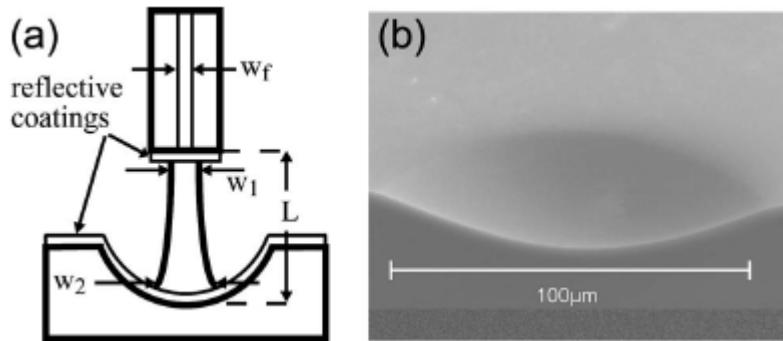

| <b>Figure 12:</b> A Schematic diagram of the cavity where $L$ is the cavity length and $w_1$ and $w_2$ represents the beam waist size. (b) Scanning electron microscope image of an uncoated mirror template cleaved almost across the diameter (Taken from ref [72]).                                                                                                                                               | 24 |

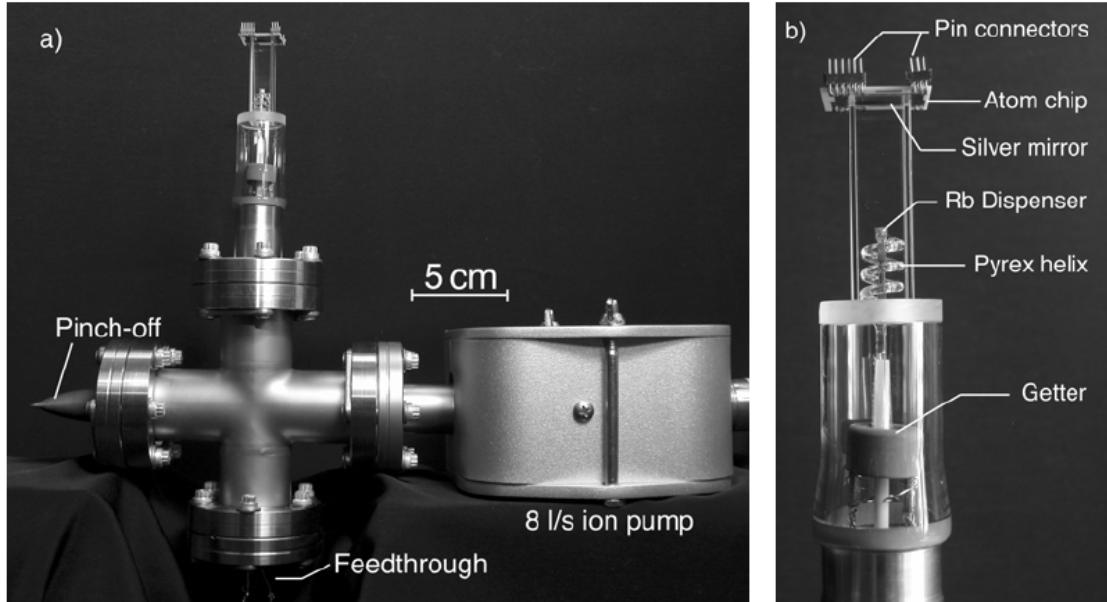

| <b>Figure 13:</b> The first ‘portable’ vacuum cell for production of a BEC on an atom chip. a) shows the complete vacuum cell b) showing the cell itself in greater detail (Taken from ref [78]). .....                                                                                                                                                                                                              | 26 |

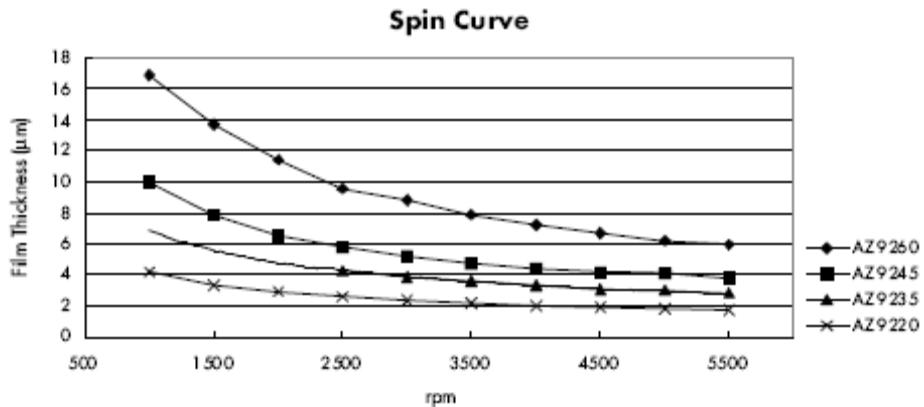

| <b>Figure 14:</b> Graph showing the film thickness created using different spin speeds for the AZ9xxx series of resists (Taken from ref [82]). .....                                                                                                                                                                                                                                                                 | 28 |

| <b>Figure 15:</b> An SEM image of a cavity with spray coated resist covering the sidewalls showing resist thinning at the top and thickening at the bottom (Taken from ref [84]). .....                                                                                                                                                                                                                              | 29 |

| <b>Figure 16:</b> An SEM image showing electrodeposition of photoresist over a cavity wall. The image shows the bottom and top corner of the cavity respectively demonstrating little variation in thickness compared to other methods (Taken from ref [86]). .....                                                                                                                                                  | 30 |

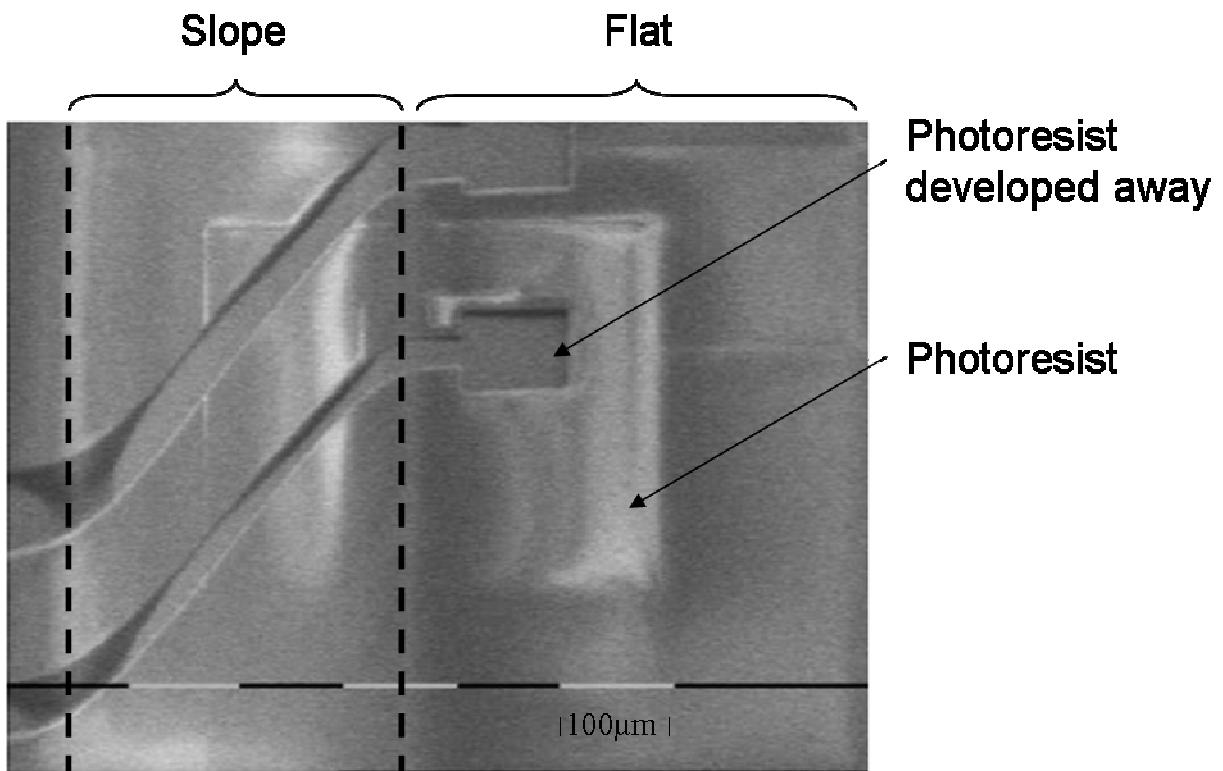

| <b>Figure 17:</b> An SEM image of a pyramidal cavity with a patterned resist running along the angled side walls created using electrodeposition of photoresist (Taken from ref [86]). .....                                                                                                                                                                                                                         | 30 |

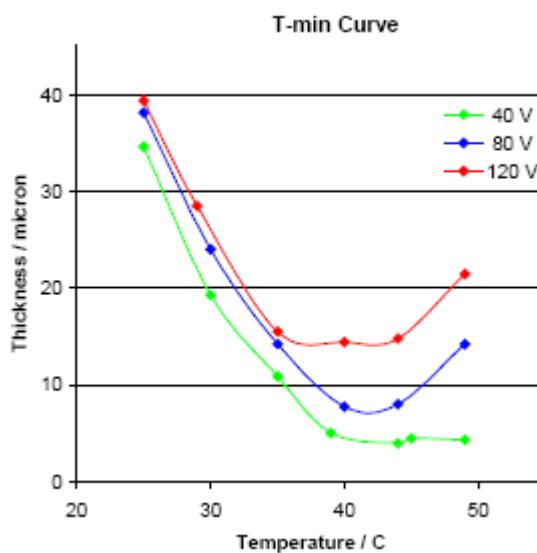

| <b>Figure 18:</b> Graph showing the thickness of electrodeposited films at different temperatures and voltages (Taken from ref [89]). .....                                                                                                                                                                                                                                                                          | 31 |

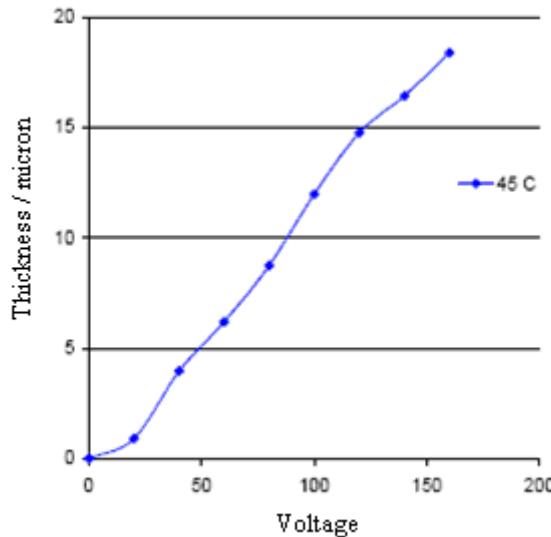

| <b>Figure 19:</b> Graph showing the resist thickness as a function of applied voltage at 45°C (Taken from ref [89]). .....                                                                                                                                                                                                                                                                                           | 32 |

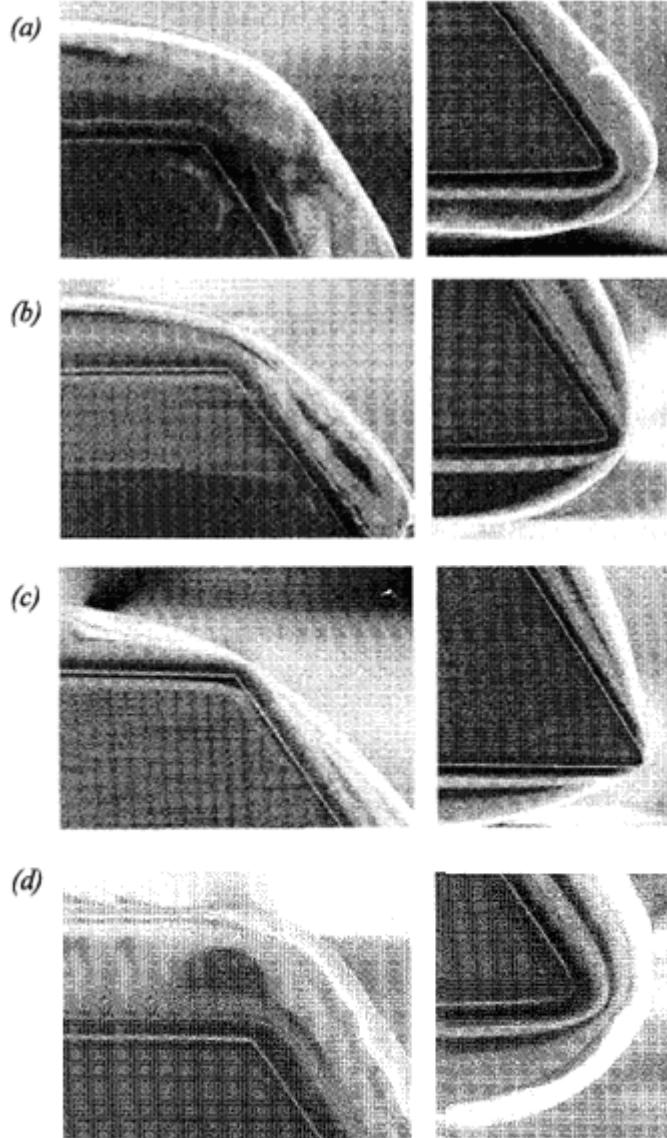

| <b>Figure 20:</b> SEM image of an obtuse (left) and acute (right) corner covered in 12 $\mu$ m of electrodeposited photoresist, (a) before prebake (b) 25 minutes at 50°C prebake (c) 3                                                                                                                                                                                                                              | 3  |

|                                                                                                                                                                                                                                                                                                                                                                          |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| minutes at 80°C prebake (d) vacuum treated for 1 hour at $10^{-4}$ Pa (Taken from ref [90]).                                                                                                                                                                                                                                                                             | 33 |

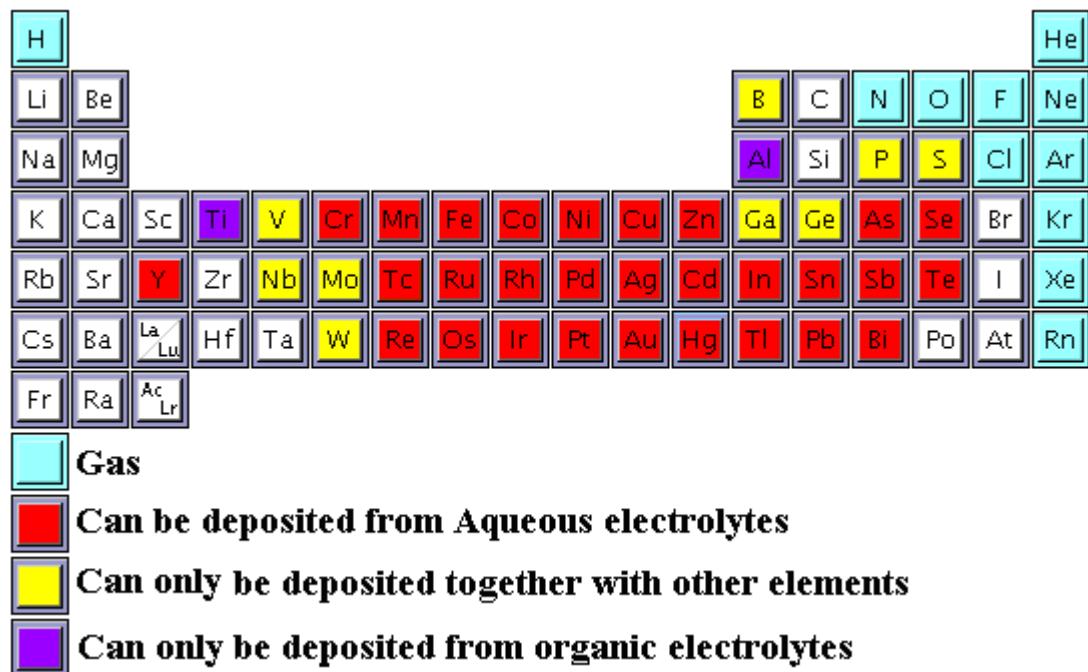

| <b>Figure 21:</b> Periodic table showing the elements that can be electrochemically deposited, (Adapted from ref [88]).                                                                                                                                                                                                                                                  | 35 |

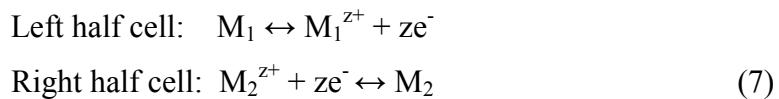

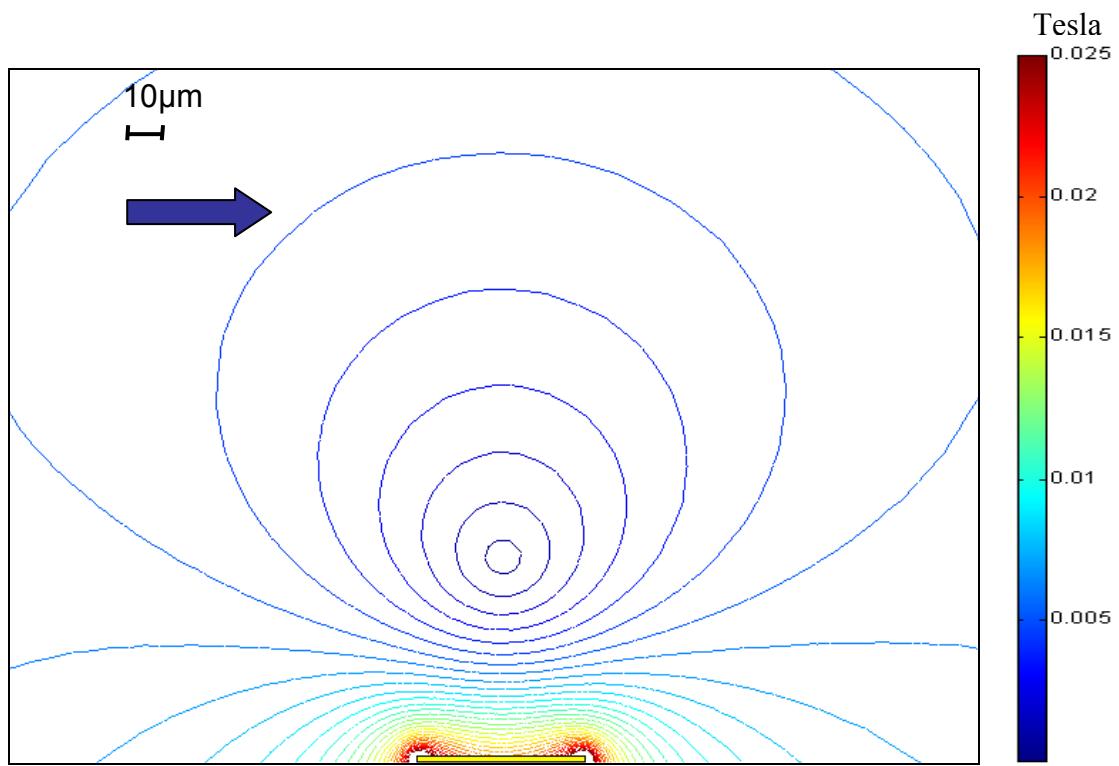

| <b>Figure 22:</b> a) shows the spatial dependence of the magnetic field strength for a quadrupole trap and b) an Ioffe trap. The quadrupole trap has a zero minimum while the Ioffe trap has a non zero minimum.                                                                                                                                                         | 45 |

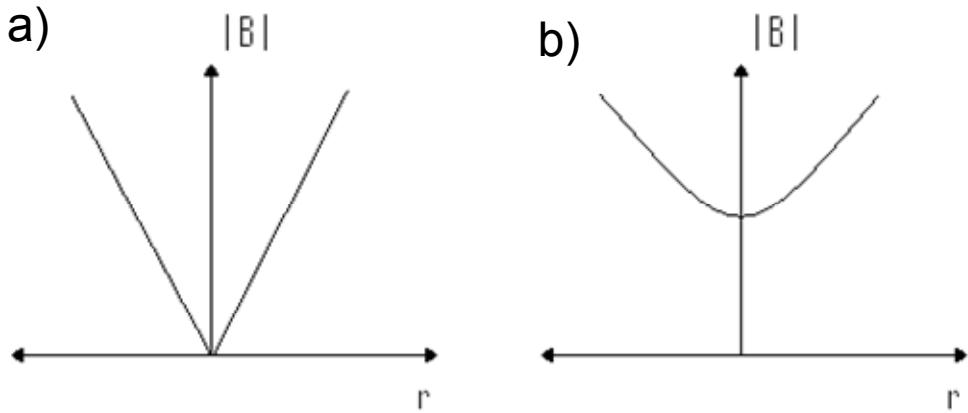

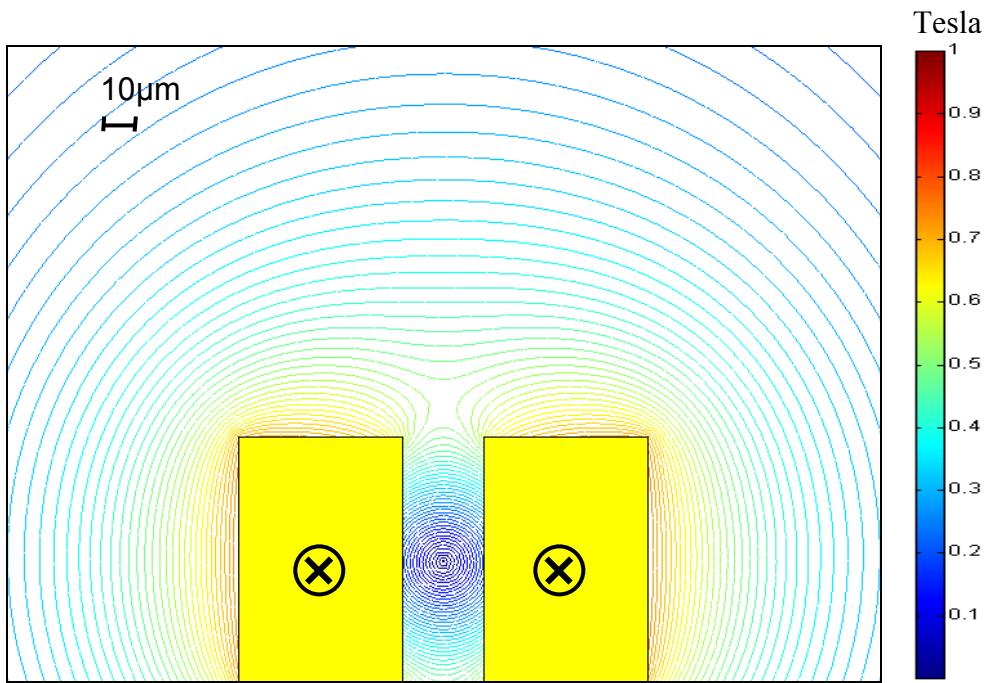

| <b>Figure 23:</b> Magnetic field produced by a single current carrying wire. The wire has the same dimensions as the actual wires used on the atom chips produced in this thesis.                                                                                                                                                                                        | 46 |

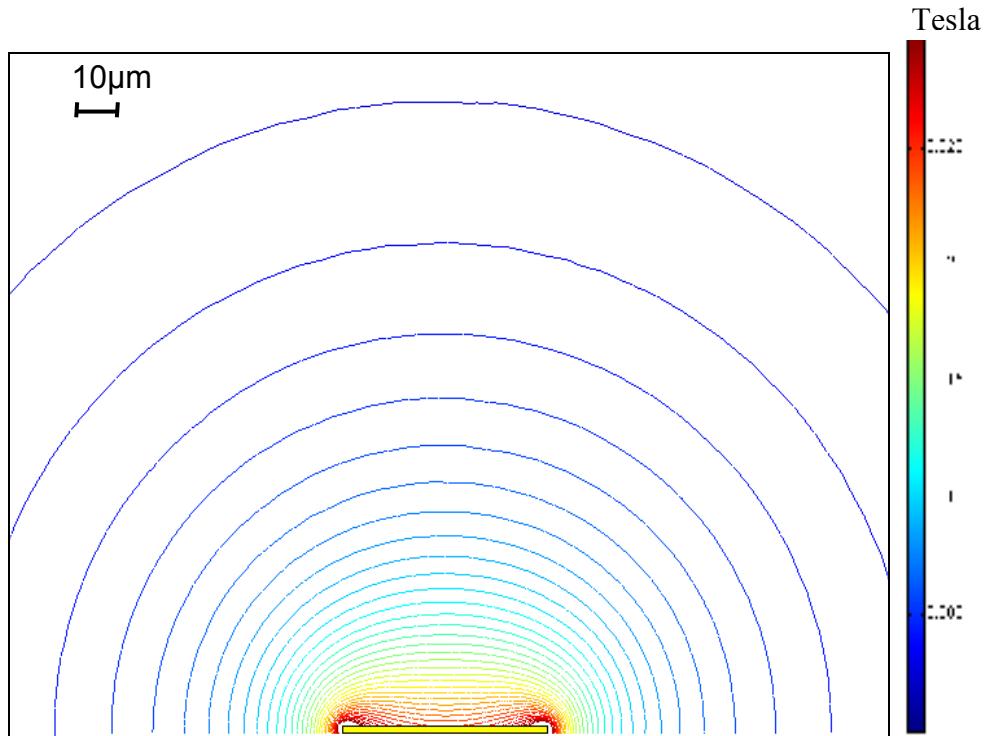

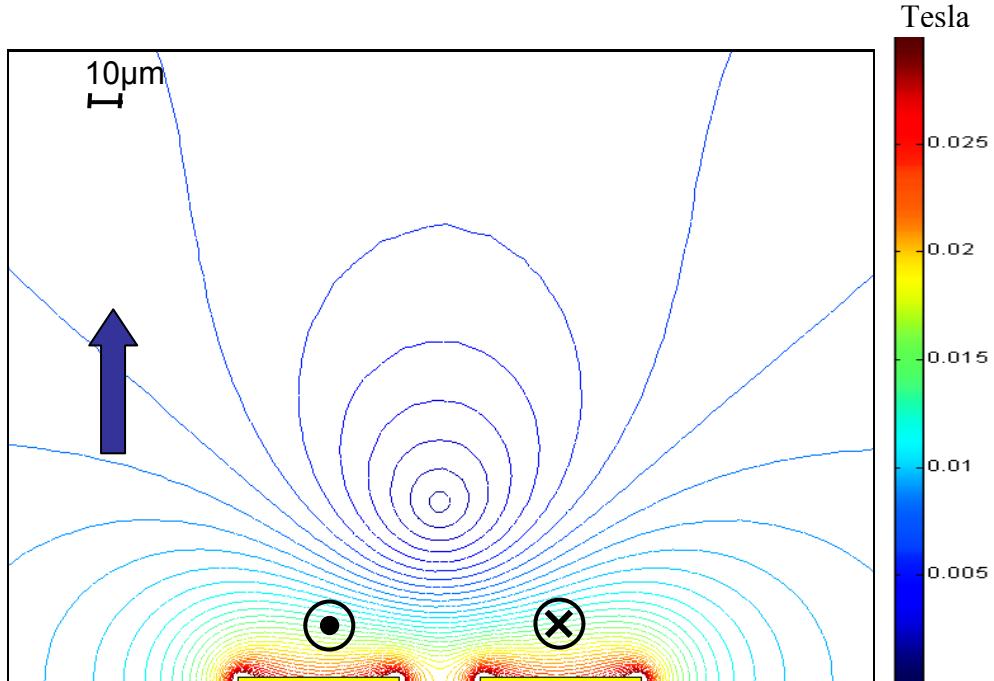

| <b>Figure 24:</b> Magnetic field due to a current carrying wire with an applied external field bias (Blue arrow). The wire has the same dimensions as the actual wires used on the atom chips produced in this thesis.                                                                                                                                                   | 47 |

| <b>Figure 25:</b> Magnetic field due to high relief current carrying wires.                                                                                                                                                                                                                                                                                              | 48 |

| <b>Figure 26:</b> Magnetic field due to two current carrying wires with an applied external field bias (Blue arrow). The wire has the same dimensions as the actual wires used on the atom chips produced in this thesis.                                                                                                                                                | 48 |

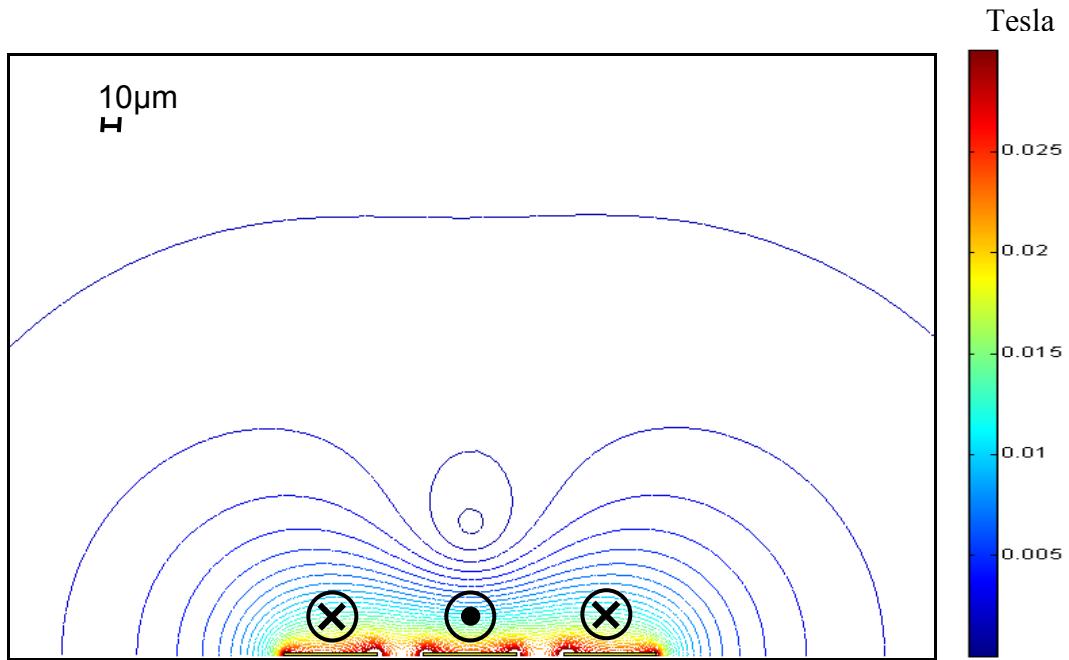

| <b>Figure 27:</b> Magnetic field due to three current carrying wires. The wire has the same dimensions as the actual wires used on the atom chips produced in this thesis.                                                                                                                                                                                               | 49 |

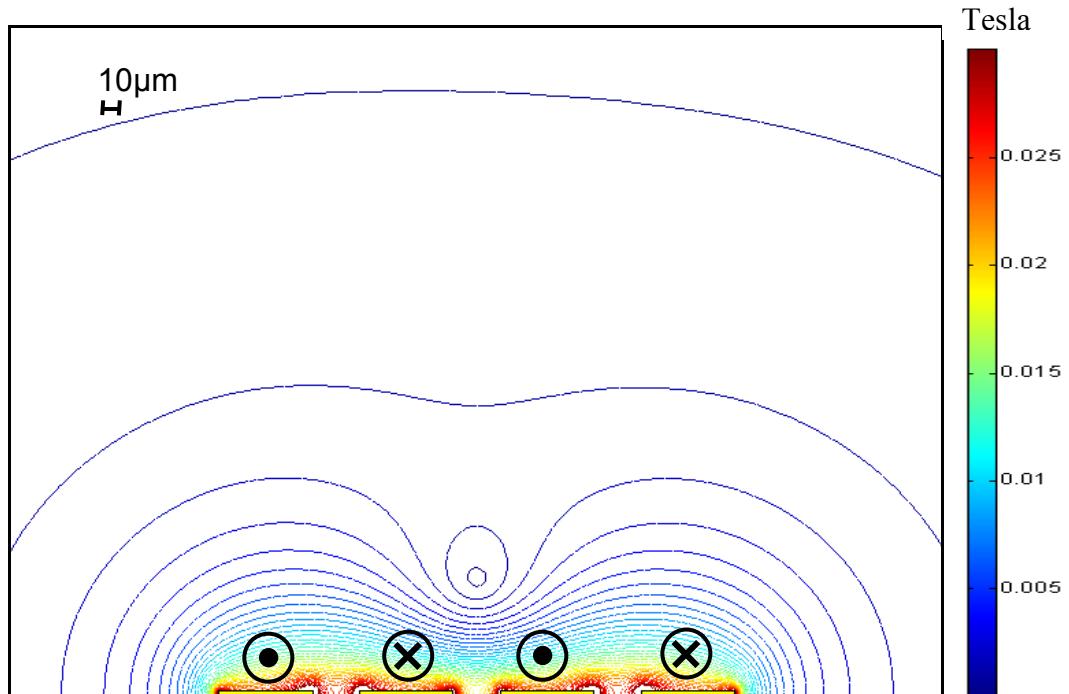

| <b>Figure 28:</b> Magnetic field due to four current carrying wires. The wire has the same dimensions as the actual wires used on the atom chips produced in this thesis.                                                                                                                                                                                                | 49 |

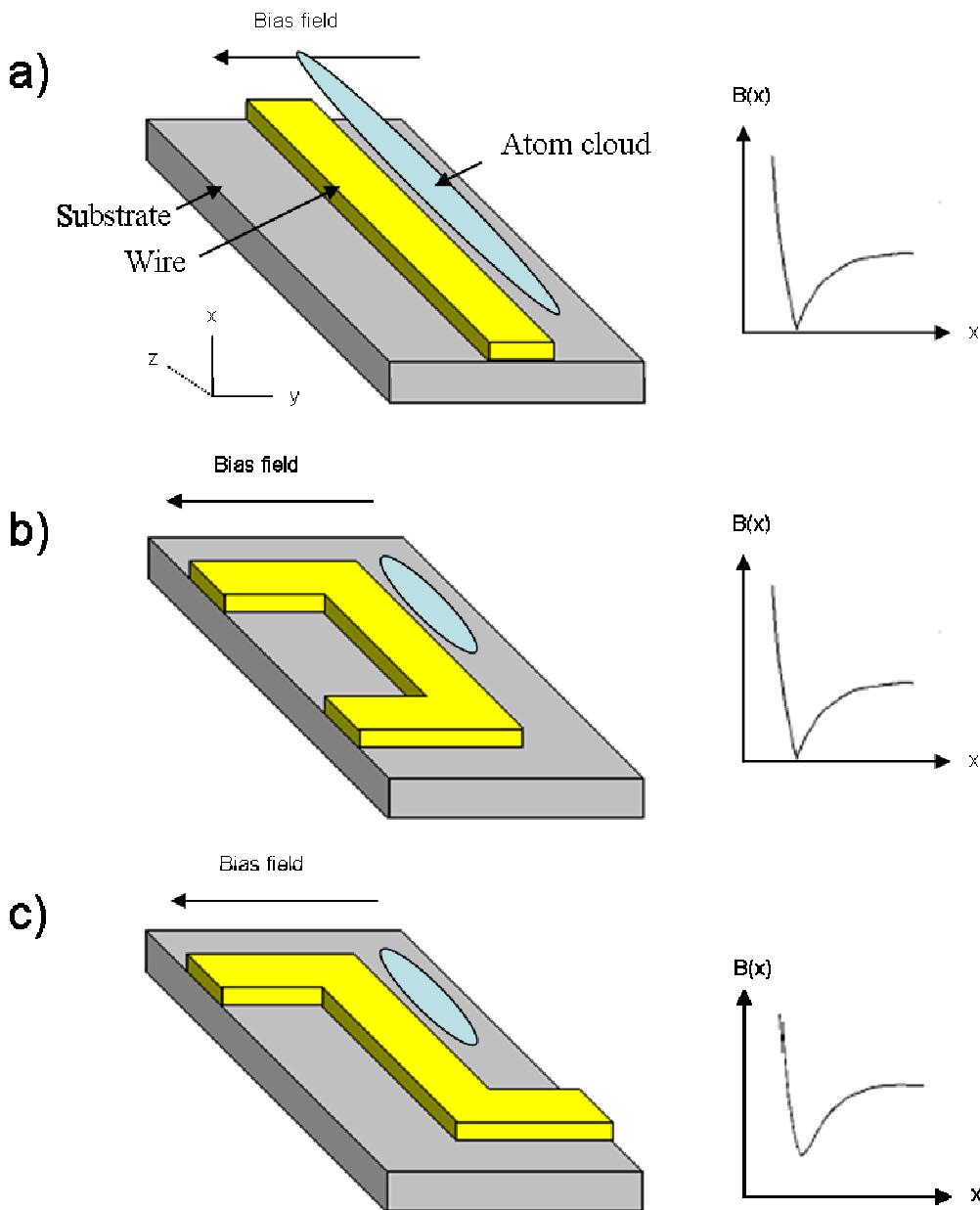

| <b>Figure 29:</b> Figure showing the magnetic field created from a current carrying wire and an external field bias. The straight wire creates an infinite tube of minima (a). The U shaped wire creates a quadrupole trap with a stop on each end of the tube (b) and the Z shaped wire creates a Ioffe-Pritchard trap with the same stops (c) (Adapted from ref [15]). | 51 |

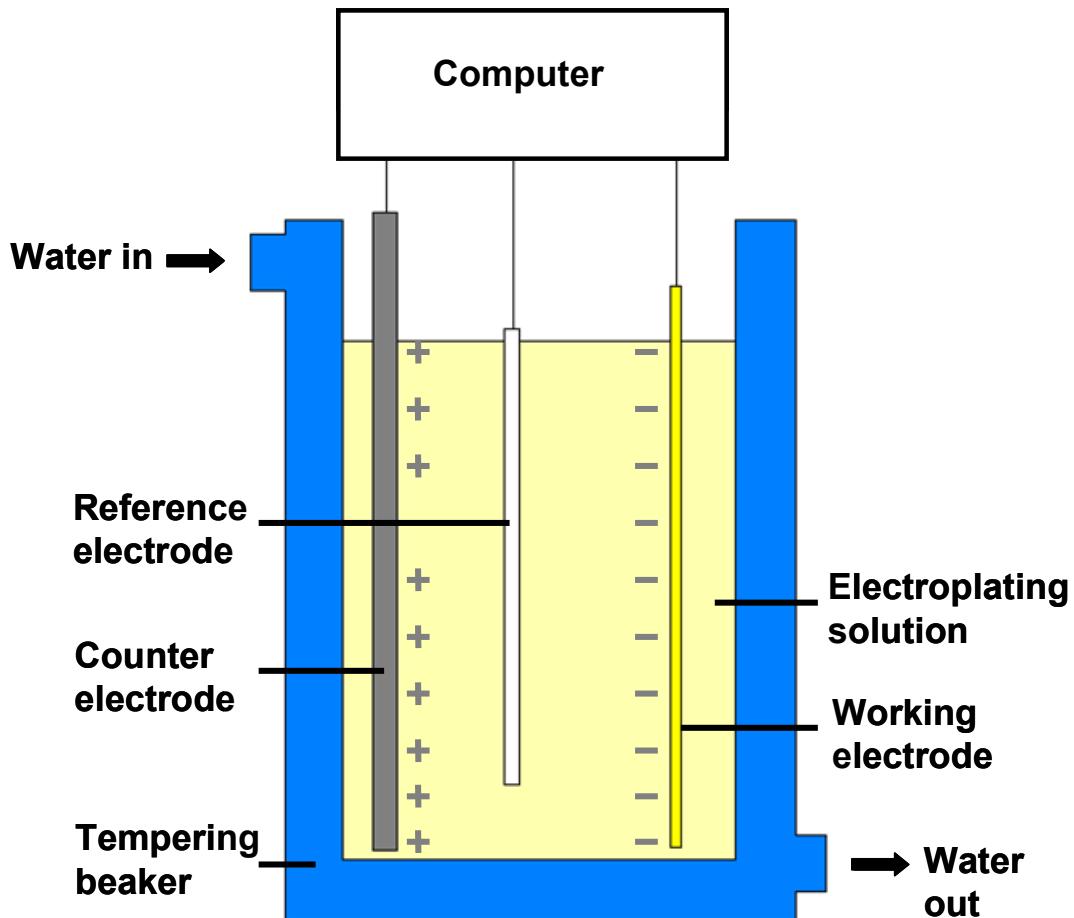

| <b>Figure 30:</b> Image showing the electro deposition setup.                                                                                                                                                                                                                                                                                                            | 58 |

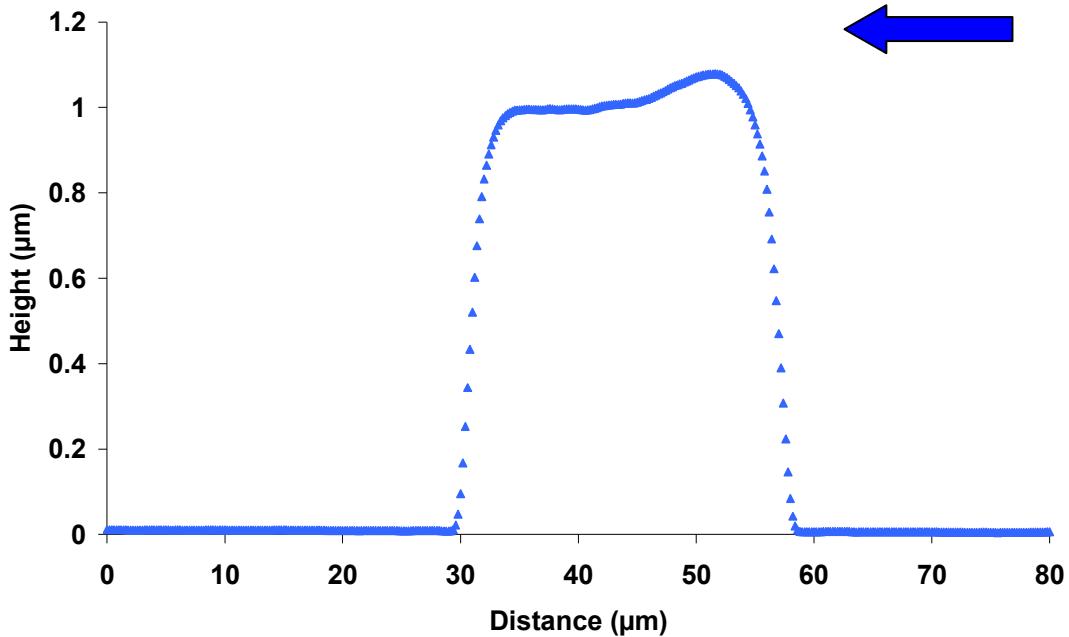

| <b>Figure 31:</b> Graph showing a wire created by electro chemical deposition into a photoresist mould. The electroplating solution was agitated using a magnetic stirrer during the deposition. The arrow shows the direction of fluid flow.                                                                                                                            | 60 |

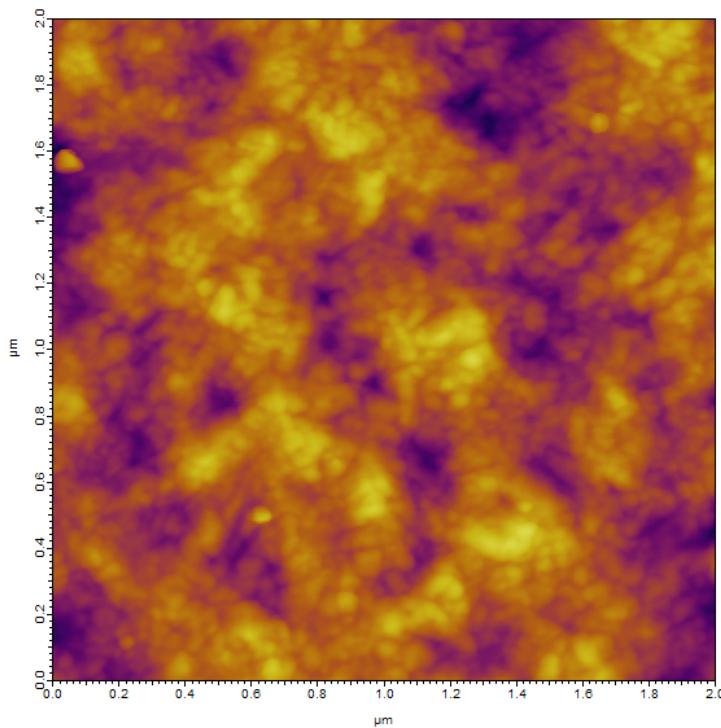

| <b>Figure 32:</b> AFM scan of the top of a wire created by electrochemical deposition in a 40 °C bath                                                                                                                                                                                                                                                                    | 61 |

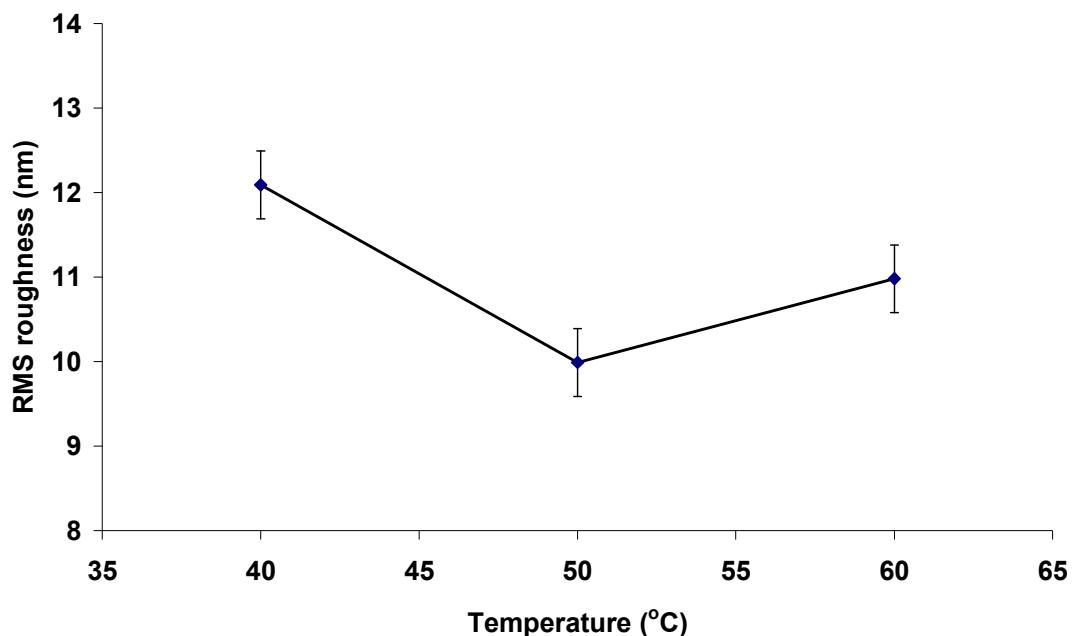

| <b>Figure 33:</b> Graph showing the effect of deposition temperature on the roughness of electroplated gold.                                                                                                                                                                                                                                                             | 61 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

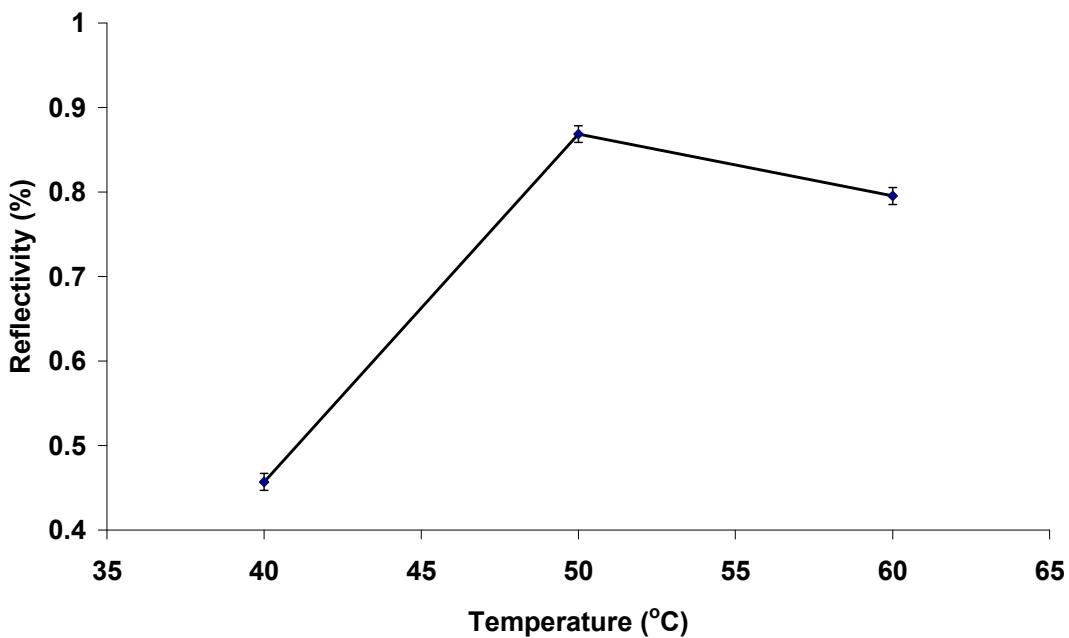

| <b>Figure 34:</b> Graph showing the effect on the reflectivity of electro depositions at different temperatures. ....                                                                                                                                                                                                                                                                                                                                                                                     | 62 |

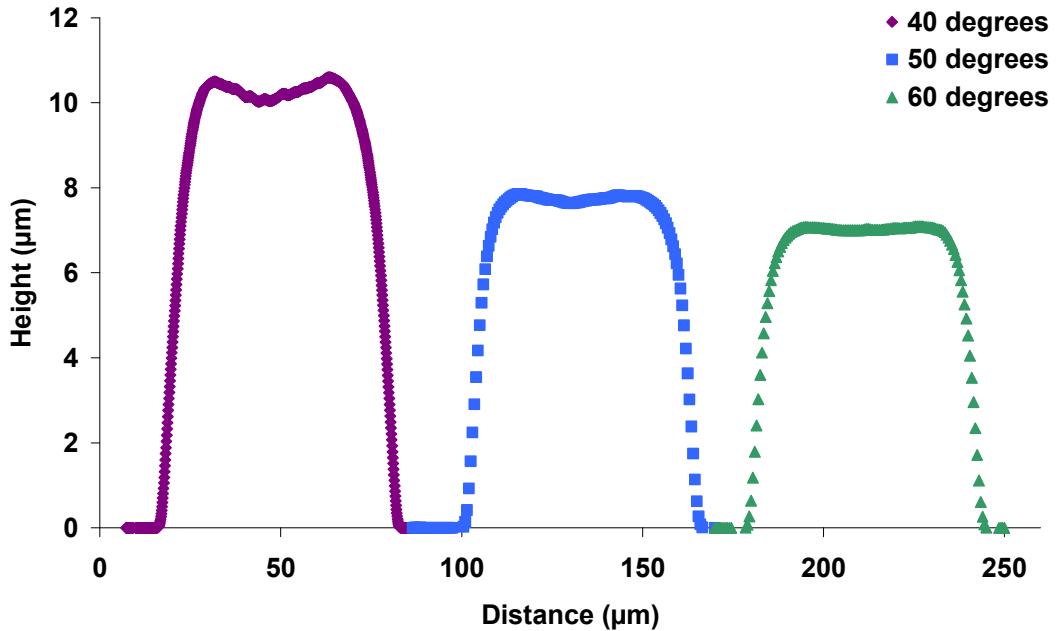

| <b>Figure 35:</b> Graph showing the profile of wires created by electro deposition at different temperatures. ....                                                                                                                                                                                                                                                                                                                                                                                        | 63 |

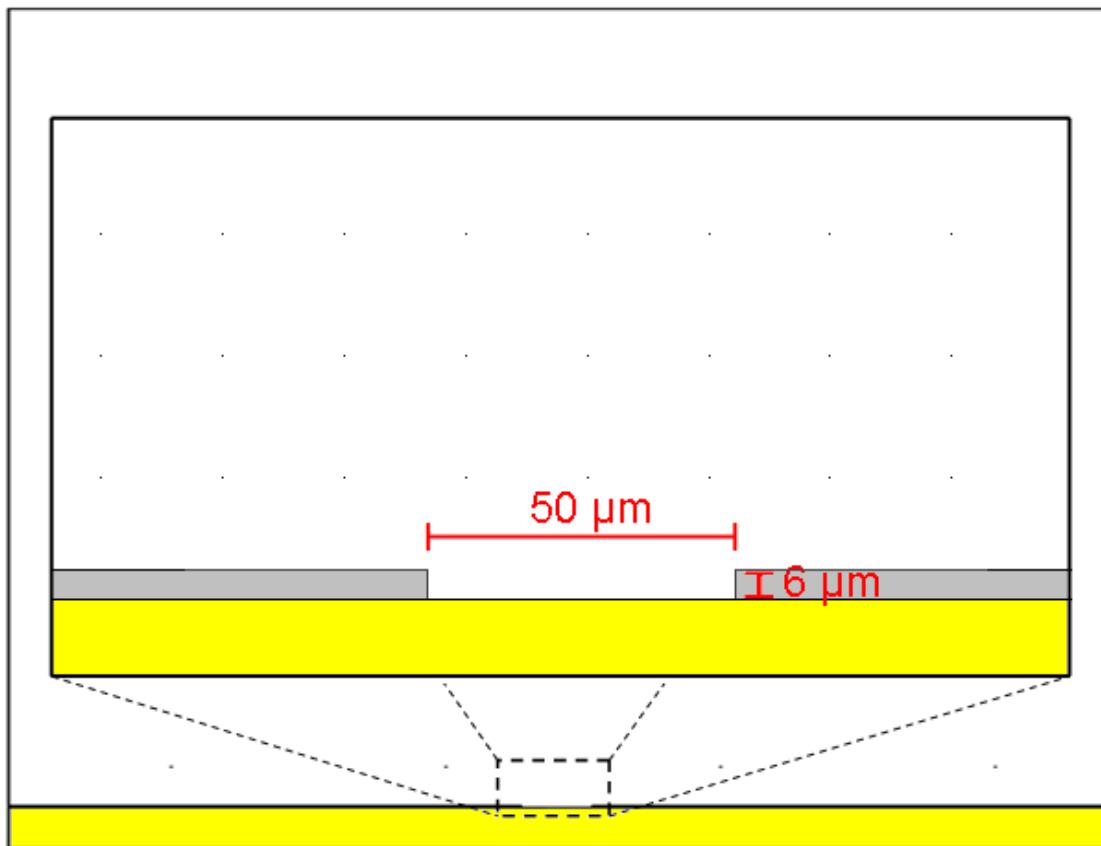

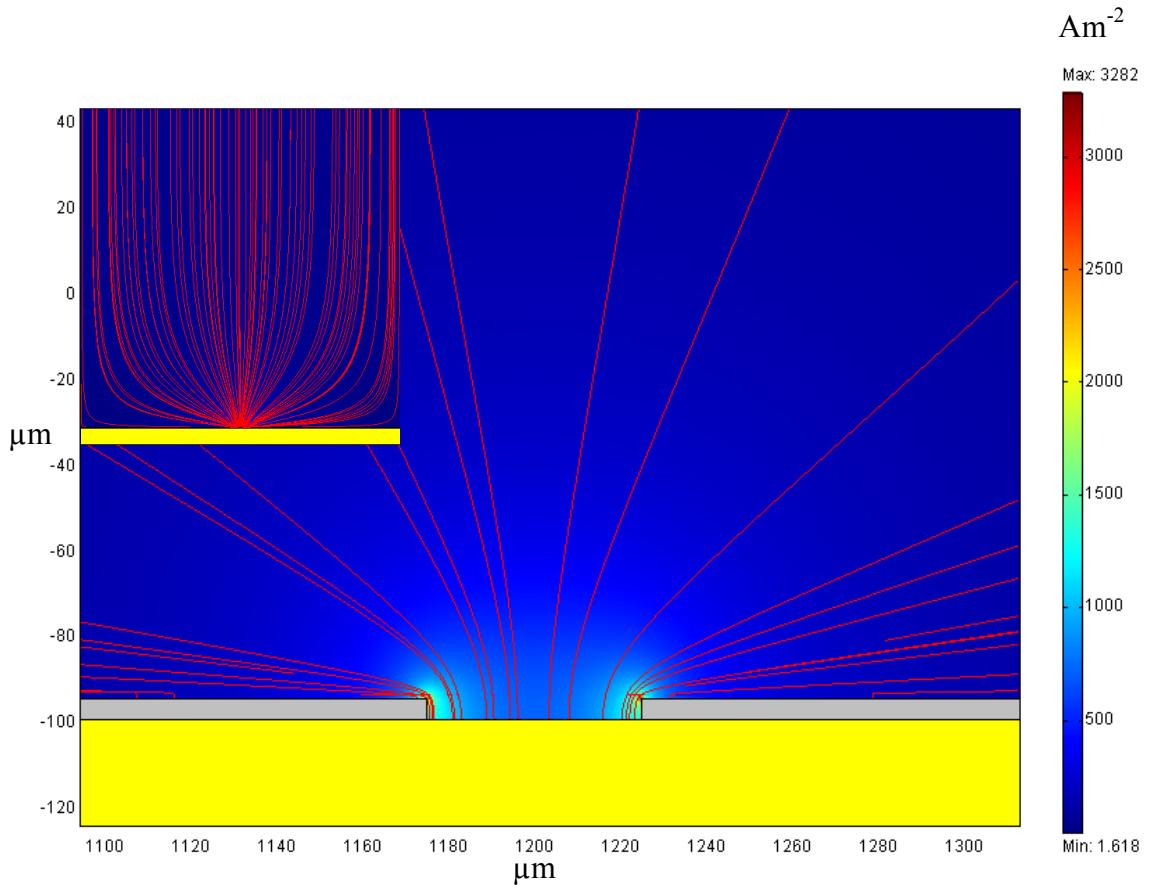

| <b>Figure 36:</b> Figure showing the Femlab simulation setup. A large volume is used to represent the plating bath. The yellow box at the bottom represents the sample being electroplated and the grey areas represent the photoresist mould. ....                                                                                                                                                                                                                                                       | 64 |

| <b>Figure 37:</b> Plot showing a close up of the electroplating openings, the electric field lines are shown in red. The background colour represents the current density in the solution. Top left shows the whole simulated system. ....                                                                                                                                                                                                                                                                | 65 |

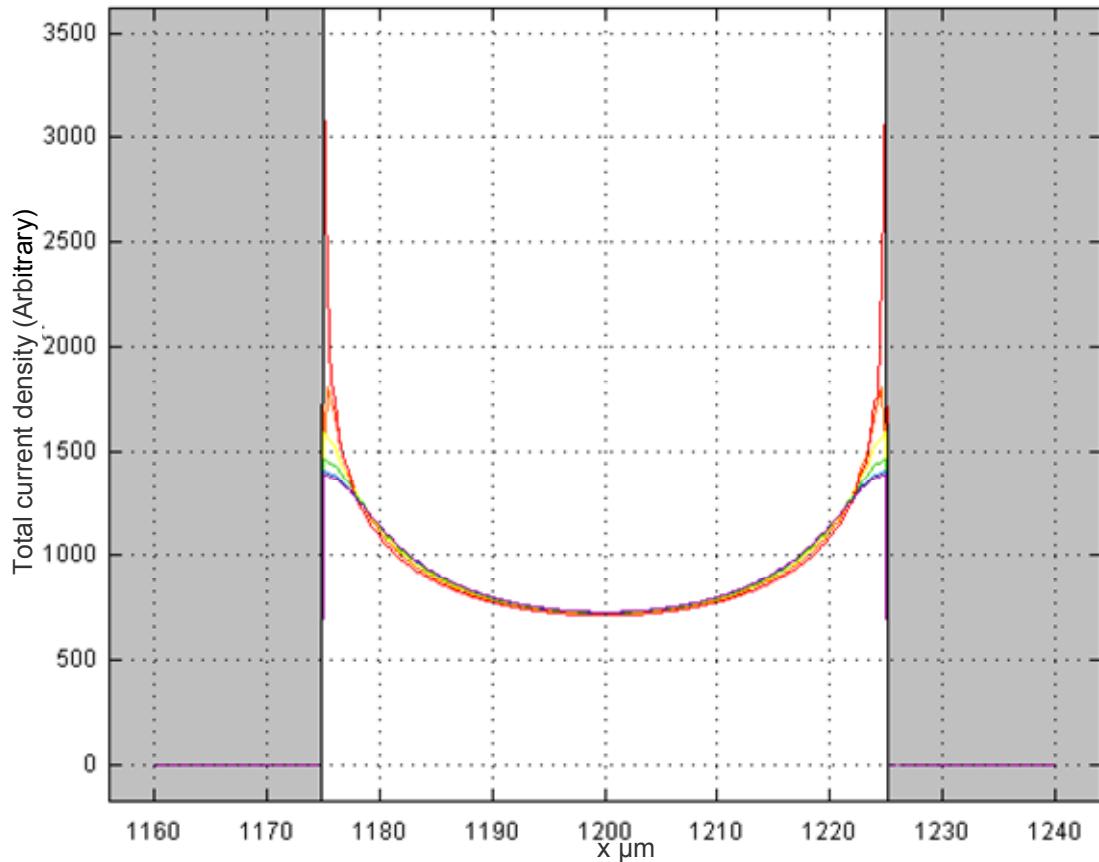

| <b>Figure 38:</b> Graph showing the current density as a function of position in a line on the charged surface (purple); 1 $\mu\text{m}$ (blue), 2 $\mu\text{m}$ (green), 3 $\mu\text{m}$ (yellow), 4 $\mu\text{m}$ (orange) and 5 $\mu\text{m}$ (red) above the surface representing the wafer. The x coordinate corresponds to the position of the line in Figure 37. The grey area represents the area where photoresist is present and the white area represents the opening in the photoresist. .... | 66 |

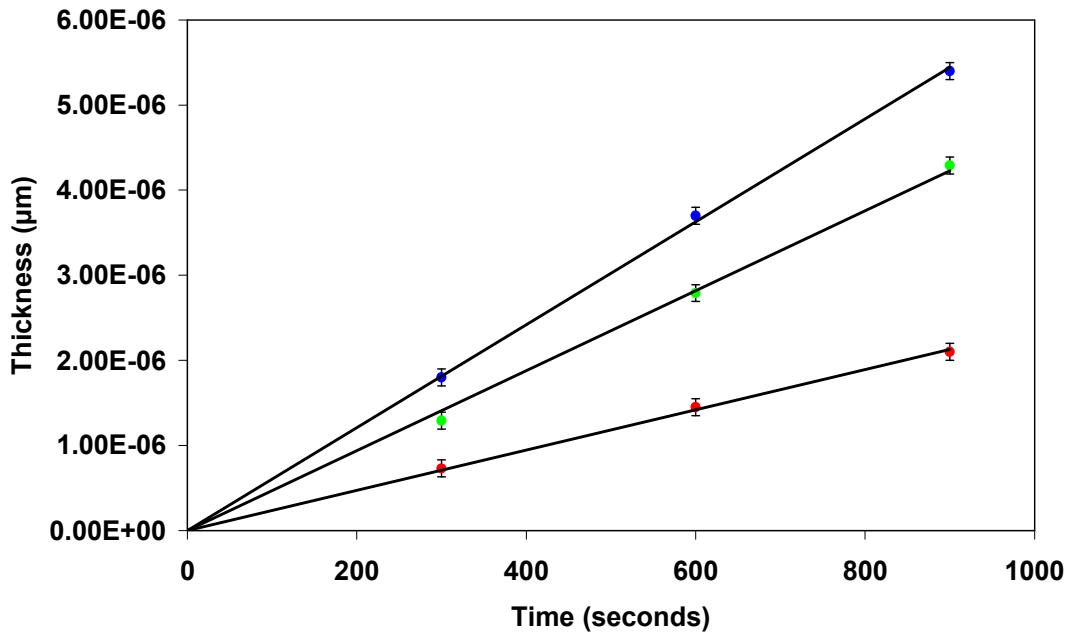

| <b>Figure 39:</b> Graph showing how the thickness varies with time for different current densities; 23.1 $\text{A}/\text{m}^2$ (red) 38.5 $\text{A}/\text{m}^2$ (green) 46.2 $\text{A}/\text{m}^2$ (blue) ....                                                                                                                                                                                                                                                                                            | 67 |

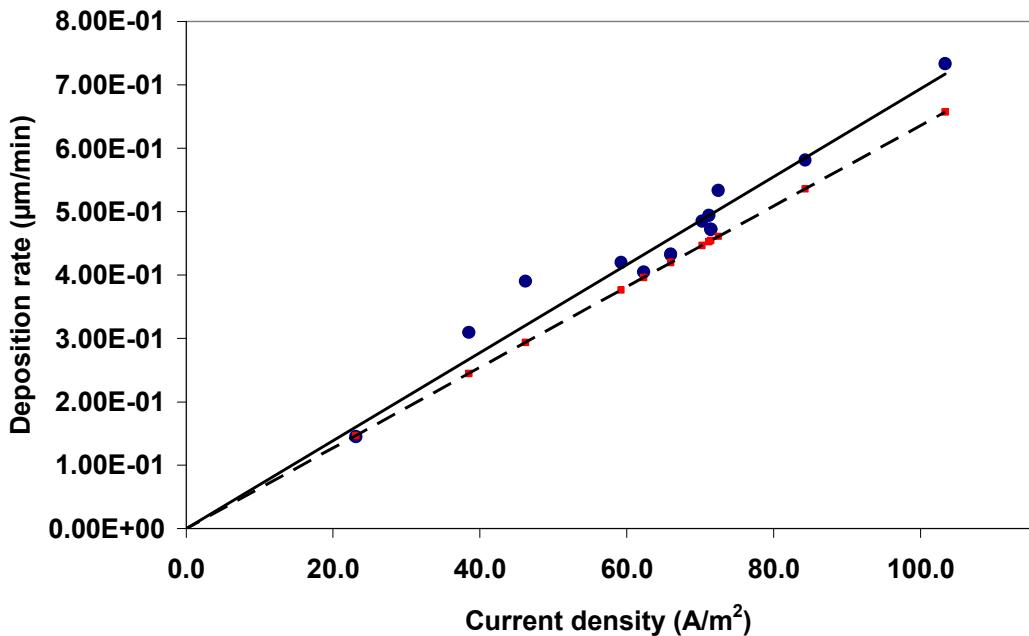

| <b>Figure 40:</b> Graph showing the effect of the current density on the deposition rate of electroplated wires. The solid line represents a best fit line of the experimental data while the doted line is theoretical data. ....                                                                                                                                                                                                                                                                        | 68 |

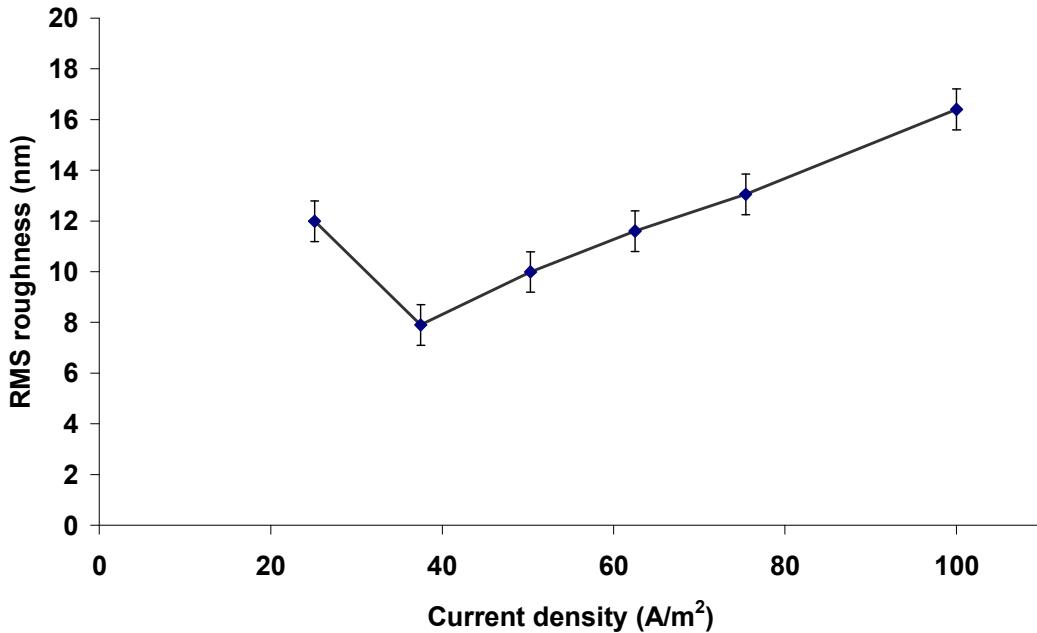

| <b>Figure 41:</b> Graph showing the effect of the current density on the roughness of electroplated gold. ....                                                                                                                                                                                                                                                                                                                                                                                            | 69 |

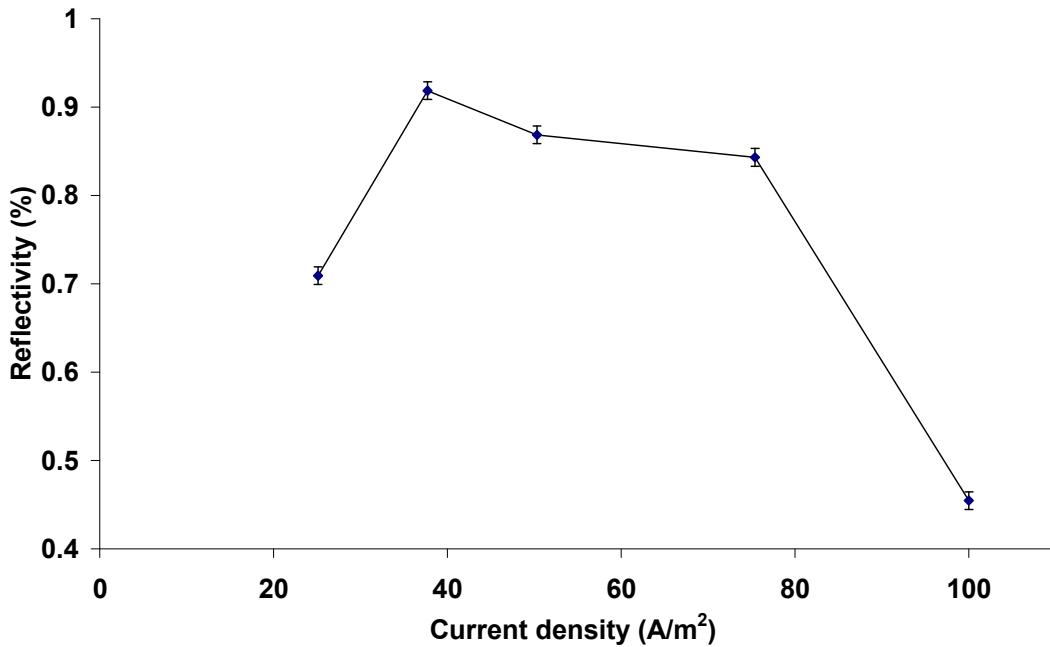

| <b>Figure 42:</b> Graph showing the effect of current density on the reflectivity of electroplated gold at 780 nm. ....                                                                                                                                                                                                                                                                                                                                                                                   | 69 |

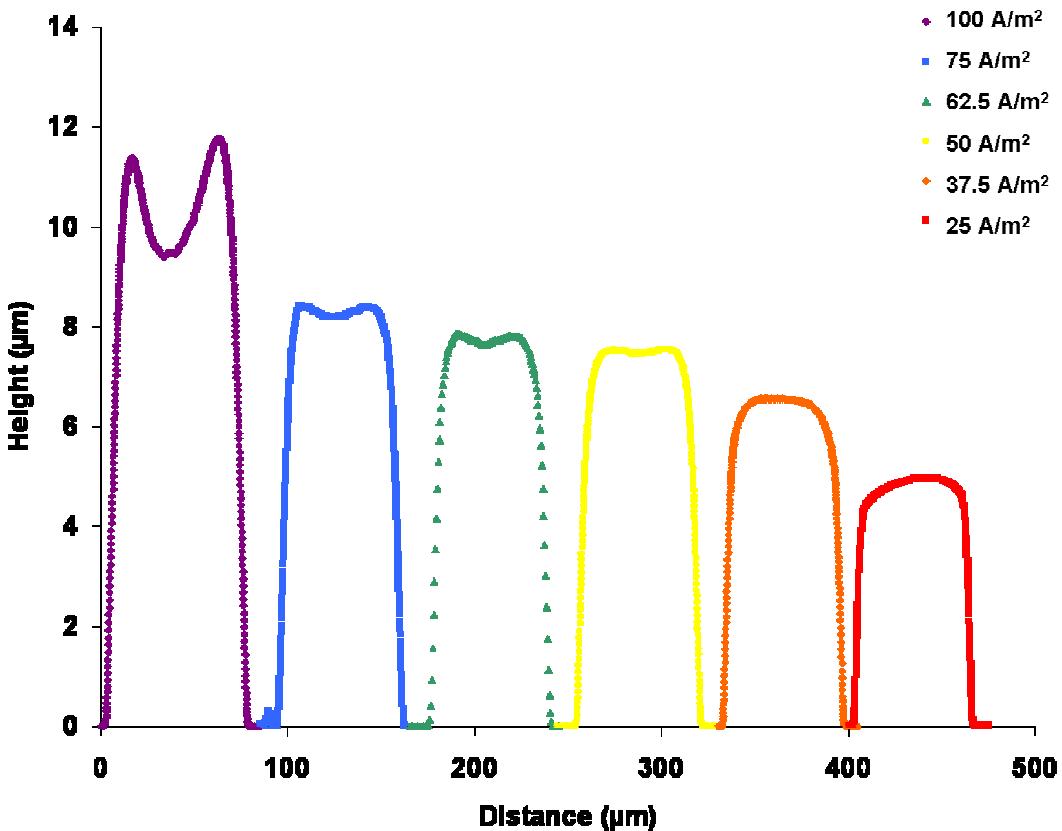

| <b>Figure 43:</b> Graph showing the profile of wires created by electro deposition at different current densities. Each wire was electroplated at a different current density. ....                                                                                                                                                                                                                                                                                                                       | 70 |

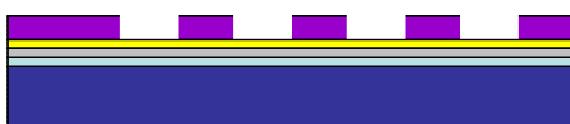

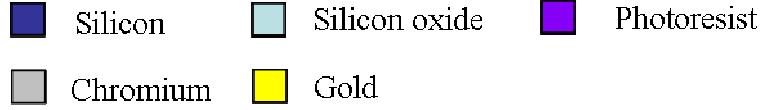

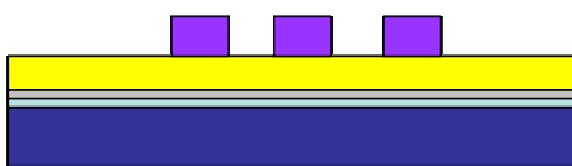

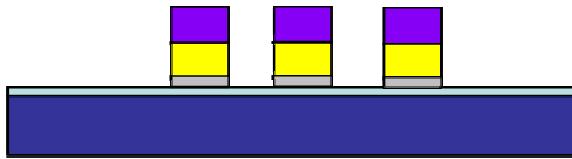

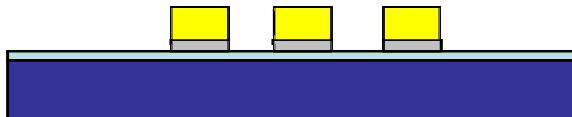

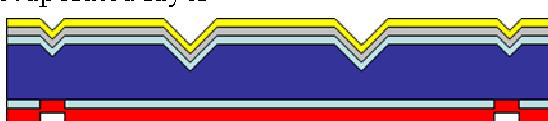

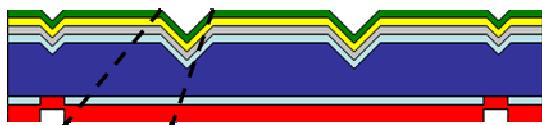

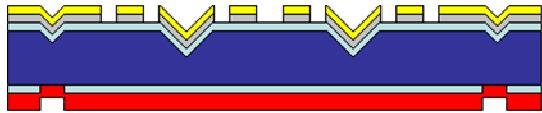

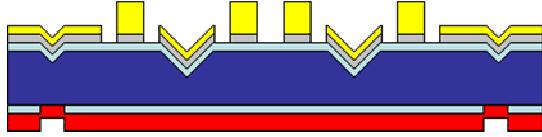

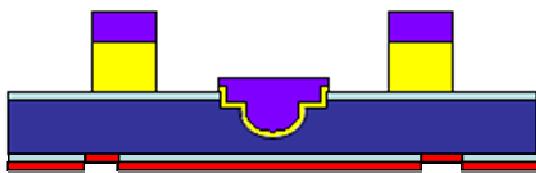

| <b>Figure 44:</b> Process flow an atom guide with electroplated wires. ....                                                                                                                                                                                                                                                                                                                                                                                                                               | 72 |

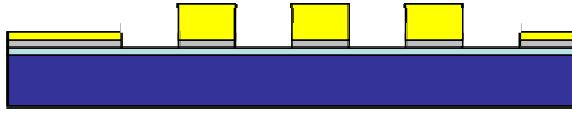

| <b>Figure 45:</b> Mask design used for wire fabrication. The design contains the trapping wires in a Z shape, contact pads for connecting the chip into the MOT, gold mirrors to allow a mirror MOT to be formed from the chip and a large contact pad to allow a crocodile clip to easily be applied for electroplating the sample ....                                                                                                                                                                  | 73 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

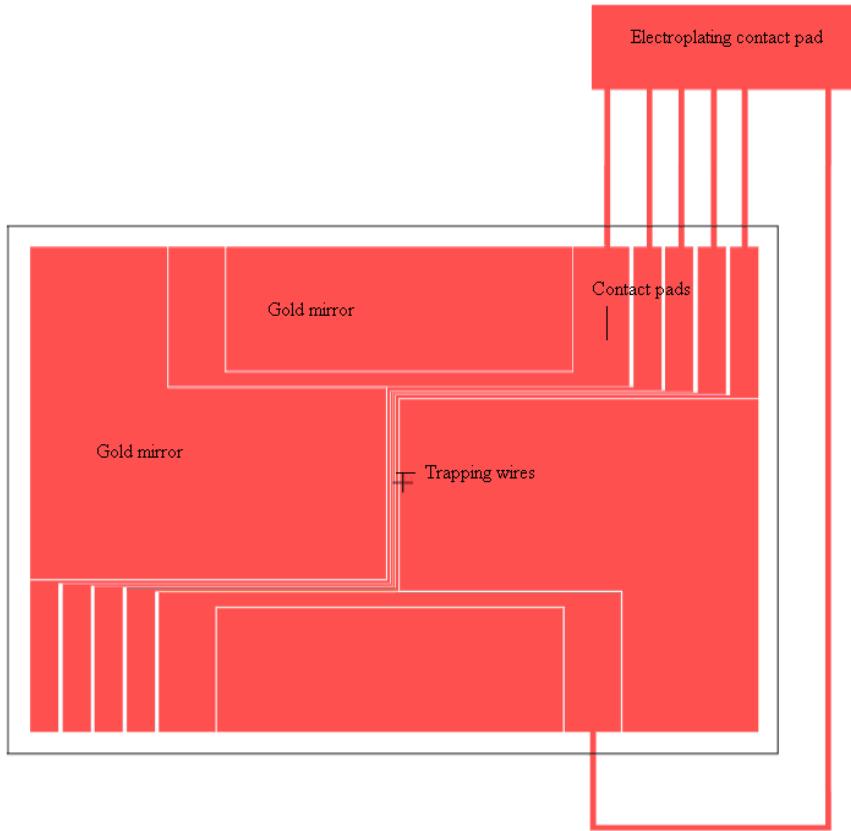

| <b>Figure 46:</b> Atom guide with plating mould in place. The resist is covering all areas except the wires and contact pads which appear as a lighter gold colour.....                                                                                                                                                                                                                                                                         | 74 |

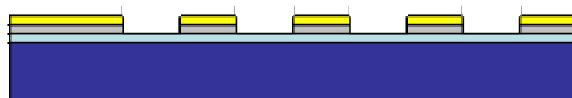

| <b>Figure 47:</b> Process flow for fabricating the gold wires via ion beam milling.....                                                                                                                                                                                                                                                                                                                                                         | 77 |

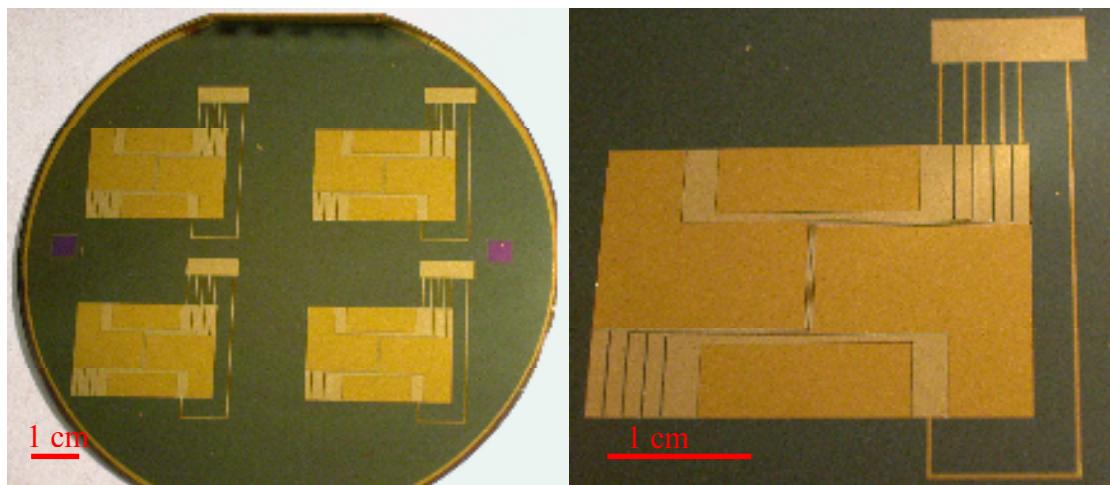

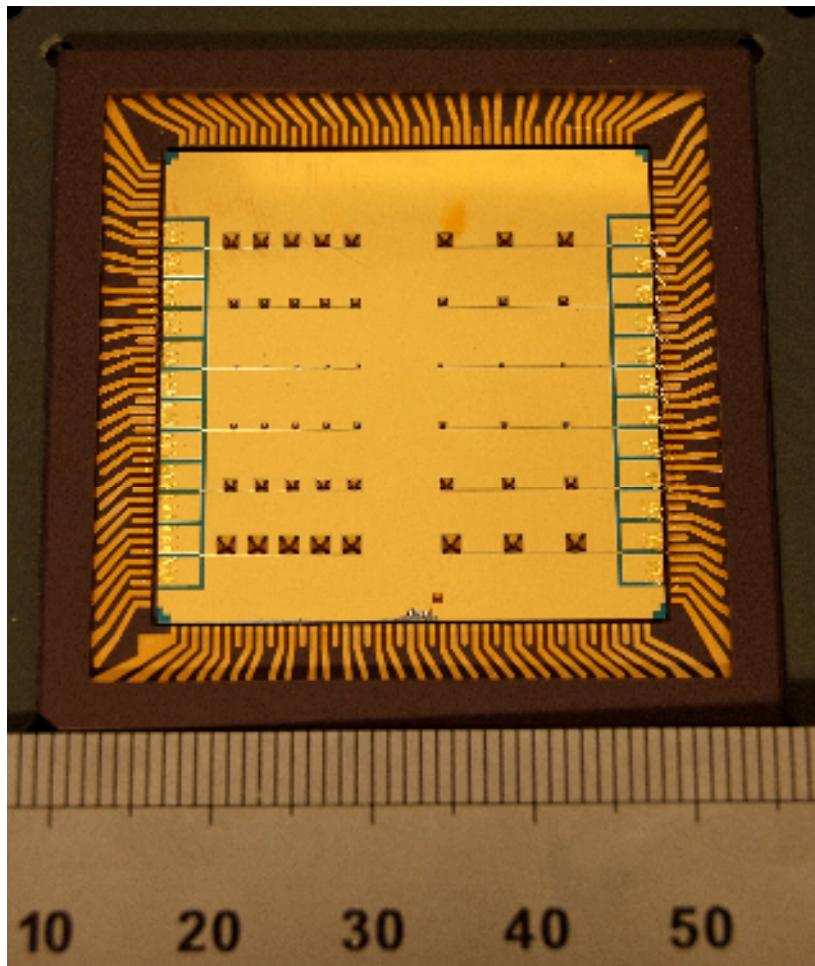

| <b>Figure 48:</b> Image of the wafer and an individual atom chip.....                                                                                                                                                                                                                                                                                                                                                                           | 78 |

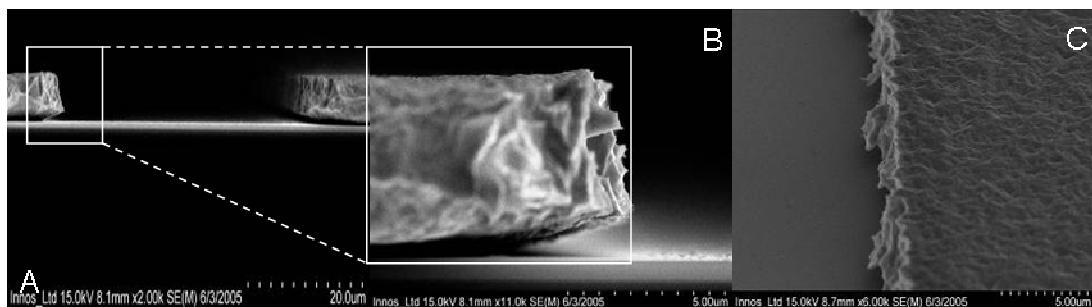

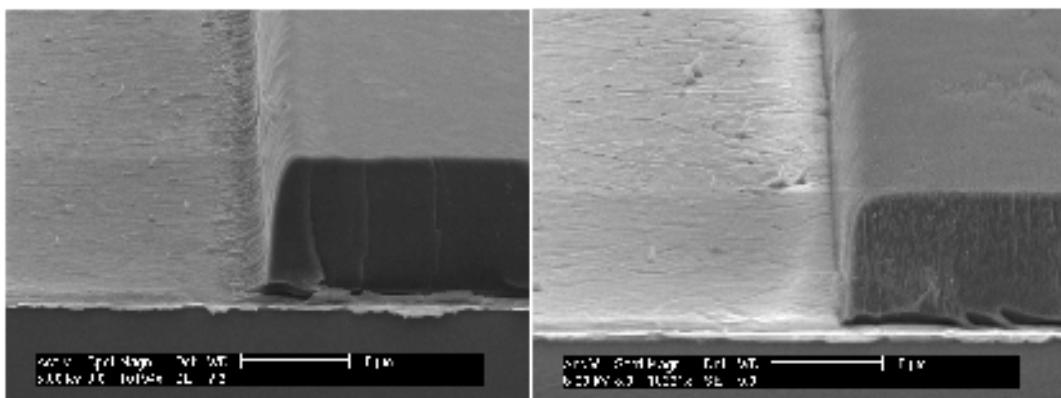

| <b>Figure 49:</b> Scanning electron microscope images of microfabricated wires. A: Cross section of two wires. B: Magnified view of one wire edge.....                                                                                                                                                                                                                                                                                          | 79 |

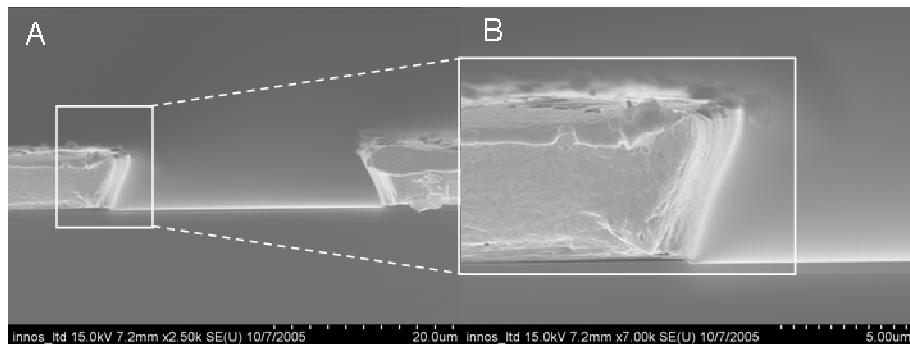

| <b>Figure 50:</b> Scanning electron microscope images of microwires fabricated by ion beam milling. A: Cross section of two wires. B: Magnified view of one wire edge. .                                                                                                                                                                                                                                                                        | 80 |

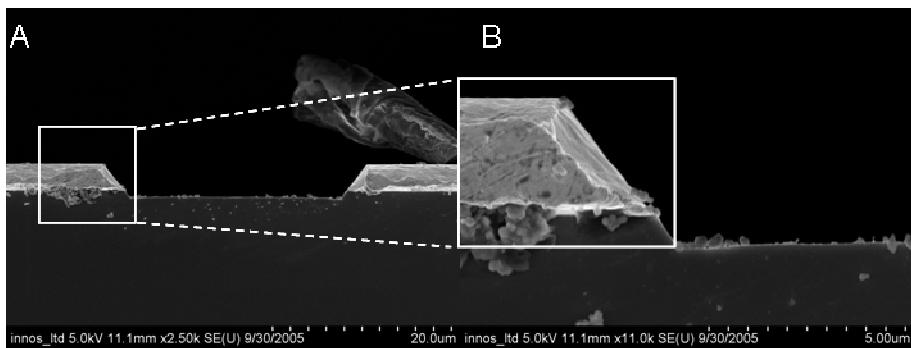

| <b>Figure 51:</b> Scanning electron microscope images of microwires fabricated by wet etching. A: Cross section of two wires. B: Magnified view of one wire edge. C: Top view of the wires sidewall.....                                                                                                                                                                                                                                        | 80 |

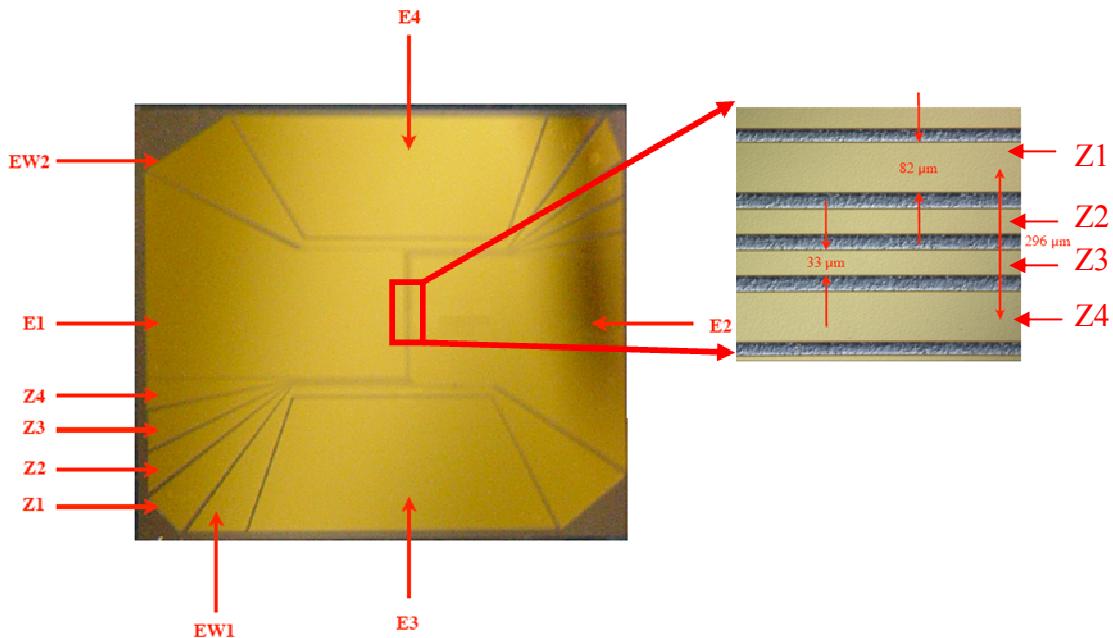

| <b>Figure 52:</b> Layout of the atom chip showing the whole chip and a close up of the central trapping region. Four current carrying wires can be seen creating the Z trap across the centre of the chip (Z1-Z4) and two end wires EW1,2 which provide additional axial confinement.....                                                                                                                                                       | 81 |

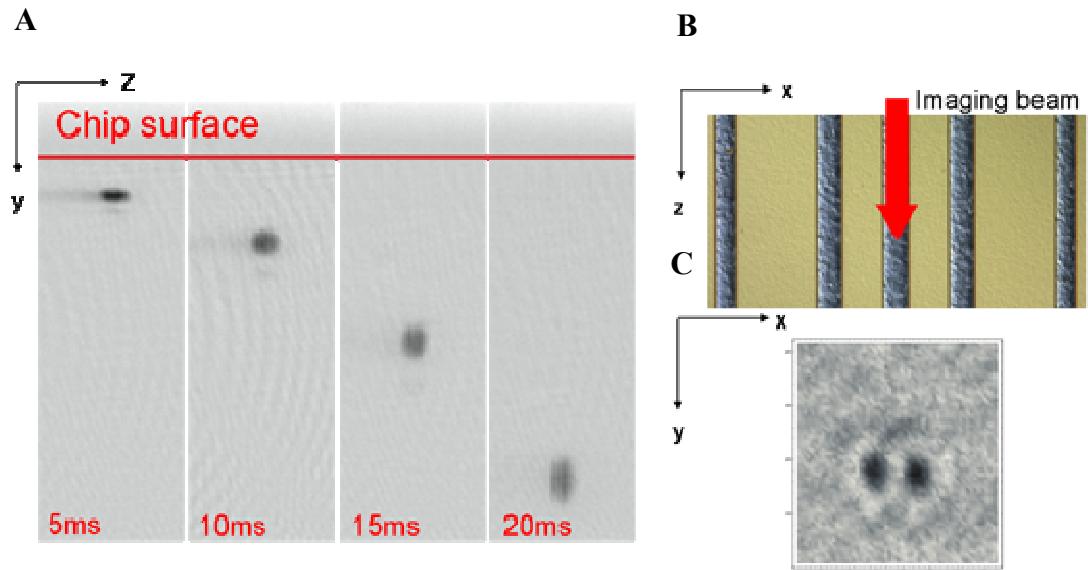

| <b>Figure 53:</b> Image showing a BEC with $\sim 2 \times 10^5$ atoms that have been trapped on the atom guide. a) Shows atoms in free fall having been trapped and confined on the atom guide, b) shows the close up of the atom guide used to trap these atoms and c) shows a double well potential having split the BEC into two separate wells (Taken from ref[117]). .....                                                                 | 83 |

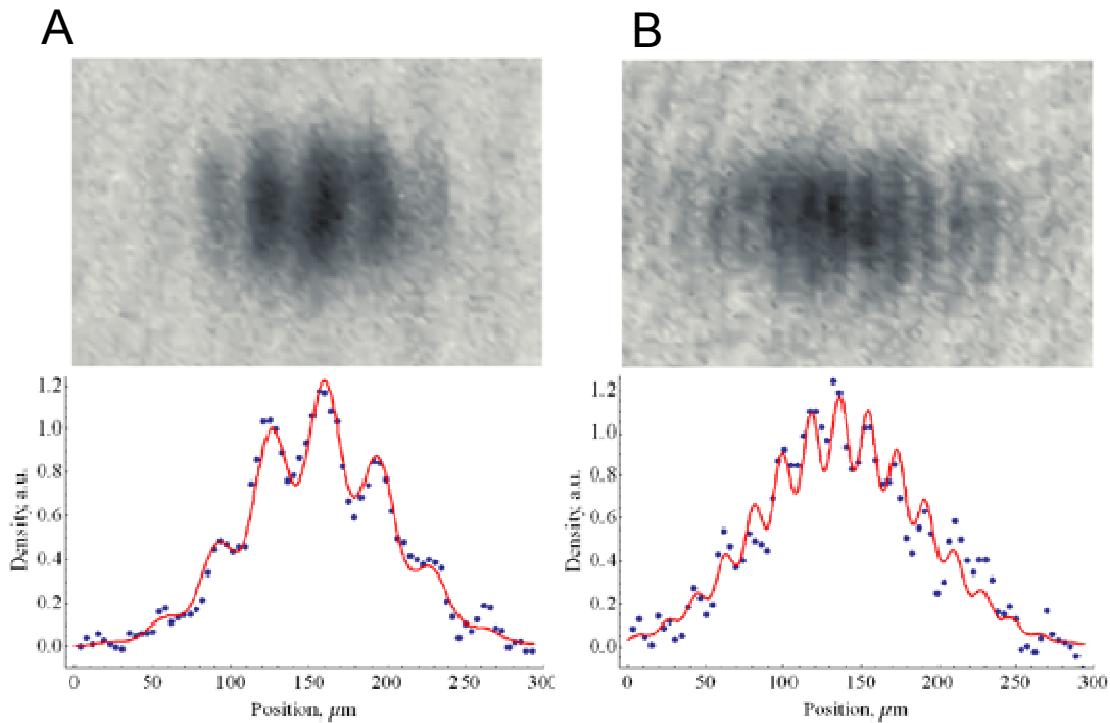

| <b>Figure 54:</b> Interference fringes visible after 16ms time of flight. Both A and B show the fringes produced by the quantum wave interference. B shows a cloud split by a higher RF-intensity than A, leading to a larger well separation and smaller fringe spacing. The red line shows the curve fit of a modulated Gaussian envelope and the blue dots represent the density measured by absorption imaging (Taken from ref [117])...... | 84 |

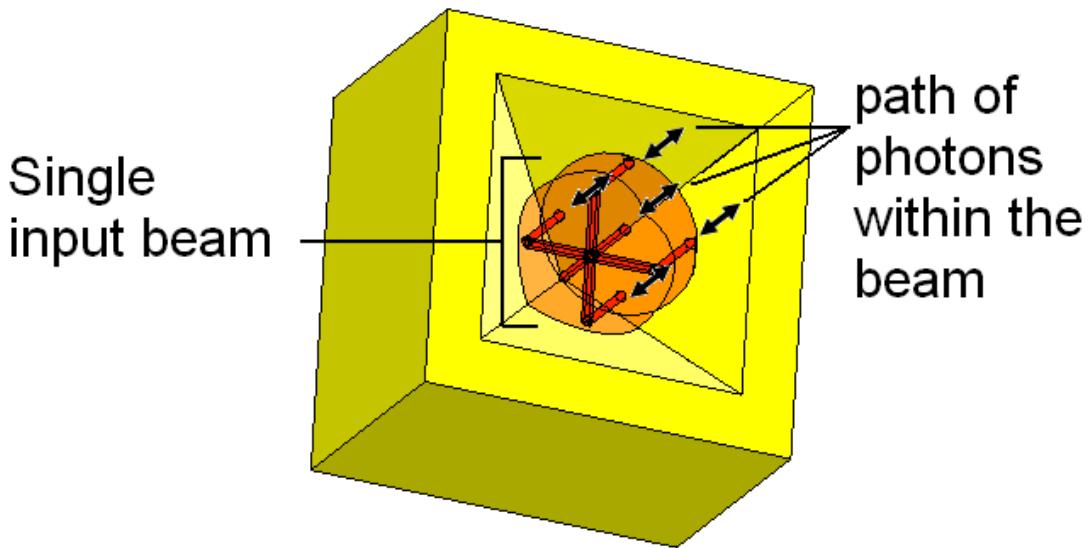

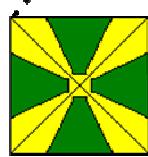

| <b>Figure 55:</b> Diagram showing a laser beam incident on a pyramidal pit. Within the laser beam the standard six beam MOT is created by the incident and reflected photons. ....                                                                                                                                                                                                                                                              | 86 |

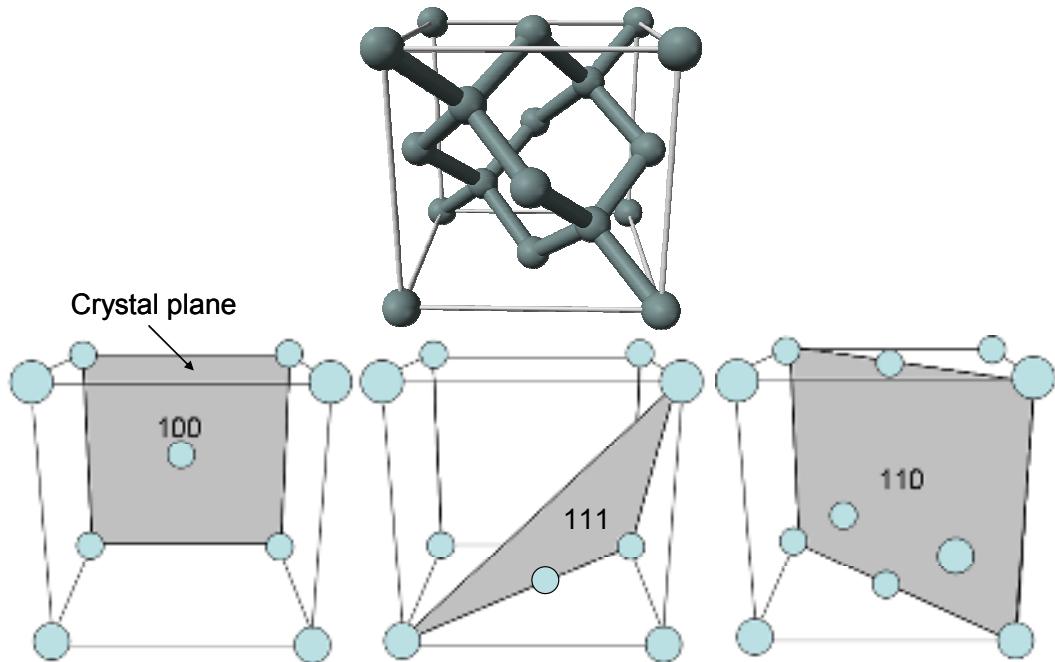

| <b>Figure 56:</b> A face centered cubic unit cell as formed by silicon. Also shown are some of the crystal planes (Adapted from ref [118])......                                                                                                                                                                                                                                                                                                | 87 |

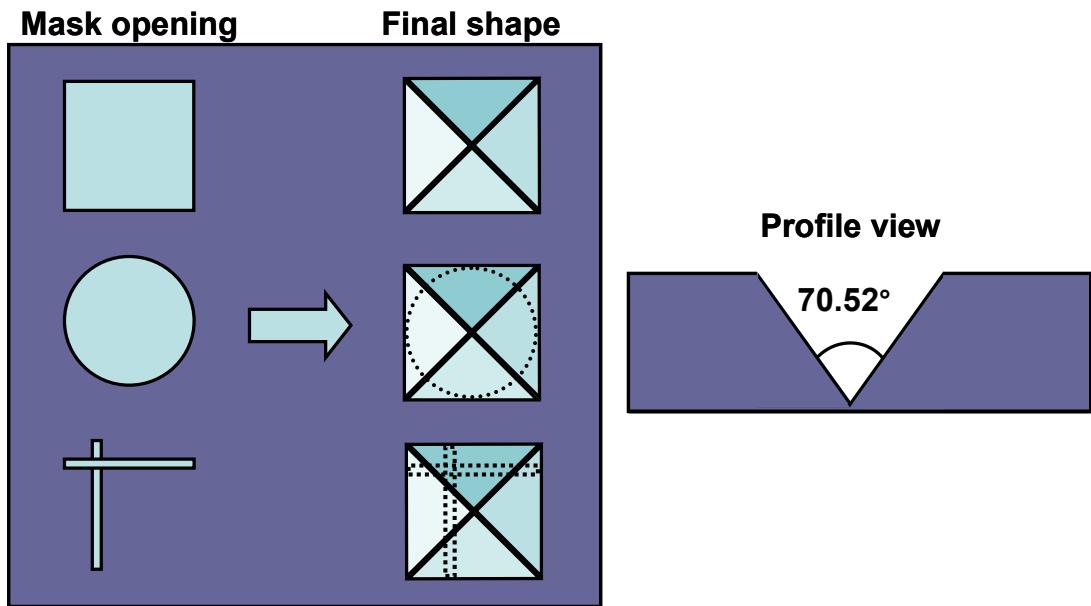

| <b>Figure 57:</b> Picture showing the effect of different openings on the final etch shape after placing {100} wafers into KOH. ....                                                                                                                                                                                                                                                                                                            | 88 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

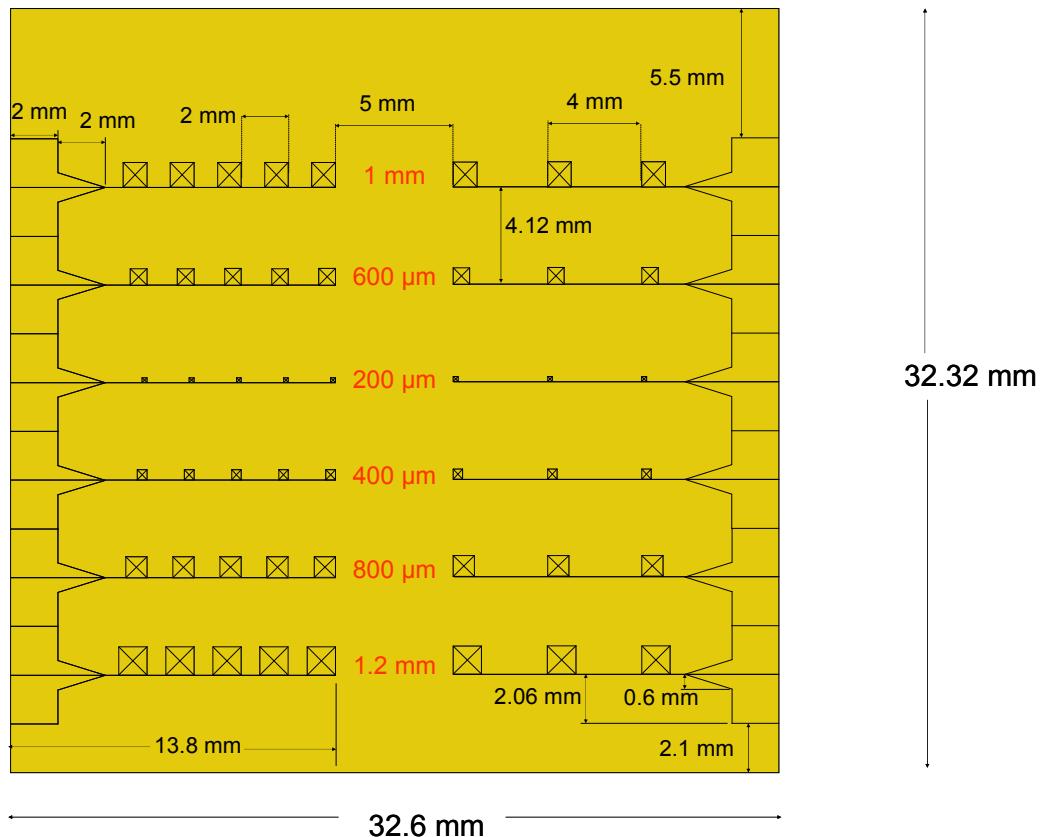

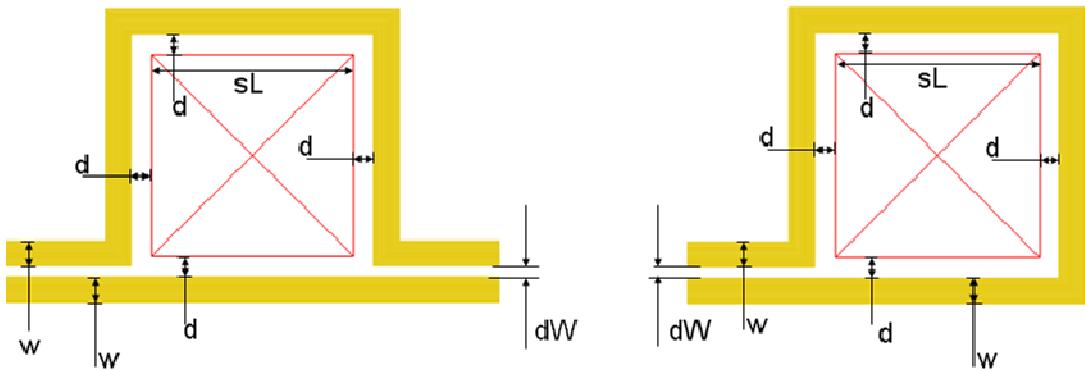

| <b>Figure 58:</b> Schematic showing the design of the pyramidal chip. The squares with crosses represent the pyramidal pits while the lines represent the wires circulating and connecting the sets of pyramids together. To the left and right of the chip large bond pads are seen these are needed for wire bonding the chip into a package. The red writing denotes the size of the pyramidal opening.....                                                                                                 | 89  |

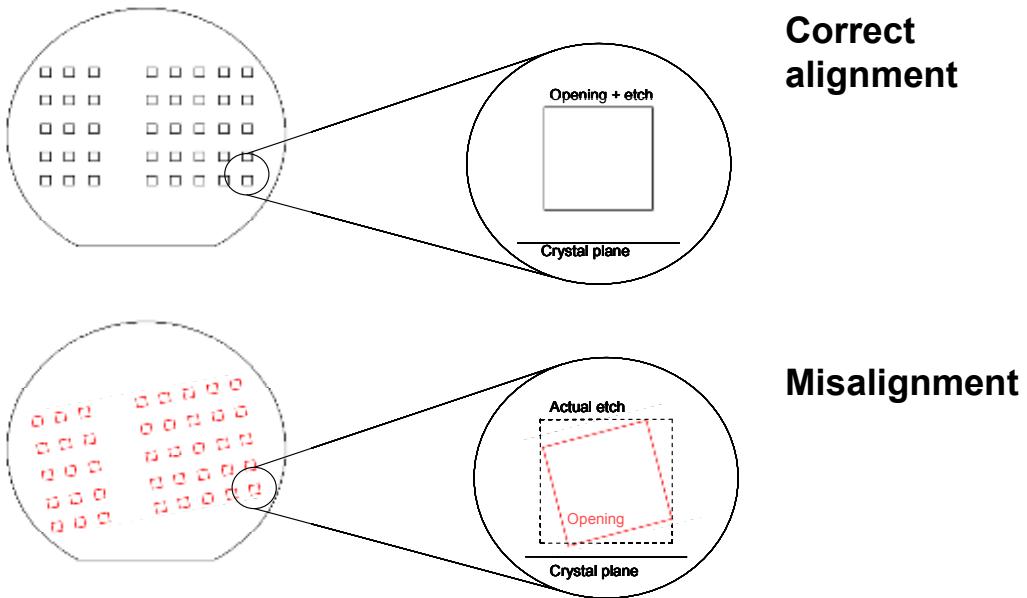

| <b>Figure 59:</b> Diagram showing the result of misalignment of the initial opening on the subsequent KOH etch of the pyramids.....                                                                                                                                                                                                                                                                                                                                                                            | 91  |

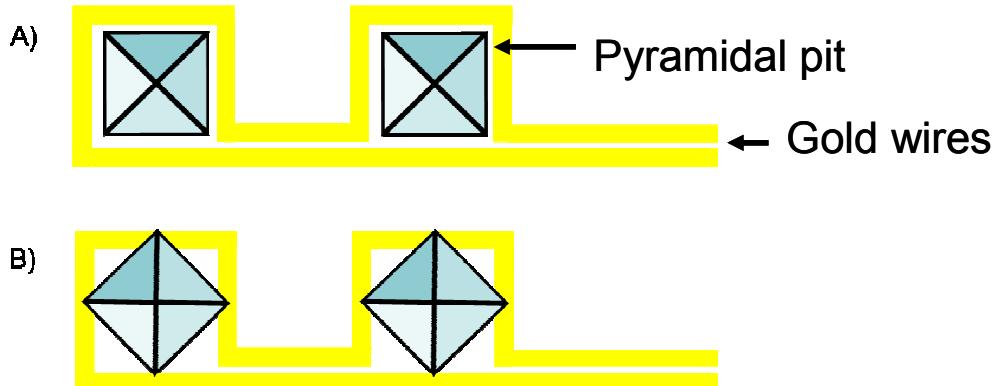

| <b>Figure 60:</b> Image showing the problem of misalignment to the crystal planes on the wire placement. A) shows the correct alignment while B) shows pyramids of the same size but created with the rows of pyramids not aligned to the crystal planes. The wires can clearly not be rotated to fit this new orientation. ....                                                                                                                                                                               | 92  |

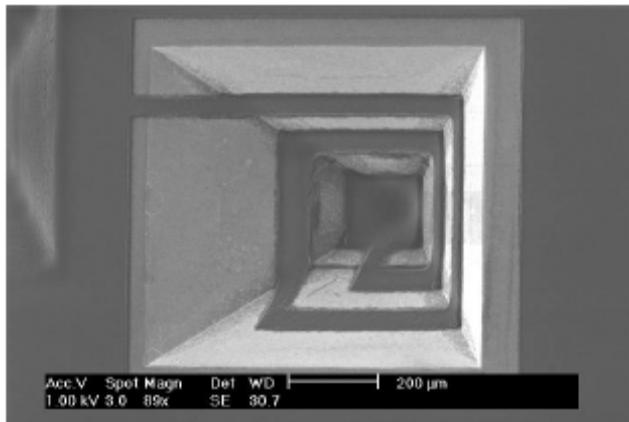

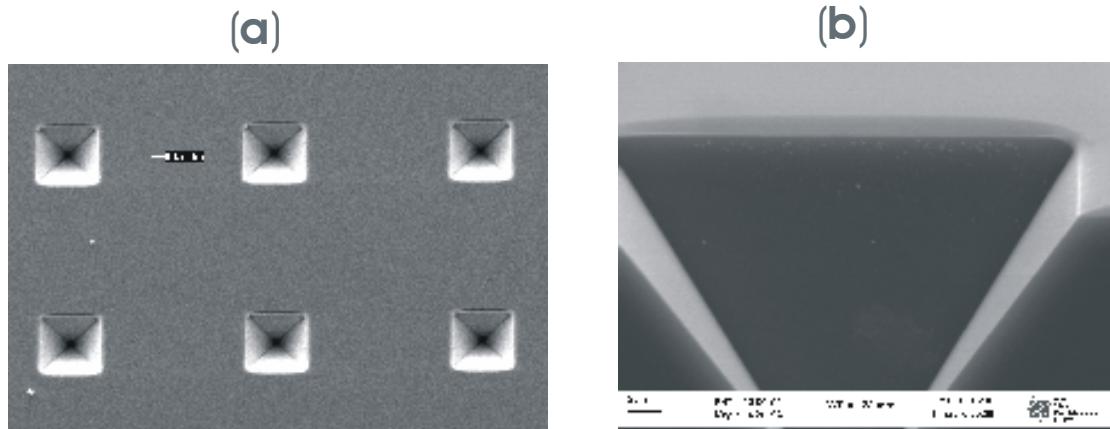

| <b>Figure 61:</b> SEM images of etched and gold coated pyramids: (a) showing the top view of an array of pyramids with pitch 100 $\mu$ m, (b) showing a cross section of a single pyramid with an opening 30 $\mu$ m wide corresponding to a depth of 21.3 $\mu$ m....                                                                                                                                                                                                                                         | 93  |

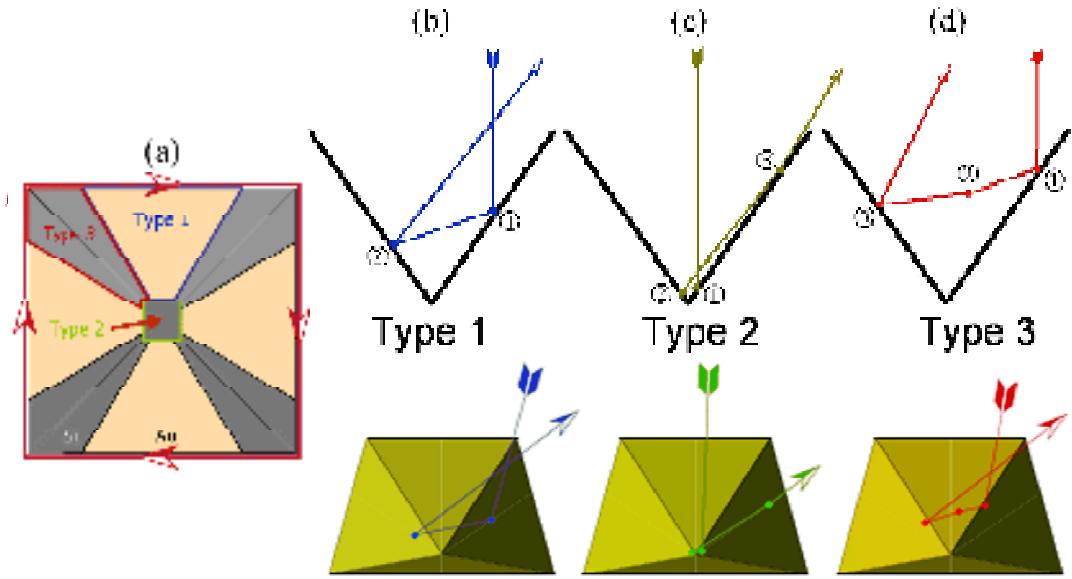

| <b>Figure 62:</b> (a) Plan view of pyramid showing the three regions of reflection and the encircling current. (b) Cross section through pyramid and 3D projection showing a type-1 reflection. (c) Type-2 reflection. (d) Type-3 reflection where the ray is intercepted by the adjacent mirror at the point marked 2.....                                                                                                                                                                                    | 94  |

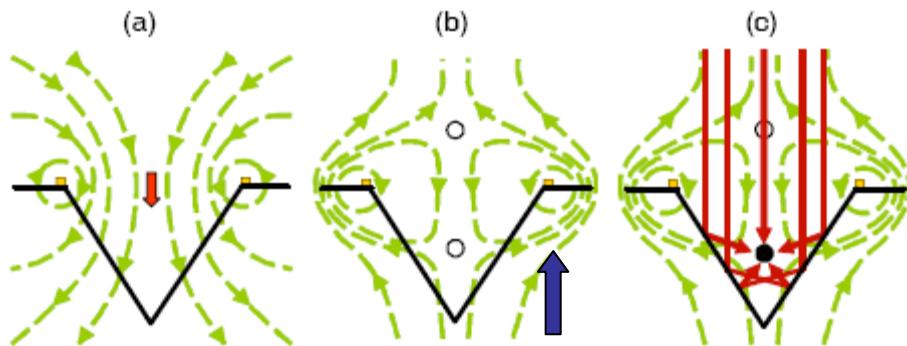

| <b>Figure 63:</b> (a) Dashed lines: magnetic field created solely by the wires around the pyramid opening. Block arrow: maximum field strength is at the centre of the loop. (b) With the addition of a uniform bias, whose direction is indicated by the blue arrow, the net field acquires two minima, indicated by solid circles. (c) Circularly polarised light creates a magneto-optical trap at the field minimum indicated by a filled circle. The beams that contribute are shown as solid arrows..... | 96  |

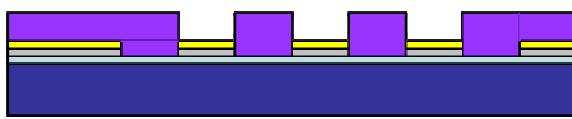

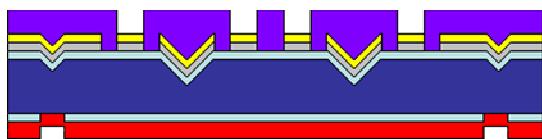

| <b>Figure 64:</b> Process flow for the creation of pyramidal micromirrors.....                                                                                                                                                                                                                                                                                                                                                                                                                                 | 99  |

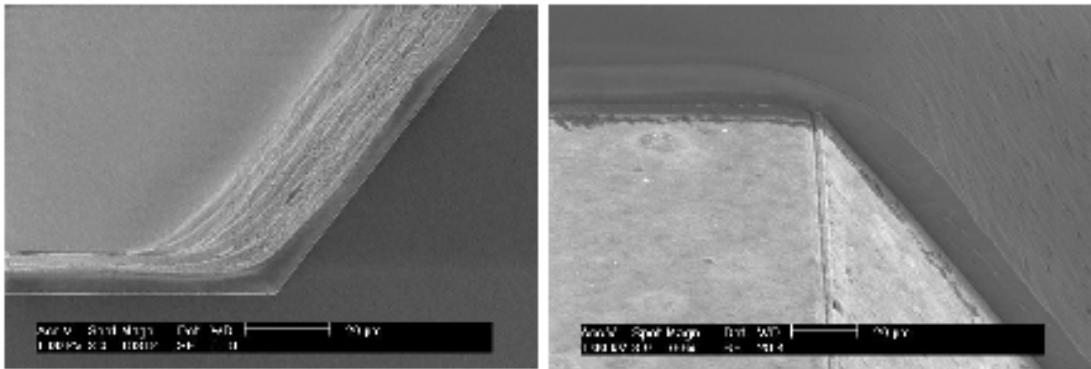

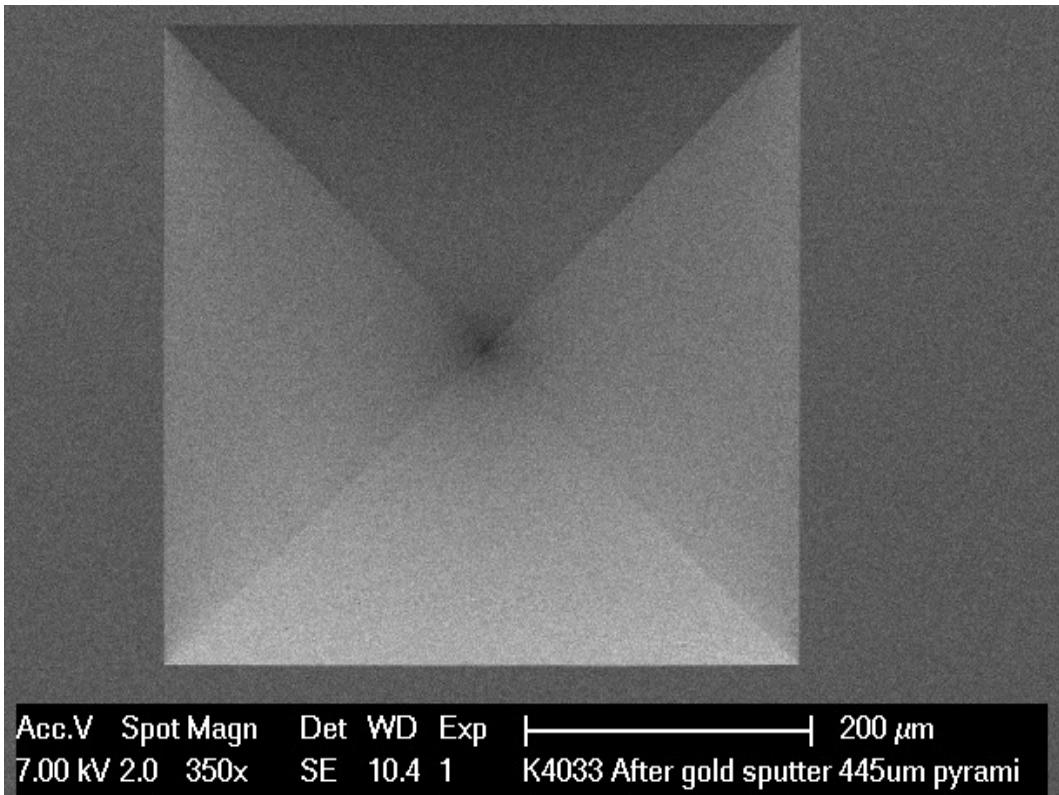

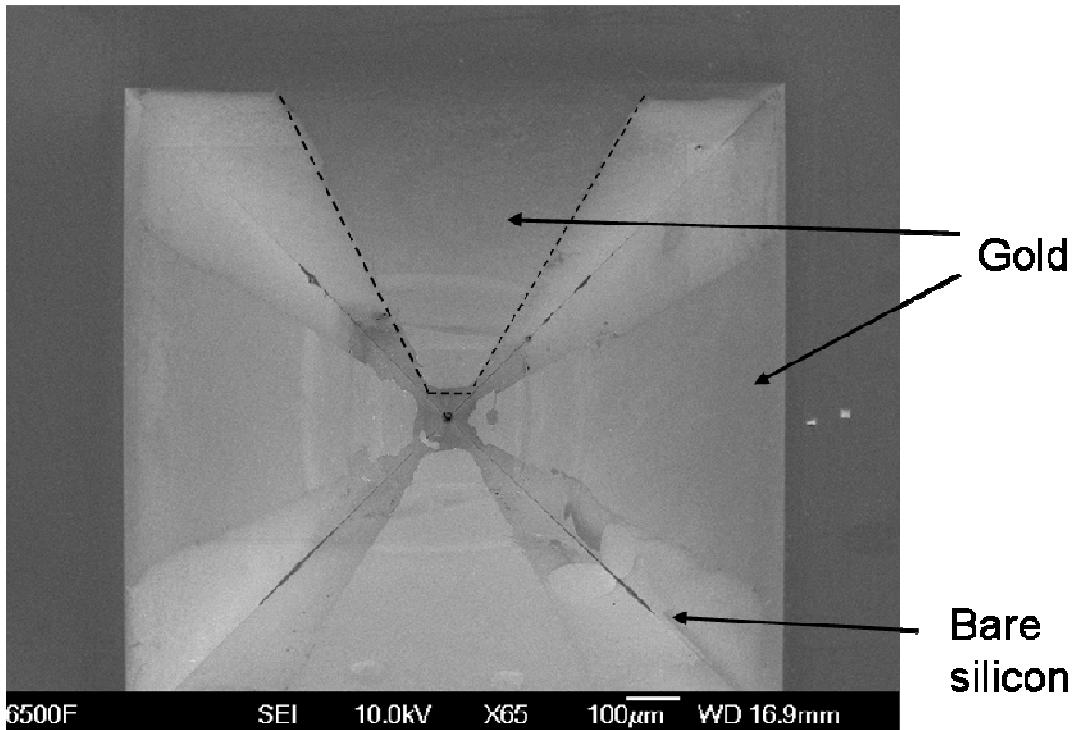

| <b>Figure 65:</b> SEM image of a 400 $\mu$ m wide pyramidal etch. ....                                                                                                                                                                                                                                                                                                                                                                                                                                         | 101 |

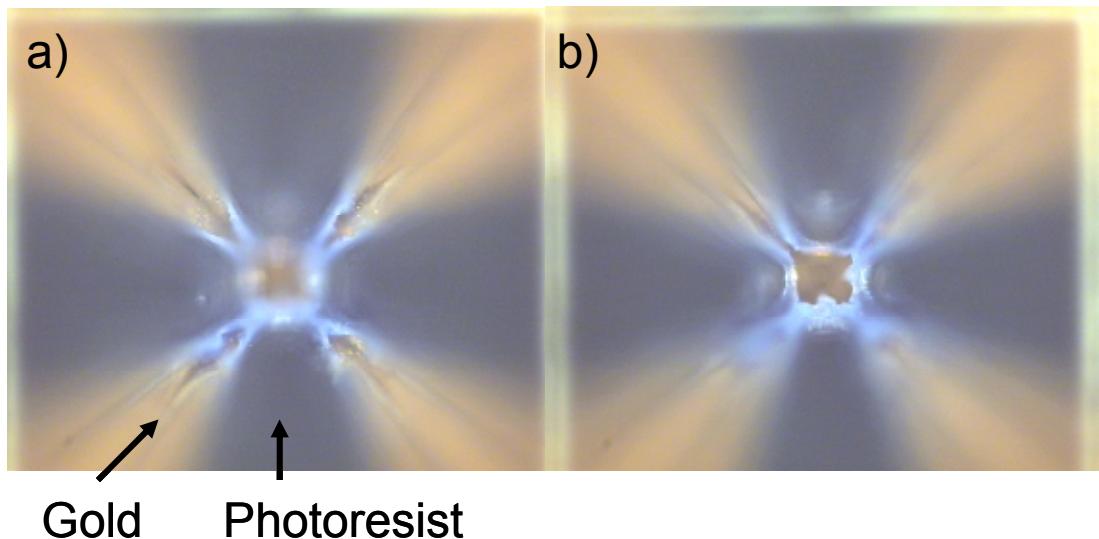

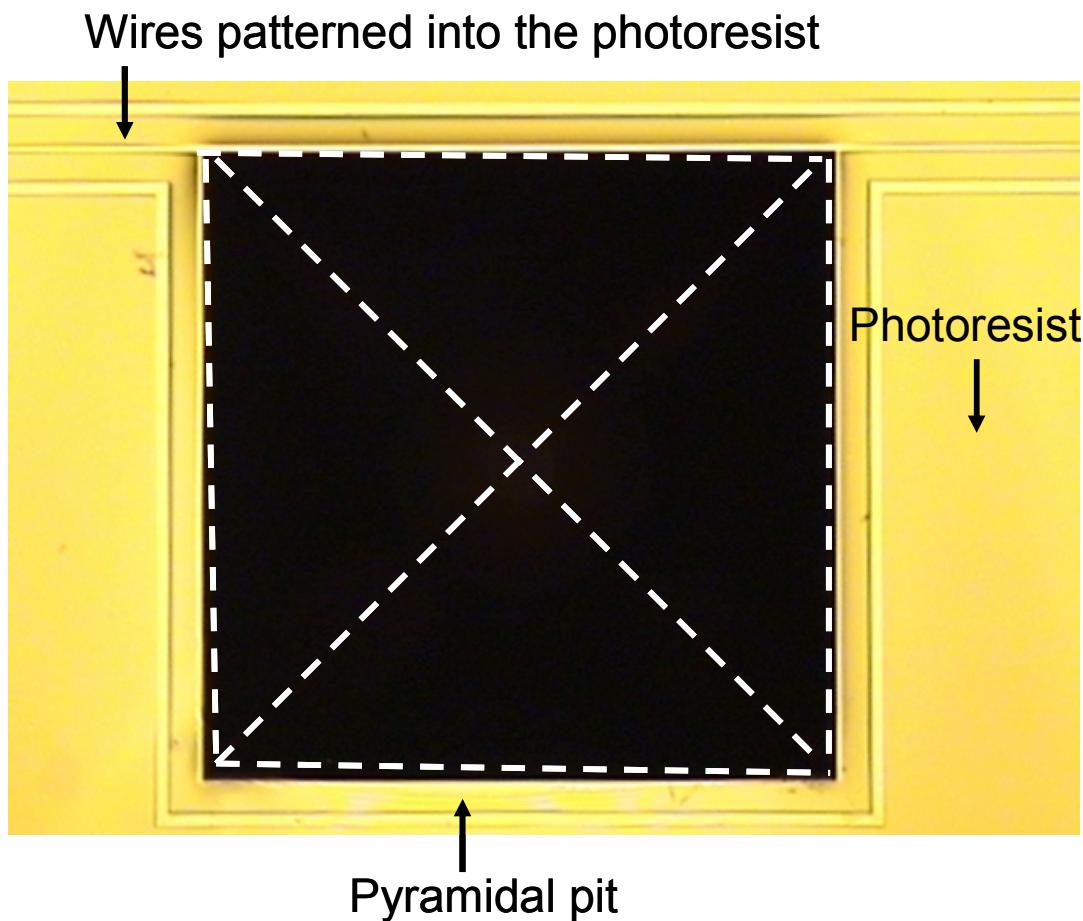

| <b>Figure 66:</b> Microscope images of the pyramidal micro-mirrors with patterned electrochemically deposited photoresist before gold etching the flower pattern. The images show the same image with an increasing focal depth. a) shows the focus at the middle depth of the pyramid while b) shows the focus at the apex of the pyramid..                                                                                                                                                                   | 103 |

| <b>Figure 67:</b> Patterned electrochemically deposited photoresist after standard development (left) and patterned electrochemically deposited photoresist after development and a hot water rinse (right) (Taken from ref [89]). ....                                                                                                                                                                                                                                                                        | 103 |

|                                                                                                                                                                                                                                                                                                                                                                                            |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| <b>Figure 68:</b> SEM image showing the flower pattern created on the side walls of all the pyramids. Due to difficulty in achieving a uniform exposure of the resist inside the pyramid, resist residue can be seen in the diagonals and at the apex of the pyramid as dark areas. The colour of the silicon surface also varies due to differential charging during the SEM session..... | 104 |

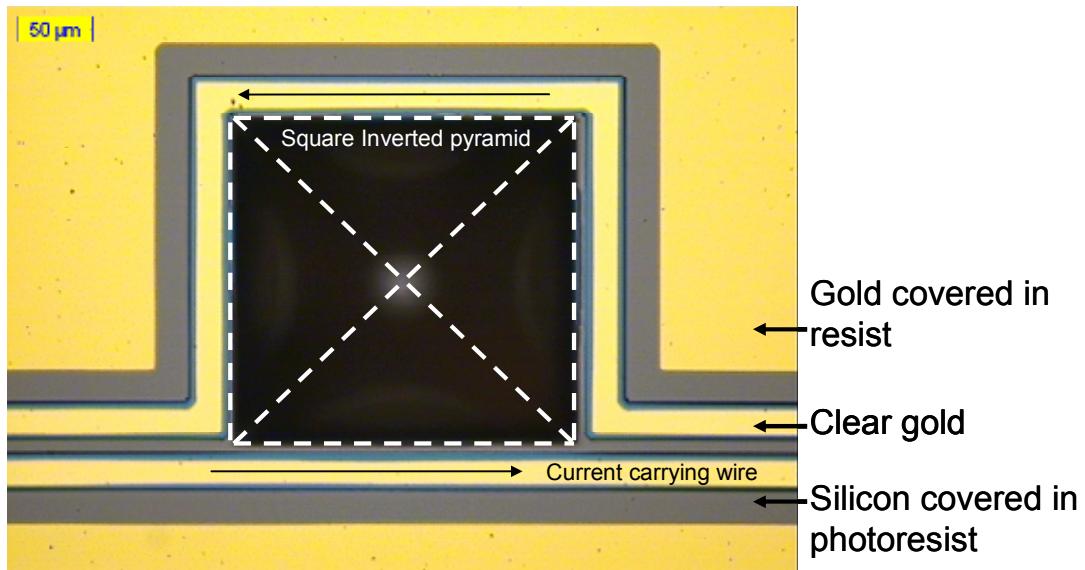

| <b>Figure 69:</b> Microscope image showing the resist mask around a pyramid that allows the gold to be wet etched to create isolated wires.....                                                                                                                                                                                                                                            | 105 |

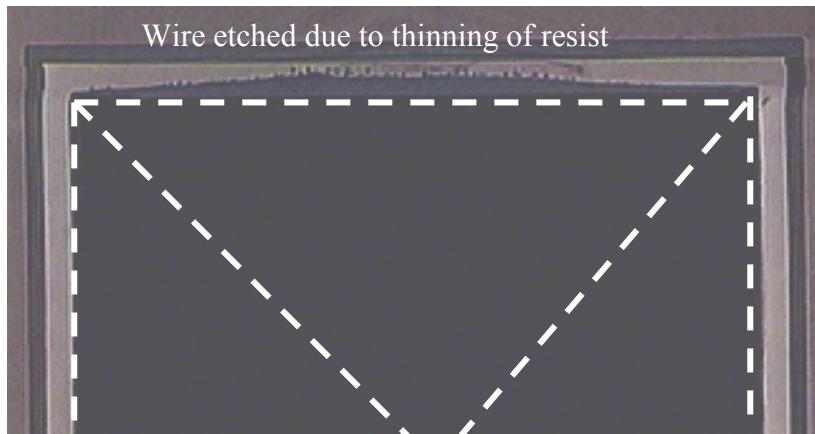

| <b>Figure 70:</b> Photograph showing the edge of the pyramid and its circulating wire. Due to poor resist coverage because of the problems of spinning over large topological structures the wire has become etched almost to destruction.....                                                                                                                                             | 106 |

| <b>Figure 71:</b> Microscope image of the tracks around the pyramid with the electroplating mould in place all around the wire edges.....                                                                                                                                                                                                                                                  | 107 |

| <b>Figure 72:</b> Photograph of the gold, flower design pyramid chip wire bonded into a ceramic pin grid array package. The inside of the pyramids clearly show the flower patterning. Nine bond wires are used on each chip pad to safely allow large currents to be applied. ....                                                                                                        | 108 |

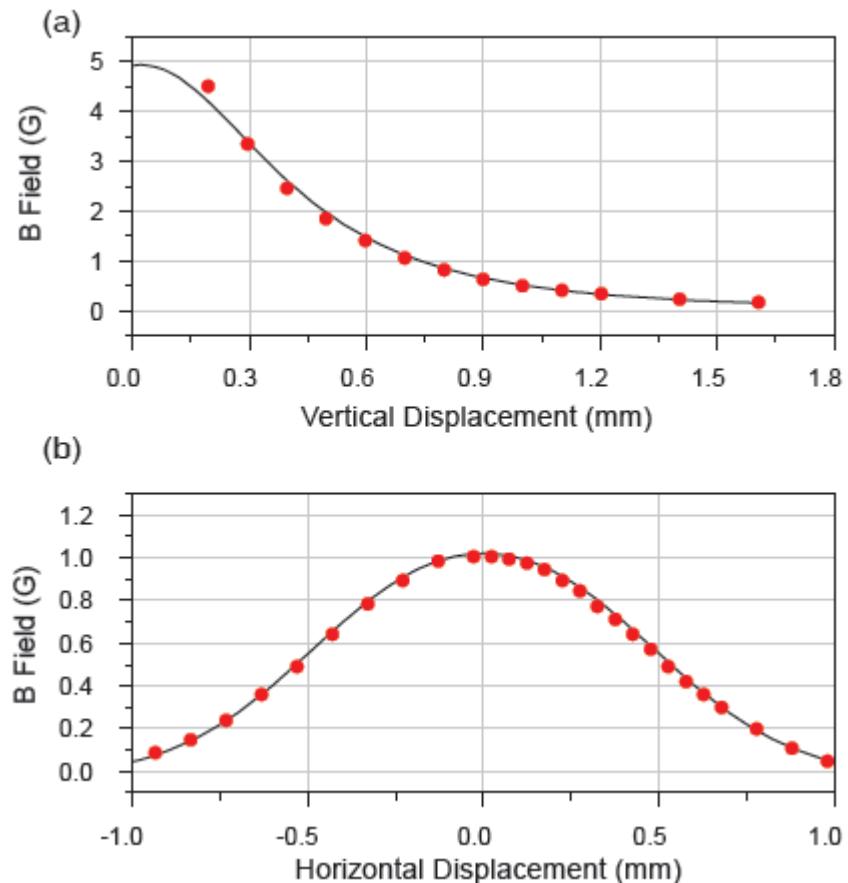

| <b>Figure 73:</b> Graph showing the vertical component of the magnetic field above an 800 $\mu\text{m}$ pyramid with 480mA in the wire. Showing the probe a) translated perpendicularly away from the chip surface along the pyramids central axis, b) translated parallel to the chip and the pyramid rows at a height of 0.7 mm, across the centre of the pyramid.....                   | 110 |

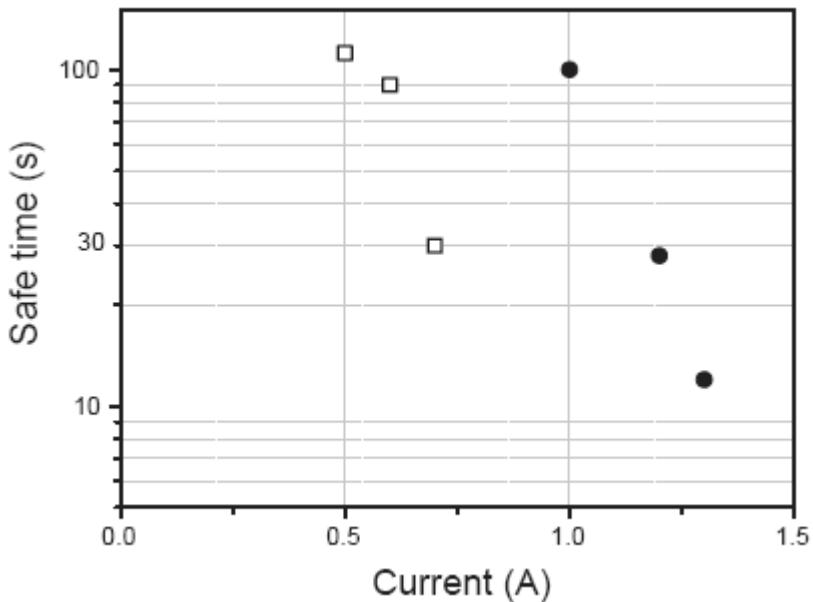

| <b>Figure 74:</b> Time taken for the chip wire temperature to reach 120 $^{\circ}\text{C}$ for various currents. Filled circles represent 50 $\mu\text{m}$ wire wires while open squares represent 25 $\mu\text{m}$ wide wires. ....                                                                                                                                                       | 112 |

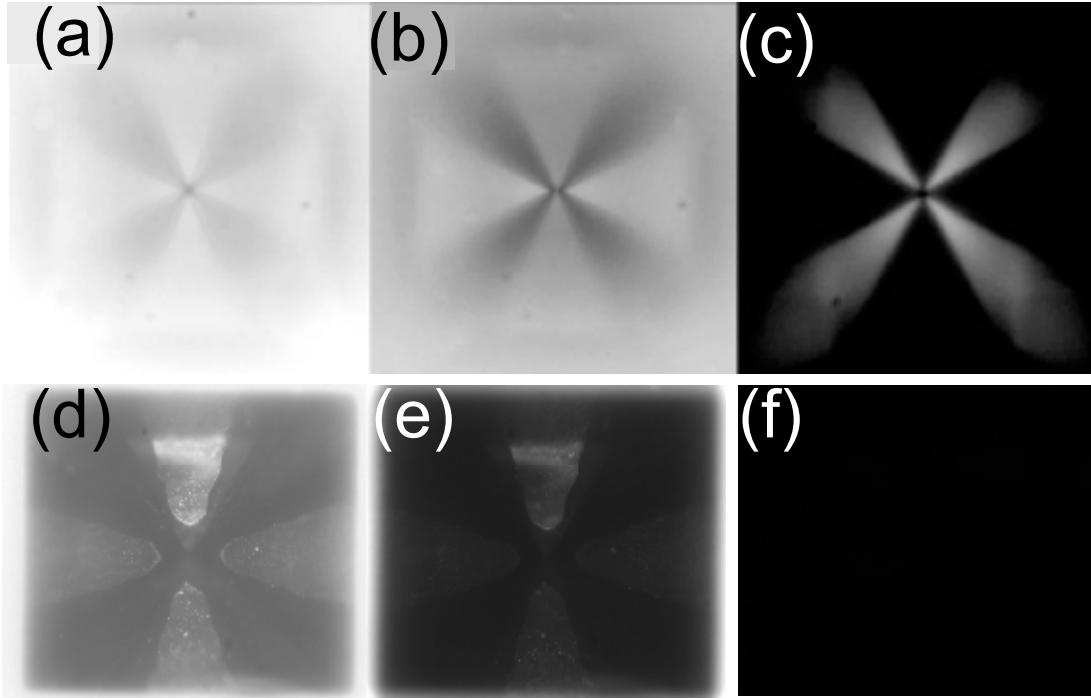

| <b>Figure 75:</b> Views of the pyramidal mirror under an optical microscope. The top row shows photographs of unpatterned pyramids, the bottom row shows patterned pyramids. Images (a, d) are without polarizers; (b, e) have parallel polarizer and analyzer and (c, f) have crossed polarizer and analyzer.....                                                                         | 113 |

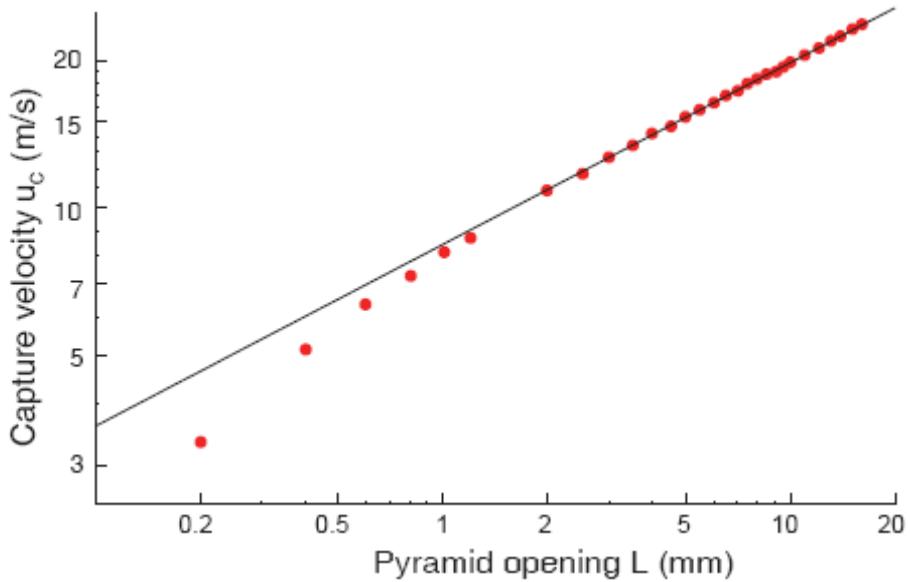

| <b>Figure 76:</b> Graph showing the capture velocity against the size of the pyramid opening. This is calculated by numerical integration using the model described in [126]. ....                                                                                                                                                                                                         | 115 |

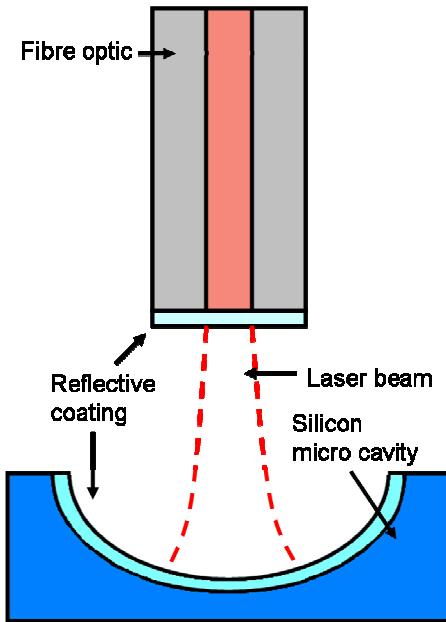

| <b>Figure 77:</b> Schematic diagram of the hemispherical optical cavity. ....                                                                                                                                                                                                                                                                                                              | 118 |

| <b>Figure 78:</b> The fabrication process for the silicon microcavities. ....                                                                                                                                                                                                                                                                                                              | 119 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

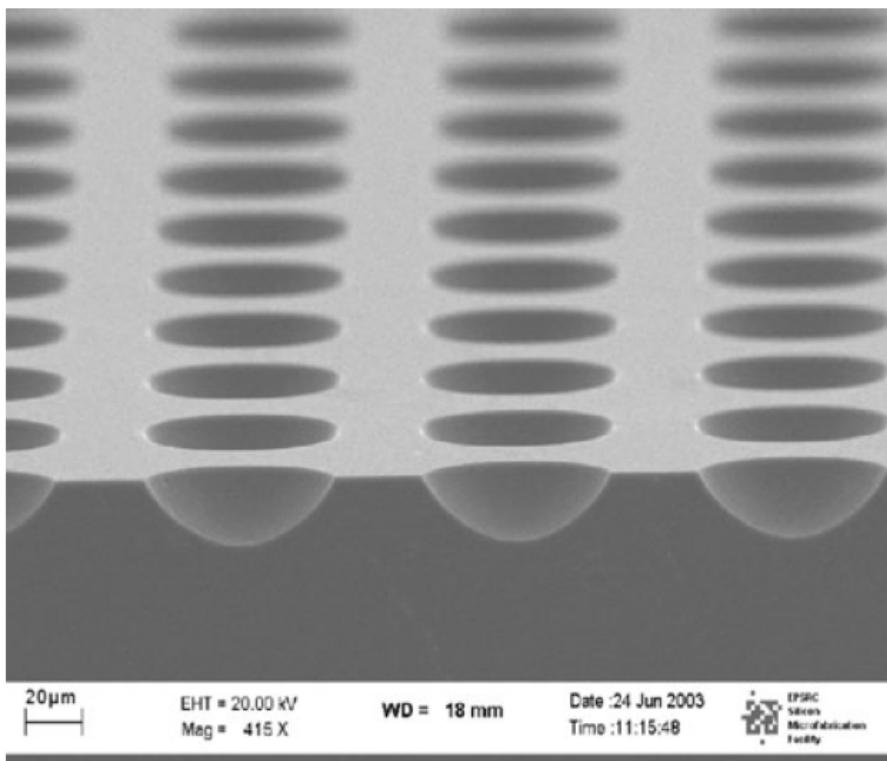

| <b>Figure 79:</b> SEM image showing a cross-sectional cut through micro-cavities 21 $\mu\text{m}$ deep. These are formed by etching through 15 $\mu\text{m}$ holes in a SiO <sub>2</sub> mask for 72 min using a 9:75:30 HNA solution. The mirrors are 67 $\mu\text{m}$ in diameter. ....                                                                                                                                                           | 120 |

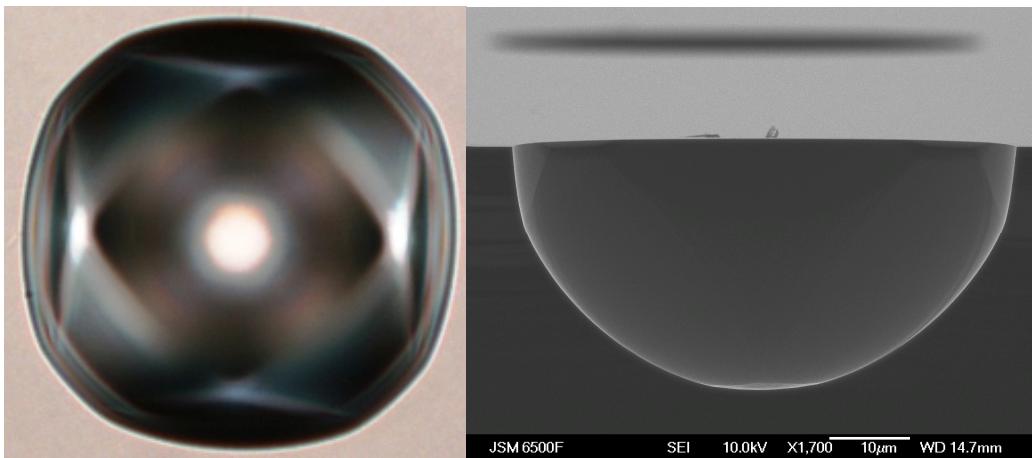

| <b>Figure 80:</b> Left, An optical microscope image of a 20 $\mu\text{m}$ initial opening hemisphere wet etched for 2 minutes in HNA. Right, An SEM image of the cross section of the cavity. Both images clearly show anisotropy.....                                                                                                                                                                                                              | 121 |

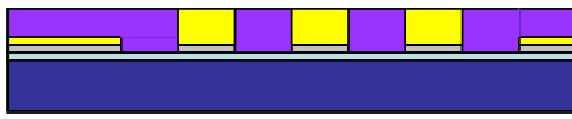

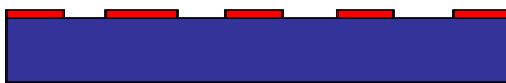

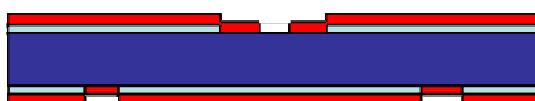

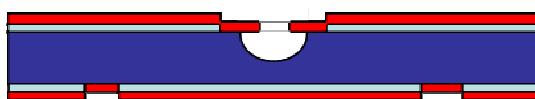

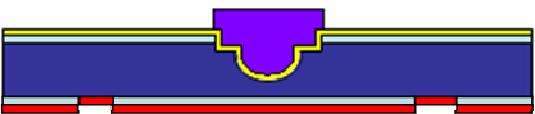

| <b>Figure 81:</b> Process flow for the creation of hemispherical micro-cavities.....                                                                                                                                                                                                                                                                                                                                                                | 124 |

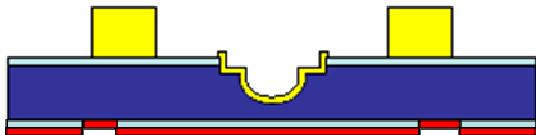

| <b>Figure 82:</b> SEM image of the final atom chip. The image shows a cross section of a micro-cavity with gold microwires forming an atom guide positioned on either side. ....                                                                                                                                                                                                                                                                    | 126 |

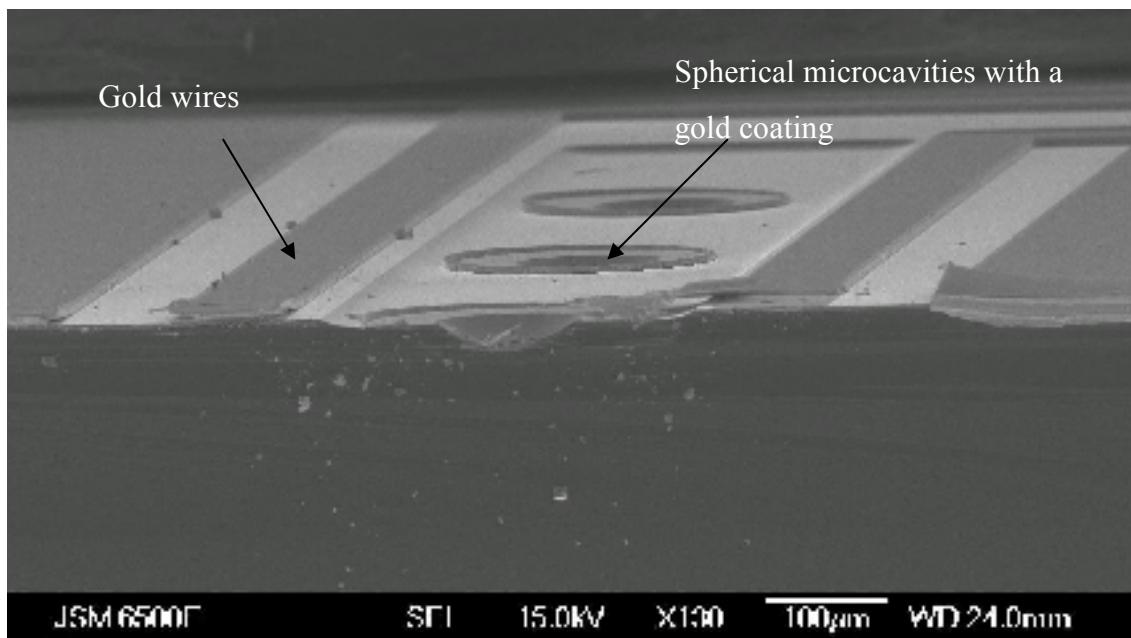

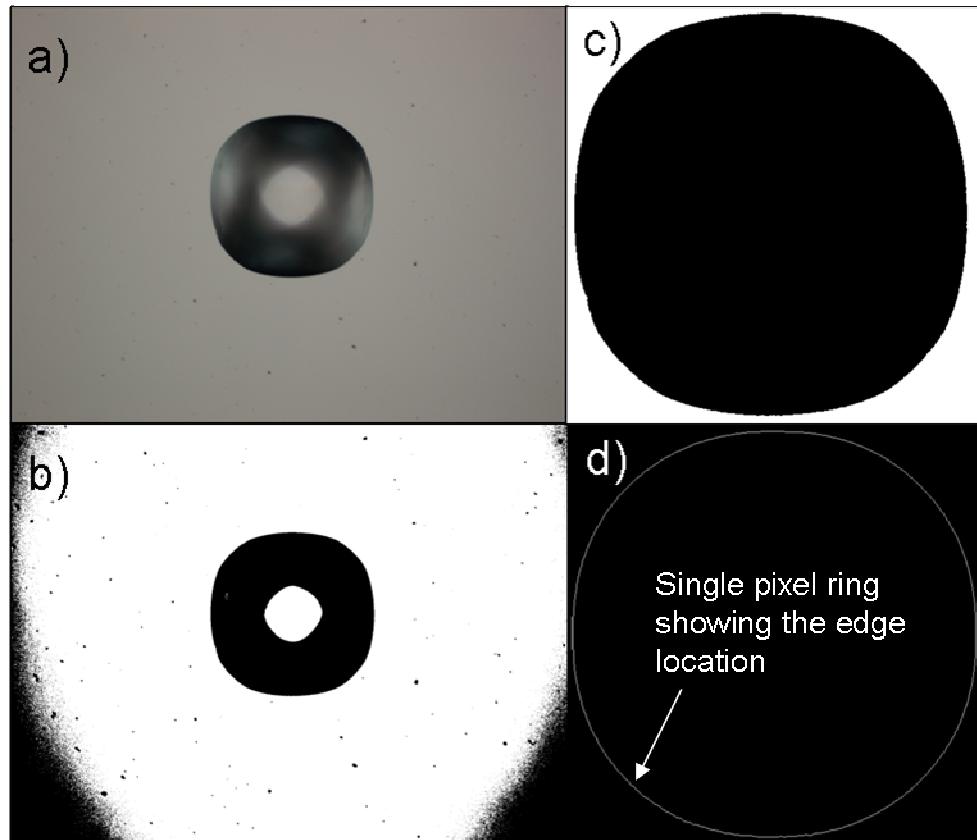

| <b>Figure 83:</b> Images showing the process steps used to calculate the radius of the spherical micro-cavities. a) shows the image of a micro-cavity taken via a microscope b) shows the image turned into a 2 tone black and white image c) shows the image after it had been cropped and the central light spot removed d) shows the image after being processed through a Matlab edge finding algorithm. ....                                   | 128 |

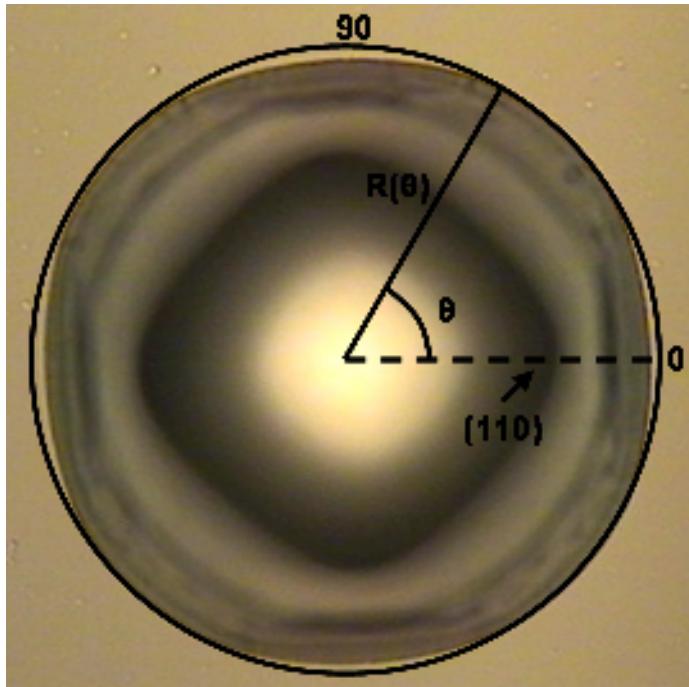

| <b>Figure 84:</b> Representation of how the data was recorded showing the zero point and direction theta was measured. ....                                                                                                                                                                                                                                                                                                                         | 129 |

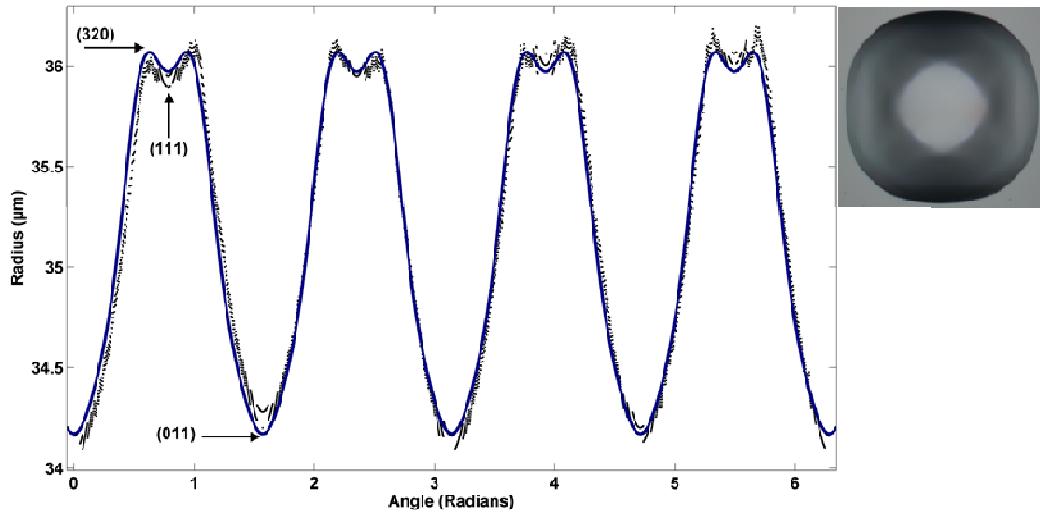

| <b>Figure 85:</b> Graph of the 20 $\mu\text{m}$ initial opening hemisphere showing the anisotropy of the 2D circular opening, after a two minute wet HNA etch, as a function of the angle. The data has been fitted to equation 37. The raw data is shown as black circles while the fitting is shown as a solid blue line. The crystal planes for the points of significance are also shown. The optical image is also shown in the top right..... | 130 |

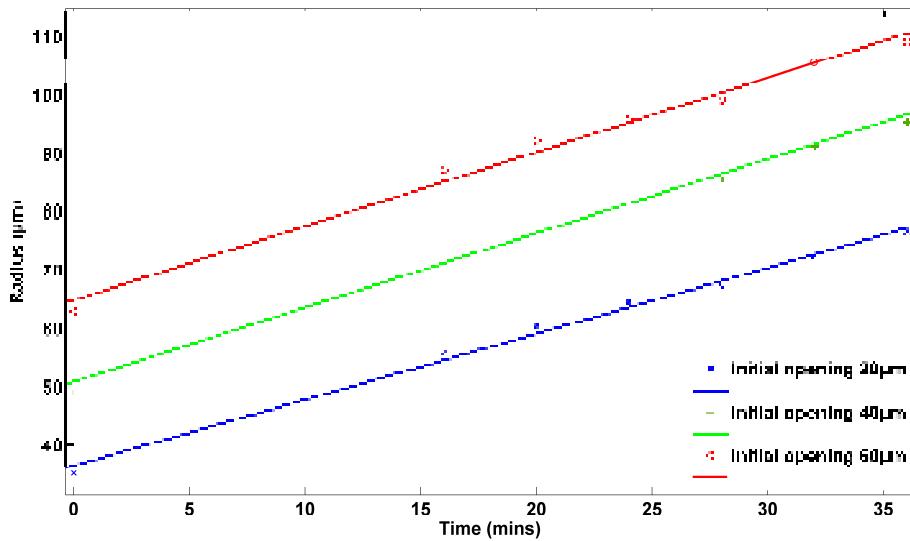

| <b>Figure 86:</b> Graph of the 20 $\mu\text{m}$ (Blue) 40 $\mu\text{m}$ (Green) and 60 $\mu\text{m}$ (Red) initial opening hemispheres showing the mean radius of the 2D circular opening of the etch as a function of ICP etching time. ....                                                                                                                                                                                                       | 131 |

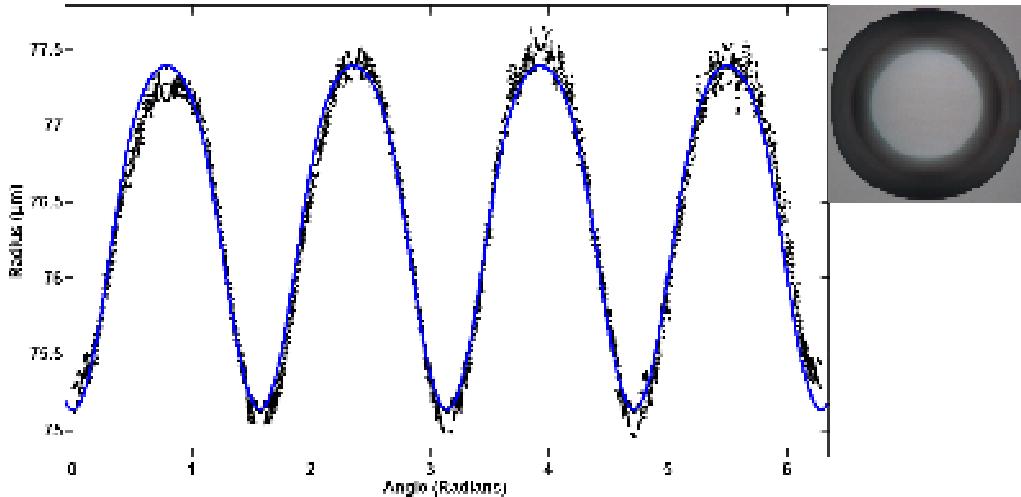

| <b>Figure 87:</b> Graph showing the 20 $\mu\text{m}$ initial opening hemisphere showing the anisotropy in the 2D circular opening created after a 36 minute ICP etch on the wet etched cavities. The data has been fitted to equation 37. The raw data is shown as black circles while the fitting is shown as a solid blue line An optical image is also shown at top right. ....                                                                  | 131 |

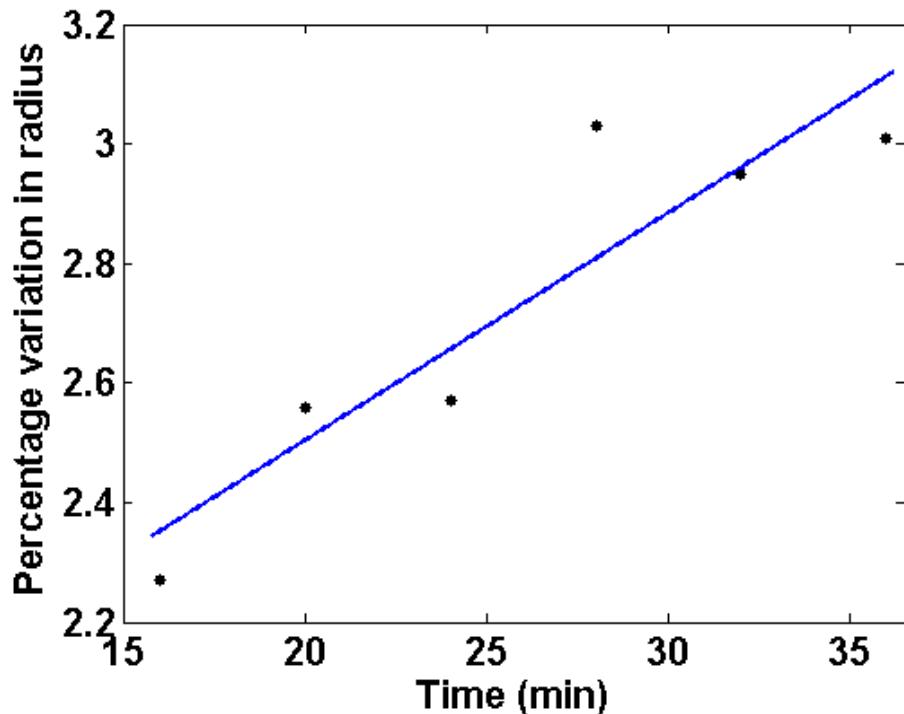

| <b>Figure 88:</b> Graph showing the percentage variation from a perfect circle as a function of ICP etching time. ....                                                                                                                                                                                                                                                                                                                              | 132 |

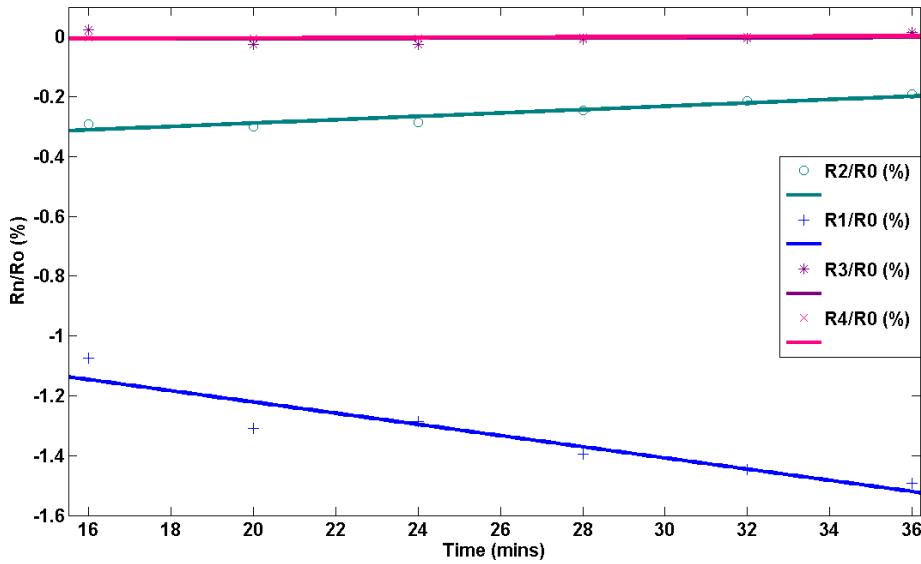

| <b>Figure 89:</b> Variation of the anisotropy harmonics with the ICP etching time for initial opening 20 $\mu\text{m}$ .....                                                                                                                                                                                                                                                                                                                        | 133 |

|                                                                                                                                                                                                                                                                |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

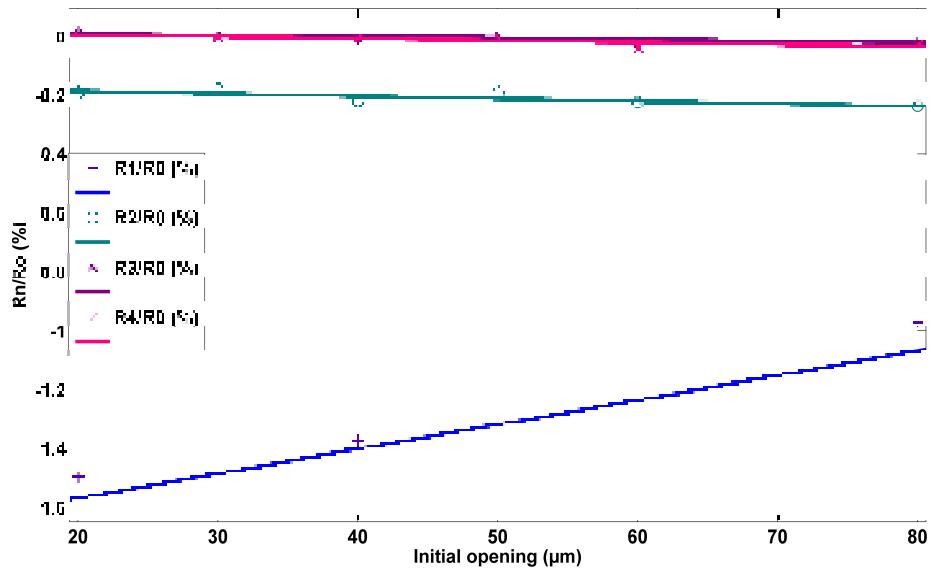

| <b>Figure 90:</b> Variation of the anisotropy harmonics with the initial opening size for wafers ICP etched for 36 minutes .....                                                                                                                               | 134 |

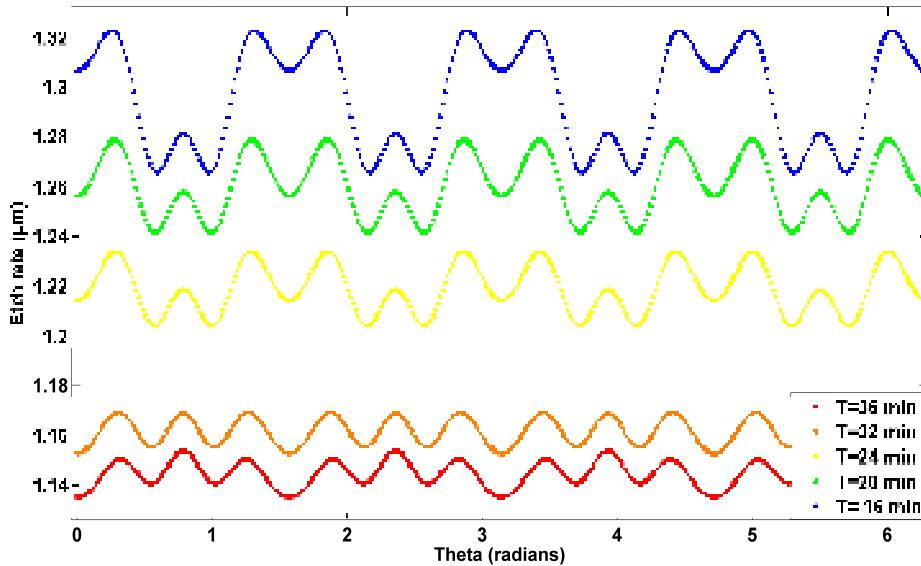

| <b>Figure 91:</b> Graph showing the etch rate as a function of theta for the 20 $\mu\text{m}$ initial opening cavities as it evolves over time.....                                                                                                            | 135 |

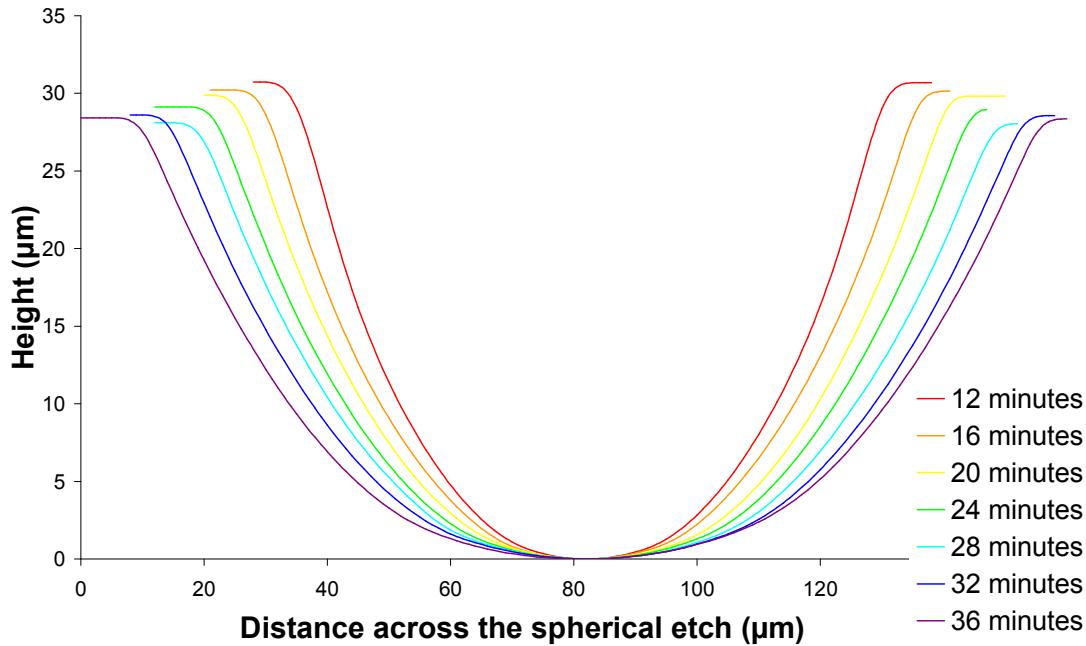

| <b>Figure 92:</b> Graph showing a 2D slice into the plane of the wafer through the center of the hemispherical cavities .....                                                                                                                                  | 136 |

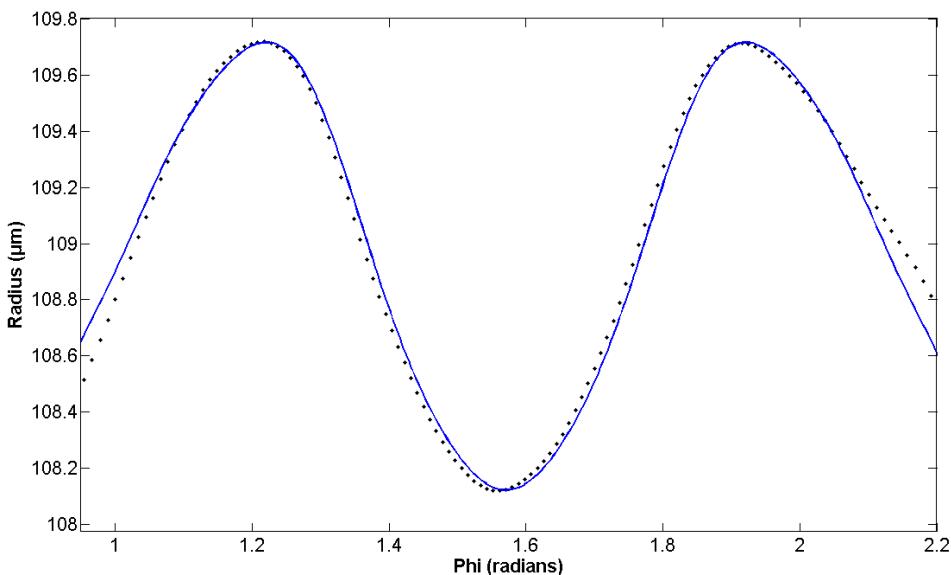

| Figure 93: Graph showing a 2D slice through the centre of a hemispherical cavity along $\theta=0^\circ$ (initial opening 20 $\mu\text{m}$ and ICP etching time 36 minutes). The data has been fitted to equation 37.....                                       | 137 |

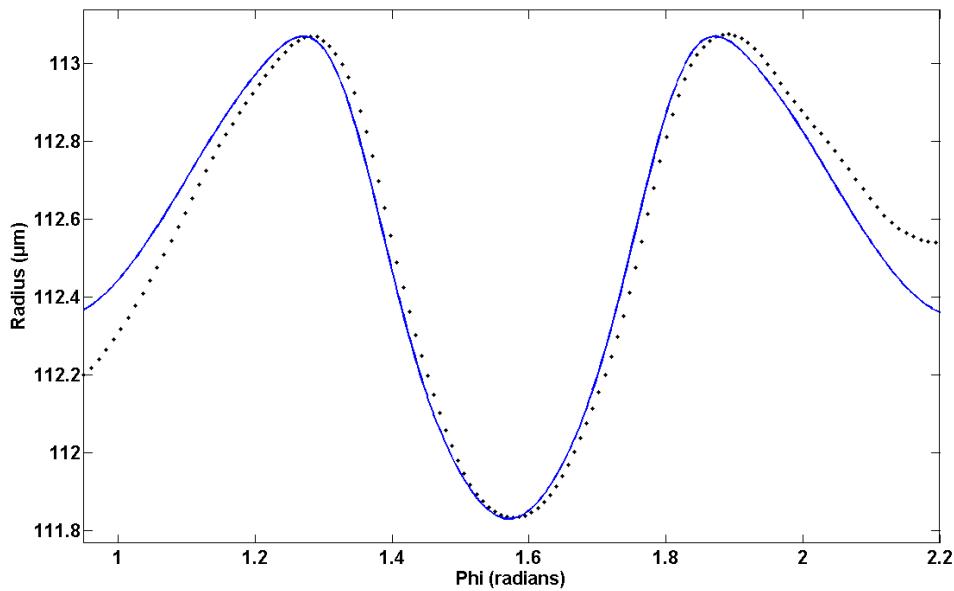

| Figure 94: Graph showing a 2D slice through the centre of a hemispherical cavity along $\theta=45^\circ$ (initial opening 20 $\mu\text{m}$ and ICP etching time 36 minutes). The data has been fitted to equation 37.....                                      | 138 |

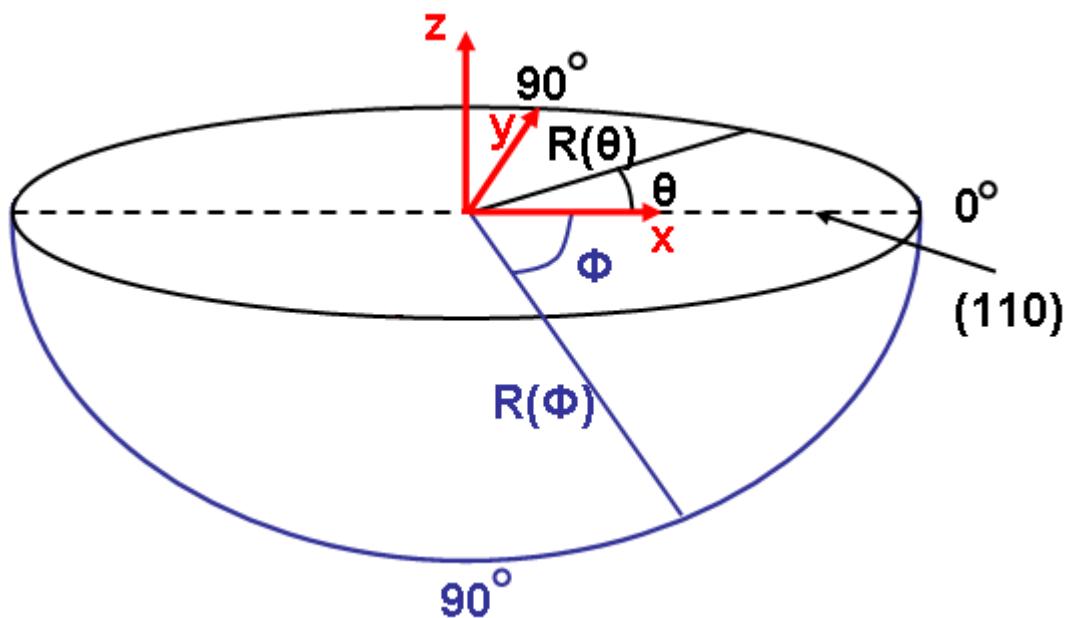

| <b>Figure 95:</b> Representation of how the data was recorded and labelled. The zero angle was common to both theta and phi with theta varying from 0-360 degrees while phi varies between 0-180 degrees. The centre of the bowl was chosen as the origin..... | 139 |

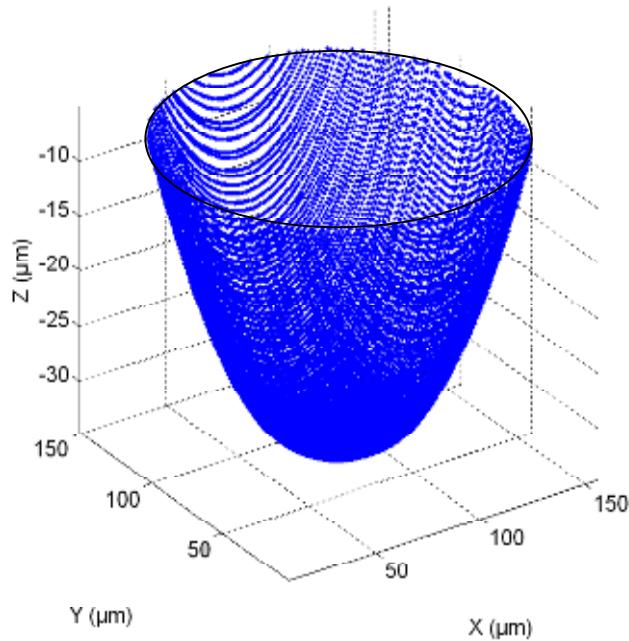

| <b>Figure 96:</b> 3D plot of the stylus profiler data for a hemisphere produced from an initial opening of 20 $\mu\text{m}$ and an ICP etching time of 36 minutes .....                                                                                        | 140 |

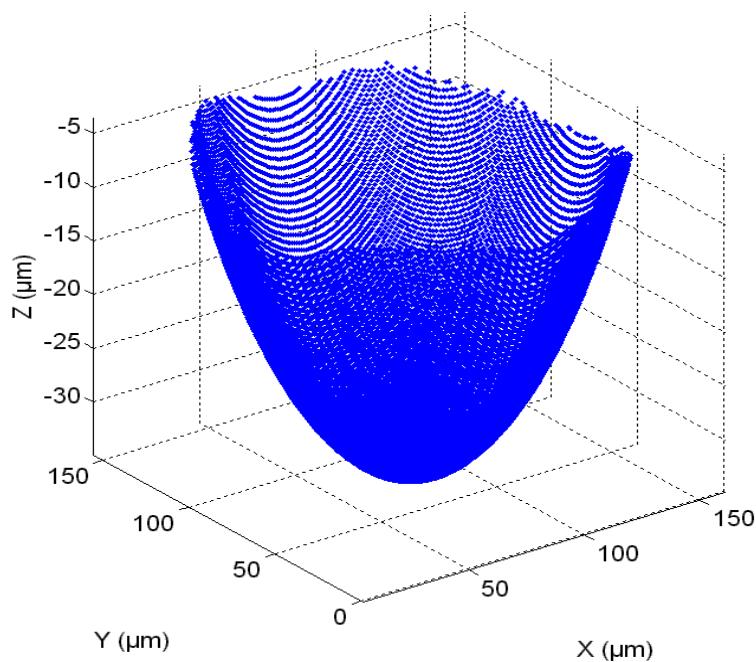

| Figure 97: 3D plot of best fit hemisphere to the micro-cavity.....                                                                                                                                                                                             | 141 |

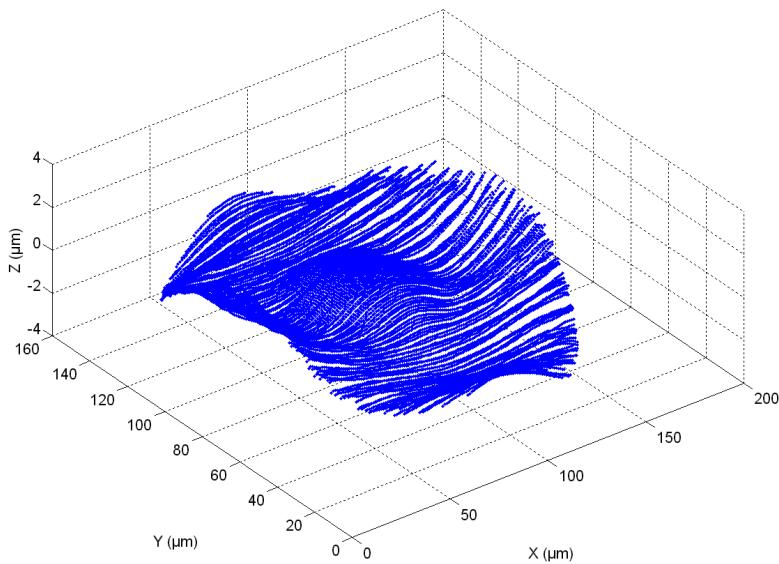

| <b>Figure 98:</b> 3D plot of the difference between the real data and the best fit hemisphere.....                                                                                                                                                             | 141 |

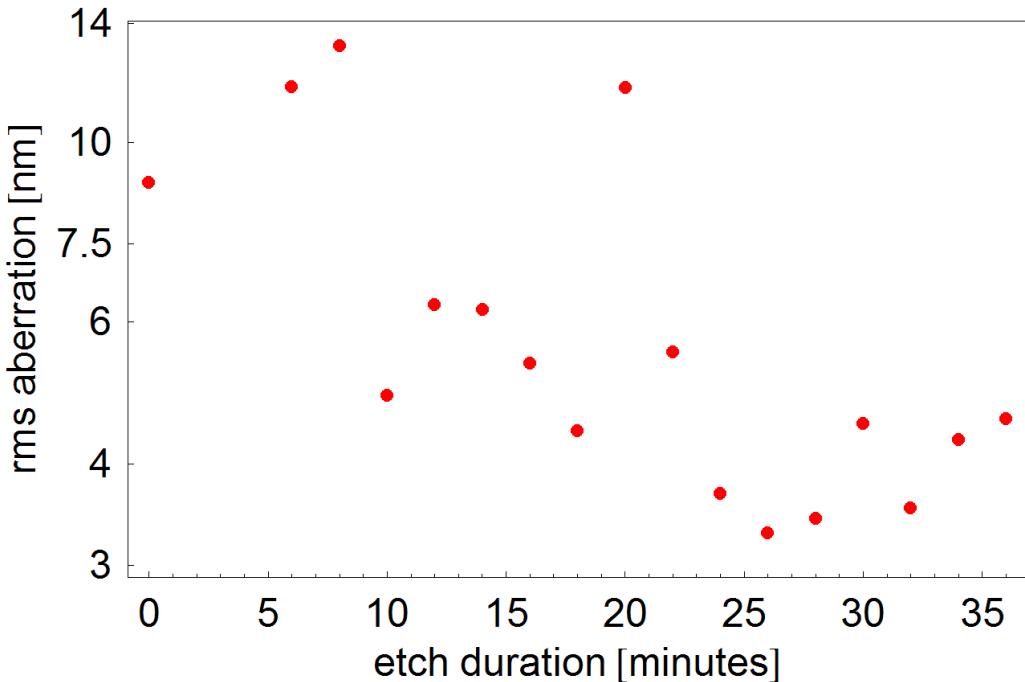

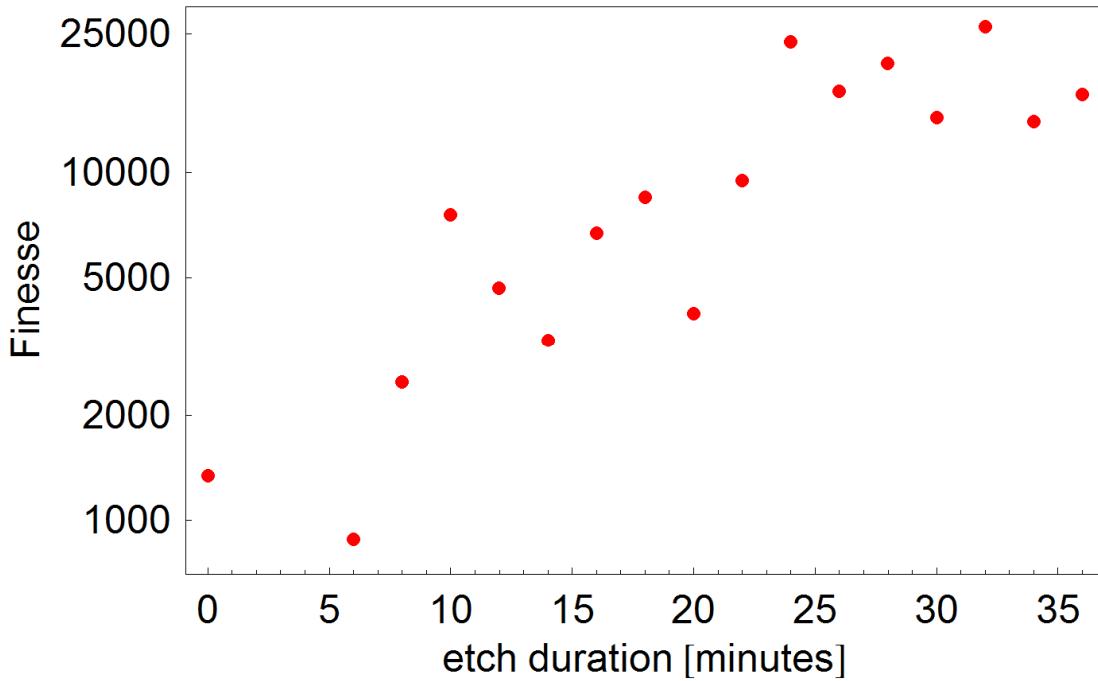

| <b>Figure 99:</b> aberration of the surface from a perfect sphere, versus etch duration... ..                                                                                                                                                                  | 143 |

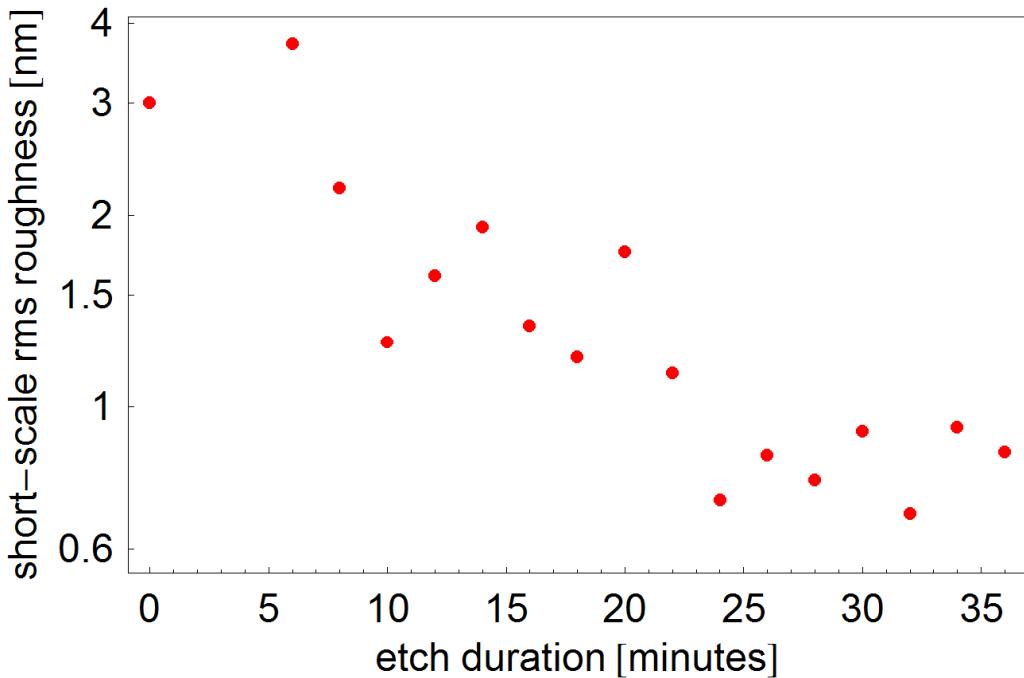

| <b>Figure 100:</b> Short-scale (1.2 $\mu\text{m}$ ) rms roughness of the surface from a perfect sphere, versus etch duration.....                                                                                                                              | 144 |

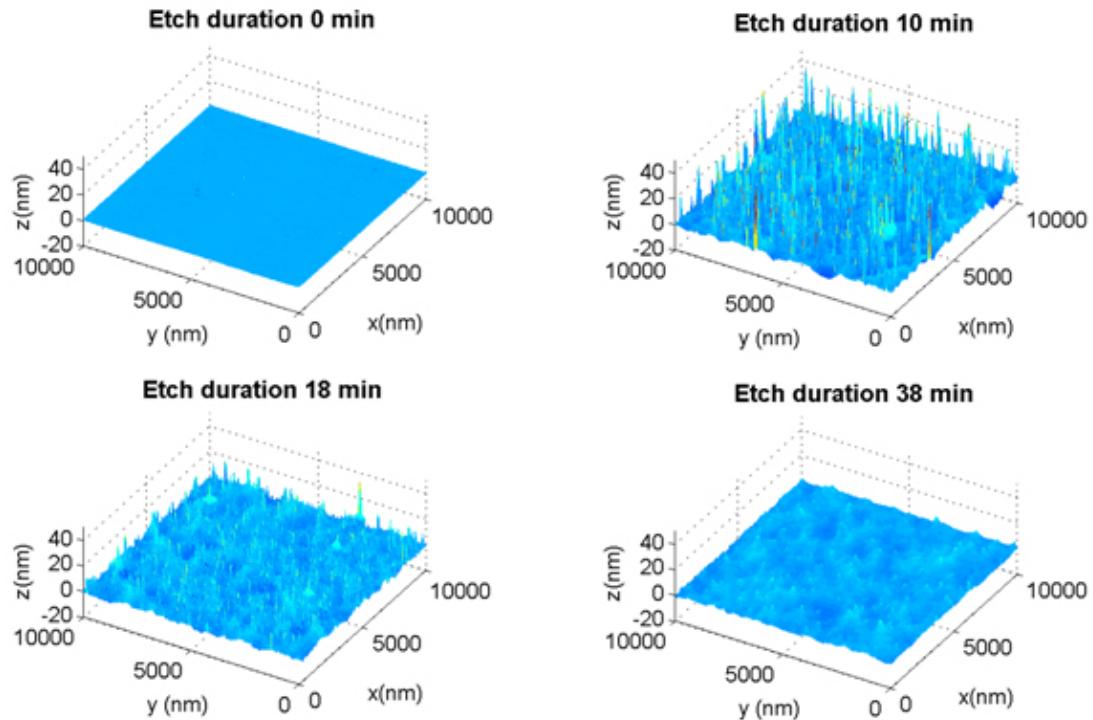

| <b>Figure 101:</b> AFM scans depicting the evolution of the flat portion of the wafer as a function of ICP etch time.....                                                                                                                                      | 145 |

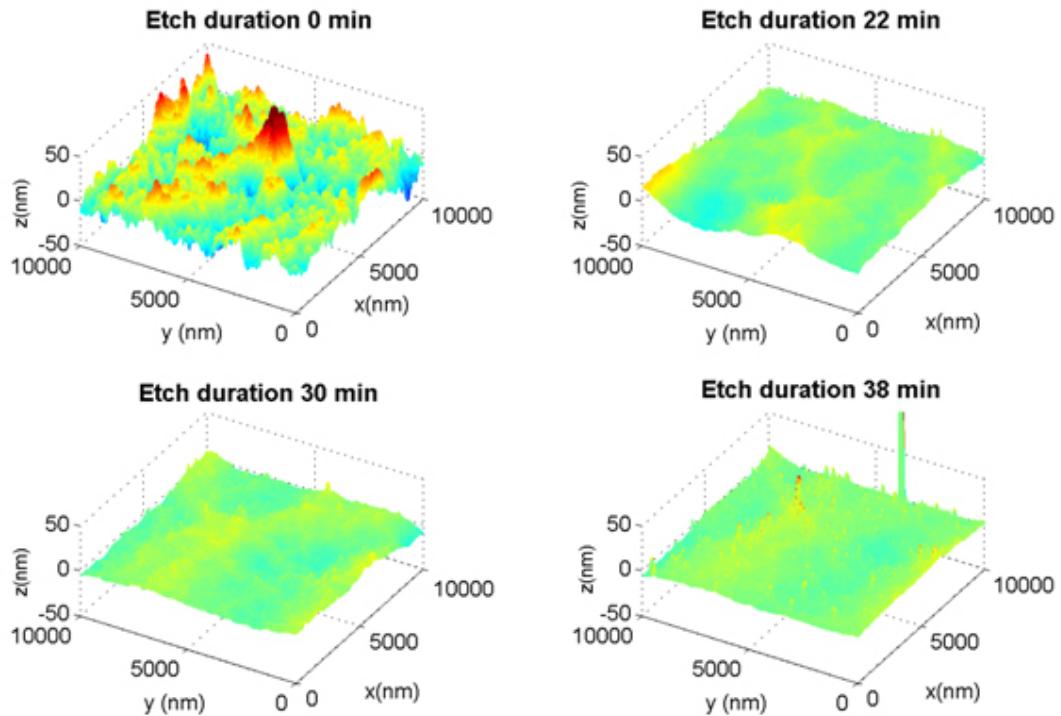

| <b>Figure 102:</b> AFM scans depicting the evolution of the concave micro cavity surface as a function of ICP etch time.....                                                                                                                                   | 146 |

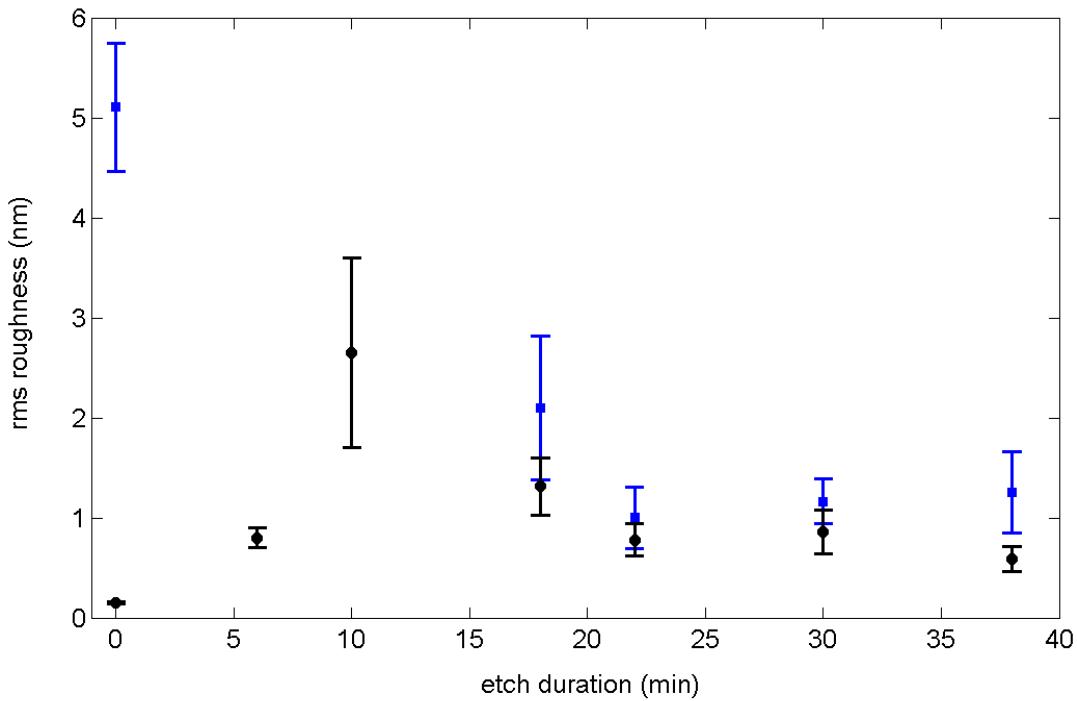

| <b>Figure 103:</b> Graph showing the evolution of the RMS roughness of the concave micro-cavity surface (blue) and flat wafer surface (black) with respect to ICP etching time.....                                                                            | 147 |

| <b>Figure 104:</b> Maximum possible finesse, inferred from the short-scale roughness measurement assuming a perfectly reflecting mirror.....                                                                                                                   | 148 |

|                                                                                                                                                                                                                                                                                                                                                                                            |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

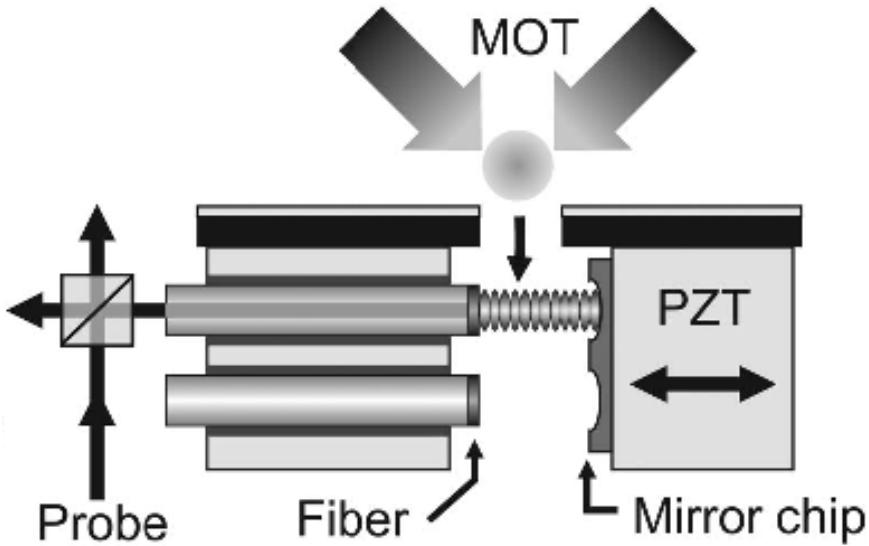

| <b>Figure 105:</b> Picture showing the setup used to create an optical resonator from the silicon micro cavities.....                                                                                                                                                                                                                                                                      | 149 |

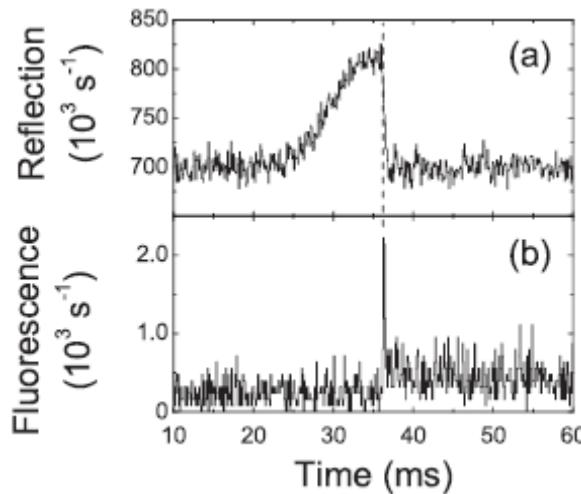

| <b>Figure 106:</b> Graph showing the ability to produce photons on demand using the micro-cavity. a) shows the reflectance signal as a cloud of atoms is dropped into the cavity, b) shows the fluorescence recorded from the cavity .....                                                                                                                                                 | 150 |

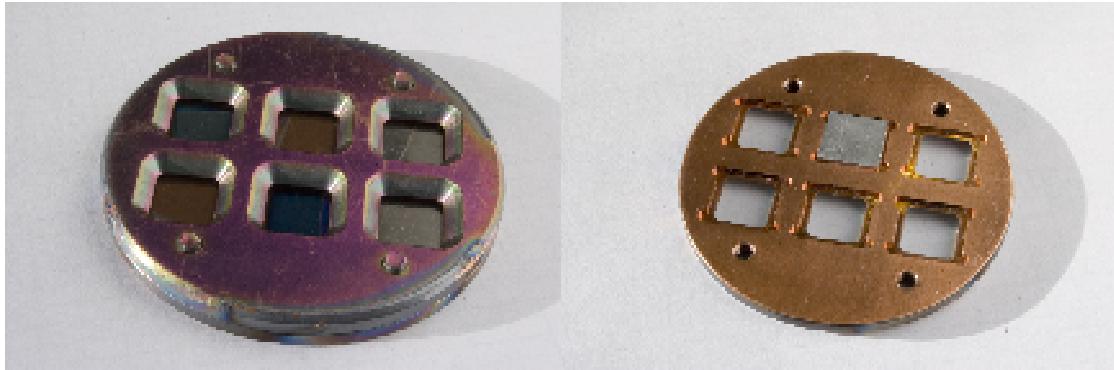

| <b>Figure 107:</b> Photograph of the sample holder used to sputter up to six samples. Left: Front view of the complete holder. Right: Back view of the front plate, the six slots used to hold the samples in place can clearly be seen. The top middle slot is shown holding a typical sample.....                                                                                        | 154 |

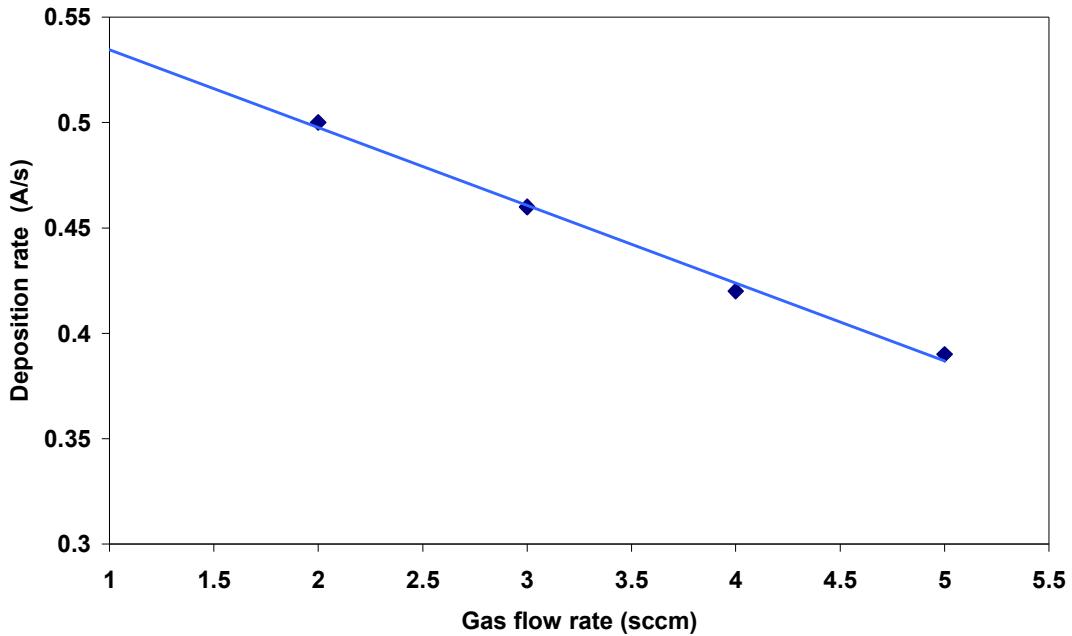

| <b>Figure 108:</b> Graph showing the effect of gas flow rate on the deposition rate of silicon.....                                                                                                                                                                                                                                                                                        | 155 |

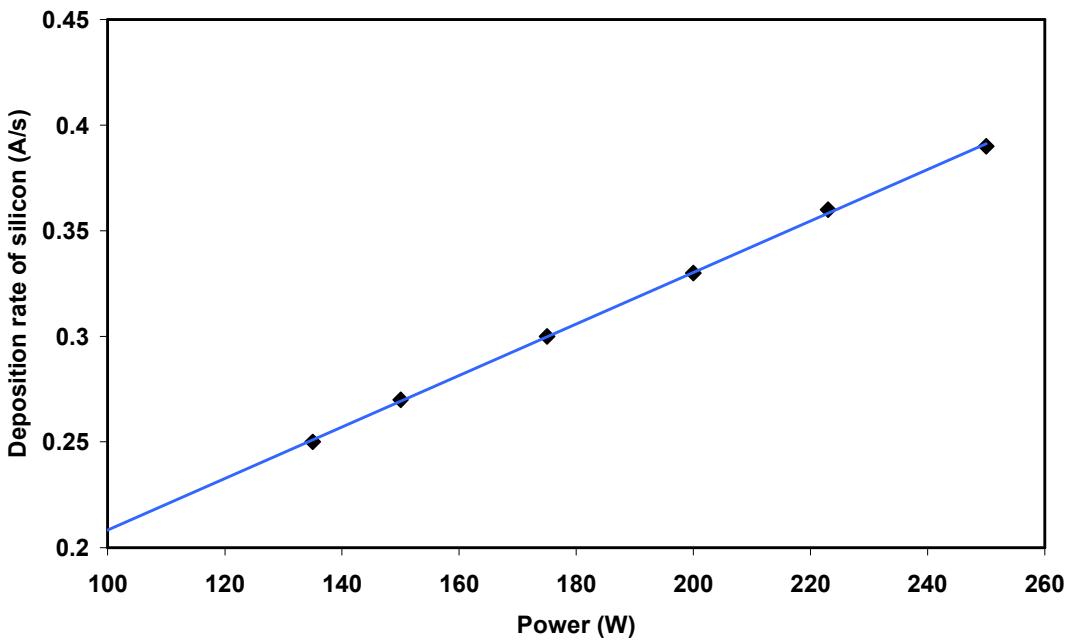

| <b>Figure 109:</b> Graph showing the effect of the power on the deposition rate of silicon. ....                                                                                                                                                                                                                                                                                           | 155 |

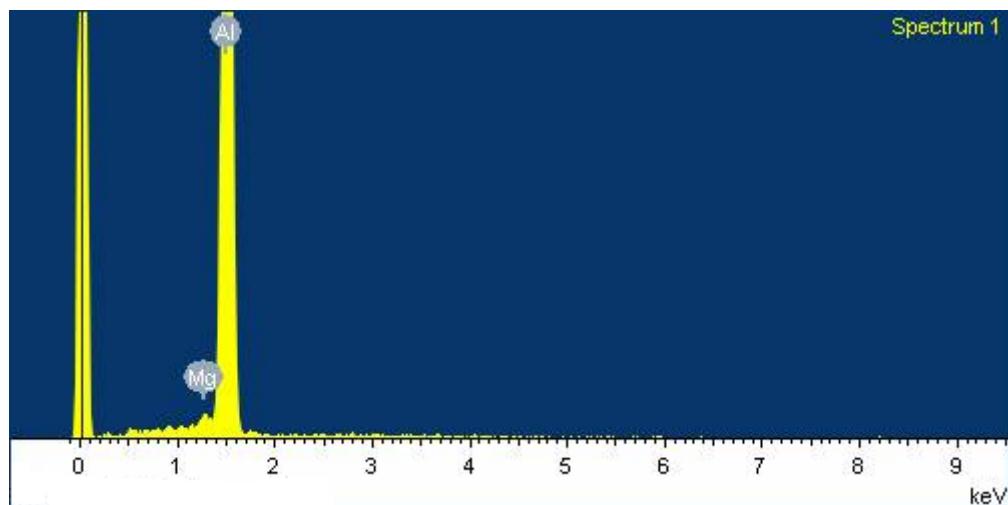

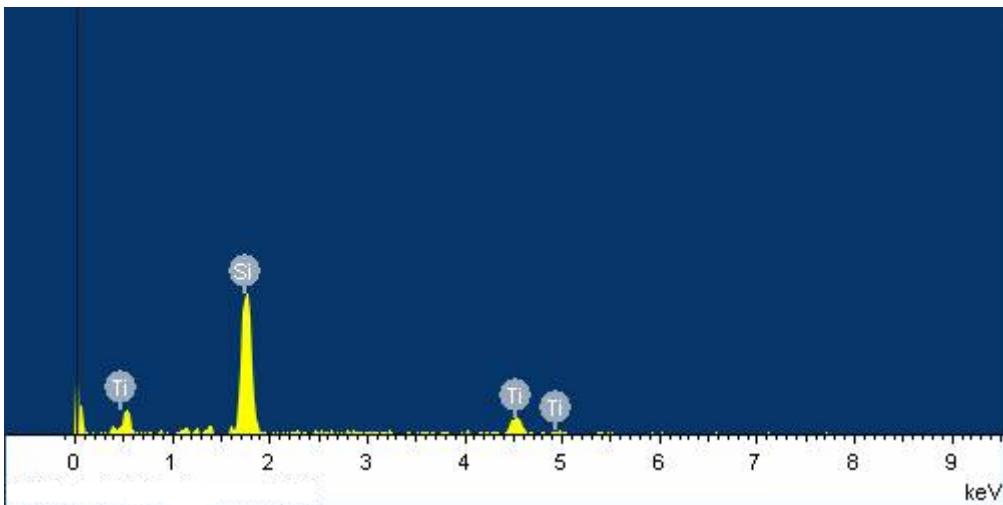

| <b>Figure 110:</b> EDX spectrum of the aluminium substrate. ....                                                                                                                                                                                                                                                                                                                           | 157 |

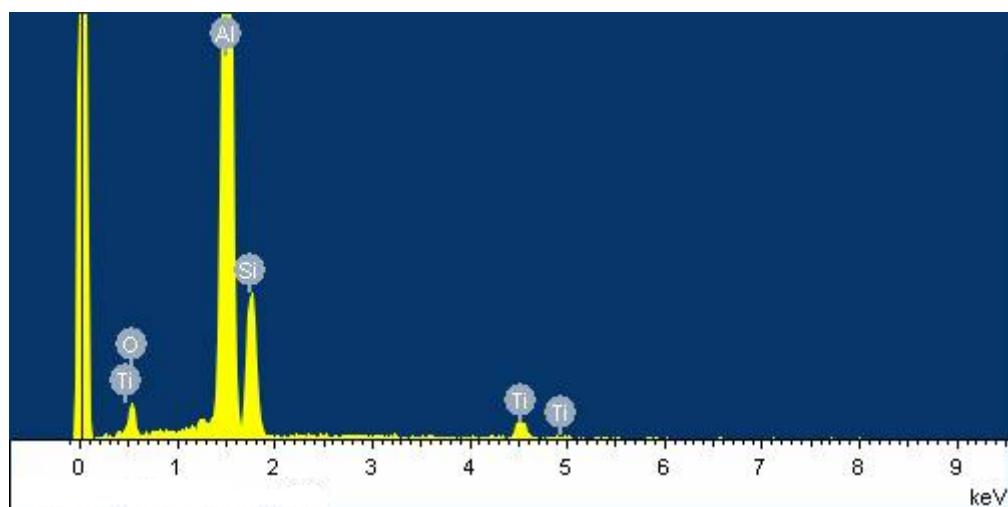

| <b>Figure 111:</b> Typical EDX spectra obtained from the silicon titanium samples. ....                                                                                                                                                                                                                                                                                                    | 157 |

| <b>Figure 112:</b> Typical EDX spectra obtained from the silicon titanium samples after the substrate has been subtracted from the results. ....                                                                                                                                                                                                                                           | 158 |

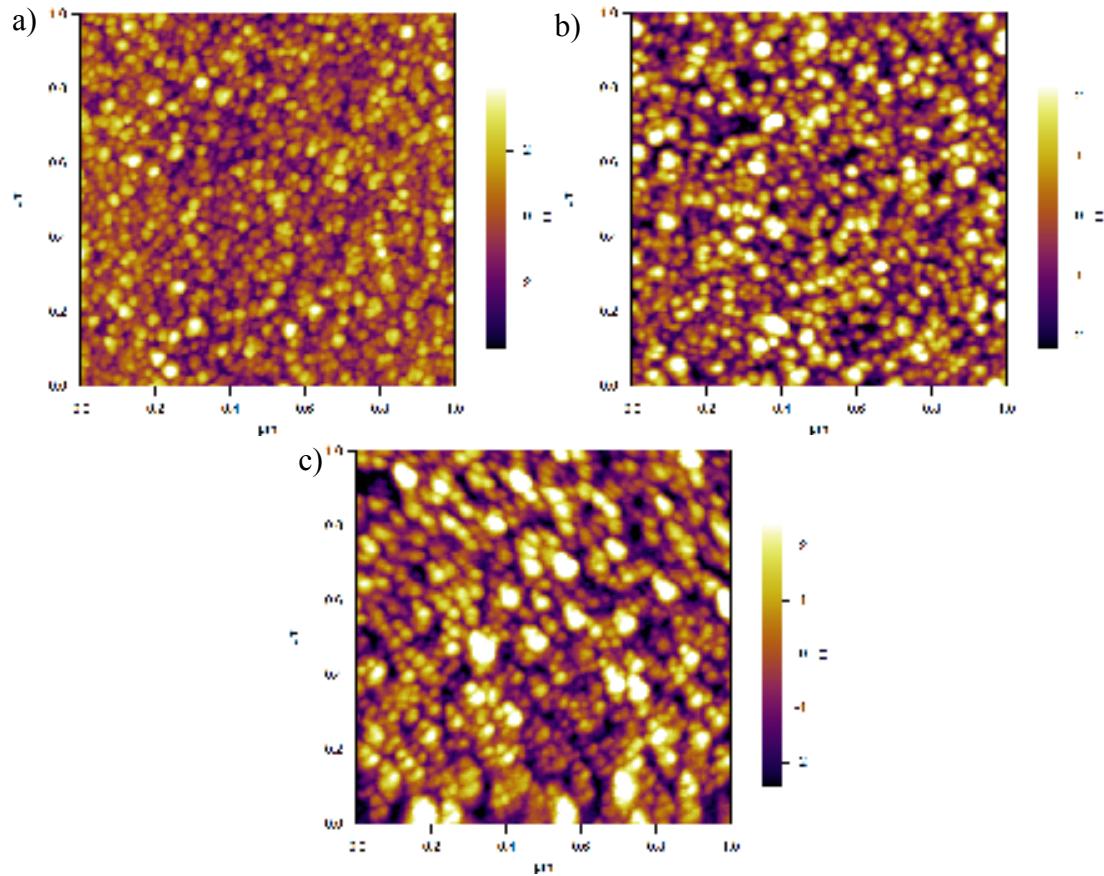

| <b>Figure 113:</b> A 1 $\mu\text{m}$ by 1 $\mu\text{m}$ Atomic Force Microscope image of co-sputtered silicon-titanium thin film a) un-annealed b) annealed at 300°C and c) annealed at 500 °C.....                                                                                                                                                                                        | 159 |

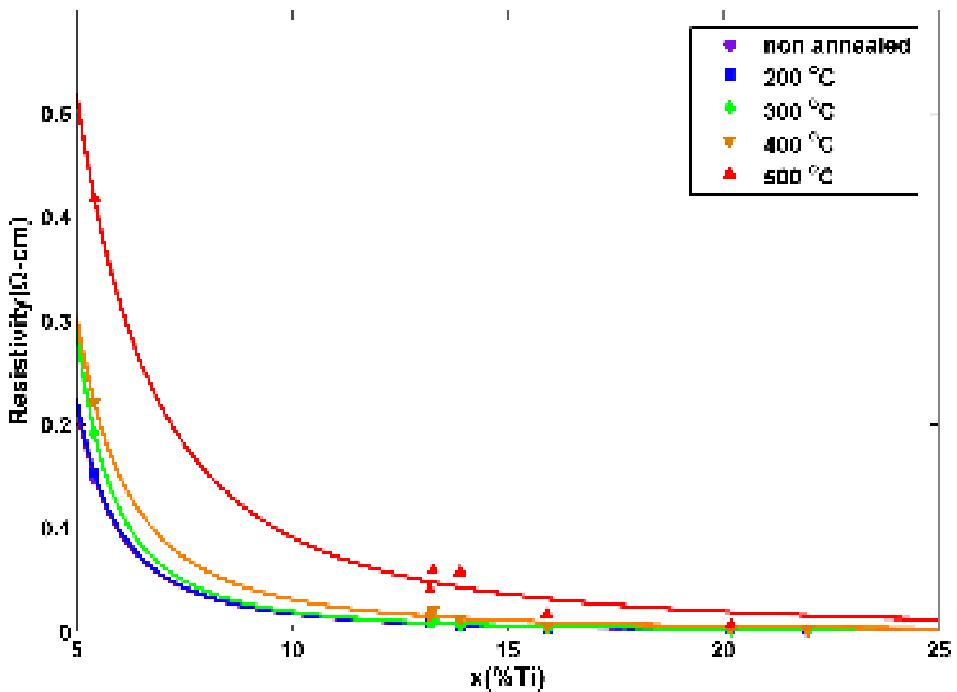

| <b>Figure 114:</b> Plots of the resistivity as a function of the titanium content in % weight at 5 different annealing temperatures: non annealed (purple circles), 200°C (blue squares) 300°C (green diamonds) 400°C (orange triangles) and 500°C (red triangles). The solid lines are the nonlinear regression fits of the formula $\rho = a(T)(x - x_c(T))^{-\alpha}$ to the data. .... | 160 |

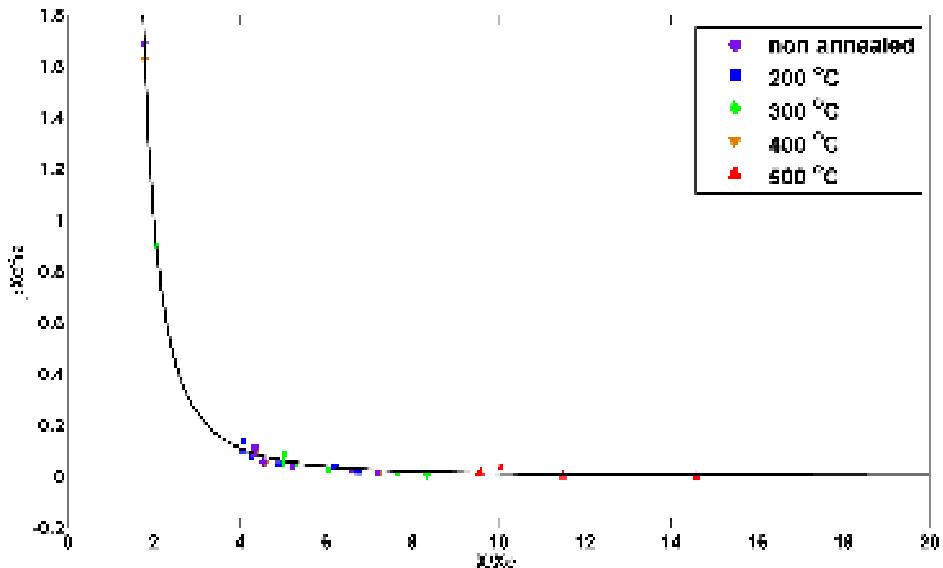

| <b>Figure 115:</b> Data collapse at different annealing temperatures in the rescaled variables $x=x_c$ versus $\rho x_c^{-\alpha}/a$ . The value of the exponent is $\alpha = 2$ . ....                                                                                                                                                                                                    | 161 |

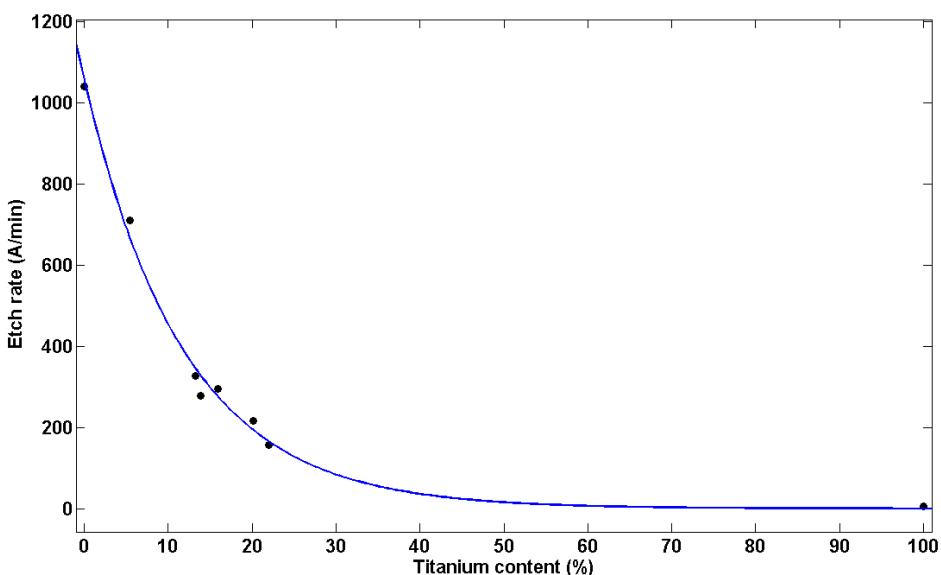

| <b>Figure 116:</b> Graph showing the etch rate of the silicon titanium films as a function of the percentage titanium. ....                                                                                                                                                                                                                                                                | 161 |

# List of Tables

|                                                                                                                                                |     |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| <b>Table 1:</b> A table summarising the three main methods used to apply photoresist .....                                                     | 34  |

| <b>Table 2:</b> Standard electrode potentials $E^{\circ}$ (Taken from ref [93]). .....                                                         | 37  |

| <b>Table 3:</b> Effect of different parameters on the grain size in electrochemically deposited films (Taken from ref [96]). .....             | 42  |

| <b>Table 4:</b> A table showing the resistance in mega ohms of the chip wires as measured by a digital ohm-metre. .....                        | 82  |

| <b>Table 5:</b> A table showing the current density each wire could safely contain. ....                                                       | 82  |

| <b>Table 6:</b> Table showing the different dimensions of the pyramids and wires present on the atom chip. ....                                | 90  |

| <b>Table 7:</b> Table showing the $R_n$ constants used to fit the data to equation 37 for two different 2d slices through the hemisphere. .... | 138 |

| <b>Table 8:</b> Comparison of mechanical properties of poly silicon, a-Si:H and titanium. ....                                                 | 153 |

## DECLARATION OF AUTHORSHIP

I, Gareth Neil Lewis declare that the thesis entitled 'Towards an Integrated Atom Chip'

and the work presented in the thesis are both my own, and have been generated by me as the result of my own original research. I confirm that:

- this work was done wholly or mainly while in candidature for a research degree at this University;

- where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- where I have consulted the published work of others, this is always clearly attributed;

- where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work;

- I have acknowledged all main sources of help;

- where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself;

- parts of this work have been published as:

Resistivity percolation of co-sputtered amorphous Si/Ti films, Materials Letters, Volume 63, Issue 2, 31 January 2009, Pages 215-217

Fabrication of Magneto-Optical Atom Traps on a Chip, Journal of Microelectromechanical Systems, Accepted for publication

Signed: .....

Date: .....

# Acknowledgements

First and foremost I must thank supervisor Prof. Michael Kraft, who has guided me throughout my research and has been indispensable in completing my thesis. Next I would like to thank Dr Zakaria Moktadir for his wealth of knowledge and time he spent on me and my project at every step. I must also thank Dr Liudi Jiang who let me run her project after the fire giving me my 6<sup>th</sup> chapter.

I must thank the Atom chip group including Carsten whom I worked along side and everyone at Imperial College London including Prof. Ed Hinds, Athanasis, Fernando, Michael, Sam, Stefan and Rob for all the work they did making this thesis possible.

Thank you to the NSI group, who supported me from the start and then the SES, ORC and Physics department who allowed me to use their facilities after the fire. Special thanks have to go to Zondy Webber from the Physics cleanroom, who tirelessly helped train me and then fixed the machines as they constantly broke. He was always on hand whenever needed and would go out of his way to be helpful at all times.

Thank you to everyone involved in the setting up and working of the temporary clean room especially Dave Sagan and Neil Sessions who kept it all running smoothly.

Thank you to everyone at Innos who were responsible for helping with many stages of my fabrication especially Graham, Janet, Nasser, Neil, Brian and Jean. I must especially thank Mir for making my secondment to Eindhoven possible as well as Richard, Enrico Corry, Denny, Tim, Pejwaak and Tony for keeping me company while I was out there.

A special thank you goes to Mike Wild of Metalor Ltd for all his help in getting my electroplating started and continued technical support. This knowledge was invaluable at the start of my PhD.

Thank you to Dr P Thurner for allowing me to use his AFM and for his invaluable input into creating my results and Shuncai Wang for his continual input on my SEM/EDX work.

I must also acknowledge all the support and help I received from my group colleagues Badin and Kian. They both helped me out whenever I needed something done or just a discussion on a fabrication issue.

I must thank Kevin, Stuart and Timothy for the hours of their time I must have wasted chatting when I was bored or fed up of my work. Thank you to all my fellow students and colleges especially Ben, Chien, Chris J, and Sun, who made it such a hard place to leave. You have all made my PhD period more enjoyable.

I must thank my parents who made it all possible by supporting me throughout my academic career both in spirit and financially.

Finally thank you to my girlfriend Gemma Gwynne for putting up with me throughout the whole period.

# **Chapter 1**

## **Introduction**

Since the Nobel Prize winning work of Cohen-Tannoudji, Chu and Phillips for laser cooling and trapping of atoms in 1997 [1] and Ketterle, Cornell and Wieman for Bose-Einstein condensation (BEC) in dilute alkali gases in 2001 [2], there has been a huge increase in the field of cold and ultra cold atom physics. Using ultra cold atoms it is possible to study the quantum wave like nature of matter in a manner not previously possible which, in turn, is opening up the field of atom optics and quantum information processing. These original traps were created using only optical elements but since then new faster methods for producing BEC's have been created involving micro machined microchips [3].

Micro-Electro-Mechanical Systems (MEMS) is the manufacturing of micro machined sensors and actuators on a substrate to create new integrated devices. Using tools and methods developed for the integrated circuit industry, microelectronic fabrication techniques are combined with micromachining processes to realise a complete system on a single microchip. MEMS processing is therefore ideally suited for use in the production of micro machined chips for trapping ultra cold atoms often termed 'atom chips'. Atom chips combine cold atom physics with MEMS microfabrication techniques to create electric, magnetic and optical fields to trap and manipulate cold atom clouds [4-6] and to form BECs [7-9].