University of Southampton Research Repository

ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

UNIVERSITY OF SOUTHAMPTON

FACULTY OF ENGINEERING, SCIENCE AND MATHEMATICS

SCHOOL OF ELECTRONICS AND COMPUTER SCIENCE

**Electrodeposited Ni/Ge and Germanide Schottky

Barriers for Nanoelectronic Applications**

by

Muhammad Khaled Husain

*A thesis submitted in partial fulfilment of the

requirements for the award of Doctor of Philosophy

at the University of Southampton*

July 2009

SUPERVISOR:

Cornelis H. "Kees" de Groot

---

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

Faculty of Engineering, Science and Mathematics

School of Electronics and Computer Science

A thesis submitted in partial fulfilment of the

requirements for the award of Doctor of Philosophy

**Electrodeposited Ni/Ge and Germanide Schottky Barriers

for Nanoelectronic Applications**

by Muhammad Khaled Husain

In recent years metal/semiconductor Schottky barriers have found numerous applications in nanoelectronics. The work presented in this thesis focuses on the improvement of a few of the relevant devices using electrodeposition of metal on Ge for Schottky barrier fabrication. This low energy metallisation technique offers numerous advantages over the physical vapour deposition techniques. Electrical characteristics of the grown diodes show a high quality rectifying behaviour with extremely low leakage currents even on highly doped Ge. A non-Arrhenius behaviour of the temperature dependence is observed for the grown Ni/Ge diodes on lowly doped Ge that is explained by a spatial variation of the barrier heights. The inhomogeneity of the barrier heights is explained in line with an intrinsic surface states model for Ge. The understanding of the intrinsic surface states will help to create ohmic contacts for doped n-MOSFETs. NiGe were formed single phase by annealing. Results reveal that by using these high-quality germanide Schottky barriers as the source/drain, the subthreshold leakage currents of a Schottky barrier MOSFET could be minimised, in particular, due to the very low drain/body junction leakage current exhibited by the electrodeposited diodes. The Ni/Ge diodes on highly doped Ge show negative differential conductance at low temperature. This effect is attributed to the inter-valley electron transfer in Ge conduction band to a low mobility valley. The results show experimentally that Schottky junctions could be used for hot electron injection in transferred-electron devices. A vertical Co/Ni/Si structure has been fabricated for spin injection and detection in Si. It is shown that the system functions electrically well although no magnetoresistance indicative of spin injection was observed.

# Declaration of authorship

I, Muhammad Khaled Husain, declare that the thesis entitled:

"Electrodeposited Ni/Ge and Germanide Schottky Barriers for Nanoelectronic Applications"

and the work presented in it are my own. I confirm that:

- this work was done wholly or mainly while in candidature for a research degree at this University;

- where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated;

- where I have consulted the published work of others, this is always clearly attributed;

- where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- where the thesis is based on work done by myself jointly with others, I have made clear exactly what I have contributed by myself and for the integrality of projects, I have made clear what was done by others.

- parts of this work have been published in research journals. A list of publications is provided with this manuscript.

Signed:

Date:

# Acknowledgements

I would like to thank my supervisor Dr. Kees de Groot for his guidance, technical and otherwise, throughout my PhD studies. The intellectual freedom he possesses and encourages has made my time here in Southampton very productive, both personally and professionally. In this opportunity I would like to convey my deepest gratitude for providing me tremendous support after the ECS cleanroom fire to pursue my interest, and at the same time keeping me focused and nudging me in the right direction. I also want to thank Professor Peter Ashburn and my advisor, Dr. Nicolas Green for their useful advice and feedback during my nine months and M.Phil to PhD upgrade defence viva, respectively.

I would like to thank all the members of the research group for the help, knowledge, and assorted truisms passed back and forth over the years. Special thanks to Dr. Xiaoli Li, Dr. David Gonzalez, and Dr. Michalis Kiziroglou for training me to use the Electrodeposition setup. I would like to thank the entire cleanroom staff, past and present, for their support in the fab. In particular Dr. Dave Sehgal, and Dr. Neil Sessions for their help with annealing, evaporation and HF etching. I acknowledge the support from Zondy Webber of the Physics Department for training me to use the Evaporator, Direct write lithography and SEM. A special thanks to Chris Morrison, Dawei Wang and Professor Peter de Groot for their continuous support in letting me use their low temperature measurement facility.

I owe everything to my parents. A mere 'thank you' to acknowledge their sacrifice can hardly do justice to the immense gratitude I feel. I hope my accomplishments can make them proud. Last, but not the least, a big thanks goes to my wife and my little son Fahham. I could not have made it this far without their (Fahhams!) constant support, encouragement and patience.

---

# List of Publications

## Articles

### Inhomogeneous Ni/Ge Schottky barriers due to variation in Fermi-level pinning

X. V. Li, **M. K. Husain**, M. Kiziroglou and C. H. de Groot, Microelectronic Engineering, Vol. 86 (7-9), pp. 1599-1602, 2009.

### High-quality Schottky contacts for limiting leakage currents in Ge-based Schottky barrier MOSFETs

**M.K. Husain**, X. V. Li, and C.H. de Groot, IEEE Transactions on Electron Devices, Vol. 56, No. 3, pp.499-504, 2009.

### High-quality NiGe/Ge diodes for Schottky barrier MOSFETs

**M.K. Husain**, X. V. Li, and C.H. de Groot, Materials Science in Semiconductor Processing, 2009 (in press, available online).

### Observation of negative differential conductance in a reverse-biased Ni/Ge Schottky diode

**M.K. Husain**, X. V. Li, and C.H. de Groot, IEEE Electron Device Letters, Vol. 30, No. 9, pp.966-968, 2009 .

### A vertical transport geometry for electrical spin injection and extraction in Si

**M.K. Husain**, X. V. Li, and C.H. de Groot, Solid State Communications, Vol. 149, pp.1565-1568, 2009.

## Conference Presentations

**Electrical spin injection and extraction in Si in a vertical transport geometry**

**M.K. Husain**, X. V. Li, and C.H. de Groot, IEEE International Magnetics Conference, 2009, Sacramento, CA, USA (Accepted).

**High-quality Schottky contacts for limiting leakage currents in Ge based Schottky barrier MOSFETs**

**M.K. Husain**, X. V. Li, and C.H. de Groot, UK Semiconductors conference 2008, Sheffield, UK.

**High-quality NiGe/Ge contacts for Schottky barrier MOSFETs**

**M.K. Husain**, X. V. Li, and C.H. de Groot, E-MRS Spring Meeting, 2008, Strasbourg, France.

**A study on Ge based spin-LED for spintronic applications**

**M.K. Husain**, X. V. Li, and C.H. de Groot, Condensed Matter and Materials Physics, 12-13 April 2007, University of Leicester , UK

# List of symbols

|                      |                                                |

|----------------------|------------------------------------------------|

| $a, b, c$            | Lattice constants                              |

| $d$                  | Broadening of an XRD peak                      |

| $d_{Res}$            | Resolution of XRD                              |

| $d_{Observed}$       | Observed broadening of an XRD peak             |

| $e^-$                | Electron                                       |

| $h^+$                | Hole                                           |

| $k$                  | Boltzmann constant                             |

| $k_l$                | A fitting parameter of Lombardi model          |

| $i_o$                | Exchange current density                       |

| $i_L$                | Mass transport limited current                 |

| $m^*$                | Effective mass                                 |

| $m_j$                | Nondegenerate quantum states                   |

| $n_t$                | Number of different mobility mechanisms        |

| $q$                  | Electron charge                                |

| $t$                  | Time                                           |

| $t_{ox}$             | Gate oxide thickness of a MOSFET               |

| $v_{sat}$            | Saturation velocity of electrons               |

| $v_1, v_2, v_3, v_4$ | Electron drift velocities                      |

| $z$                  | Valency                                        |

| $A^*$                | Richardson constant                            |

| $A^r$                | A fitting parameter of Arora mobility model    |

| $B_l$                | A fitting parameter of Lombardi mobility model |

| $C_l$                | A fitting parameter of Lombardi mobility model |

| $C$                  | Capacitance                                    |

| $C_{ox}$             | Gate oxide capacitance                         |

| $C_b$                | Bulk concentrations of metal ion in a solution |

| $D_p$                | Hole diffusion constant                        |

| $D_n$                | Electron diffusion constant                    |

| $D_M$                | Density of metal M                             |

| $E_{bgn}$            | A material parameter for Slotboom model        |

---

|            |                                                                                |

|------------|--------------------------------------------------------------------------------|

| $E_C$      | Conduction band energy level                                                   |

| $E_V$      | Valence band energy level                                                      |

| $E_o$      | Vacuum energy level                                                            |

| $E_F$      | Fermi energy level                                                             |

| $E_m$      | Most probable energy of tunneling electrons                                    |

| $E_{CNL}$  | Charge neutrality energy level in a semiconductor                              |

| $E_g$      | Semiconductor bandgap energy                                                   |

| $E_{eq}$   | Equilibrium potential of an electrode                                          |

| $G_{CC}$   | Generation rate in the conduction band                                         |

| $I$        | Current                                                                        |

| $I_S$      | Saturation current                                                             |

| $I_{sub}$  | Subthreshold current                                                           |

| $I_{DS}$   | Drain to source current in a MOSFET                                            |

| $I_{GIDL}$ | Gate induced drain leakage current                                             |

| $I_{SD}$   | Source to drain current                                                        |

| $J$        | Current density                                                                |

| $J_p$      | Hole current density                                                           |

| $J_n$      | Electron current density                                                       |

| $J_+$      | Current density from semiconductor to metal                                    |

| $J_-$      | Current density from metal to semiconductor                                    |

| $J_S$      | Saturation current density                                                     |

| $J_{CC}$   | Current density of electrons tunneling from bulk to interface conduction bands |

| $L_g$      | Gate length of a MOSFET                                                        |

| $M$        | A metal                                                                        |

| $M_w$      | Atomic weight of metal M                                                       |

| $N_A$      | Avogadro's number                                                              |

| $N_d$      | Donor doping density                                                           |

| $N_a$      | Acceptor doping density                                                        |

| $N_i$      | Total concentration of ionised impurity                                        |

| $N_0$      | A reference impurity concentration of Arora mobility model                     |

| $N_{ref}$  | A reference impurity concentration for Slotboom model                          |

---

|              |                                                              |

|--------------|--------------------------------------------------------------|

| $Q$          | Cathodic charge in electrodeposition                         |

| $Q_T$        | Total charge of all reactions during electrodeposition       |

| $R_S$        | Series resistance of a Schottky diode                        |

| $R_{sh}$     | Sheet resistance                                             |

| $R_r$        | Recombination rate                                           |

| $R_g$        | Gas constant                                                 |

| $R_{CC}$     | Recombination rate in the conduction band                    |

| $S$          | Fermi-level pinning factor                                   |

| $T$          | Temperature                                                  |

| $T_{film}$   | Deposited metal film thickness                               |

| $T_n$        | Electron temperature                                         |

| $Vol_M$      | Volume of metal M                                            |

| $V$          | Voltage                                                      |

| $V_g$        | Gate voltage of a MOSFET                                     |

| $V_{gsub}$   | Subgate voltage                                              |

| $V_d$        | Drain voltage of a MOSFET                                    |

| $V_{DS}$     | Drain to source voltage in a MOSFET                          |

| $V_{GS}$     | Gate to source voltage in a MOSFET                           |

| $V_T$        | Threshold voltage                                            |

| $V_n$        | Depth of Fermi-level below the conduction band               |

| $V_i$        | Intercept of the $C^{-2}$ - $V$ curve with voltage axis      |

| $W/L$        | Aspect ratio of the gate in a MOSFET                         |

| $X_d$        | Offset between drain and gate edge                           |

| $\alpha$     | Current efficiency of electrodeposition                      |

| $\beta_c$    | A temperature dependent parameter in Canali Mobility model   |

| $\delta$     | Thickness of diffusion layer                                 |

| $\delta_l$   | A fitting parameter of Lombardi model                        |

| $\Phi_m$     | Metal work function                                          |

| $\Phi_{CNL}$ | Energy difference between charge neutrality level and vacuum |

| $\Phi_s$     | Semiconductor work function                                  |

| $\phi_n$     | Electron Schottky barrier height                             |

| $\phi_p$     | Hole Schottky barrier height                                 |

---

|                     |                                                        |

|---------------------|--------------------------------------------------------|

| $\overline{\phi_n}$ | Mean electron Schottky barrier height                  |

| $\eta$              | Ideality factor                                        |

| $\eta_l$            | A fitting parameter of Lombardi model                  |

| $\Theta$            | The unit step function                                 |

| $\chi$              | Semiconductor electron affinity                        |

| $\psi_i$            | Built-in potential                                     |

| $\psi_s$            | Surface potential                                      |

| $\rho$              | Resistivity                                            |

| $\mathcal{E}$       | Electric field                                         |

| $\mathcal{E}_{eq}$  | Equilibrium electric field                             |

| $\mathcal{E}_t$     | Transverse electric field                              |

| $\mathcal{E}_{ref}$ | A reference electric field of Lombardi model           |

| $\mathcal{E}_d$     | A component of electric field parallel to current flow |

| $\mathcal{E}_0$     | An electric field constant                             |

| $\epsilon_s$        | Dielectric constant                                    |

| $\epsilon_\infty$   | Electronic component of dielectric constant            |

| $\mu_n$             | Electron mobility                                      |

| $\mu_p$             | Hole mobility                                          |

| $\mu_{dop}$         | Doping dependent mobility                              |

| $\mu_{min}$         | A reference mobility of Arora mobility model           |

| $\mu_d$             | A reference mobility of Arora mobility model           |

| $\mu_{ac}$          | Mobility due to acoustic surface phonons               |

| $\mu_{sr}$          | Mobility due to surface roughness                      |

| $\mu_{low}$         | Low field mobility                                     |

| $\Gamma_{CC}$       | Probability of tunneling to conduction band            |

| $\sigma_s$          | Standard deviation of barrier height                   |

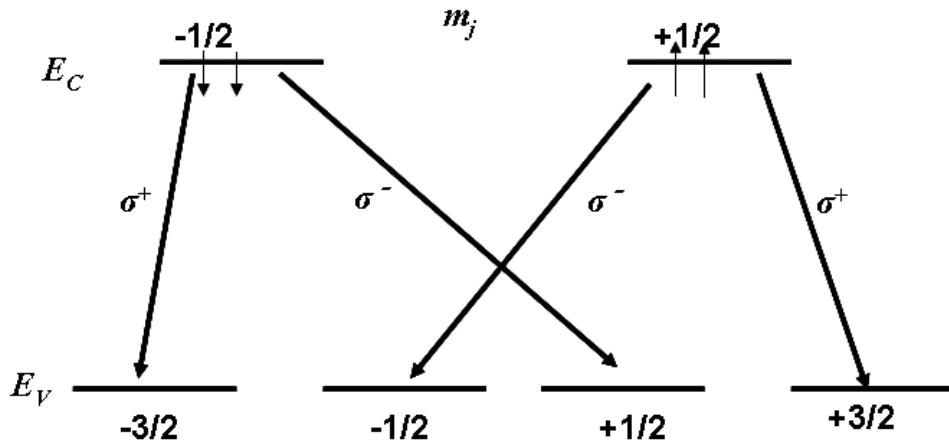

| $\sigma^+$          | Left circularly polarised electroluminescence          |

| $\sigma^-$          | Right circularly polarised electroluminescence         |

| $\lambda_l$         | Transverse electric field                              |

| $\lambda$           | Wavelength                                             |

| $\zeta$             | Overpotential of an electrode                          |

# List of acronyms

|            |                                                   |

|------------|---------------------------------------------------|

| 2DEG       | 2-dimensional electron gas                        |

| CMOS       | Complementary metal-oxide-semiconductor           |

| FE         | Field emission                                    |

| GIDL       | Gate-induced drain leakage                        |

| LED        | Light emitting diode                              |

| MIGS       | Metal-induced gap states                          |

| nMOSFET    | n channel MOSFET                                  |

| pMOSFET    | p channel MOSFET                                  |

| MOSFET     | Metal-oxide-semiconductor field effect transistor |

| NDC        | Negative differential conductance                 |

| SB-MOSFET  | Schottky barrier MOSFET                           |

| SB-nMOSFET | Schottky barrier n-channel MOSFET                 |

| SB-pMOSFET | Schottky barrier p-channel MOSFET                 |

| SEM        | Scanning electron microscope                      |

| TE         | Thermionic emission                               |

| TFE        | Thermionic field emission                         |

| WKB        | Wentzel-Kramers-Brillouin                         |

| XRD        | X-ray diffraction                                 |

# Contents

|                                                                          |            |

|--------------------------------------------------------------------------|------------|

| <b>Abstract</b>                                                          | <b>i</b>   |

| <b>Declaration of Authorship</b>                                         | <b>ii</b>  |

| <b>Acknowledgements</b>                                                  | <b>iii</b> |

| <b>List of publications</b>                                              | <b>iv</b>  |

| <b>List of symbols</b>                                                   | <b>vi</b>  |

| <b>List of acronyms</b>                                                  | <b>x</b>   |

| <b>1 Introduction</b>                                                    | <b>1</b>   |

| 1.1 General . . . . .                                                    | 1          |

| 1.2 A Schottky barrier . . . . .                                         | 2          |

| 1.3 Schottky barriers in conventional MOSFETs . . . . .                  | 2          |

| 1.4 Schottky barriers as source/drain in MOSFETs . . . . .               | 3          |

| 1.5 Schottky barriers in Gunn diodes . . . . .                           | 4          |

| 1.6 Schottky barriers in Spin transistors . . . . .                      | 5          |

| 1.7 Outline of this thesis . . . . .                                     | 6          |

| <b>2 Schottky barriers</b>                                               | <b>8</b>   |

| 2.1 Introduction . . . . .                                               | 8          |

| 2.2 Formation and operational principles of a Schottky barrier . . . . . | 9          |

| 2.2.1 Thermionic emission for Schottky characterisation . . . . .        | 11         |

| 2.2.2 Field emission and thermionic field emission . . . . .             | 15         |

| 2.3 Schottky barrier fabrication by electrodeposition . . . . .          | 16         |

| 2.3.1 Electrodeposition principle . . . . .                              | 17         |

| 2.3.2 Film thickness control . . . . .                                   | 20         |

| 2.4 Device simulation framework . . . . .                                | 21         |

| 2.4.1 An introduction to the simulation tool . . . . .                   | 21         |

| 2.4.2 Simulation models . . . . .                                        | 23         |

| 2.4.3 Schottky barrier simulation . . . . .                              | 26         |

---

|                                                                                       |            |

|---------------------------------------------------------------------------------------|------------|

| <b>3 Inhomogeneous Ni/Ge Schottky barriers</b>                                        | <b>30</b>  |

| 3.1 Introduction . . . . .                                                            | 30         |

| 3.2 A conventional doped source/drain MOSFET . . . . .                                | 31         |

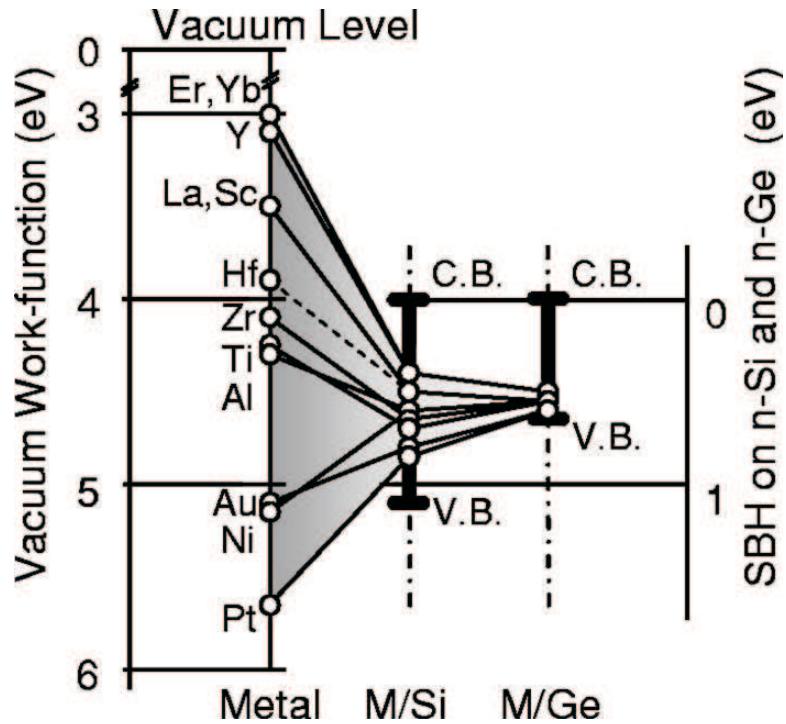

| 3.3 Fermi-level pinning by metal-induced gap states . . . . .                         | 33         |

| 3.4 Experimental procedure . . . . .                                                  | 37         |

| 3.5 Results and discussions . . . . .                                                 | 40         |

| 3.5.1 Electrical characteristics . . . . .                                            | 40         |

| 3.5.2 Inhomogeneity of Schottky barrier . . . . .                                     | 46         |

| 3.6 Conclusions . . . . .                                                             | 50         |

| <b>4 NiGe/Ge contacts for Schottky barrier MOSFETs</b>                                | <b>51</b>  |

| 4.1 Introduction . . . . .                                                            | 52         |

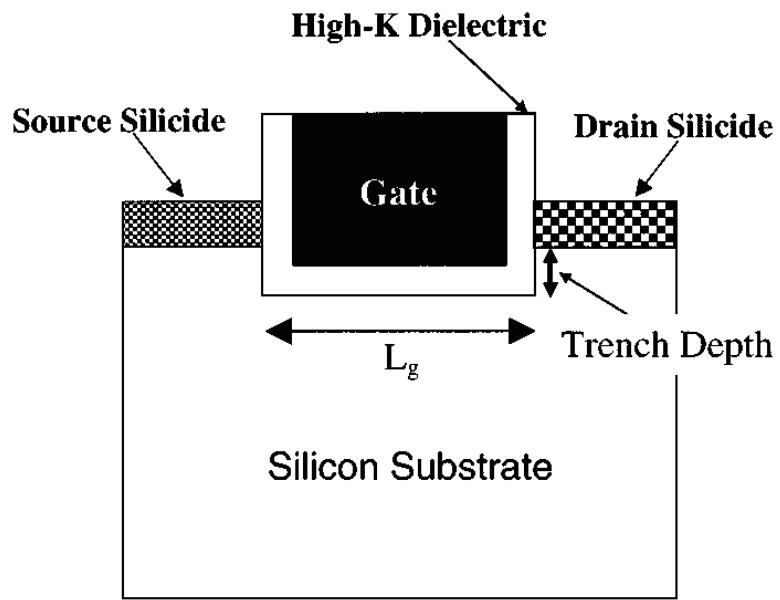

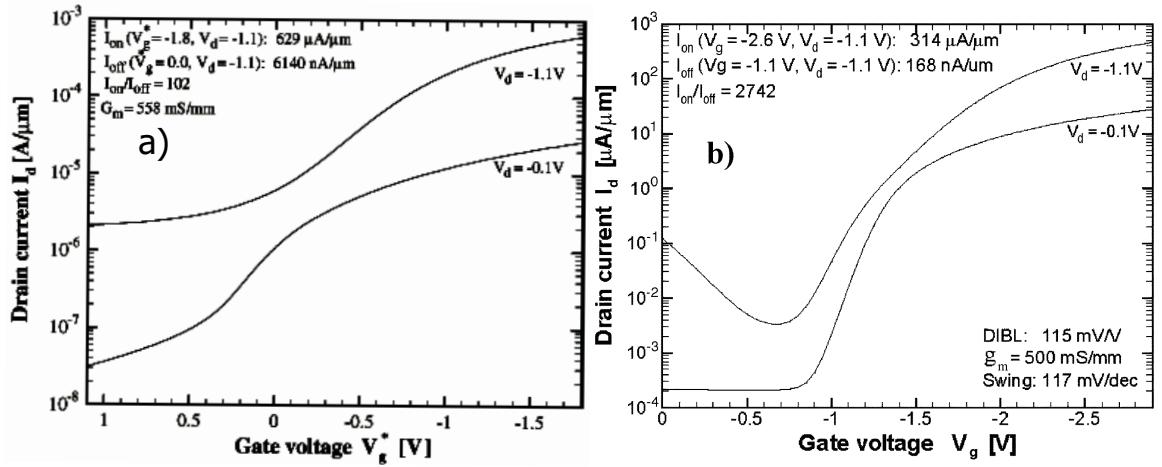

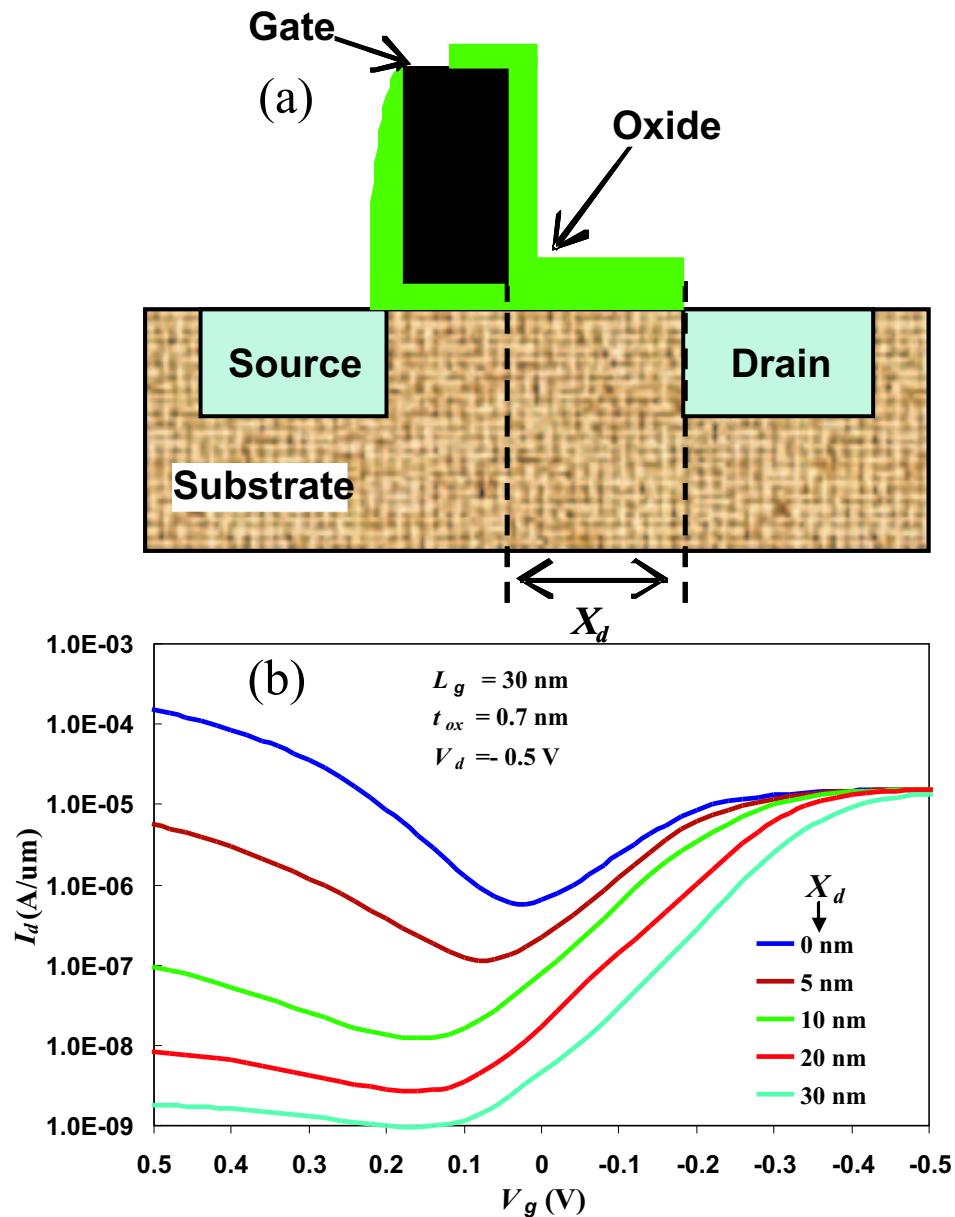

| 4.2 The Schottky barrier MOSFET . . . . .                                             | 52         |

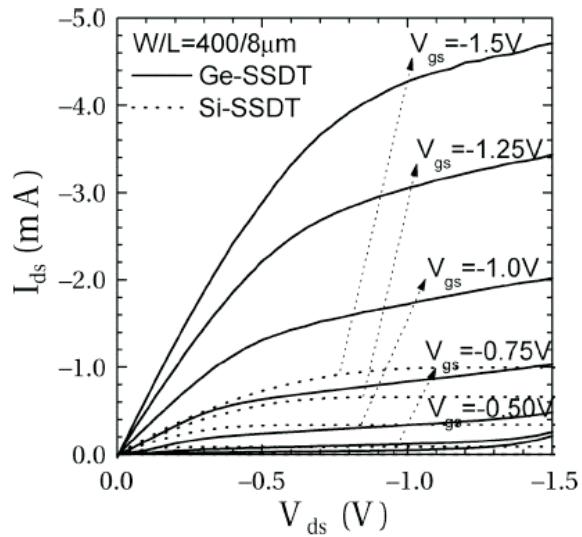

| 4.3 Ge based Schottky barrier MOSFETs . . . . .                                       | 58         |

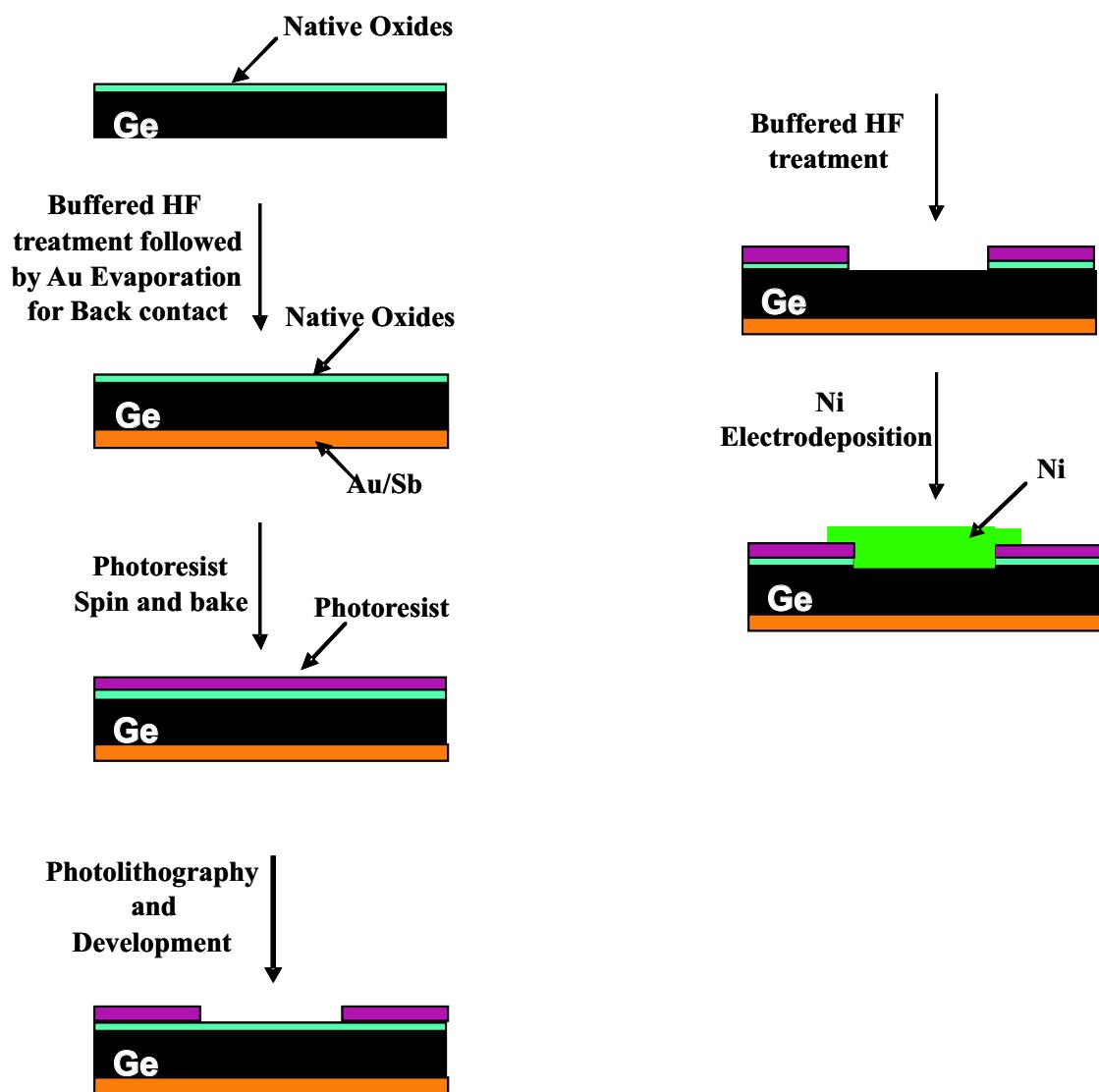

| 4.4 Experimental procedure . . . . .                                                  | 64         |

| 4.5 Results and discussions . . . . .                                                 | 66         |

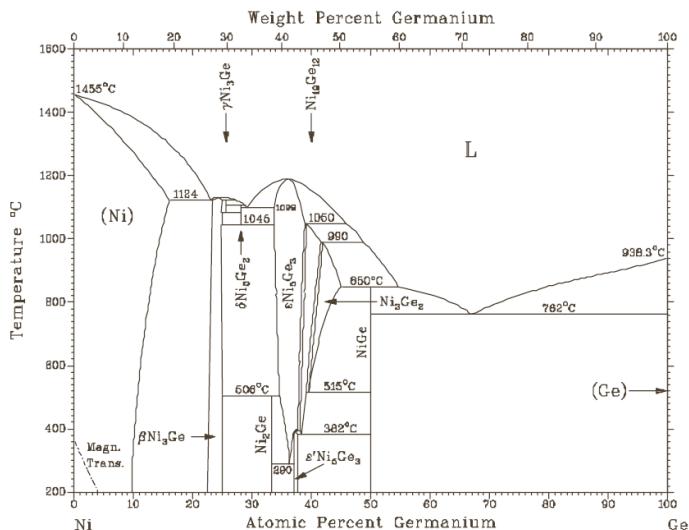

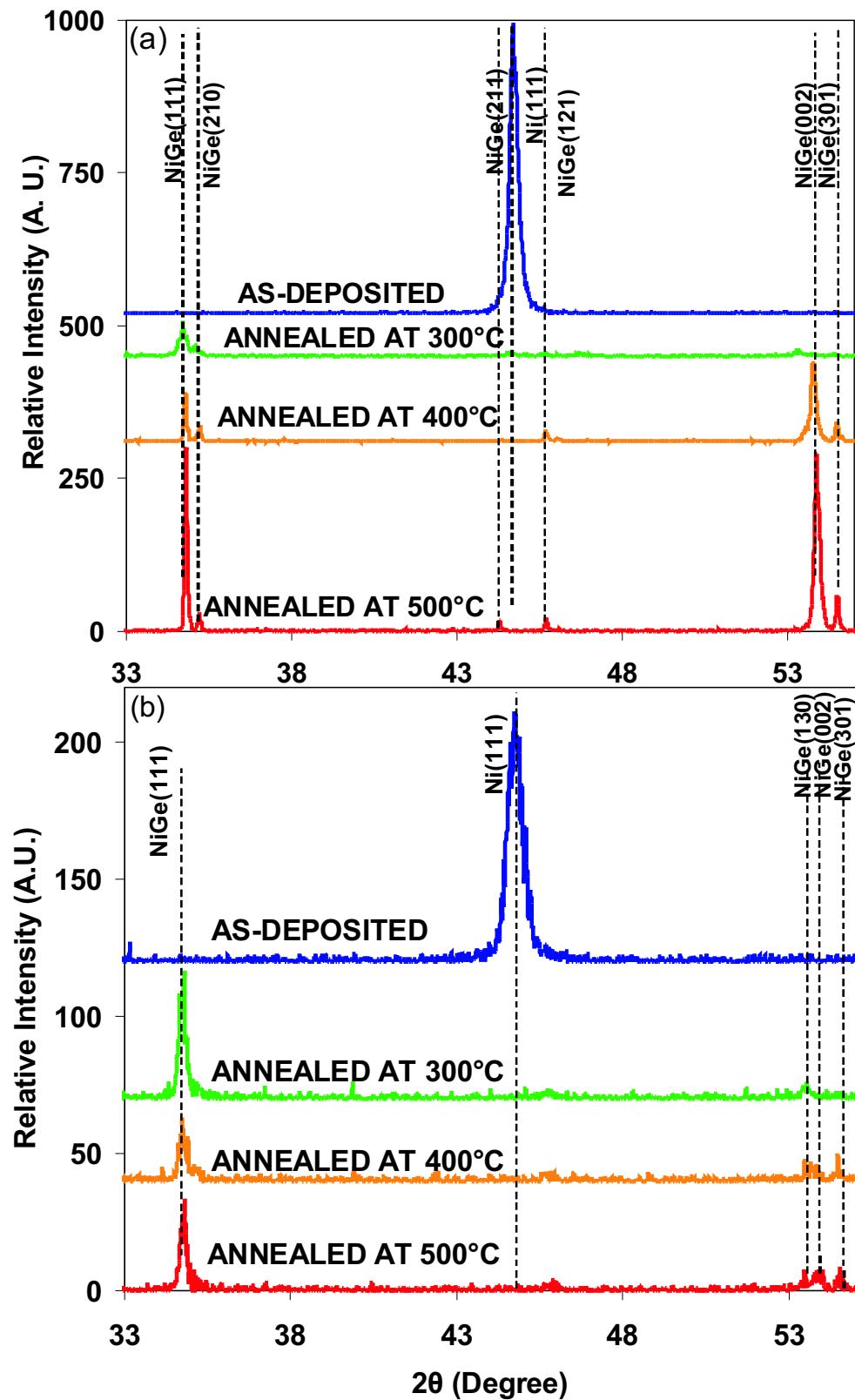

| 4.5.1 Germanidation of Ni . . . . .                                                   | 66         |

| 4.5.2 Electrical characteristics . . . . .                                            | 74         |

| 4.6 SB-MOSFET simulation . . . . .                                                    | 81         |

| 4.6.1 Calibration of simulation to experiments . . . . .                              | 81         |

| 4.6.2 Leakage current suppression . . . . .                                           | 83         |

| 4.7 Conclusions . . . . .                                                             | 93         |

| <b>5 Negative differential conductance in a reverse-biased Ni/Ge Schottky barrier</b> | <b>94</b>  |

| 5.1 Introduction . . . . .                                                            | 94         |

| 5.2 The transferred-electron device . . . . .                                         | 95         |

| 5.3 Electrical characteristics of Ni/Ge diode . . . . .                               | 99         |

| 5.4 Calculation of the energy of tunneling electrons . . . . .                        | 105        |

| 5.5 Conclusions . . . . .                                                             | 109        |

| <b>6 Electrical spin injection and extraction in Si using Schottky barriers</b>       | <b>111</b> |

| 6.1 Introduction . . . . .                                                            | 112        |

| 6.2 Spin injection and extraction in a semiconductor . . . . .                        | 113        |

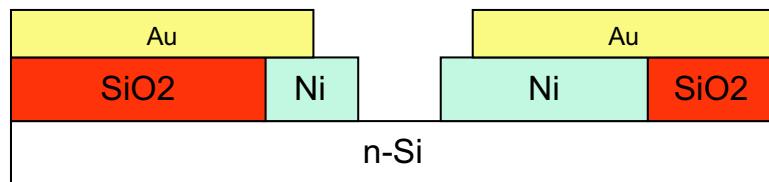

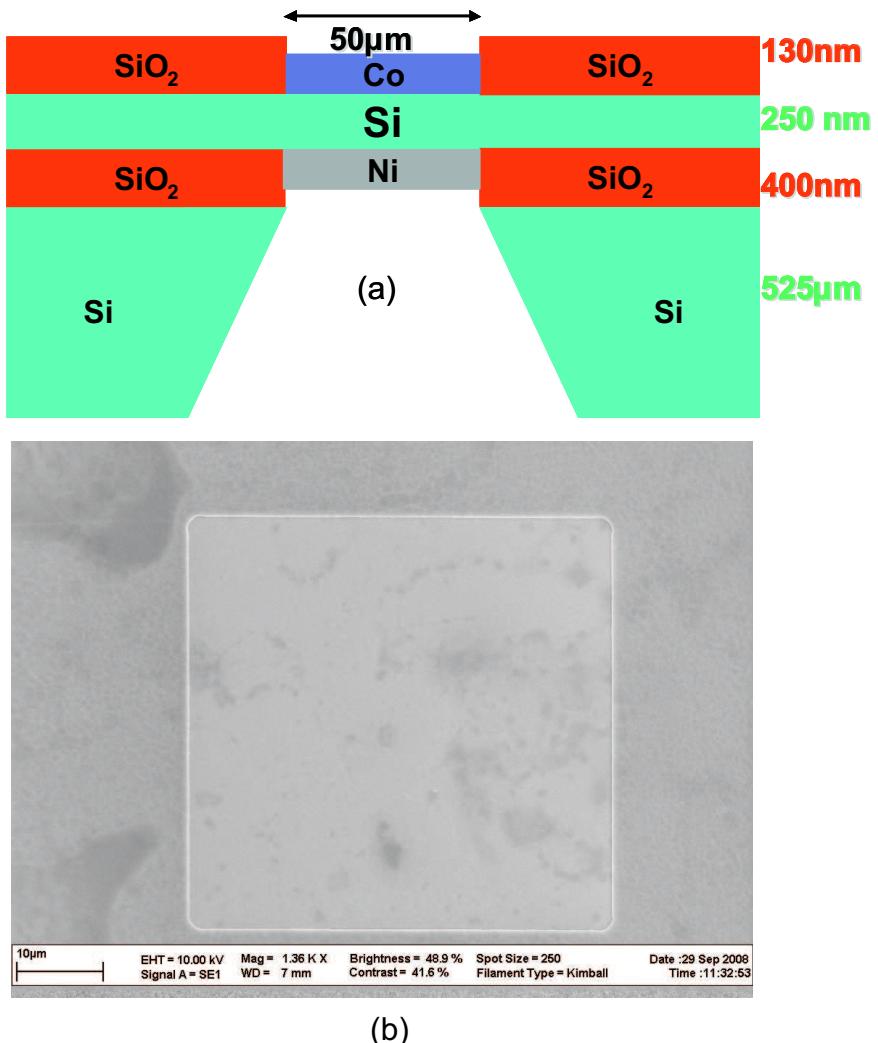

| 6.3 Si-based vertical geometry for spin injection . . . . .                           | 118        |

| 6.4 Experimental procedures . . . . .                                                 | 120        |

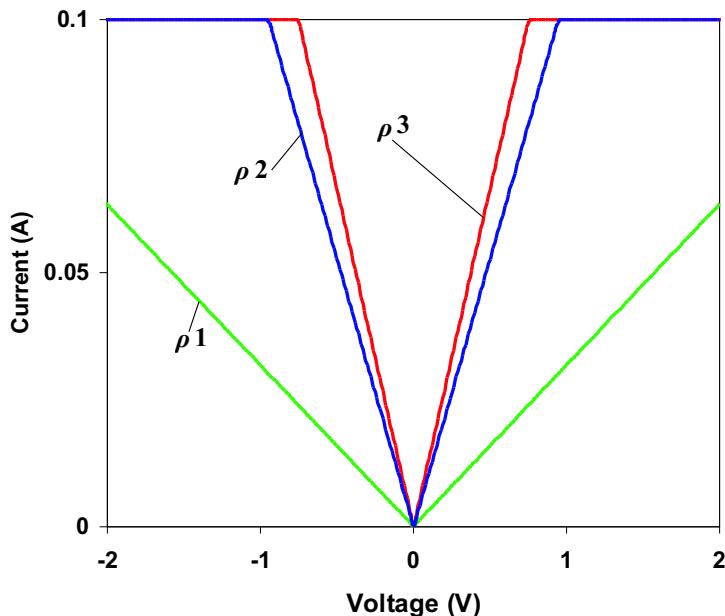

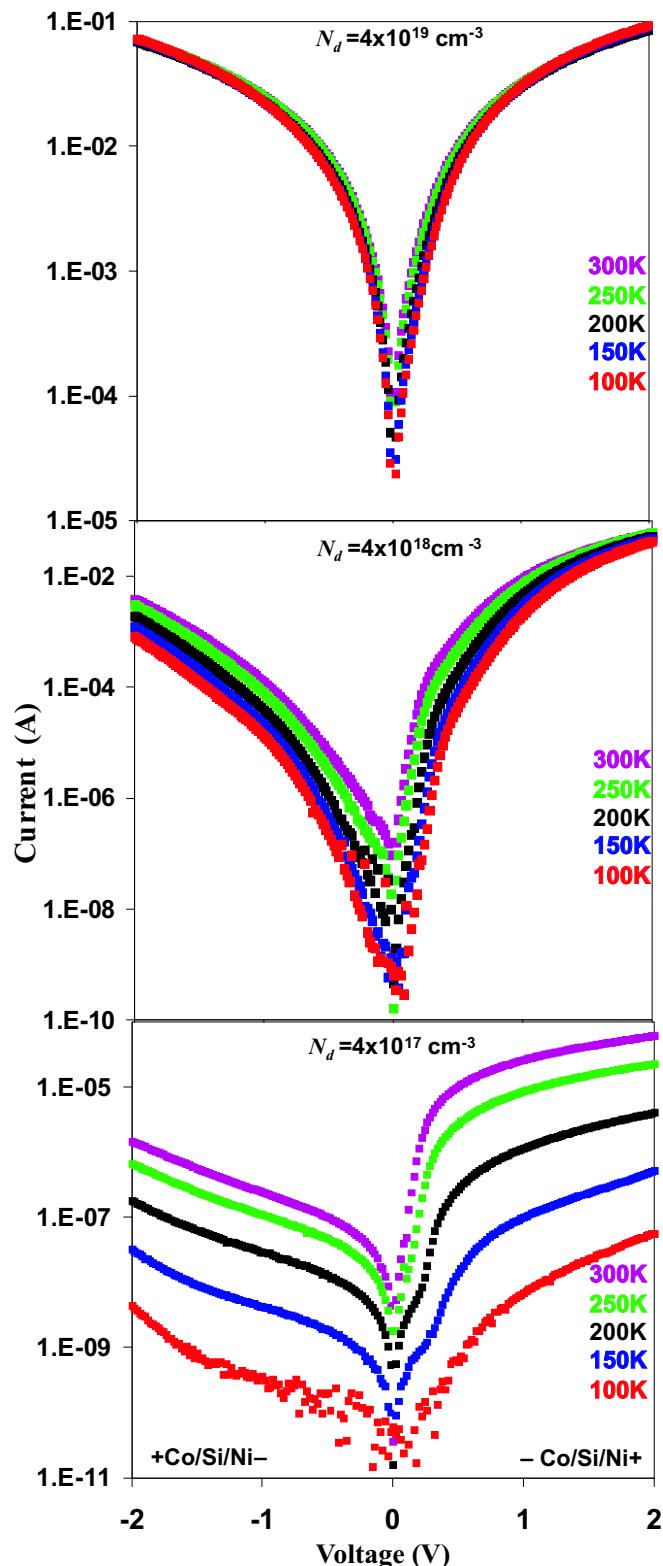

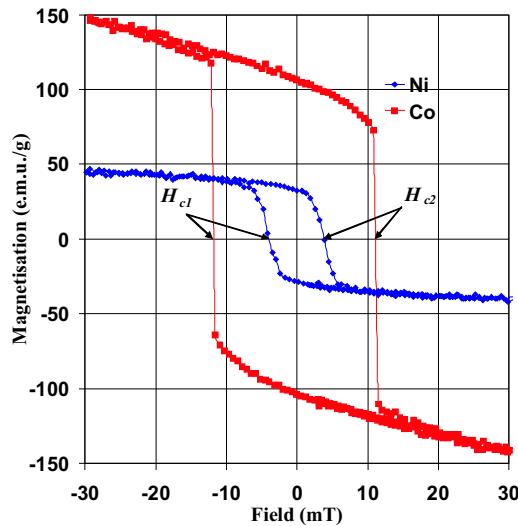

| 6.5 Results and discussions . . . . .                                                 | 122        |

| 6.5.1 Electrical characteristics . . . . .                                            | 122        |

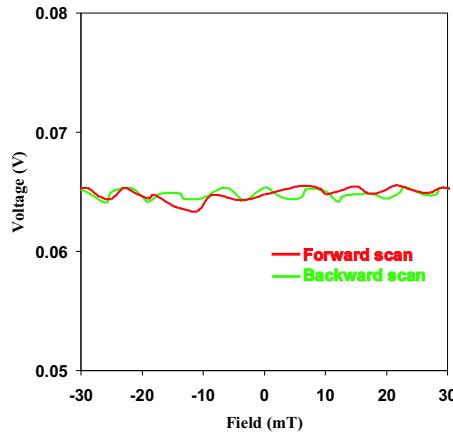

| 6.5.2 Magnetotransport characteristics . . . . .                                      | 125        |

| 6.5.3 Simulation of the spin injection extraction device . . . . .                    | 129        |

| 6.6 Conclusions . . . . .                                                             | 130        |

| <b>7 Conclusions and outlook</b>                                                      | <b>132</b> |

| <b>Bibliography</b>                                                                   | <b>136</b> |

# Chapter 1

## Introduction

### 1.1 General

Semiconductor devices have been studied for over 125 years [1]. A metal / semiconductor interface was the first semiconductor device ever studied. This interface can be used as a rectifying contact, that is the device allows electrical current to flow easily only in one direction, or as an ohmic contact, which can pass current in either direction with only a negligible voltage drop. This device is much easier to fabricate than a p-n junction rectifier, which is formed at the interface of a p-type and an n-type semiconductor. During the past forty years components based on metal/semiconductor rectifying junctions have been increasingly used in microelectronics, and research activity has continued with the aim of obtaining a full understanding of the physics of the rectifying barrier formation and the current transport across metal/semiconductor interfaces. Modern surface science analytical methods have been applied to probe the detailed microscopic interactions at interfaces between metals and semiconductors. However, as the transistors sizes are going down to allow higher density of information processing and storage, a flexible and commercially viable technique of fabrication on the nanometre-scale will be required. This imposes a challenge to the growth of electronics industry in future. The conventional metallisation in microelectronics is performed by physical vapour deposition methods like evaporation and sputtering. In contrast, electrodeposition is adopted for metallisation on semiconductors in this project for metal/semiconductor rectifying contact

fabrication. It is shown that this technique gives higher rectification both for Si and in particular for Ge. The fabricated contacts could offer significant improvement of semiconductor device performance for the devices discussed in the next sections.

## 1.2 A Schottky barrier

A Schottky barrier is the rectifying junction formed by the intimate contact of a metal and a semiconductor having nonequal work functions or electronegativities. The devices is dominated by a majority carrier current flow, i.e., electrons for n-type and holes for p-type semiconductors. Because of the metal on one side of the junction, a Schottky barrier has less depletion layer than a conventional p-n junction diode. This results in less stored charge and faster switching of the device. Design considerations with Schottky barriers are limited in some applications compared to p-n junction rectifiers because their reverse leakage currents are many times higher. Still the physical and transport properties of the Schottky barrier contacts are of huge interest because of their much easier fabrication and potential applications in nanoelectronics as well as spintronics.

## 1.3 Schottky barriers in conventional MOSFETs

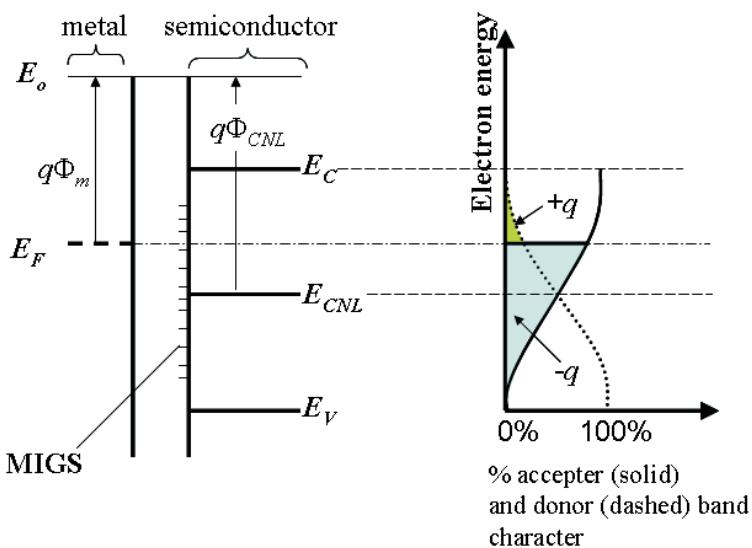

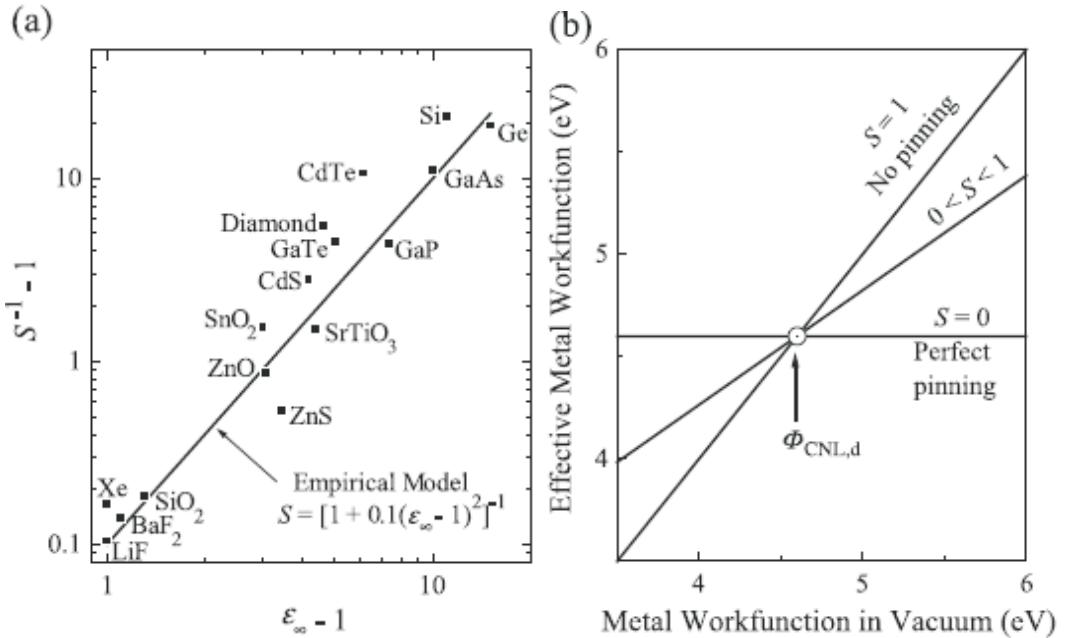

Metal-oxide-semiconductor field effect transistors (MOSFETs) have demonstrated a continuous pace in performance improvement over the past thirty years due to aggressive device scaling at the cost of more and more complex process engineering. As the scaling of the modern complementary MOSFETs continue, Si is approaching its fundamental scaling limits. To overcome this, Ge is proposed as an alternative channel material. This new material offers higher bulk carrier mobilities for both electron and hole than Si at low electric fields. Currently, one of the big challenges imposed by ultra-scaled Ge based devices is the formation of ultra shallow, highly doped source/drain regions, keeping the parasitic series resistances as low as possible. The Fermi-levels at any metal/Ge interfaces are pinned near the valence band edge of Ge. So, ohmic characteristics for p-Ge and Schottky characteristics for n-Ge are observed irrespective of metal work functions. This results in high parasitic resistance

in the source/drain of n-channel Ge MOSFETs. In order to reduce this parasitic resistance a mechanism of Fermi-level de-pinning at the metal/nGe interface would be required. Hence, an investigation and clear understanding of the Fermi-level pinning mechanism in metal/Ge Schottky barriers is of great importance.

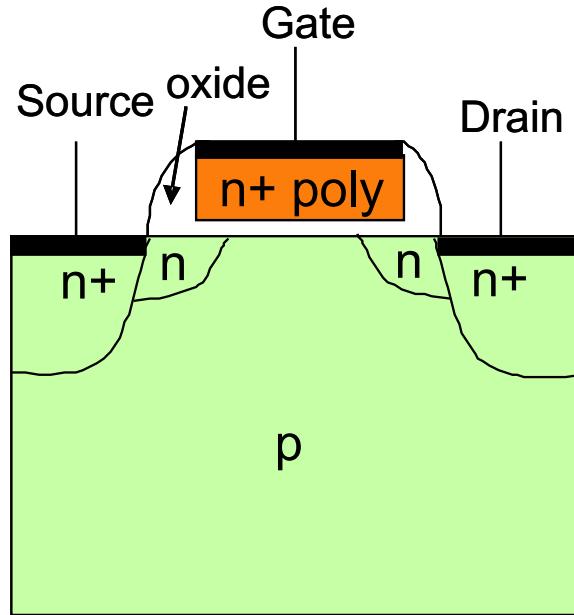

## 1.4 Schottky barriers as source/drain in MOSFETs

As discussed in the previous section, the continuing drive towards high integration is causing the semiconductor industry to consider significant scaling by device modifications and incorporation of new materials in order to improve transistor performance. New device structures are also being considered to replace the MOSFETs when conventional scaling fails. One such structure is the Schottky barrier MOSFET [2, 3] (SB-MOSFET). In this device, the problems associated with doping are completely eliminated by forming metallic silicide source and drain contacts. Unlike a doped source-drain architecture, the metallic silicide junctions form an atomically abrupt interface to the substrate and channel region, making the device scalable to the sub-10 nm regime with relative ease. The silicided junctions result in a low series resistance, provide an easy method to produce ultra-shallow junctions and overcome the solid solubility limitation associated with doping. The SB-MOSFET can realise complimentary operation by choosing a low work function metal for nMOSFET (electrons as majority carriers) and a high work function metal for pMOSFET (holes as majority carriers).

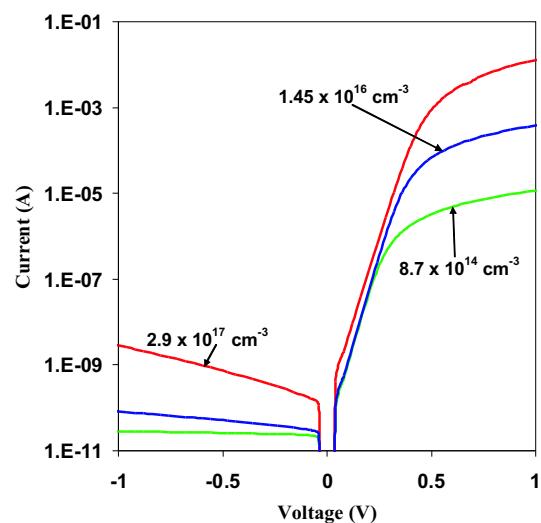

A SB-MOSFET imposes several challenges for obtaining high drive current and at the same time low off state leakage current for a given channel doping density. For a SB-MOSFET, it may be difficult to achieve high drive current due to the relatively high potential barrier between the source and the channel [4]. This problem may be overcome, or at least alleviated, by using a Ge substrate as opposed to Si because of the low Schottky barrier height of germanide/Ge contact and the higher carrier mobility of Ge. High drive current could also be achieved by reducing the doping density in the channel region increasing the channel mobility for a long channel MOSFET. Another challenge is to obtain high or nearly ideal electron barrier heights on nGe for the source drain of a pMOSFET by metal deposition and keeping the Fermi-

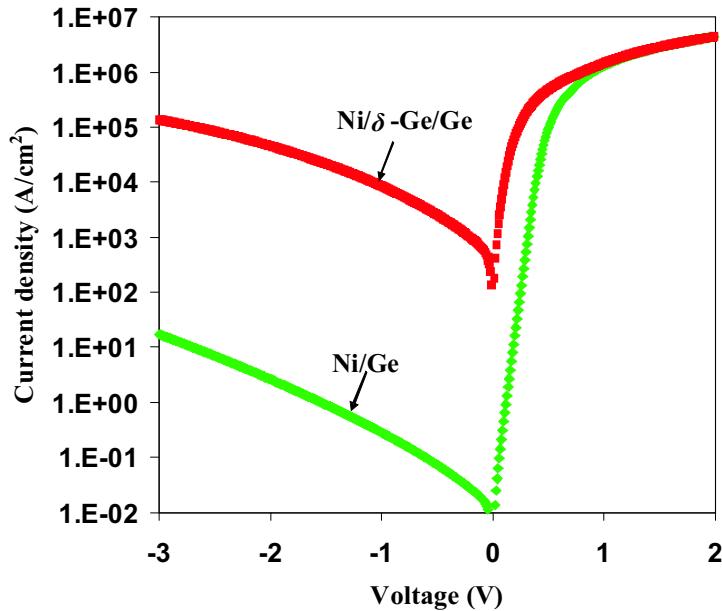

level pinning intact up to the annealing temperatures where germanidation results in the lowest specific resistance of the metal germanides. As Ge is a narrow band-gap semiconductor, Ge-based SB-MOSFET is badly affected by off-state leakage currents which result from tunnelling current through the Schottky barrier at the drain end, which is sensitive to barrier heights. To overcome this problem, electrodeposition of metals on semiconductor could be performed in order to obtain high Schottky barrier heights [5, 6] at the drain contact as opposed to those formed by physical vapour deposition. By using this technique, the junction leakage currents in an SB-MOSFET could be minimised.

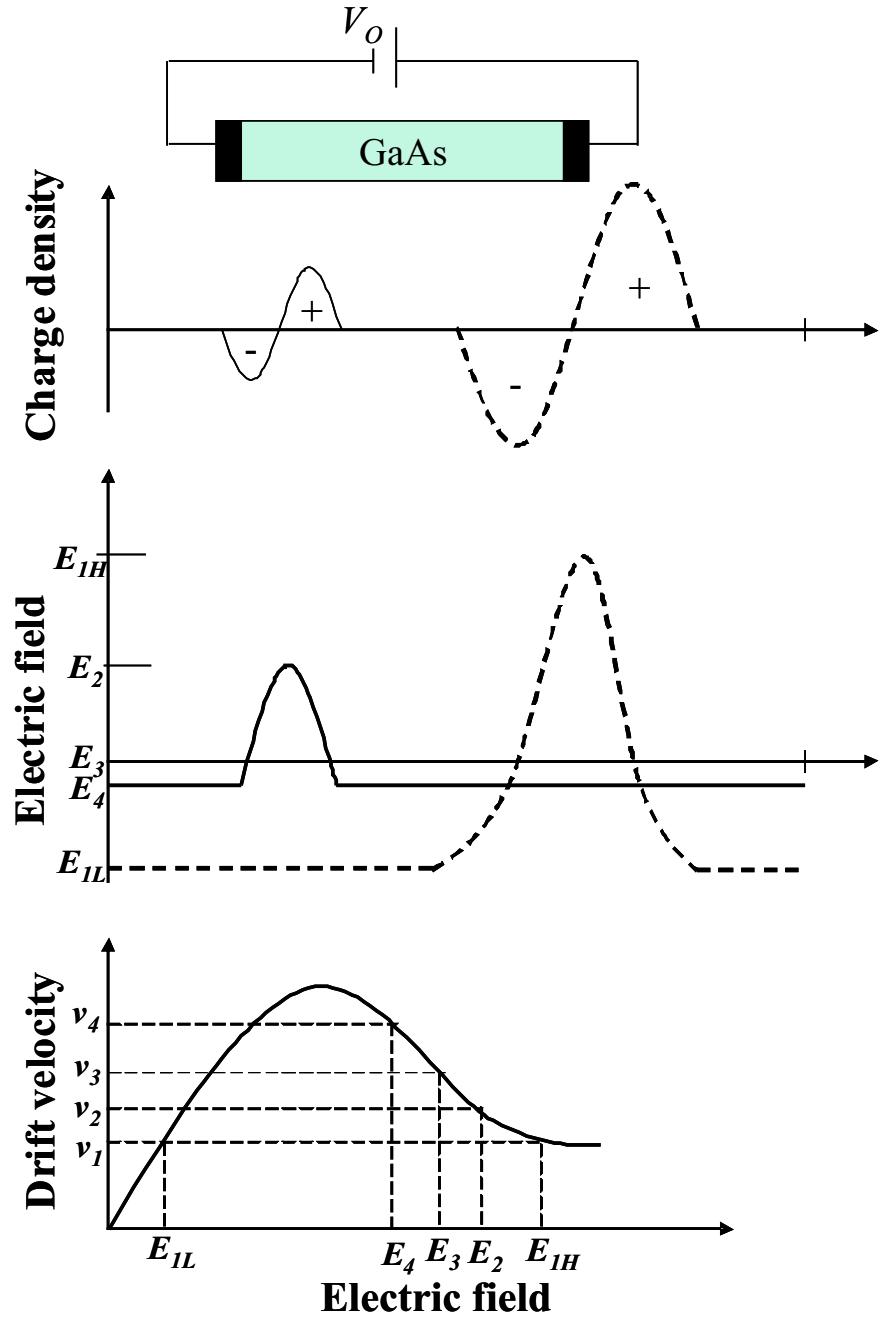

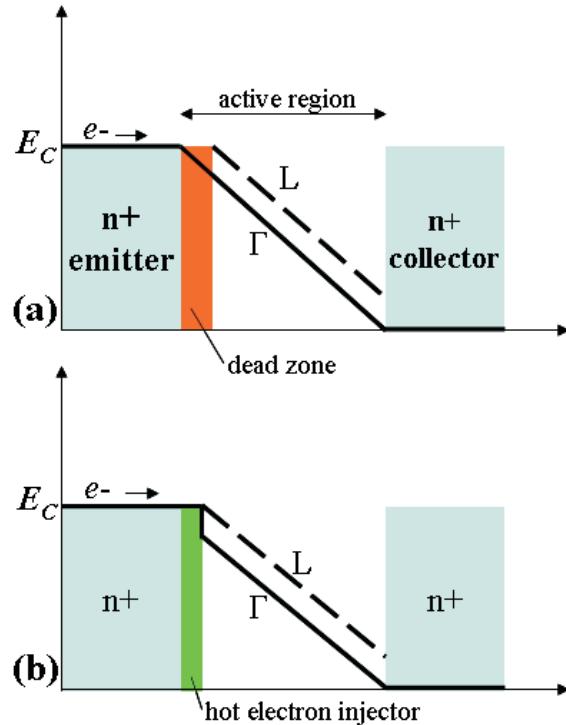

## 1.5 Schottky barriers in Gunn diodes

A Gunn diode, also known as a transferred-electron device, is a form of diode used in high-frequency electronics. The active area of a Gunn diode consists only of *n*-doped semiconductor material (e.g. GaAs, Ge, GaN and InP) with two electrical contacts on opposite ends. These semiconductors are characterised by having two valleys in their conduction bands with different mobility. When a proper bias is applied, inter valley electron transfer occurs and the diode exhibits negative differential resistance. Gunn diodes made of conventional III-V compound semiconductors (e.g. GaAs) have been successfully applied for generation of high-power millimeter-wave signals using oscillators based on the negative resistance effect. Injection limited cathode contacts of linearly-graded  $\text{Al}_x\text{Ga}_{1-x}\text{As}$  have been used to increase the efficiency of the Gunn devices. However, a simpler Schottky barrier contact has not been explored as a means of hot electron injection over the barrier, particularly because of the high barrier heights of most metals with GaAs. As an alternative, hot carrier injection by tunneling mechanism through the Schottky barriers could be explored. Electrodeposition method could be adopted to form a sharp metal/semiconductor interface on a highly doped semiconductor to enable hot electron tunneling. This may result in hot electron injection in a Gunn diode, which would benefit from a simpler fabrication of Schottky barrier contacts.

## 1.6 Schottky barriers in Spin transistors

The operation of a conventional MOSFET is dependent on the charge of electrons or holes. A spin transistor uses the angular momentum of an electron, called spin, apart from its charge. In the corresponding research area, Spintronics, a two-channel model is assumed for the possible states of spin-up and spin-down electrons, between which rarely occurs any interchange of states. Albert Fert and Peter Grunberg independently discovered the giant magnetoresistance (GMR) effect in 1988 [7,8] and won the 2007 Nobel Prize in physics for their work. GMR is the first effect directly related to spin dependent transport. The commercial success of the two-terminal all-metal GMR device as magnetic read heads and magnetic random access memory, resulted in an enormous interest in three terminal semiconductor based hybrid spin transistors [9–12].

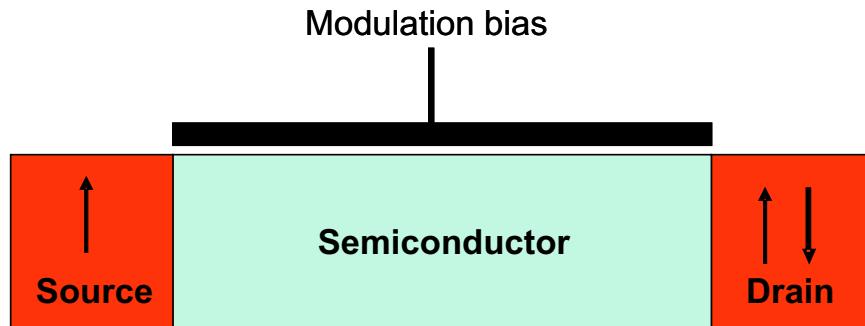

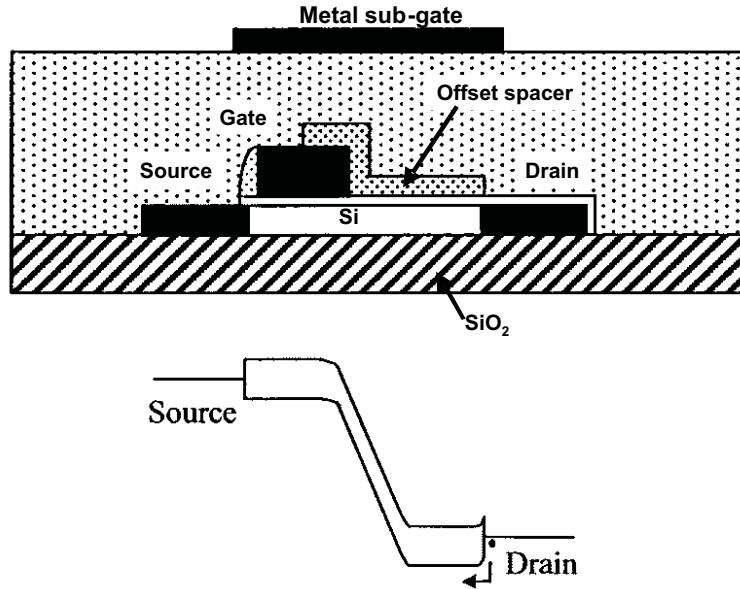

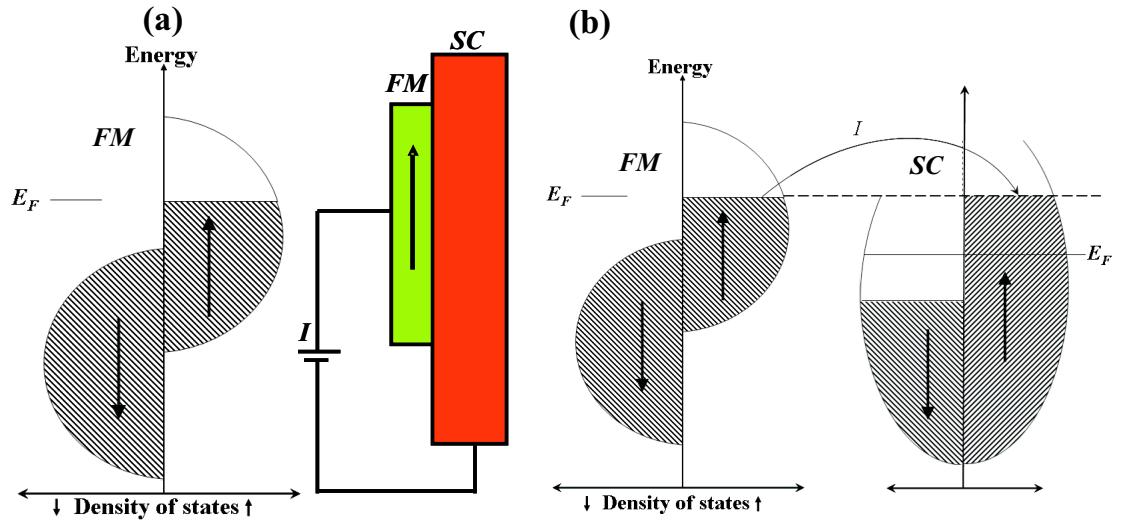

The first prototypical spin transistor scheme presented in Fig. 1.1 was proposed by S. Datta and B. Das [13] in 1990. A current passes through a ferromagnetic source and becomes spin polarised. This current is then injected into a semiconductor through a tunneling or a Schottky barrier contact. The current flow through the semiconductor is modulated using an external modulation bias. Finally the spin polarised current is collected at a second ferromagnetic drain contact.

Figure 1.1: An example of a spin transistor structure. The source and the drain are ferromagnets while the channel is a semiconductor. A spin-dependent modulation mechanism controls the spin current flow through the semiconductor.

The semiconductor based spin transistor is a very promising alternative to conventional transistors. The relative advantages of a spin transistor over a conventional transistor could be its operation at terahertz frequency, lower power, smaller size, larger scale of integration and lower cost. However, current gain is the property lack-

ing in the spin transistors developed so far and this has become the main obstacle for its integration with conventional electronic circuits. Semiconductor materials offer the possibility of new device functionalities, which are not realisable in metallic systems. For example, equilibrium carrier densities in semiconductors can be varied through a wide range by doping. Moreover, as the typical carrier densities in semiconductors are low compared to metals, electronic properties are easily tunable by gate potentials. A vast body of knowledge concerning semiconductor materials and processing already exists. Many of these processes have already been scaled up to commercial production lines. All these factors make semiconductors the natural choice for hybrid spintronics specifically for realising spin transistors.

For successful fabrication of a semiconductor spin transistor, the major challenge is the transfer of spin polarised carriers into a semiconductor such as Si or Ge. The main obstruction in this process is the conductivity mismatch problem which could be overcome by using a Schottky barrier contact of a ferromagnet with a semiconductor. Electrodeposition of a metal could be very useful as opposed to other deposition techniques since it produces very sharp interface with the semiconductor without intermixing. The second challenge followed by spin injection is obviously to detect the injected carriers in the semiconductor. A Schottky contact at the drain could be used for this detection. The spin polarised electrons results in a high magnetoresistance signal in the detection electrode when its magnetisation direction is opposite to that of the injection electrode. In this work, spin injection in Si will be electrically investigated using Schottky barriers at the injection and detection contacts.

## 1.7 Outline of this thesis

The thesis is organised as follows:

Chapter 2 discusses in detail the physics of Schottky barrier contacts and their characterisation techniques. An introduction to the metal electrodeposition technique is presented. Moreover, an introduction to the numerical simulation tool Sentaurus Device that has been used to simulate Schottky barriers and MOSFETs in this project is given.

Chapter 3 presents an investigation on the barrier inhomogeneity in Ni/Ge Schot-

tky barriers. The spatial variation of a Schottky barrier height is explained in light of modern theoretical models. The results help us understand the mechanism of Fermi-level pinning and its dominance in the source/drain formation and the solution to mitigate the effect in doped source/drain MOSFETs.

In Chapter 4, the theory of SB-MOSFETs is presented, emphasising the difference with the scaling limitations of the conventional MOSFETs. The experimental results of high-quality Ni/Ge Schottky barriers grown by electrodeposition is presented. The fabricated Schottky barriers show excellent rectification with very low leakage current. By numerical simulation it is shown that such high quality contacts could be used in SB-MOSFETs to suppress subthreshold leakage currents.

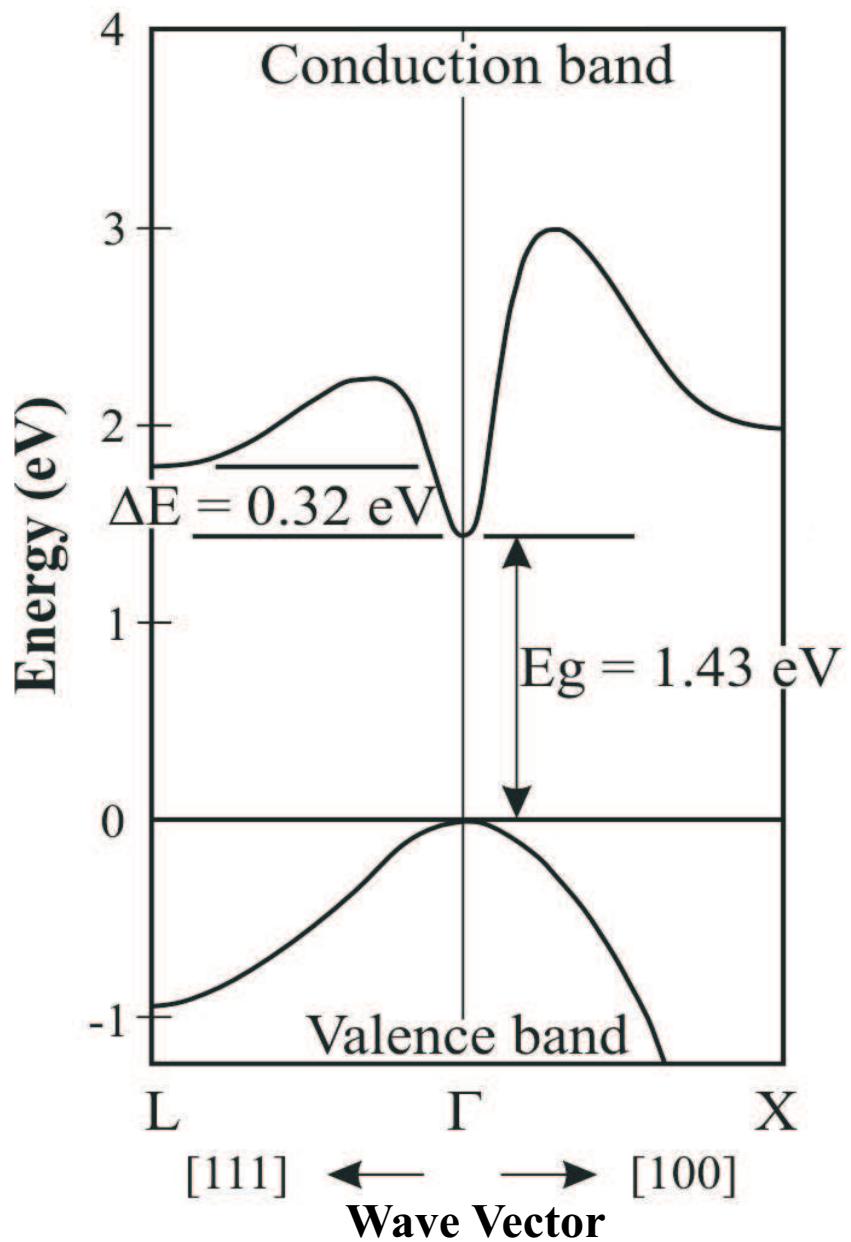

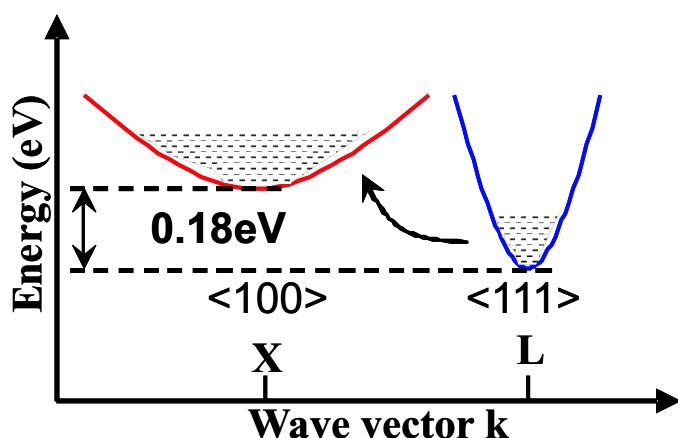

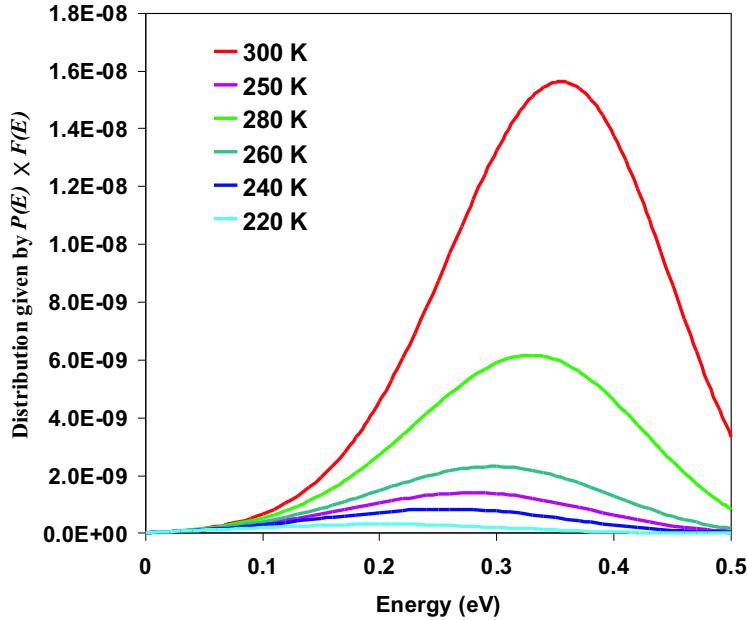

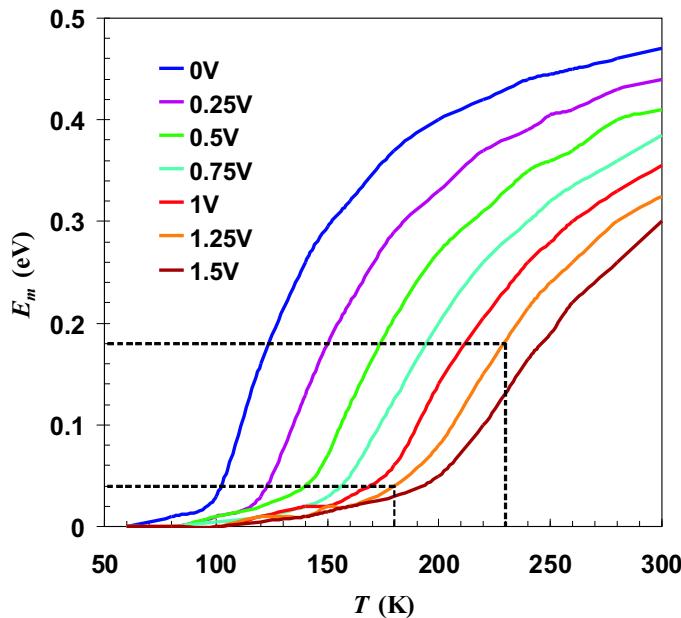

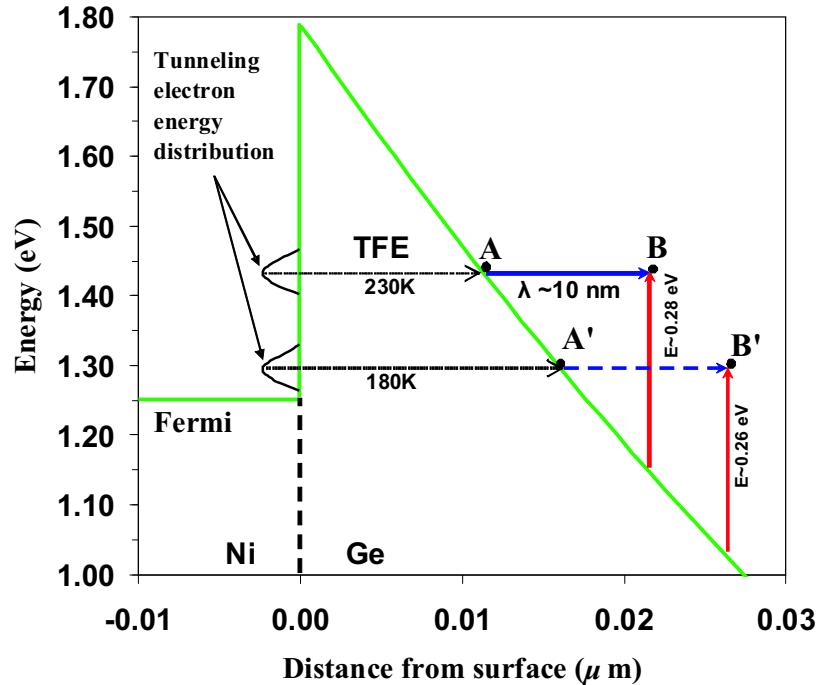

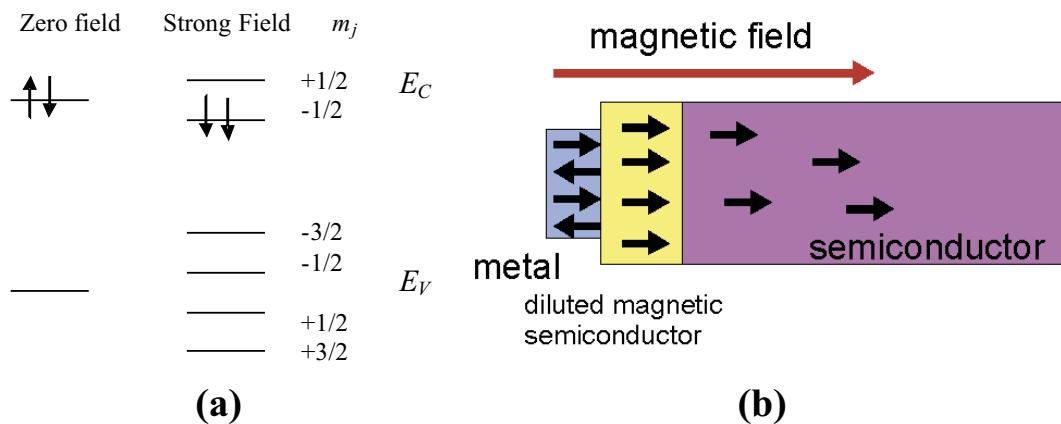

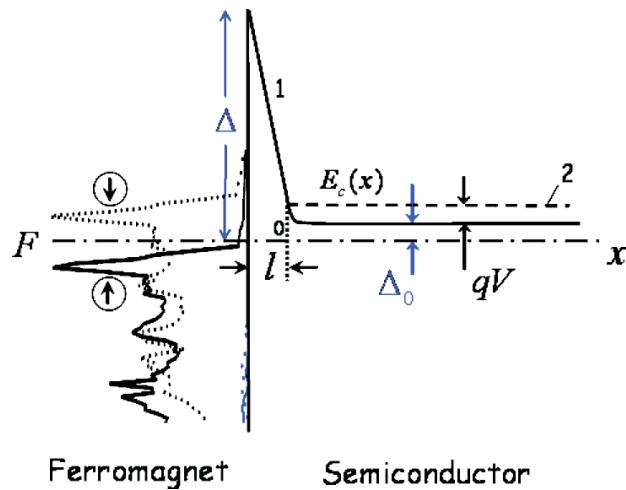

In Chapter 5, the experimental observation of negative differential conductance in a Ni/Ge Schottky barrier is reported. With the aid of theoretical models and numerical simulation it is shown that, at reverse bias, electrons tunnel into the high electric field of the depletion region of the Ni/Ge Schottky barrier. This scatters the electrons into the upper valley of the Ge conduction band, which has a lower mobility. The observed effect is hence attributed to the transferred electron effect, typical in a semiconductors with two-valley conduction bands, eg. in GaAs and InP.

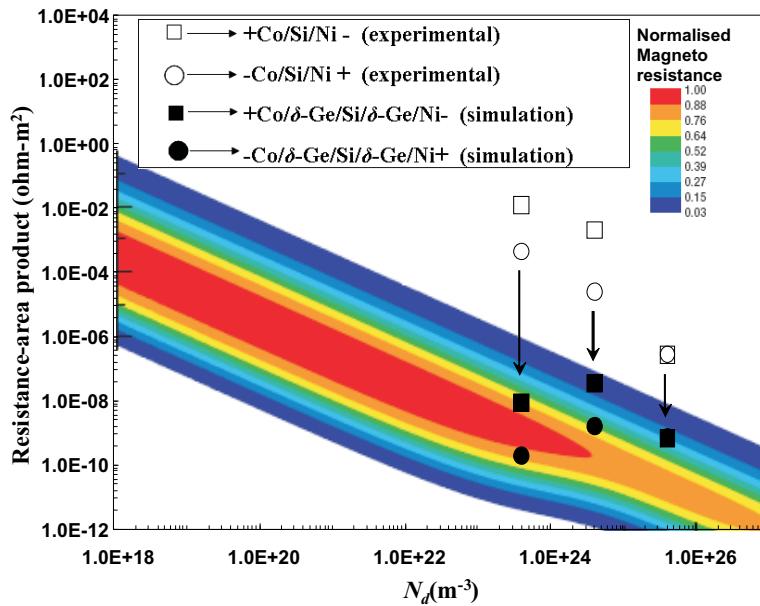

In Chapter 6 an overview of various fundamental principles underpinning electrical spin injection to semiconductors is presented. Electrical spin polarised carrier injection and extraction in Si has been investigated using a Co/Si/Ni vertical structure built on Si membrane. Electrical characteristic measurements performed on the devices at low temperatures show evidence of the conduction being dominated by tunneling. The devices, however, did not show any magnetoresistance signal even at low temperatures. Numerical simulations are performed to identify the possible reason hampering the spin injection. Investigation shows that the resistance-area product at the spin injection contacts hampers spin polarised carrier injection. This could be overcome by growing a thin highly doped Ge layer at the Schottky junctions, which tunes the resistance-area products to obtain spin injection in Si.

# Chapter 2

## Schottky barriers

*In this chapter the background on a metal/semiconductor Shottky barrier contact, its formation, current transport mechanisms are presented. A brief introduction to the Fermi-level pinning mechanism is given. Various experimental methods for extracting Shottky barrier parameters are discussed. As a fabrication technique of metal/semiconductor Shottky barrier, electrochemical deposition technique is briefly introduced. An introduction to the numerical simulation tool Sentaurus Device that has been used to simulate the Ni/Ge Shottky barriers in this project is given.*

### 2.1 Introduction

Metal/semiconductor contacts are of great importance since they are present almost in every semiconductor device. They can behave either as an Shottky barrier or as an ohmic contact depending on the characteristics of the interface. The difficulties associated with the scaling of conventional doped source/drain MOSFETs could be overcome by using a Schottky source/drain. In the following sections the background on the metal/semiconductor Shottky barrier is presented.

## 2.2 Formation and operational principles of a Schottky barrier

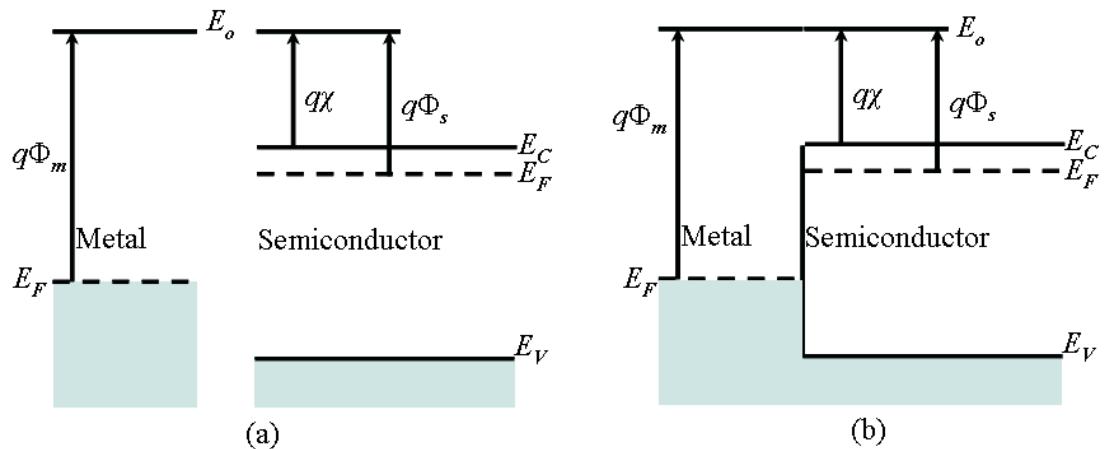

The energy band diagram of a metal and an n-type semiconductor aligned using the same vacuum level ( $E_o$ ) is shown in Fig. 2.1a. As the metal and semiconductor are brought together, the Fermi energies of the metal and the semiconductor do not change immediately. This yields the flat-band diagram of Fig. 2.1b, which is not at thermal equilibrium, since the Fermi energy in the metal is lower than that in the semiconductor. The energy of the electrons in the semiconductor is lowered by diffusion of electrons into the metal.

Figure 2.1: Energy band diagram of a metal and a semiconductor (a) before and (b) immediately after a contact is made. Here  $q$ ,  $\Phi_m$ ,  $\Phi_s$  and  $\chi$ ,  $E_o$ ,  $E_C$ ,  $E_V$ ,  $E_F$  are the electronic charge, the metal work function, the semiconductor work function, the semiconductor electron affinity, the vacuum energy level, the conduction band energy, the valence band energy, and the Fermi-level, respectively.

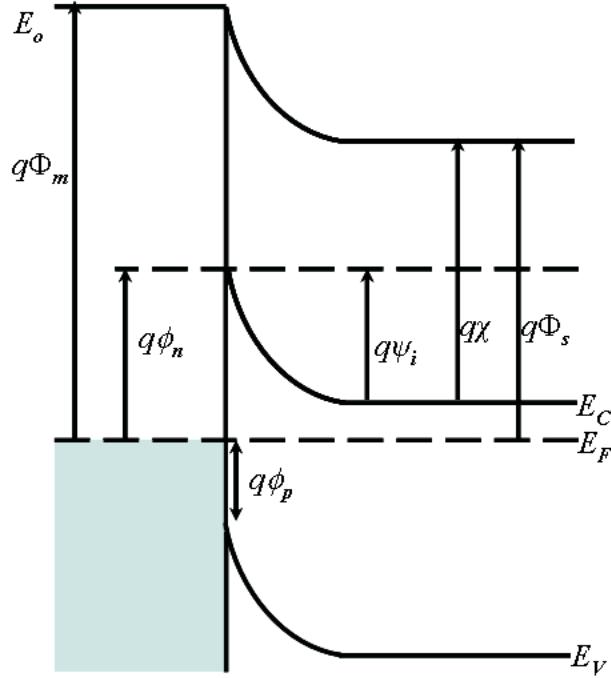

As the electrons leave the semiconductor, a positive charge, due to the ionised donor atoms, stays behind forming the depletion region. This charge creates a negative field and lowers the band edges of the semiconductor. Electrons flow into the metal until equilibrium is reached between the diffusion of electrons from the semiconductor into the metal and the drift of electrons caused by the field created by the ionised impurity atoms. The corresponding band diagram is shown in Fig. 2.2. This equilibrium is characterised by a constant Fermi energy throughout the structure.

The margin of the metal work function  $\Phi_m$  and semiconductor electron affinity  $\chi$

Figure 2.2: Energy band diagram of a metal-semiconductor contact in thermal equilibrium. Here,  $\phi_n$ ,  $\phi_p$  and  $\psi_i$  are the electron barrier height, the hole barrier height and the built-in potential, respectively.

is defined as the electron barrier height  $\phi_n$  given by:

$$\phi_n = \Phi_m - \chi \quad (2.1)$$

If  $E_g$  is the bandgap of the semiconductor then the hole barrier height  $\phi_p$  is given by:

$$\phi_p = \frac{E_g}{q} + \chi - \Phi_m \quad (2.2)$$

where  $q$  is the electronic charge and  $E_g$  is given by

$$E_g = q(\phi_p + \phi_n) \quad (2.3)$$

The built-in potential  $\psi_i$  is defined as the difference between the Fermi energy of the metal and that of the semiconductor:

$$\psi_i = \Phi_m - \chi - \frac{E_C - E_F}{q} \quad (2.4)$$

Experimentally it has been found that equation 2.1 does not correctly predict the barrier height.  $\phi_n$  is strongly influenced by the Fermi-level pinning effect, which is

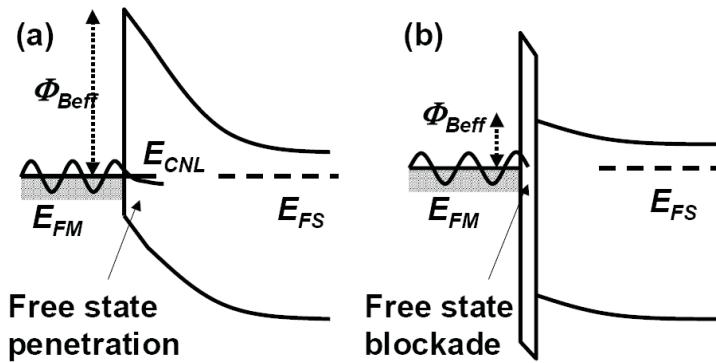

mainly caused by intrinsic interface states at the semiconductor boundary. Dangling bonds and the species of chemicals adsorbed on the surface of semiconductors give rise to surface states modelled by Bardeen [14]. These states introduce energy levels that are within the energy gap of the host crystal, creating acceptor or donor type surface traps. These states can have a very high density and a narrow distribution of energies within the band-gap. Electrons from the conduction band may be trapped in these surface states. These states typically are sufficiently dense that in equilibrium the Fermi-level falls within them at the surface. As a result, the barrier height is determined by the property of the semiconductor surface and is independent of the metal work function. Moreover, Heine [15] pointed out that localised surface states cannot exist in the semiconductor when it is contacting the metal, but resonance surface states, which are tails of the metal wave functions can exist. The length of this tail can be about a few lattice constant. The gap states tend to lead towards a matching of some neutrality level lying in the gap in each semiconductor. The mechanism of the Fermi-level pinning by this model will be presented in Chapter 3.

The current transport in a Schottky barrier under various bias conditions could be due to the carrier transport over the barrier and through the barrier. In addition there are two more mechanisms such as recombination in the space-charge region and recombination in the neutral region. The overall current can be approximately modelled by a combination of the thermionic emission current and the tunnelling current for semiconductors with a high mobility and low density of defect states because in this case the current from electron-hole recombination and hole injection can be neglected.

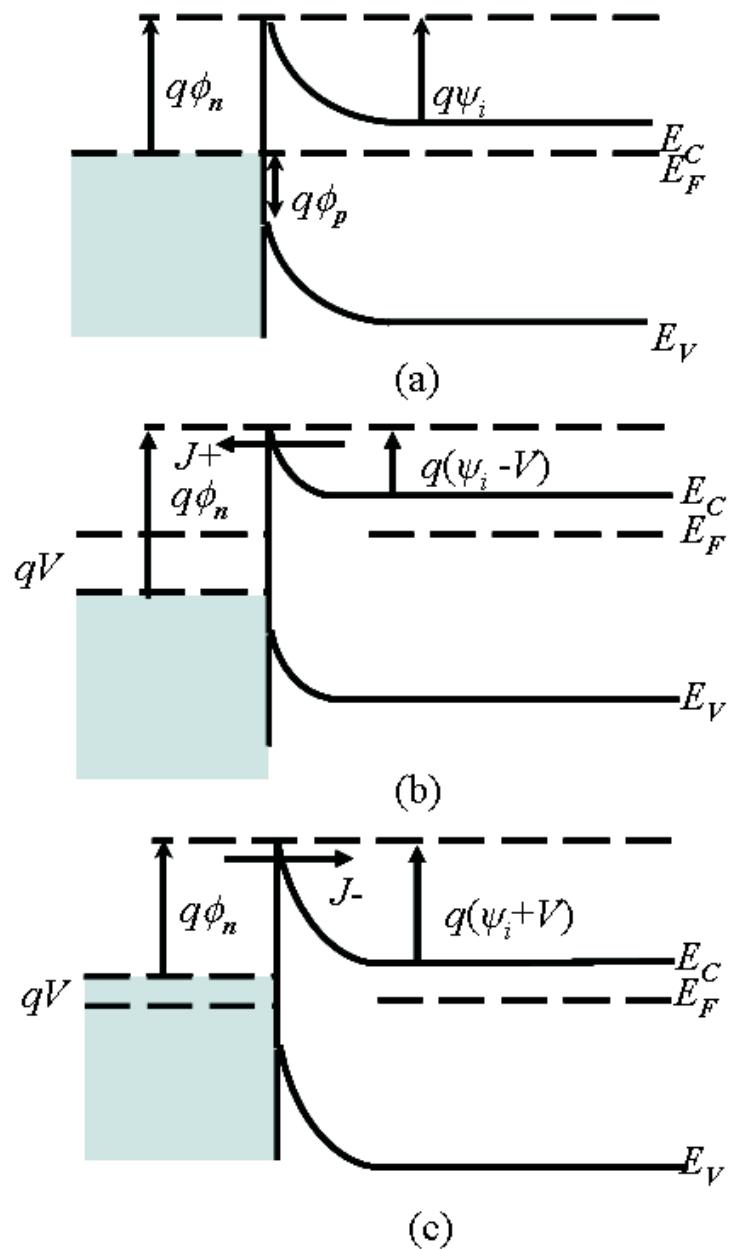

### 2.2.1 Thermionic emission for Schottky characterisation

Ideal Schottky barriers exhibit rectifying behaviour due to carrier emission over the top of the barrier at room temperature. This is known as the thermionic emission (TE) mechanism, which is presented schematically in Fig. 2.3. Only the carriers with energies larger than  $q\phi_n$  can overcome the Schottky barrier presented in Fig. 2.3a and contribute to the transport from the metal to the semiconductor or vice versa. Under forward bias condition as shown in Fig. 2.3b, a positive bias is applied to the metal. The semiconductor remains at the same potential but the metal Fermi-level is

Figure 2.3: A schematic representation of thermionic emission current transport in a Schottky barrier: (a) Equilibrium band diagram without a bias. (b) Band diagram of a forward-biased Schottky barrier when a positive bias  $V$  is applied to the metal. Here  $J+$  is the current density from the semiconductor to the metal. (c) Band diagram of a reverse-biased Schottky barrier when a negative bias  $V$  is applied to the metal.  $J-$  is the current density from the metal to the semiconductor.

shifted to lower energies due to the applied voltage and this in turn leads to a lowering of the barrier potential. Hence, the current density  $J_+$  from the semiconductor to the metal increases significantly. At the same time, the electron current density  $J_-$  from the metal to the semiconductor remains very small because of a high and almost constant barrier between the metal and the semiconductor. Similarly, under reverse bias condition as shown in Fig. 2.3c, a negative bias is applied to the metal.  $J_+$  is significantly decreased because the barrier potential is increased. Since  $J_-$  is almost voltage independent, therefore, the total current for forward and reverse bias is different. The current density ( $J$ ) of a homogeneous Schottky barrier is given by [1]:

$$J(V) = J_S(e^{\frac{qV}{\eta kT}} - 1) \quad (2.5)$$

where the saturation current density,  $J_S$  is defined as

$$J_S = A^*T^2(e^{-\frac{q\phi_n}{kT}}) \quad (2.6)$$

where  $V$  is the applied voltage,  $q$  is the electron charge,  $k$  is the Boltzmann constant,  $T$  is the absolute temperature,  $A^*$  is the Richardson constant,  $\eta$  is the ideality factor and  $\phi_n$  is the electron Schottky barrier height.

Assuming the TE mechanism as the current transport mechanism across a homogeneous Schottky barrier, current  $I$  can be expressed as a function of the applied bias  $V$  by

$$I = I_S(e^{\frac{qV}{\eta kT}} - 1) \quad (2.7)$$

where the saturation current  $I_S$ , according to equation 2.6, is given by

$$I_S = A A^* T^2 (e^{-\frac{q\phi_n}{kT}}) \quad (2.8)$$

where  $A$  is the active contact area in  $\text{cm}^2$ . If the applied bias  $V$  is much greater than  $3kT/q$  then the exponential part of equation 2.7 dominates and the equation reduces to

$$I = I_S e^{\frac{qV}{\eta kT}} \quad (2.9)$$

$$\ln I = \ln I_S + \frac{q}{\eta kT} V \quad (2.10)$$

The intercept of the straight line equation gives the value of  $\ln I_S$  when  $\ln I$  is plotted in log axis as a function of  $V$  for the values of  $V \gg \frac{3kT}{q}$ . The ideality factor  $\eta$  can be

calculated from the slope of the equation as

$$\eta = \frac{q}{kT} \frac{dV}{d(\ln I)} V \quad (2.11)$$

Then the barrier height of the Schottky diode can be worked out by

$$\phi_n = -\frac{\ln(I_S/AA^*T^2)kT}{q} \quad (2.12)$$

Moreover the slope of the linear part of the forward  $I$ - $V$  characteristics of the Schottky barrier gives the series resistance of the diode.

The height of a Schottky barrier can also be determined by the capacitance ( $C$ ) measurement. When a small AC voltage is superimposed upon a DC bias, charges of one sign are induced on the metal surface and charges of the opposite sign in the semiconductor. The relation between capacitance  $C$  and voltage  $V$  for a Schottky barrier formed by a metal and n-type semiconductor is given by [1]:

$$C = \sqrt{\frac{q\epsilon_s N_d}{2(\psi_i - V - \frac{kT}{q})}} \quad (2.13)$$

where  $\epsilon_s$  and  $N_d$  are the permittivity and the doping density of the semiconductor, respectively. From equation 2.13 the doping concentration as a function of the gradient of the inverse square capacitance per unit area can be worked out as:

$$N_d = \frac{2}{q\epsilon_s} \left( -\frac{dC^{-2}}{dV} \right)^{-1} \quad (2.14)$$

If  $N_d$  is constant the plot of  $C^{-2}$  gives a straight line and from the gradient of this line the doping density of the semiconductor is obtained. The height of the Schottky barrier is given from the intercept  $V_i$  of the extension of the straight line with the voltage axis as [1]:

$$\phi_n = V_i + V_n + \frac{kT}{q} \quad (2.15)$$

where  $V_n$  is the depth of the Fermi-level below the conduction band.

The third technique of a Schottky barrier height determination is the activation energy measurement that requires no assumption of electrically active area. By multiplying equation 2.5 by  $A$ , the electrically active area, we get

$$\ln\left(\frac{I}{T^2}\right) = \ln(AA^*) - \frac{q(\phi_n - V)}{kT} \quad (2.16)$$

where  $q(\phi_n - V)$  is the activation energy. Over a limited range of temperature, the value of  $A^*$  and  $\phi_n$  are temperature independent [1]. Therefore, for a given forward bias  $V$ , the slope of a plot of  $\ln(\frac{I}{T^2})$  versus  $1/T$  yields the barrier height  $\phi_n$ , and the ordinate intercept at  $1/T=0$  yields the product of  $A$  and  $A^*$ .

The application of an electric field in a Schottky barrier causes the image force lowering of the potential energy for charge carrier emission. Consider an electron in vacuum, at a distance  $x$  from a metal surface. A positive charge will be induced on the metal surface and will give rise to an attractive force between the two, known as the image force. The force of attraction between the electron and the induced positive charge is equivalent to the force that would exist between the electron and an equal positive charge located at  $-x$ . This positive charge is referred to as an image charge. When an external field is applied these two energy components together have the effect of lowering the barrier height. At high fields, the height of a Schottky barrier is considerably lowered by an amount given by:

$$\Delta\phi = \sqrt{\frac{q\mathcal{E}}{4\pi\epsilon_s}} \quad (2.17)$$

where  $\mathcal{E}$  is the applied electric field.

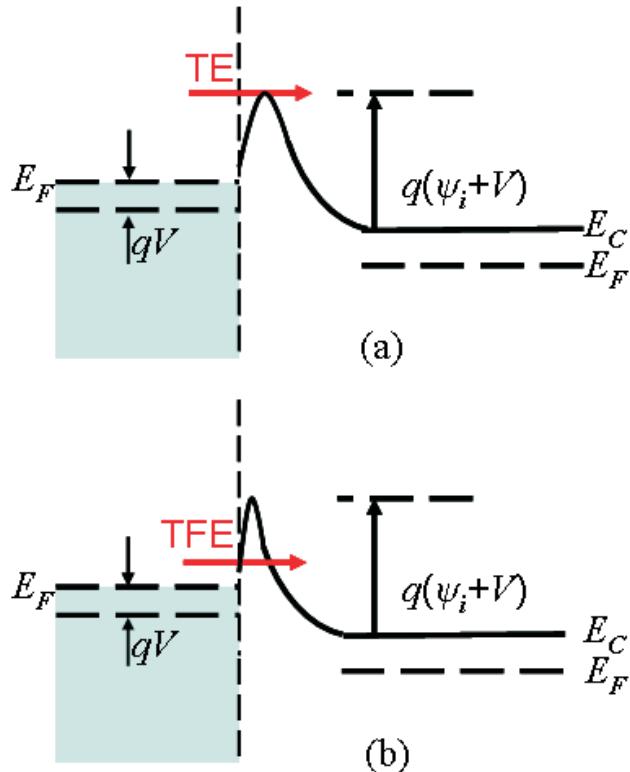

### 2.2.2 Field emission and thermionic field emission

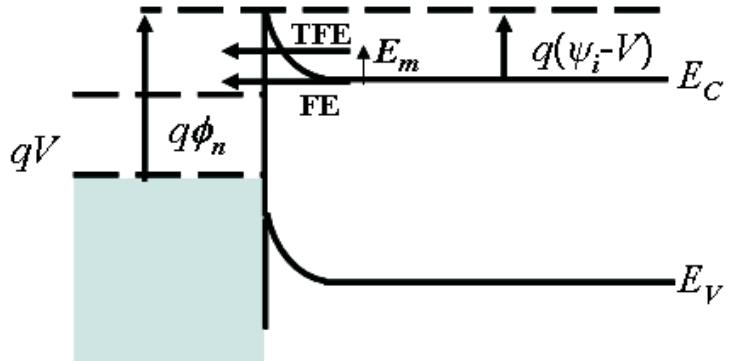

Under certain circumstances it may be possible for electrons with energies below the top of the barrier to penetrate the barrier by quantum mechanical tunneling. In the case of a very heavily doped (degenerate) semiconductor at low temperature, the current in the forward bias (same for reverse bias) arises from the tunneling of electrons with energies close to the Fermi energy in the semiconductor. This is known as field emission (FE) and is schematically shown in Fig. 2.4. If the temperature is raised, electrons are excited to higher energies and the tunneling probability increases very rapidly as the barrier to them gets thinner and lower. On the other hand, the number of excited electrons decreases very rapidly with increasing energy, and there will be a maximum contribution to the current from electrons which have an energy  $E_m$  above the bottom of the conduction band. This is known as thermionic field emission (TFE) and is presented schematically in a forward biased Schottky barrier in Fig. 2.4.

Figure 2.4: A schematic representation of a Schottky barrier energy band diagram indicating the different energies for FE and TFE under forward bias. Here TFE occurs at an energy  $E_m$  above the bottom of the conduction band.

## 2.3 Schottky barrier fabrication by electrodeposition

Electrodeposition is the material deposition technique used in this project to deposit Ni on Ge. Kiziroglou *et al.* [6] compared the transport characteristics of evaporated Ni/Si Schottky barriers with that of the electrodeposited Ni/Si Schottky barriers of the same structure and observed that the latter exhibits higher quality rectifying behaviour than the former. The poor quality rectifying of the evaporated Schottky barrier was attributed to the formation of an interfacial layer at the Ni/Si interface due to the intermixing of the high energy Ni atoms with Si during evaporation. This interfacial layer lowers the Schottky barrier height resulting in the increase of the reverse current density. Therefore, in order to obtain high quality Schottky barrier on Ge, Ni was electrodeposited. This method is attractive since it is very simple, quick and cost effective and does not require any vacuum chamber unlike the conventional material deposition techniques, eg. evaporation and sputtering. However, the method requires a conductive substrate and the lack of it results in poor nucleation, adhesion of the metal film on semiconductor. However, in this work it was found that even low doping in Ge is sufficiently conductive to allow electrodeposition.

### 2.3.1 Electrodeposition principle

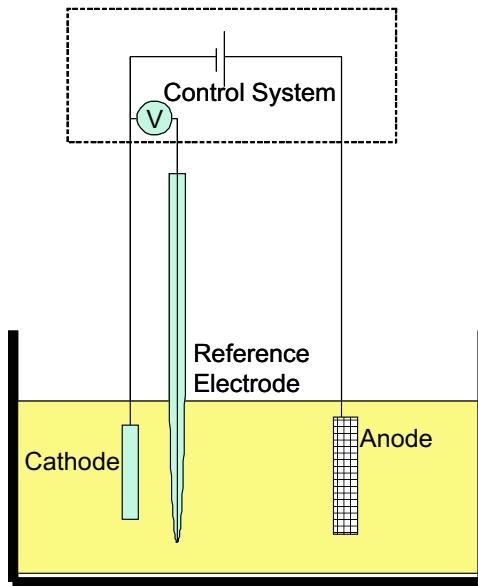

Electrodeposition, also known as electroplating, occurs in an electrochemical cell containing metal ions in a solution, a cathode or substrate upon which the metal is deposited, a reference electrode and an anode or counter electrode as shown schematically in Fig. 2.5. An electric field applied across the two electrodes provides a driving force for the ions to move. The positive metal ions move to the electrode called the cathode, where they gain electrons thereby undergoing reduction to atoms which deposit onto the cathode. A typical electrodeposition reaction for a metal  $M$  having a valency  $z$ , is given by [16]:

Figure 2.5: A schematic representation of a three electrode electrodeposition setup consisting of the cathode, the anode, and the reference electrode immersed in a solution containing metal ions.

The nature of the deposit is determined by many factors including the electrolyte composition, its pH, the substrate, the potential applied between electrodes and the current density. When an electrode is immersed in an electrochemical solution and no current is flowing through it the surface charges which build up at equilibrium lead to the formation of a potential difference between the metal electrode and the solution. This potential is called the equilibrium potential  $E_{eq}$ , which depends on

the material of the electrode and the activity of the metal salt in the electrolyte solution. If an external voltage is applied to the system, a current will flow and the voltage drop  $E(I)$  across the electrochemical system will in general be different from the equilibrium potential  $E_{eq}$ . The difference in these potentials is known as the overpotential  $\zeta$  given by:

$$\zeta = E(I) - E_{eq} \quad (2.19)$$

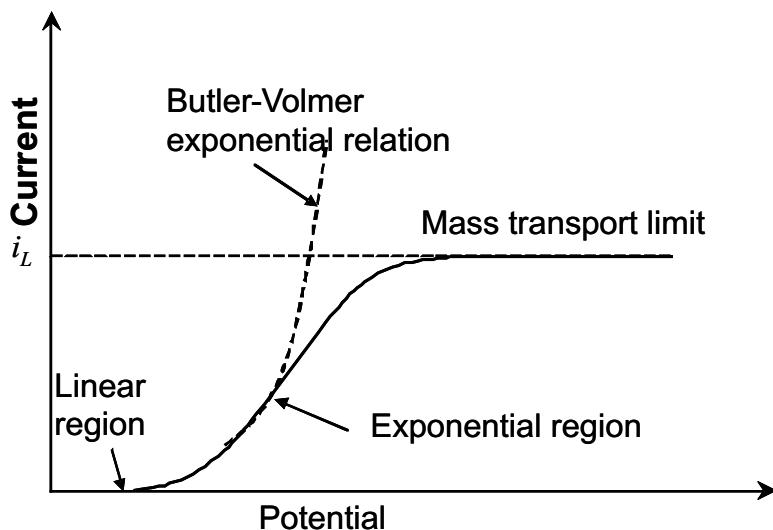

If the overpotential is negative and large, then the current-potential relationship during electrodeposition is given by the Butler-Volmer equation:

$$i = i_o \exp \frac{-\alpha z N_A q \zeta}{R_g T} \quad (2.20)$$

where  $i_o$  is termed as the exchange current density ( $i_o = i$  when  $\zeta = 0$ ),  $\alpha$  the transfer coefficient,  $N_A$  Avogadro's Number and  $R_g$  the Gas Constant. In reality, this exponential current variation cannot hold for high values of overpotential as the current density is limited by the mass transport of metal ions from the solution to the electrode. The value of the limited current is given by:

$$i_L = \frac{n_e N_A q D}{\delta} C_b \quad (2.21)$$

where  $D$  is the diffusion constant for the particular metal ions,  $C_b$  is the bulk concentrations of the metal ion in the solution,  $\delta$  is the thickness of the diffusion layer and  $n_e$  is the number of electrons involved in the reaction. Therefore, the current varies exponentially for a certain range of overpotential, but it saturates at the mass transport limit at high overpotential as shown in Fig. 2.6. With increasing potential the current increases linearly until the equilibrium potential of the metal is reached. Then the current increases exponentially while metal deposition is taking place. Finally the current saturates when it is limited by the total mass transport ability of the solution and the electrode. The rate of the metal deposited will vary with the current density due to the difference in the number of available electrons.

In a three electrode electrodeposition setup, the purpose of the anode/counter electrode is to supply the current required by the working electrode without limiting the measured response of the cell. The role of the reference electrode is to provide a fixed potential which does not vary during the experiments. During the deposition

Figure 2.6: Current voltage variation during electrodeposition.

process a potential difference arises at the metal and the solution interface as a result of charging. This potential of the cathode is measured against the reference electrode potential. The potential between the cathode and the reference electrode is controlled by a potentiostat, and as the reference cell is maintained at a fixed potential, any change in applied potential to the cell appears directly across the interface between the cathode and solution. The reference electrode serves dual purposes of providing a thermodynamic reference and also isolating the cathode from the system. In practice, however, any measuring device must draw a current to perform the measurement. Thus, a good reference electrode should be able to maintain a constant potential even if a few microamperes are passed through its surface. In this work, a saturated calomel electrode, consisting of mercury, calomel and KCl has been used as a reference electrode.

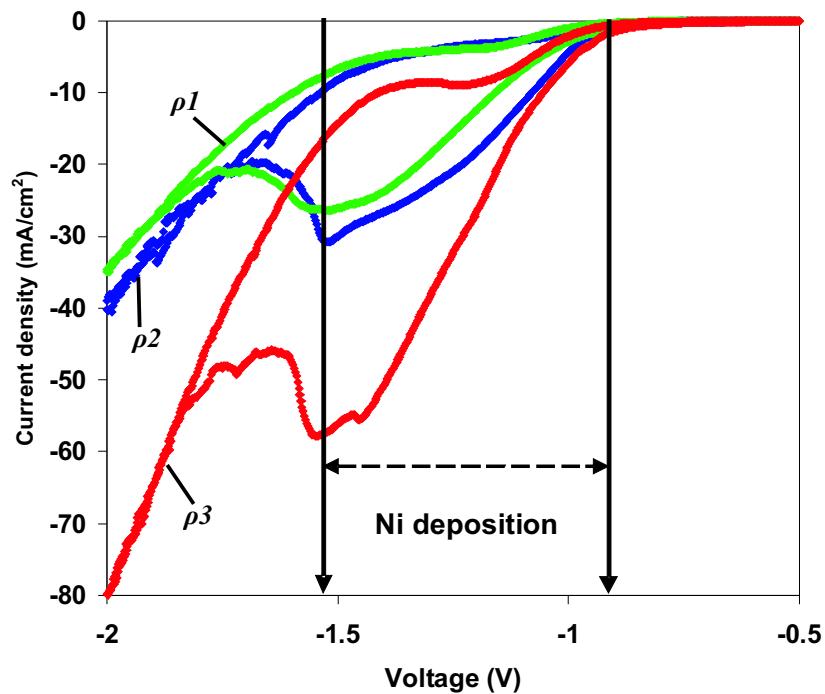

There are two different methods of electrodeposition depending on how the current or voltage is applied: the constant voltage method (current is measured during the deposition); and the constant current method (voltage is measured during the deposition). In addition, cyclic voltammetry is used in order to optimise the various electrodeposition methods by investigating the nucleation of the deposited films. In this technique an applied voltage is ramped from low to high and then back to low when the current is being measured. The optimum deposition potential is then de-

terminated from the cyclic voltammetry characteristic. Finally a constant deposition potential is maintained, during the metal deposition process, in which the actual film is deposited.

### 2.3.2 Film thickness control

The reduction of the metal has been generalised as Equation 2.18 for a single metallic ion. Therefore, to reduce one mole of a given metal  $z$  moles of electrons are required. The total cathodic charge used in the deposition  $Q$ , is the product of the gram-moles  $M$  of the metal deposited, the valency  $z$ , Avogadro's Number  $N_A$ , and the electronic charge  $q$ . Thus, the following equation gives the charge required to reduce  $M$  mole of metal:

$$Q = MzN_Aq \quad (2.22)$$

The number of moles of metal reduced by charge  $Q$  is:

$$M = \frac{Q}{zN_Aq} \quad (2.23)$$

In the electrodeposition process, two or more reactions may occur simultaneously at an electrode and the amount of total charge passed corresponds to the sum of the charges of all reactions. The current efficiency ( $\alpha$ ) for one of the simultaneous reaction (metal reduction in our case) is defined as the charge required for that reaction  $Q_M$  divided by the total amount of charge  $Q_T$  for all reactions. Therefore equation 2.23 can be written as:

$$M = \frac{\alpha Q_T}{zN_Aq} \quad (2.24)$$

The total charge used in the metal deposition can be obtained as the product of the current  $I$  and the time of deposition  $t$ . The weight of the deposit  $w$  can be obtained by multiplying equation 2.24 with the atomic weight  $M_w$  of the deposited metal. Finally, to obtain the thickness  $T_{film}$  of the deposited metal film, the density of the metal  $D_M$  is used as:

$$D_M = \frac{w}{Vol_M} = \frac{w}{AT_{film}} \quad (2.25)$$

where  $Vol_M$  is the volume of the deposited metal,  $A$  is the area of the deposit. Using Equations 2.24 and 2.25 the general equation of the required charge for the deposition of a film with thickness  $T_{film}$  is found to be:

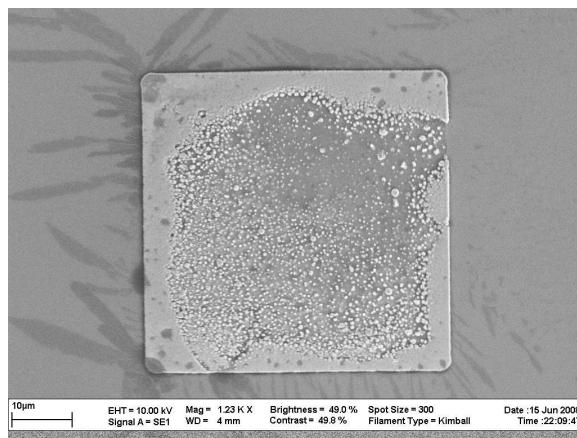

$$Q_T = \frac{zN_A q D_M A T_{film}}{\alpha M_w} \quad (2.26)$$

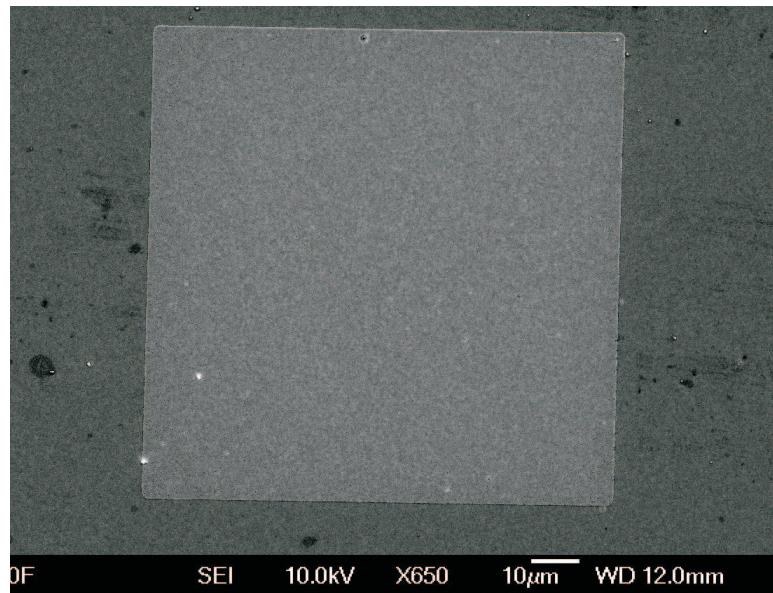

This charge can be monitored during electrodeposition by observing the current passed in a given time. The current efficiency  $\alpha$  could be estimated by measuring the film thickness by scanning electron microscope (SEM) after electrodeposition.

## 2.4 Device simulation framework

Device modeling of Ge-based Schottky barriers were performed for investigation of Ge channel SB-MOSFETs with dimensions in the sub-100 nm regime, i.e., channel lengths less than 100 nm and gate oxide layers as thin as 1 nm. Investigation of devices with various structures and materials, such as back-to-back Schottky barriers for electrical spin-injection experiment will be shown in Chapter 6. Fabrication of such devices would require complex lithographic techniques and sophisticated material growth processes resulting in very high cost. As a result of this high cost and the fabrication challenges, measurements on fabricated devices are not readily available for comparison with simulation results for this research study. However, this modeling study will provide useful insight into the factors limiting device performance and predict trends in device performance due to variations in device structure and design.

### 2.4.1 An introduction to the simulation tool

Numerical simulations of Ni/Ge Schottky barriers have been performed by a numerical simulator Sentaurus Device from SYNOPSYS Ltd. This tool is primarily designed for simulating the thermal, electrical, and optical characteristics of silicon devices, and is also capable of simulating other semiconductor materials such as Ge. A set of physical device equations that describe the carrier distribution and conduction mechanisms are used to compute terminal currents, voltages, and charges.

In the simulator, a real semiconductor device is represented as a virtual device whose properties are discretised onto a non-uniform grid or mesh. This is done by

the Sentaurus structure editor tool. A virtual device structure is then defined by two files. One is a grid file containing a description of the various regions within the device, i.e., boundaries, types of materials, location of electrical contacts, as well as the location of all the discrete nodes and their connectivity (the device mesh). The second is a data file containing the doping profiles of the device. Sentaurus device uses these files along with various transport equations and built-in physical models to describe the devices electrical characteristics, as well as the devices internal parameter variations and distributions, such as electrostatic potential, carrier concentrations, carrier mobilities, and carrier velocities.

The electrical terminal characteristics of the device are predicted by solving key semiconductor equations, including Poissons Equation and the electron and hole continuity equations, at the nodes within the device mesh. These equations are given below:

$$\text{Poisson's equation} : \nabla(\epsilon \nabla \psi) = -q(p - n + N_d^+ - N_a^-) \quad (2.27)$$

$$\text{Electron continuity equation} : \nabla J_n = qR_r + q \frac{\partial n}{\partial t} \quad (2.28)$$

$$\text{Hole continuity equation} : -\nabla J_p = -qR_r + q \frac{\partial p}{\partial t} \quad (2.29)$$

where  $\psi$  is the electrostatic potential,  $p$  and  $n$  are the hole and electron density,  $N_d^+$  and  $N_a^-$  are the ionised donor and acceptor concentrations,  $R_r$  is the recombination rate.  $J_n$  and  $J_p$  consists of the drift and the diffusion terms as given by:

$$\text{Electron drift - diffusion current} : J_n = q\mu_n n \nabla \psi + qD_n \nabla n \quad (2.30)$$

$$\text{Hole drift - diffusion current} : J_p = q\mu_p p \nabla \psi - qD_p \nabla p \quad (2.31)$$

where  $D_n$  and  $D_p$  are the diffusion constants,  $\mu_n$  and  $\mu_p$  are the electron and hole mobility respectively. The system unknowns are  $\psi$ ,  $n$  and  $p$ . The Sentaurus device tool integrates the equations over a test volume, applying the Gaussian theorem, and discretising the resulting terms to a first-order approximation to obtain a solution.

The accuracy of the simulation arises from its accurate description of the physics of device operation. Numerical simulations utilising the many tools provided by the Sentaurus software were performed in order to obtain a realistic description of the Schottky diodes behaviour. Therefore, the device characteristics presented in this thesis are reasonable predictions of what can be expected in fabricated structures.

### 2.4.2 Simulation models

One of the major advantages of Sentaurus Device is the ability to selectively include specific numerical model functions such as mobility, tunneling effects, bandgap narrowing, etc. In order to obtain an accurate description of the carrier mobilities in the MOSFETs modeled in the simulation study, a physical model is used to describe their affect on the carrier mobilities.

A large variety of models have been developed, which describe mobility dependency on material properties and operating conditions. The mobility models that were used in the simulations of MOSFETs are discussed. Different mobility contributions can be combined according to Mathiessen's rule:

$$\frac{1}{\mu} = \sum_{n_t} \frac{1}{\mu_{n_t}} \quad (2.32)$$

where  $\mu$  is the carrier mobility,  $n_t$  is the number of different mobility mechanisms. In this section the mobility models are reported that have been used in device simulations in this thesis. The reader is referred to Ref. [17] for a detailed explanation of model parameters.

In doped semiconductors, a degradation of the carrier mobility is experienced due to scattering of the carriers by charged impurity ions. The Arora [18] model is used to describe the mobility dependence on the impurity concentrations in MOSFETs built on silicon and germanium. The Arora model reads:

$$\mu_{dop} = \mu_{min} + \frac{\mu_d}{1 + \left(\frac{N_i}{N_0}\right)^{A^r}} \quad (2.33)$$

where  $\mu_{min}$ ,  $\mu_d$ ,  $N_0$  and  $A^r$  are the temperature dependent fitting parameters used in the Arora model and  $N_i$  denotes the total concentration of ionised impurities.

Large transverse electric fields in the channel region of MOSFETs forces carriers to interact strongly with the semiconductor-insulator interface. As a result, carriers in the channel are subjected to scattering by acoustic surface phonons ( $\mu_{ac}$ ) and surface roughness ( $\mu_{sr}$ ). Sentaurus Device generally uses the Lombardi [19] model to describe the mobility degradation caused by these effects given by:

$$\mu_{ac} = \frac{B_l}{\mathcal{E}_t} + \frac{C_l \left( \frac{N_l}{N_0} \right)^{\lambda_l}}{\mathcal{E}_t^{1/3} \left( \frac{T}{T_0} \right)^{k_l}} \quad (2.34)$$

$$\mu_{sr} = \left( \frac{\left( \frac{\mathcal{E}_t}{\mathcal{E}_{ref}} \right)^{A^*}}{\delta_l} + \frac{\mathcal{E}_t^3}{\eta_l} \right)^{-1} \quad (2.35)$$

where  $\mathcal{E}_t$  and  $\mathcal{E}_{ref}$  are the transverse electric field and a reference electric field, respectively,  $B_l, C_l, N_0, \lambda_l, k_l, \eta_l, \delta_l$  are fitting parameters. These contributions are combined with the bulk mobility according to the Mathiessens's rule.

In strong electric fields, the carrier drift velocity is no longer proportional to the electric field strength, rather, the velocity saturates to a finite speed. For Ge based devices simulation the Canali model [20] is used to model this effect:

$$\mu(\mathcal{E}_d) = \frac{\mu_{low}}{\left[ 1 + \left( \frac{\mu_{low} \mathcal{E}_d}{v_{sat}} \right)^{\beta_c} \right]^{\frac{1}{\beta_c}}} \quad (2.36)$$

where the exponent  $\beta_c$  and the saturation velocity  $v_{sat}$  are temperature dependent parameters.  $\mu_{low}$  is the low field mobility, influenced by previously described contributions. the driving force  $\mathcal{E}_d$  can be taken as the component of the electric field parallel to the current flow.

At large impurity concentrations the density of energy states no longer possesses a parabolic energy distribution, instead it becomes dependent on the impurity concentration. This results in a reduction of the bandgap due to the broadening of the impurity band along with the formation of bandtails on the conduction and valence band edges. This phenomenon strongly influences the electrical behaviour of the device, in particular, the minority carrier charge storage and the minority carrier current flow in heavily doped regions. Sentaurus device simulates the bandgap narrowing effect using the Slotboom model [21]:

$$\Delta E_g(N_i) = E_{bgn} \left[ \ln \left( \frac{N_i}{N_{ref}} \right) + \sqrt{\left( \ln \left( \frac{N_i}{N_{ref}} \right) \right)^2 + 0.5} \right] \quad (2.37)$$

where  $E_{bgn}$  and  $N_{ref}$  are material parameters.

Sentaurus Device offers three tunneling models namely 1. FowlerNordheim model 2. the direct tunneling model and 3. the non-local tunneling model. The FowlerNordheim tunneling and the direct tunneling model are restricted to trapezoidal tunneling barriers of metal/oxide/semiconductor interface. The magnitude of the tunneling current depends on the band-edge profile along the entire path between the points connected by tunneling. Therefore, computation of tunneling current at a certain point depends on quantities at other points in the structure. This makes tunneling in a Schottky barrier a nonlocal process. Therefore tunneling current at Schottky barriers, heterostructures, and gate leakage through thin, stacked insulators are best approximated by the nonlocal tunneling model.

The non-local tunneling model utilises either the Schrodinger equation or the WentzelKramersBrillouin (WKB) approximation models to obtain the tunneling probability  $\Gamma_{CC}$  for carriers tunneling to the conduction band at the Schottky contact. For an interface located at 0 and a point at  $r > 0$ , the expression for the net conduction band electron recombination rate due to tunneling to and from the conduction band at point  $0^-$  immediately to the left of the interface is:

$$R_{CC}(r) - G_{CC}(r) = \Theta [\epsilon - E_C(0^-)] \frac{A^*}{qk} \left| \frac{dE_C}{dr}(r) \right| \Theta \left[ -\frac{dE_C}{dr}(r) \right] \Gamma_{CC}(r, \epsilon) \times \left[ T_n(r) \log \left( 1 + \exp \left[ \frac{E_F(r) - \epsilon}{kT_n(r)} \right] \right) - T_n(0^-) \log \left( 1 + \exp \left[ \frac{E_F(0^-) - \epsilon}{kT_n(0^-)} \right] \right) \right] \quad (2.38)$$

where  $R_{CC}$  is the recombination rate,  $G_{CC}$  is the generation rate,  $E_C$  and  $E_F$  are the (position-dependent) conduction band edge and electron Fermi energy,  $\epsilon = E_C(r)$ ,  $\Theta$  is the unit step function,  $A^*$  is the effective Richardson constant and  $T_n$  is the electron temperature. The current density of electrons that tunnel from the conduction band in the bulk to the conduction band at an interface or a contact is the integral over the recombination rate:

$$J_{CC} = -q \int_{0^+}^{\infty} [R_{CC}(r) - G_{CC}(r)] dr \quad (2.39)$$

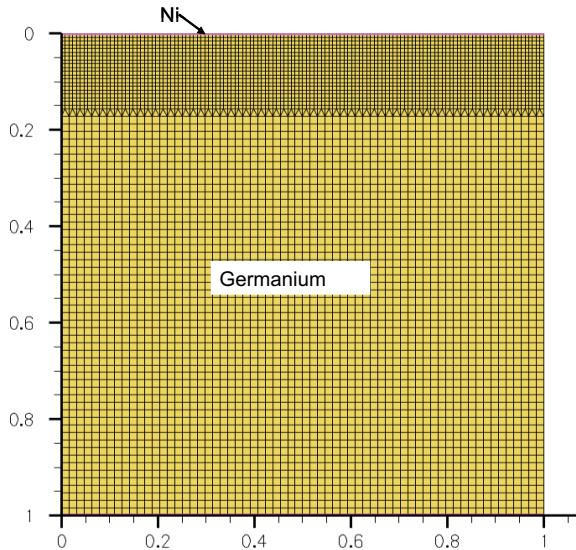

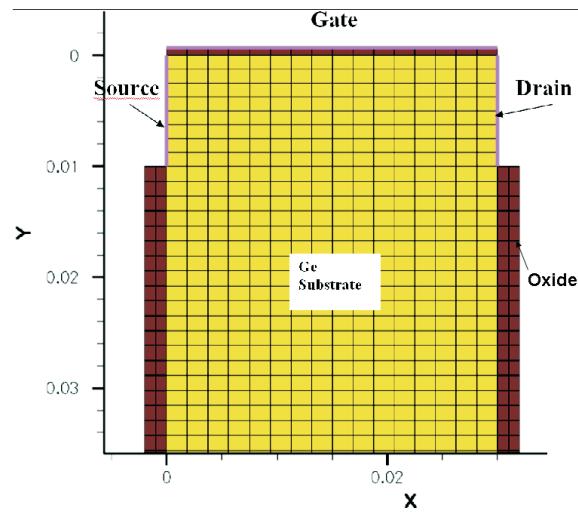

Figure 2.7: An image of the Ni/Ge Schottky barrier mesh.

where  $0^+$  denotes a position infinitesimally to the right of the interface.

The barrier lowering model due to image force can be applied to a Schottky barrier. The following expression is used to compute the value of the barrier lowering:

$$\Delta\Phi(\mathcal{E}) = a_1\left[\left(\frac{\mathcal{E}}{\mathcal{E}_0}\right)^{p_1} - \left(\frac{\mathcal{E} - \mathcal{E}_{eq}}{\mathcal{E}_0}\right)^{p_1}\right] + a_2\left[\left(\frac{\mathcal{E}}{\mathcal{E}_0}\right)^{p_2} - \left(\frac{\mathcal{E} - \mathcal{E}_{eq}}{\mathcal{E}_0}\right)^{p_2}\right] \quad (2.40)$$

where  $\mathcal{E}$  is the absolute value of the electric field,  $\mathcal{E}_{eq}$  is the equilibrium electric field for zero barrier lowering and  $\mathcal{E}_0$  is equal to 1 V/cm,  $a_1$ ,  $a_2$ ,  $p_1$  and  $p_2$  are constants.

### 2.4.3 Schottky barrier simulation

A typical mesh created by using Sentaurus Structure Editor for the Schottky diode simulation is presented in Fig. 2.7. The contact area was  $1 \mu\text{m}^2$ . For accurate calculation of the diode current a very fine mesh of  $1 \text{ nm}^2$  was used from the contact to the depletion region edges.

There is no graphical user interface for Sentaurus device for device simulation. For the definition of the transport model, physics model, the file names, the solve procedure, and so on, a script has to be written with a text editor. A typical input file for the Ni/Ge Schottky diode simulation is given below. The file section contains the filenames of the input and the output files. The Anode contact is regarded as the

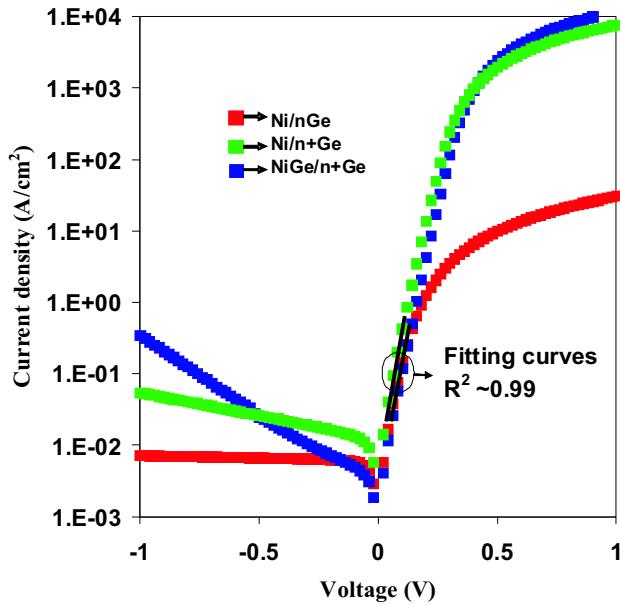

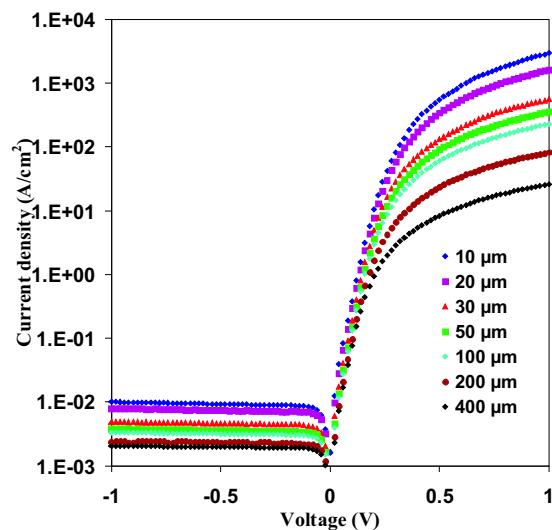

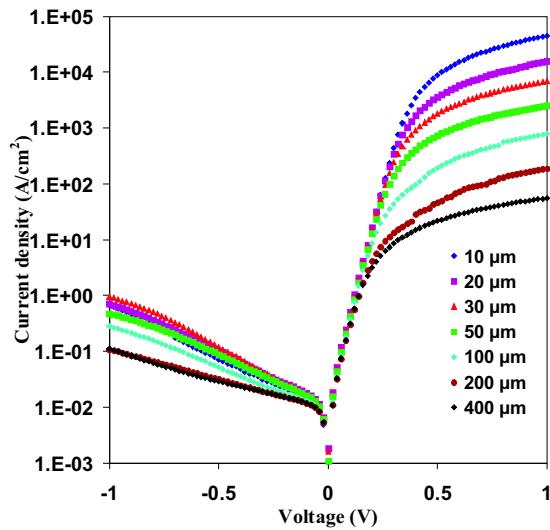

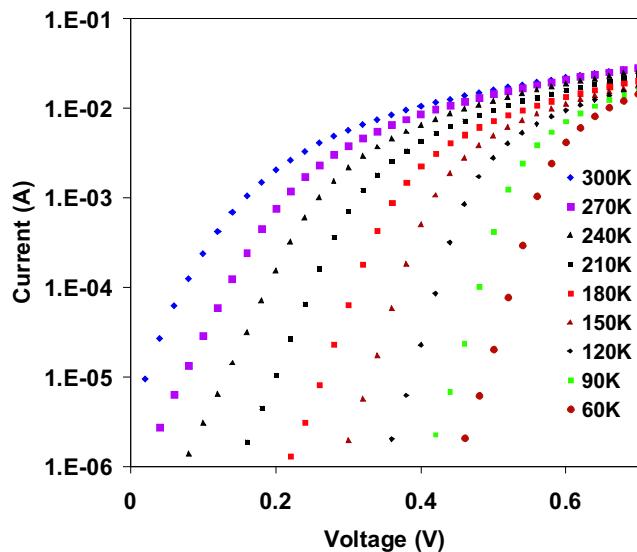

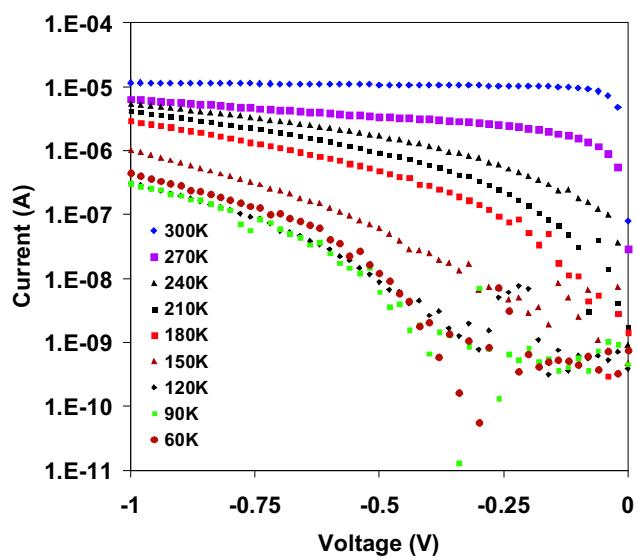

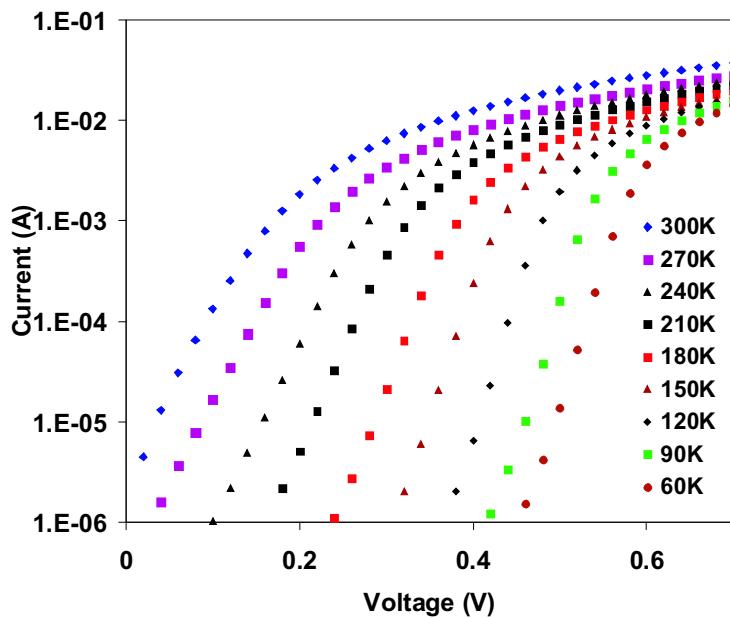

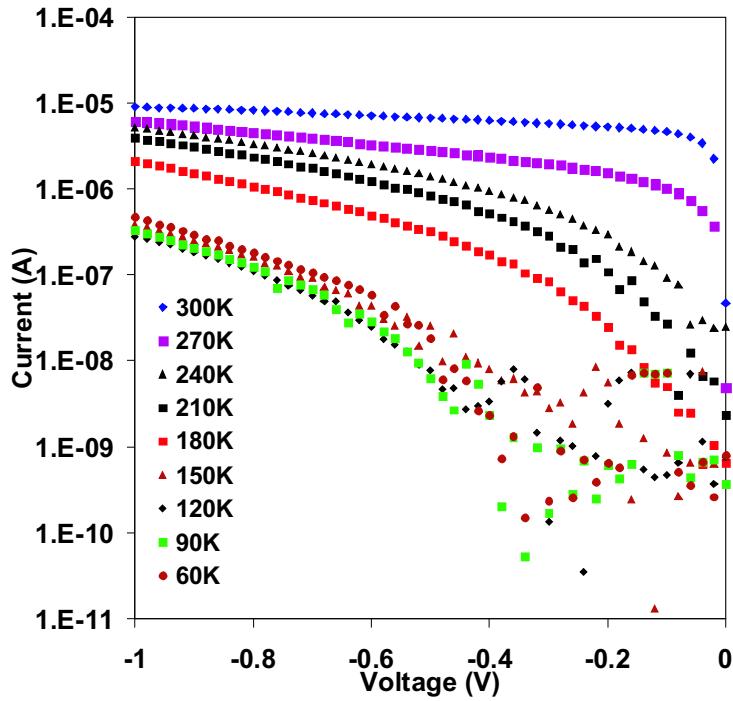

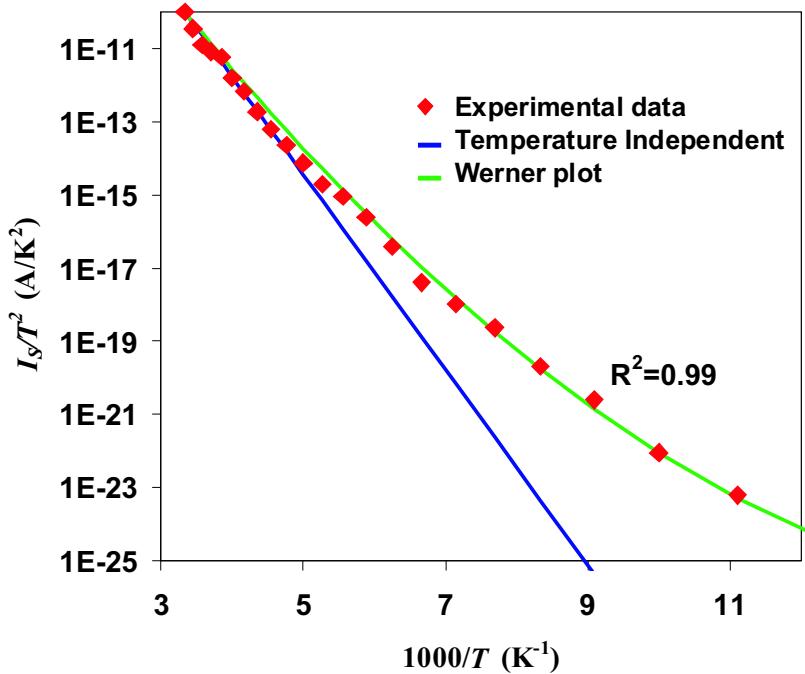

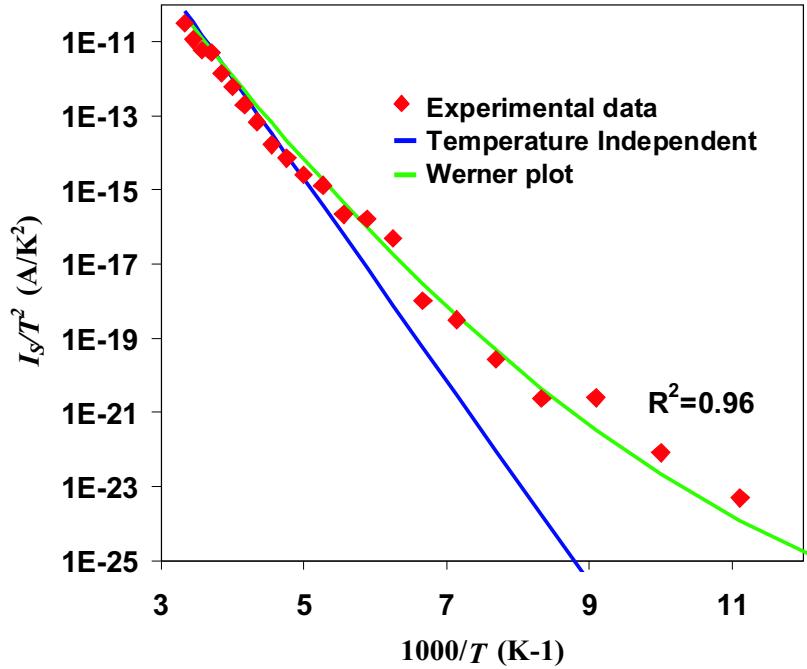

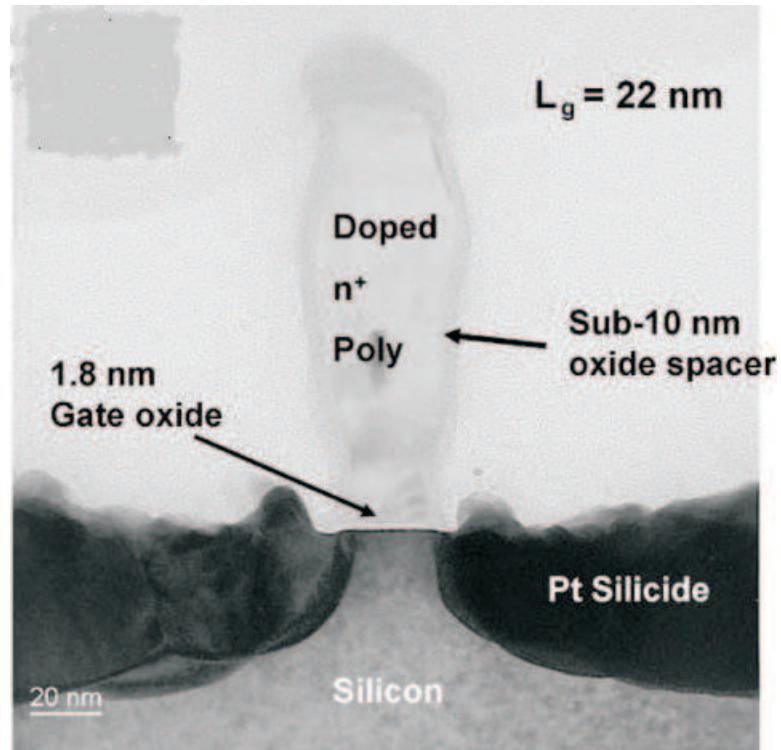

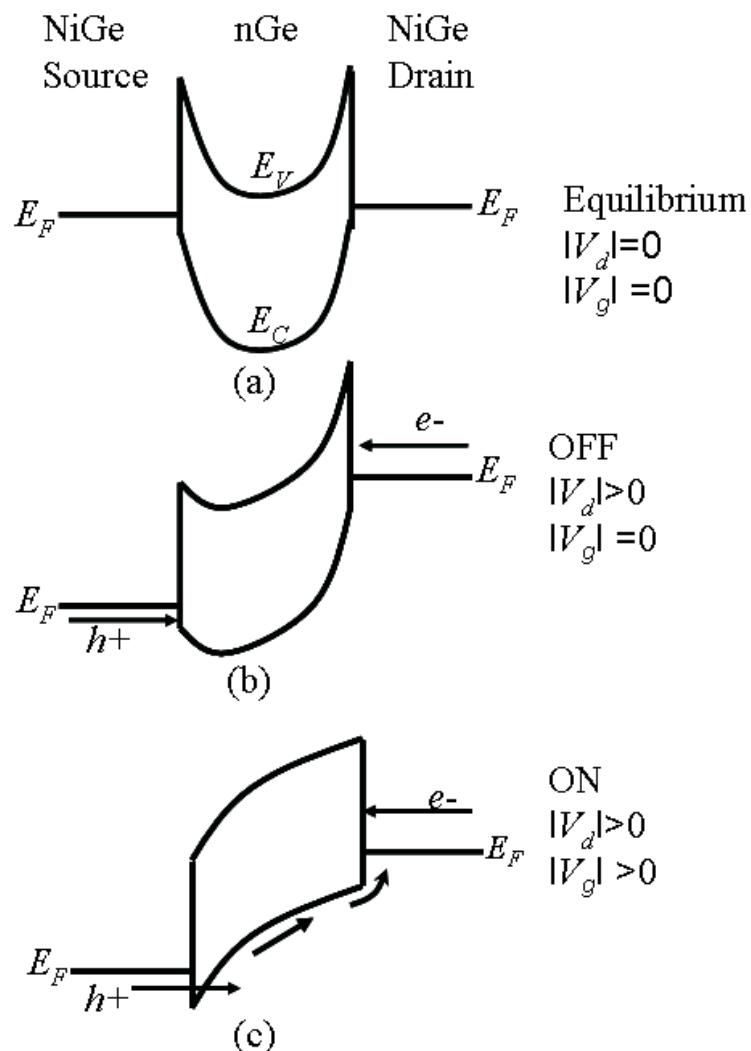

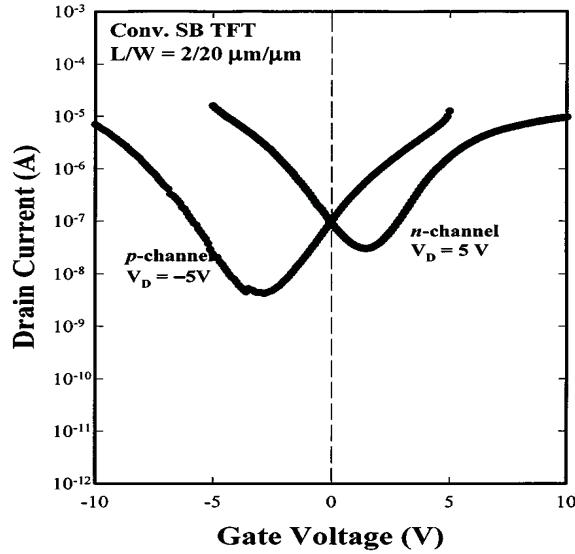

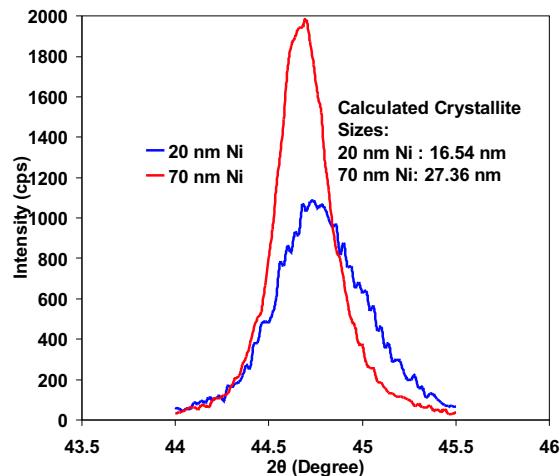

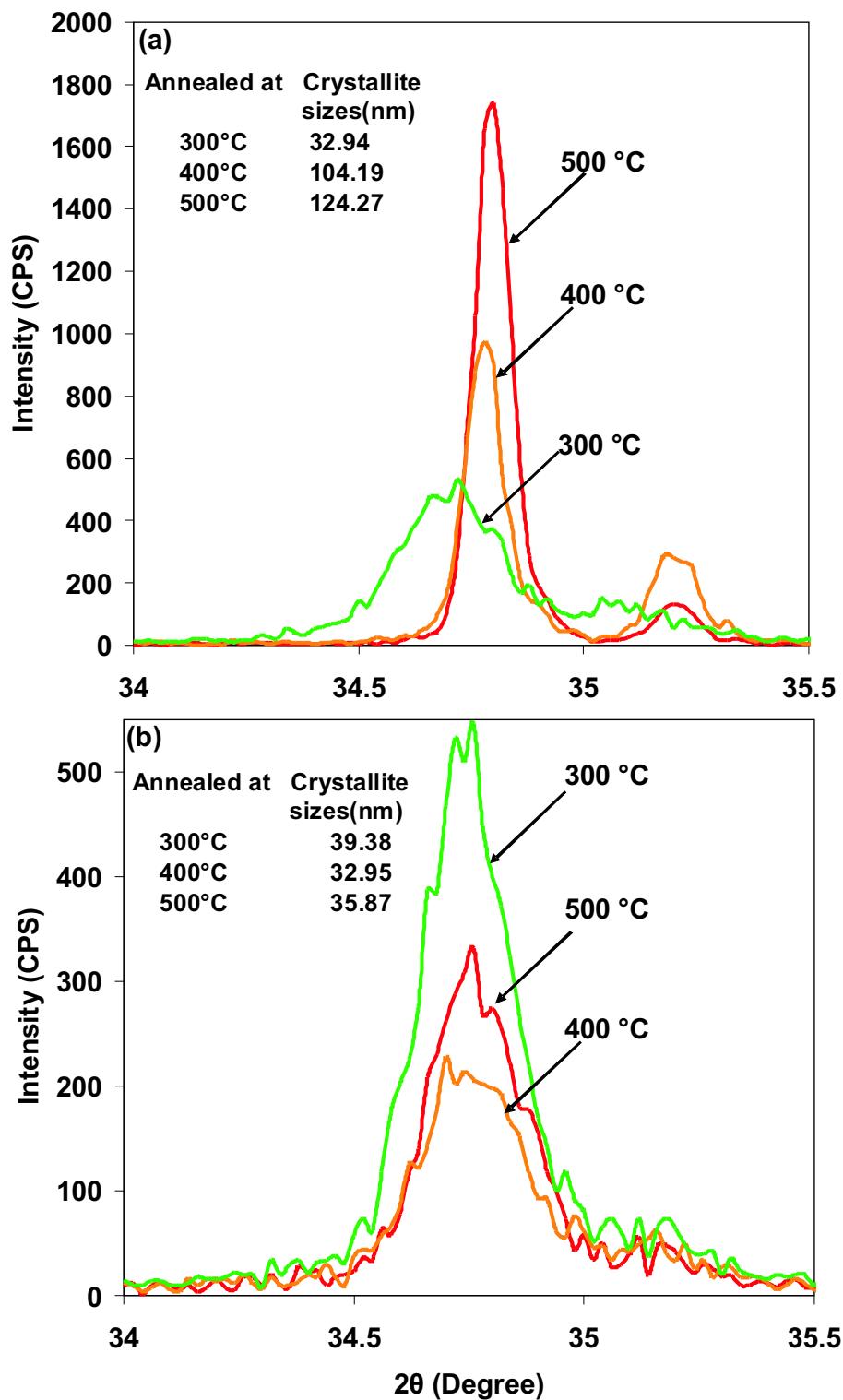

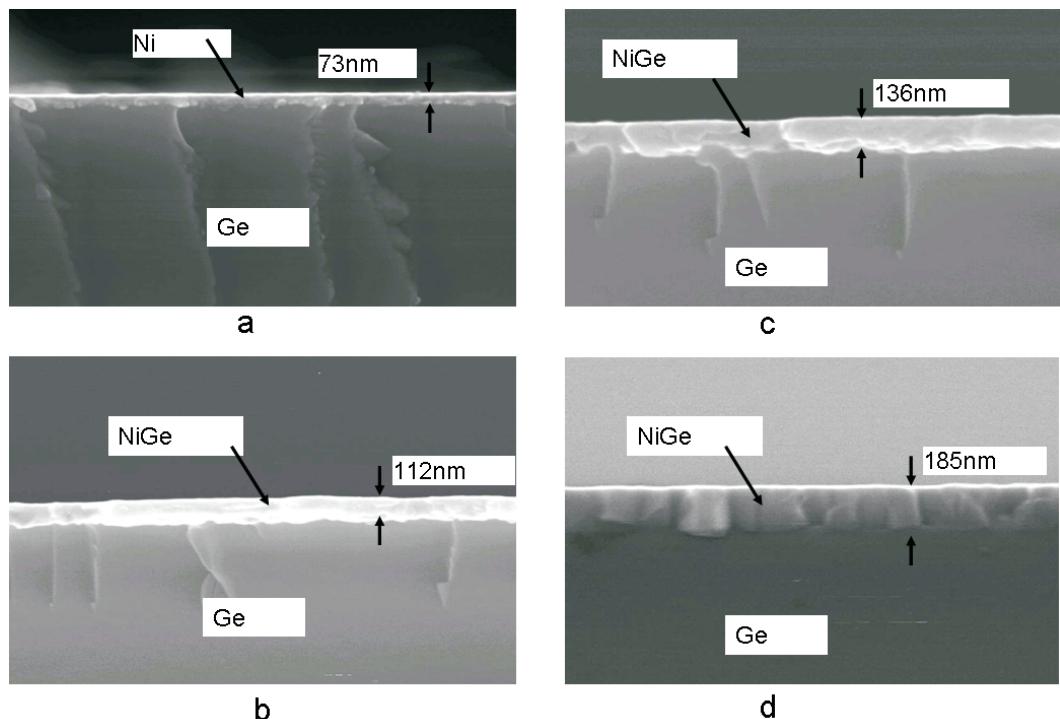

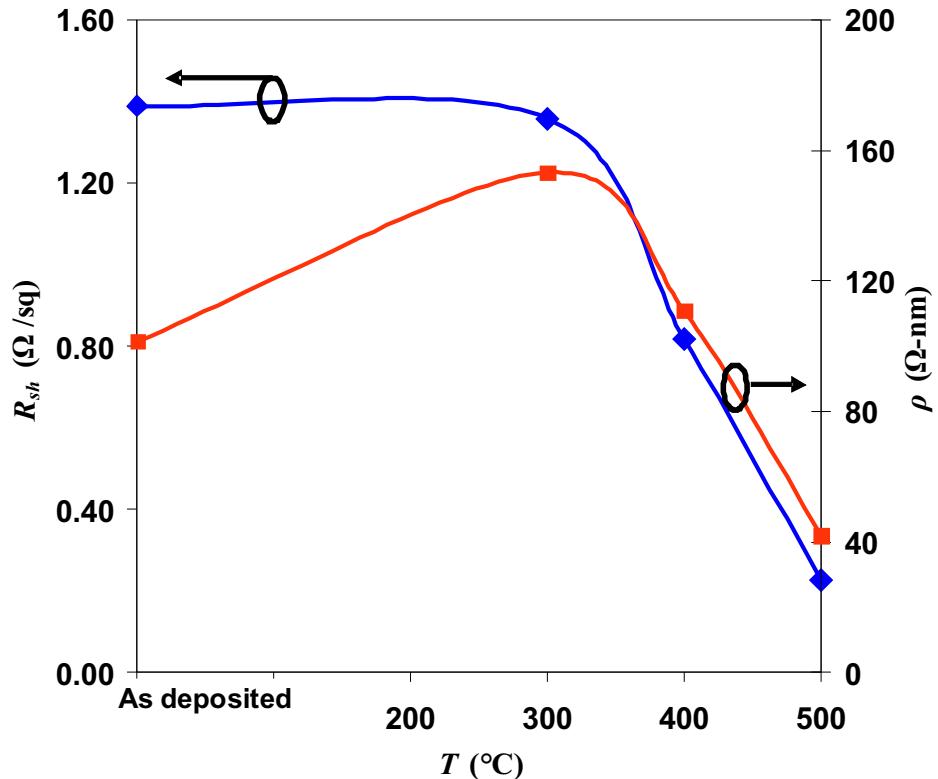

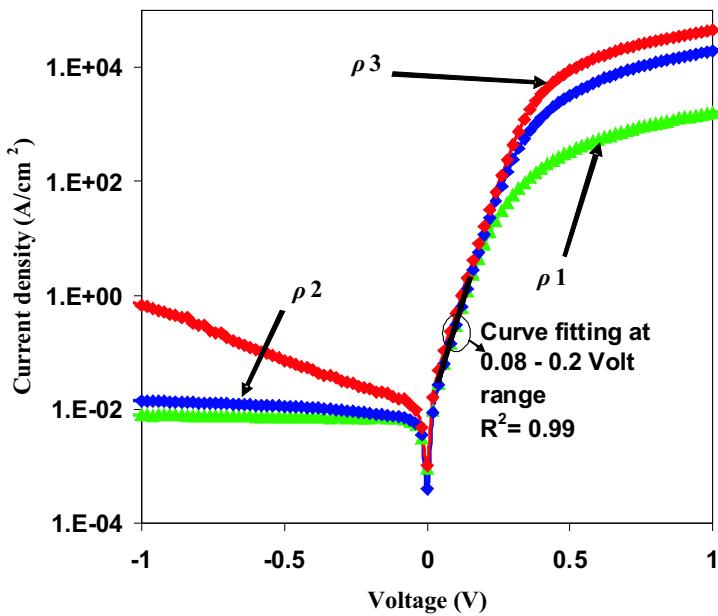

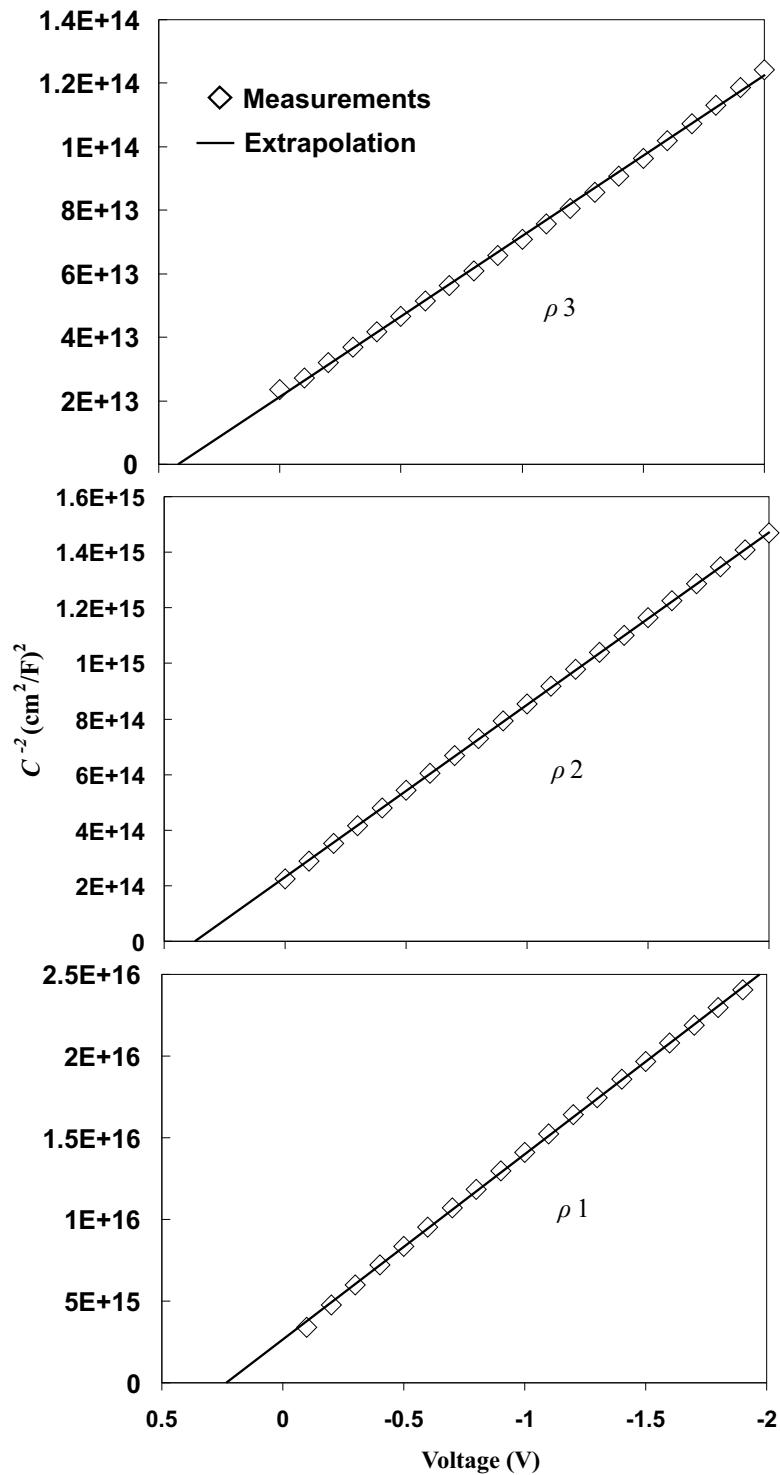

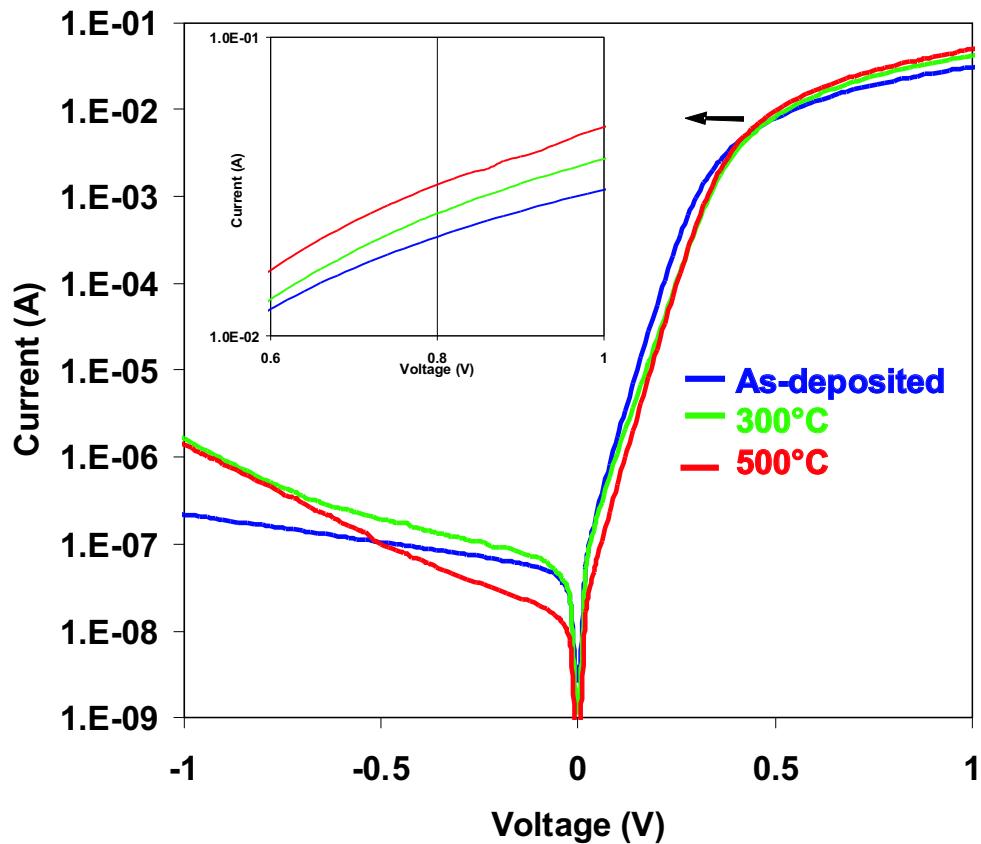

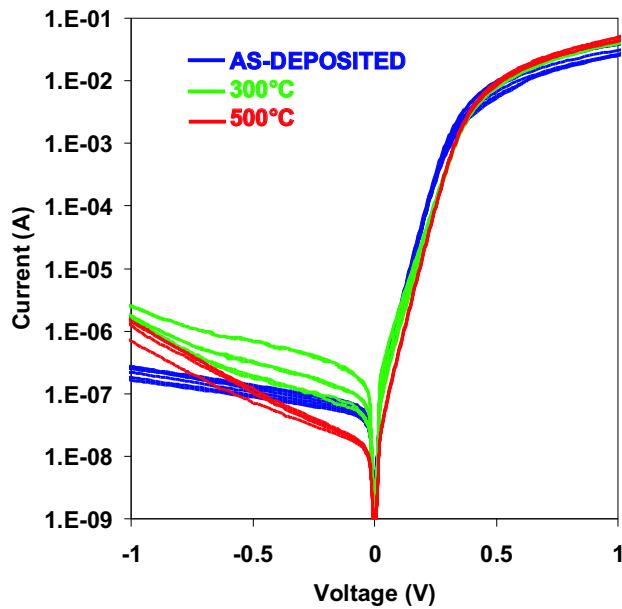

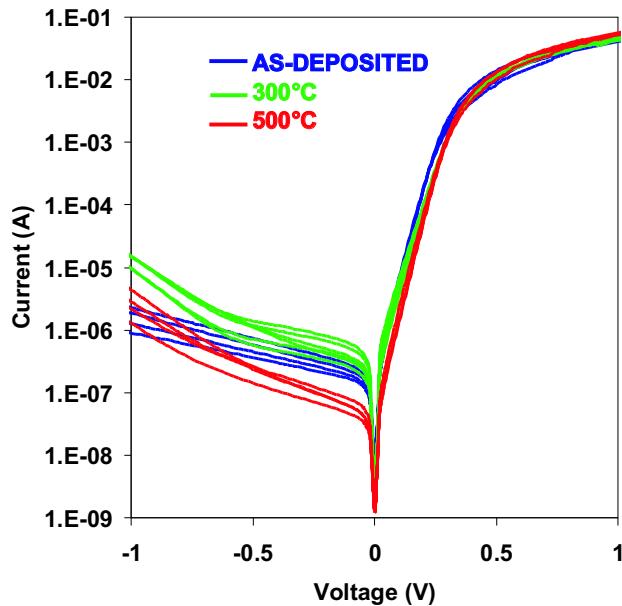

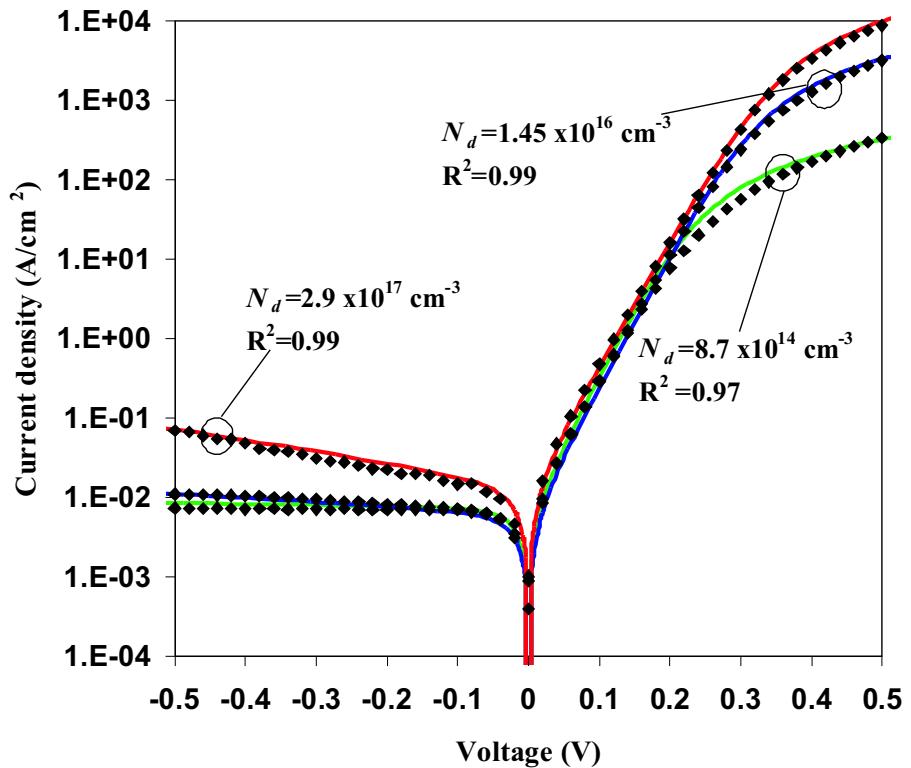

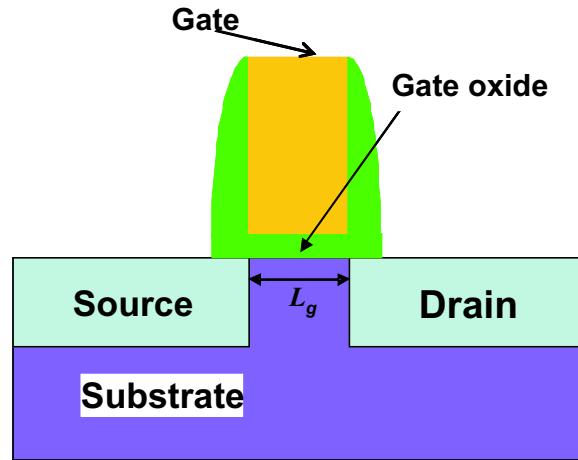

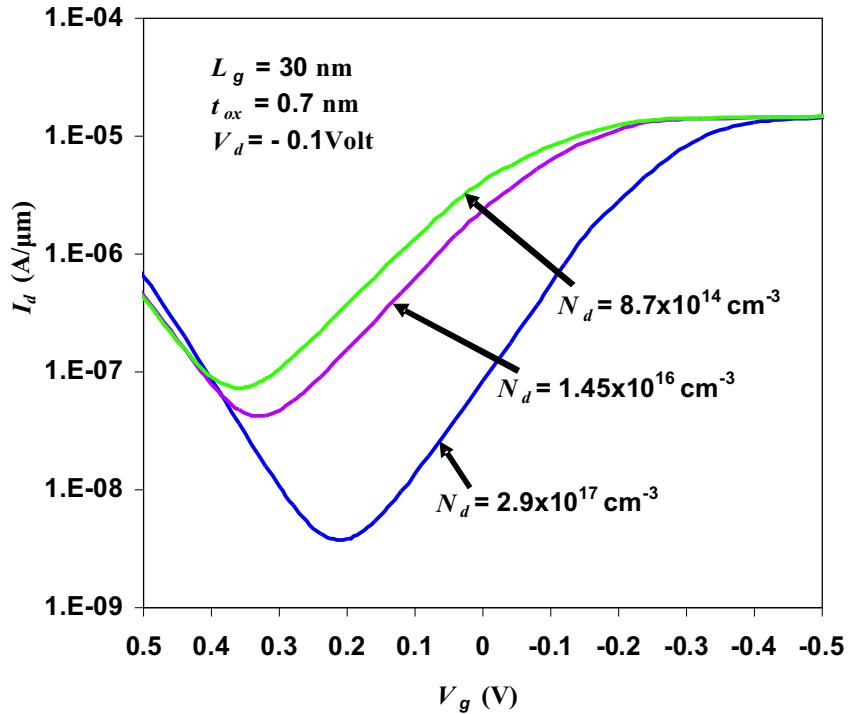

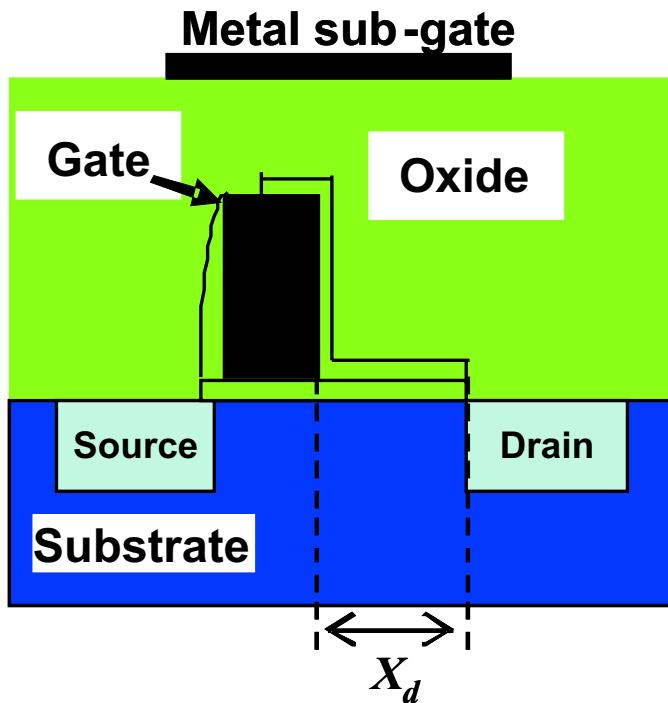

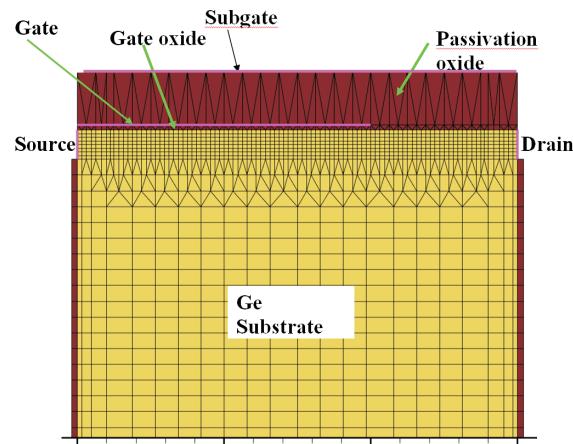

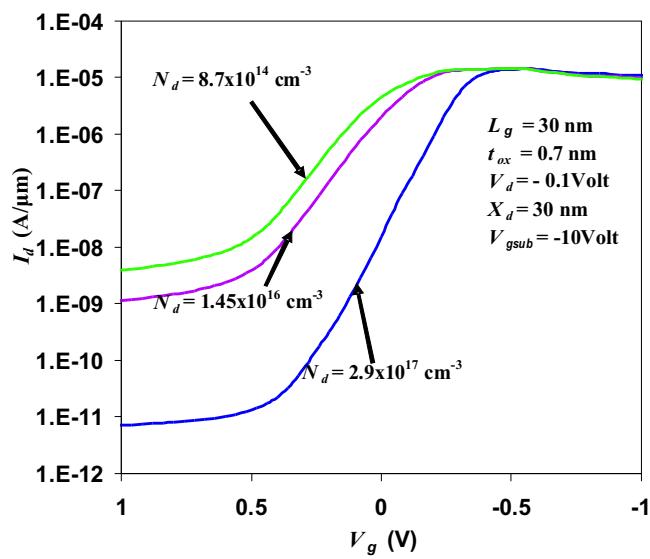

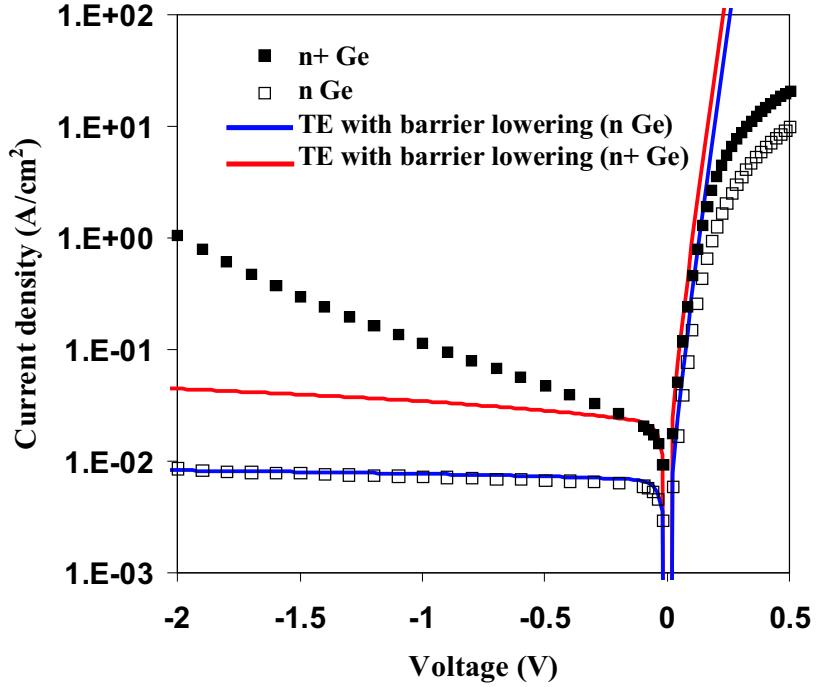

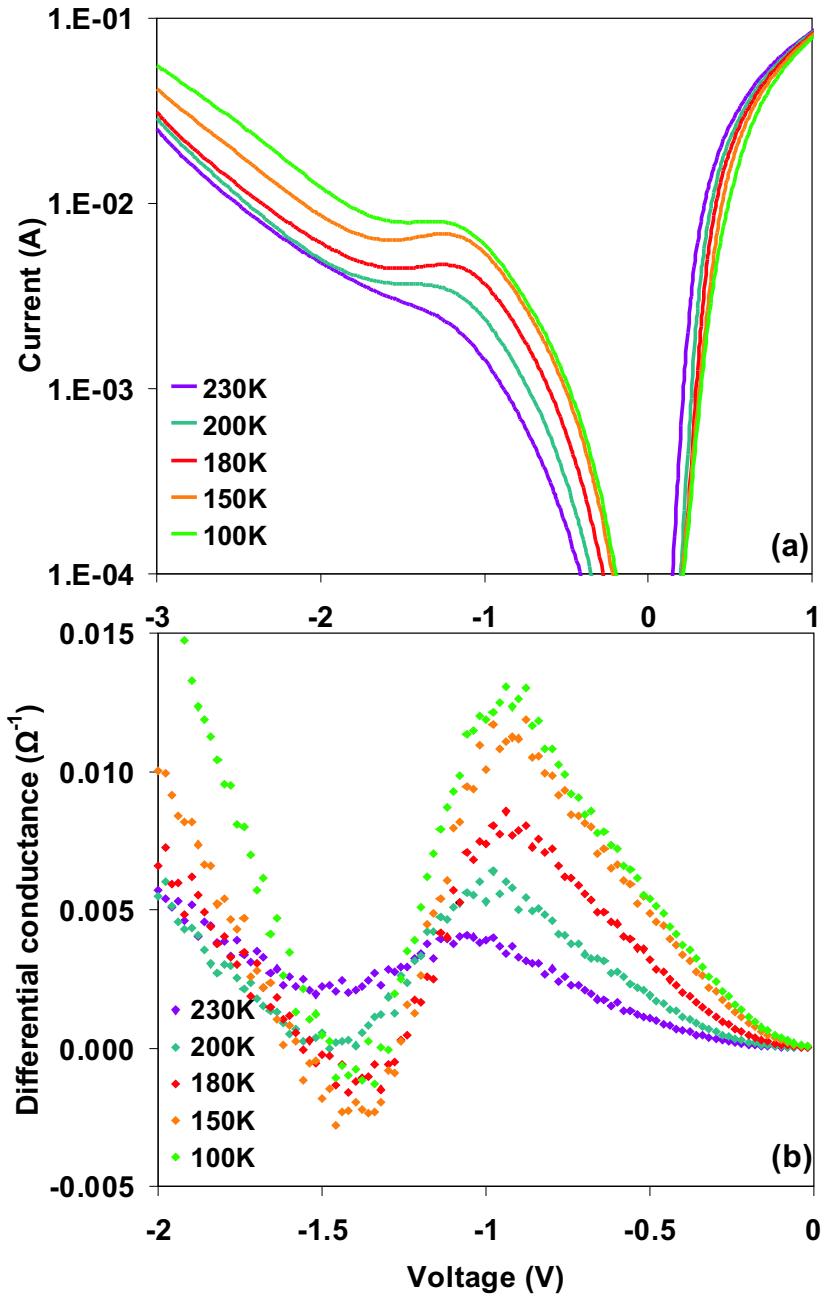

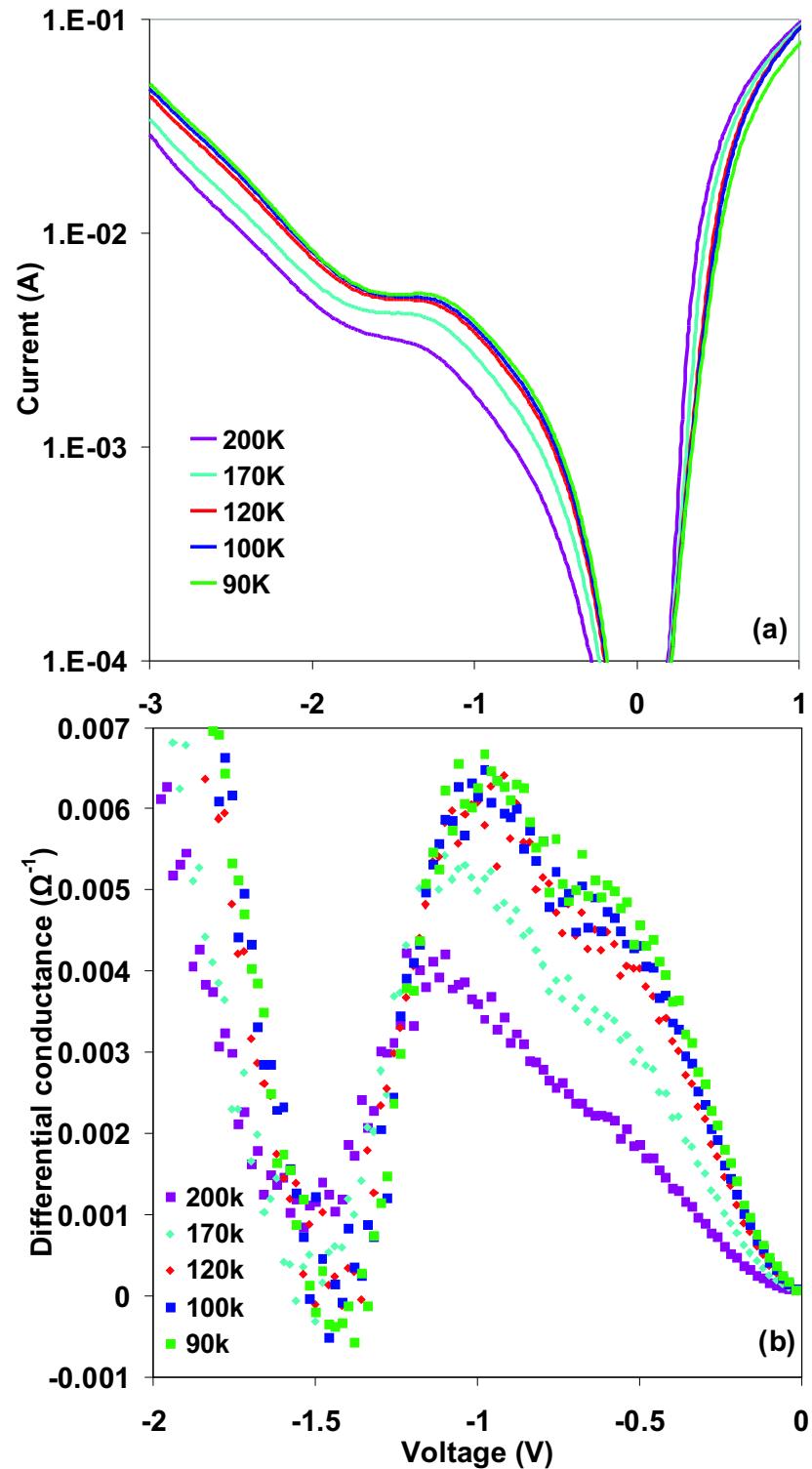

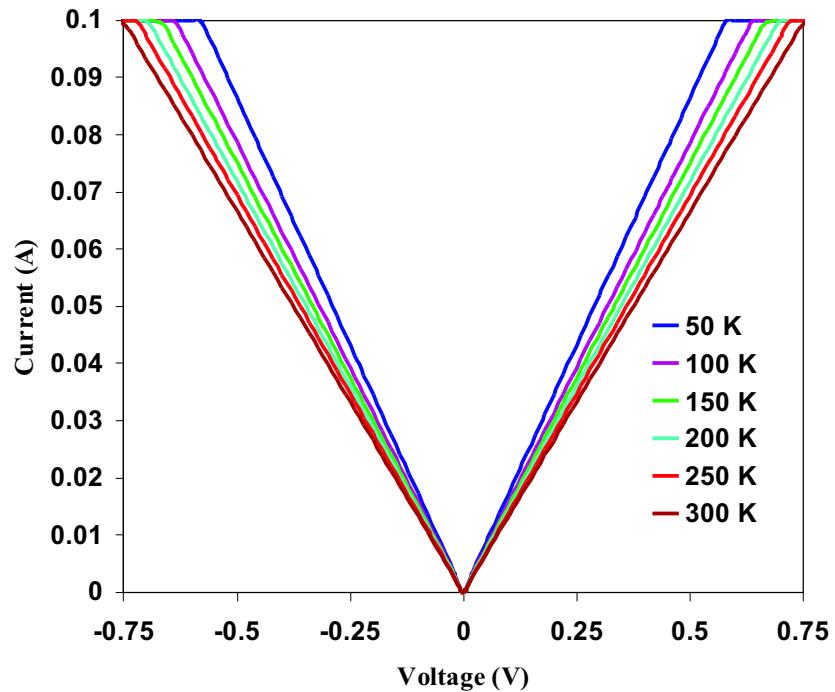

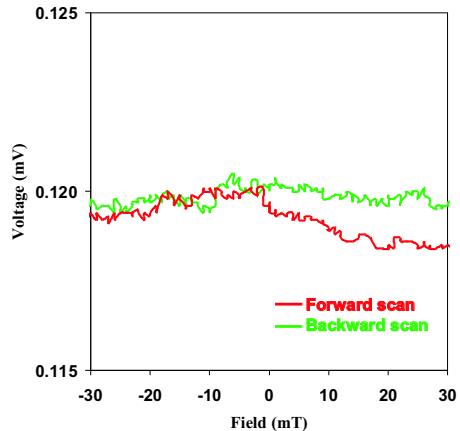

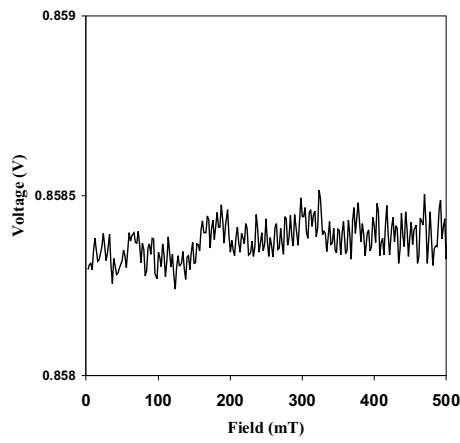

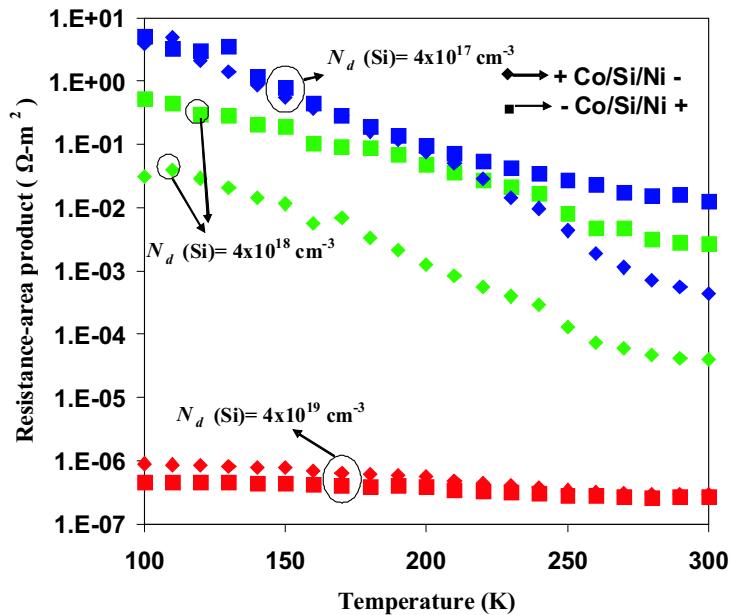

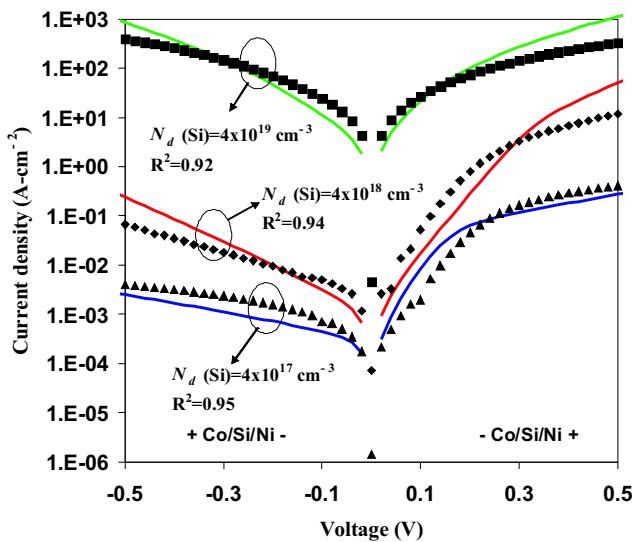

Ni Schottky contact. In order to account for the Fermi-level pinning effect in Ge the work function of the metal at the contact description was tuned so that a net electron barrier height is obtained by using equation 2.1. A lumped resistance of 10 ohm is added in the cathode electrode contact to account for any series resistance.