University of Southampton Research Repository

ePrints Soton

Copyright © and Moral Rights for this thesis are retained by the author and/or other copyright owners. A copy can be downloaded for personal non-commercial research or study, without prior permission or charge. This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the copyright holder/s. The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the copyright holders.

When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given e.g.

AUTHOR (year of submission) "Full thesis title", University of Southampton, name of the University School or Department, PhD Thesis, pagination

**A Surface-Potential-Based Compact

Model for Partially Depleted

Silicon-On-Insulator MOSFETs**

by James Benson

*Thesis, April 2009*

UNIVERSITY OF SOUTHAMPTON

FACULTY OF ENGINEERING AND APPLIED SCIENCE

DEPARTMENT OF ELECTRONICS AND COMPUTER SCIENCE

**A SURFACE-POTENTIAL-BASED COMPACT

MODEL FOR PARTIALLY DEPLETED

SILICON-ON-INSULATOR MOSFETS**

by James Benson

*Thesis, April 2009.*

To my parents, Leslie and Zora.

UNIVERSITY OF SOUTHAMPTON

ABSTRACT

FACULTY OF ENGINEERING AND APPLIED SCIENCE

DEPARTMENT OF ELECTRONICS AND COMPUTER SCIENCE

Doctor of Philosophy

A SURFACE-POTENTIAL-BASED COMPACT MODEL FOR

PARTIALLY DEPLETED SILICON-ON-INSULATOR MOSFETS

by James Benson

With the continuous scaling of CMOS technologies, Silicon-on-Insulator (SOI) technologies have become more competitive compared to bulk, due to their lower parasitic capacitances and leakage currents. The shift towards high frequency, low power circuitry, coupled with the increased maturity of SOI process technologies, have made SOI a genuinely cost-effective solution for leading edge applications.

The original STAG2 model, developed at the University of Southampton, UK, was among the first compact circuit simulation models to specifically model the behaviour of Partially-Depleted (PD) SOI devices. STAG2 was a robust, surface-potential based compact model, employing closed-form equations to minimise simulation times for large circuits. It was able to simulate circuits in DC, small signal, and transient modes, and particular care was taken to ensure that convergence problems were kept to a minimum.

In this thesis, the ongoing development of the STAG model, culminating in the release of a new version, STAG3, is described. STAG3 is intended to make the STAG model applicable to process technologies down to 100nm. To this end, a number of major model improvements were undertaken, including: a new core surface potential model, new vertical and lateral field mobility models, quantum mechanical models, the ability to model non-uniform vertical doping profiles, and other miscellaneous effects relevant to deep sub-micron devices such as polysilicon depletion, velocity overshoot, and the reverse short channel effect.

As with the previous versions of STAG, emphasis has been placed on ensuring that model equations are numerically robust, as well as closed-form wherever possible, in order to minimise convergence problems and circuit simulation times. The STAG3 model has been evaluated with devices manufactured in PD-SOI technologies down to  $0.25\mu\text{m}$ , and was found to give good matching to experimental data across a range of device sizes and biases, whilst requiring only a single set of model parameters.

# Acknowledgements

It's a sure sign that a PhD has gone well over time when your first instinct is to break up your acknowledgements into separate sub-sections. In the time since I began this research, I have moved house five times, worked in four different jobs, and seen three generations of PhD students come and go at two universities. Before any more time elapses, let us begin the credits. Profound apologies for any omissions; I'm afraid my memory isn't what it used to be.

I'll start with a big thank you to my supervisor Bill Redman-White. Despite many setbacks, he never lost faith in the project, and he went to great lengths to build collaborations and secure funding in the early years, during what was a turbulent period in the industry. When developing a compact model, it's always useful to see things from the perspective of the designer, and Bill's expertise provided a useful counterpoint to my own physics-based 'side on' view of devices. And while I never got the hang of circuit design, it certainly wasn't due to any lack of encouragement on his part!

I was lucky enough to share an office with two very capable and dedicated PhD students, Nele d'Hallewijn and Ketan Mistry. Nele's similar research interests meant that I always had a sounding board for my ideas, and our conversations provided me with a great deal of insight into the subtleties of compact model development. Ketan provided advice on everything from typesetting LaTeX documents to building measurement gear, and his help was greatly appreciated.

I also had a great deal of help from some of my fellow RAs. Mike Lee, the original author of the STAG model, made sure to pass on as much of his knowledge as he could, and got me off to a good start. Bernard Tenbroek introduced me to device characterisation, and his small-signal measurement setup continued to see use long after his departure. Craig Easson worked with me on the DERA contract until he too was lured to California.

Various partners and collaborators provided us with funding, processed devices, and measurement data. In particular, I'd like to thank Mike Uren of DERA Malvern, Jean-Luc Pelloie and Olivier Faynot of CEA-LETI Grenoble, and Mike Liu of Honeywell Semiconductors. I would also like to express my appreciation to Henri Kemhadjian and Peter Ashburn for keeping me gainfully employed when my research contract came to an end.

Other notables include John Amy and Pinder Sant, the epi gurus, Dave Batt, with whom I had a very productive collaboration writing the software for the EPI4 machine, and Glenys Howe, Lucia Hewett, and Angie Mo, who helped me out more times than I can count!

Socially, I've been fortunate to have made many good friends in each of the places I've lived, and without them I doubt I would have emerged from this whole business with my sanity intact. Since I've been getting around a bit, I'll list them by location!

**Southampton:** Thanks go to my old partners in crime Mir Mokhtari and Becky Neal, my good friend Elena Koukharenko for all the long chats over coffee, and of course Gabriela Dilliway, who has been a constant presence throughout and who taught me more about this crazy industry than anyone else. A special mention for Rona Barnedo, for all the great times both in and out of the salsa bars. Also, a big shout out to all members of the volleyball team 'The Random Collection', as well as all the other teams who helped make the volleyball league such a success. And of course, Roz Painter, for a wonderful two years, and for being my muse when it really mattered.

**Guildford:** The Denzil Road posse deserve a special mention for being quite possibly the coolest, craziest, most entertaining bunch of housemates ever gathered under one roof. Rob McCracken, Faye Stacey, Natalie Biddle, Mark Prentice, Shelley Taylor, the ever present Darren Arnold, and many others in all their strangeness. May the Denzil Road parties continue for many years to come!

Not to be outdone, the Surrey University postgrad community was one of the main reasons I stayed so long. Claire Mercier, Melanie Webb, Justin Hamilton, Daphnee Pushparajah, Laura Hyman, Tim Sinnamon, Yvonne Huebner, Liliana Cuenca, Andy Smith and many others all helped to make university life a hugely enjoyable experience for me.

Others that I count myself very fortunate to have met during my time in Surrey include Rebecca Oyabugbe, Mida Aslam (I'm not drunk!), Ashley Browning, Farnaz Behzadmehr, Andreia and Andrea (the famous Brazilian double-act), and Suzi and Harriet for their brief but memorable visit! Last but certainly not least, Fortune Mgbangson, who gave me so much support, encouragement, and inspiration during some difficult times.

**Leuven:** Some of my colleagues at NXP became good friends, and made my life more fun both in and out of work. Big thanks go to Rob Lander for footie nights and for bringing me over here in the first place, Suzanne Vollenbronck for keeping me out dancing all night, Eero Saarnilehto for asking the big questions (why did you do that?), Benoit Battaillou for being generally evil, and of course Korina Fotopoulou for her huge moral support, for her expert LaTeX assistance, and for putting a roof over my head during the final days of my thesis corrections.

Thanks also go to Tra Pham for all the good times and silly jokes, Lode Devlieghere for keeping me focused on the important things in life, Inge Lontie for showing me the wild side of Leuven, and all the staff of Ron Blacks for keeping the cider flowing. Katrien Segaert, Clara Younan, and Lavinia Butiu all deserve a mention for making my life more interesting, albeit briefly. And finally, thanks to An de Groef (a.k.a. KM), who left me with lots of great memories, and whose charm, good humour, and constant support made my first year in Leuven better than I ever could have expected.

# Contents

|                                                                  |      |

|------------------------------------------------------------------|------|

| <b>Abstract</b>                                                  | ii   |

| <b>Acknowledgements</b>                                          | iii  |

| <b>Contents</b>                                                  | v    |

| <b>List of Figures</b>                                           | viii |

| <b>List of Symbols</b>                                           | xii  |

| <b>List of Acronyms</b>                                          | xvii |

| <b>1 Introduction</b>                                            | 1    |

| 1.1 A Review of MOS Technology . . . . .                         | 1    |

| 1.1.1 Bulk Technology . . . . .                                  | 1    |

| 1.1.2 SOI Technology . . . . .                                   | 2    |

| 1.1.3 SOI versus bulk . . . . .                                  | 3    |

| 1.2 A Review of MOS Compact Models . . . . .                     | 5    |

| 1.2.1 Piece-Wise Models . . . . .                                | 5    |

| 1.2.2 Surface Potential Models . . . . .                         | 6    |

| 1.3 The STAG Model . . . . .                                     | 8    |

| 1.4 Structure of this thesis . . . . .                           | 9    |

| References . . . . .                                             | 11   |

| <b>2 Low Field DC Model</b>                                      | 14   |

| 2.1 Introduction . . . . .                                       | 14   |

| 2.2 Channel Current . . . . .                                    | 14   |

| 2.3 MOS Capacitor Structure . . . . .                            | 16   |

| 2.4 Channel and Body Charge . . . . .                            | 18   |

| 2.5 Channel Current as a function of Surface Potential . . . . . | 21   |

| 2.6 Low Field Surface Potential Model . . . . .                  | 21   |

| 2.7 Surface Potential Determination . . . . .                    | 23   |

| 2.7.1 Subthreshold . . . . .                                     | 23   |

| 2.7.2 Strong Inversion . . . . .                                 | 24   |

| 2.7.3 A Single Piece Model . . . . .                             | 25   |

| 2.7.4 Intrinsic Channel Current Expression . . . . .             | 27   |

| References . . . . .                                             | 28   |

| <b>3 High Field Effects 1: Mobility Model</b>                    | 30   |

| 3.1 Introduction . . . . .                                       | 30   |

| 3.2 Compact Mobility Models . . . . .                            | 32   |

| 3.3 STAG Mobility Model . . . . .                                | 35   |

|          |                                                               |           |

|----------|---------------------------------------------------------------|-----------|

| 3.3.1    | Phonon Scattering . . . . .                                   | 36        |

| 3.3.2    | Surface Roughness Scattering . . . . .                        | 36        |

| 3.3.3    | Coulomb Scattering . . . . .                                  | 36        |

| 3.3.4    | Complete Model . . . . .                                      | 38        |

|          | References . . . . .                                          | 40        |

| <b>4</b> | <b>High Field Effects 2: Lateral Field Model</b>              | <b>44</b> |

| 4.1      | Introduction . . . . .                                        | 44        |

| 4.2      | Modelling Velocity Saturation . . . . .                       | 45        |

| 4.3      | STAG Lateral Field Model . . . . .                            | 47        |

| 4.3.1    | Series Resistance . . . . .                                   | 47        |

| 4.3.2    | Velocity Overshoot . . . . .                                  | 48        |

| 4.3.3    | Final Expression . . . . .                                    | 49        |

| 4.4      | Calculation of Saturation Surface Potential . . . . .         | 50        |

|          | References . . . . .                                          | 54        |

| <b>5</b> | <b>High Field Effects 3: Quantum Mechanical Model</b>         | <b>56</b> |

| 5.1      | Introduction . . . . .                                        | 56        |

| 5.2      | Quantum Theory of MOSFET Inversion Layers . . . . .           | 58        |

| 5.2.1    | Triangular Potential Approximation . . . . .                  | 59        |

| 5.2.2    | Variational Method . . . . .                                  | 60        |

| 5.3      | Quantum Mechanical Compact Modelling . . . . .                | 61        |

| 5.4      | New Quantum Mechanical Model . . . . .                        | 63        |

|          | References . . . . .                                          | 65        |

| <b>6</b> | <b>Threshold Voltage Model</b>                                | <b>67</b> |

| 6.1      | Introduction . . . . .                                        | 67        |

| 6.2      | Modelling of Non-Uniform Doping . . . . .                     | 68        |

| 6.3      | New Non-Uniform Doping Model . . . . .                        | 71        |

| 6.3.1    | Approximation of the Error Function . . . . .                 | 71        |

| 6.3.2    | Obtaining a Closed-Form Expression for $x_d$ . . . . .        | 72        |

| 6.3.3    | Modifying the Body Factor $\gamma_s$ . . . . .                | 78        |

| 6.4      | Drain Induced Barrier Lowering . . . . .                      | 80        |

| 6.5      | Short Channel Effect . . . . .                                | 80        |

| 6.6      | Reverse Short Channel Effect . . . . .                        | 80        |

| 6.7      | Threshold Voltage Extraction Method . . . . .                 | 82        |

| 6.7.1    | Standard Threshold Voltage Model . . . . .                    | 83        |

| 6.7.2    | Qualitative Features of New Threshold Voltage Model . . . . . | 85        |

| 6.7.3    | Derivation of New Threshold Voltage Model . . . . .           | 86        |

| 6.7.4    | Evaluation of New Model . . . . .                             | 87        |

|          | References . . . . .                                          | 91        |

| <b>7</b> | <b>Auxiliary Model</b>                                        | <b>94</b> |

| 7.1      | Introduction . . . . .                                        | 94        |

| 7.2      | Extrinsic Parasitics and Floating Body Effects . . . . .      | 94        |

| 7.3      | Self-Heating Model . . . . .                                  | 96        |

| 7.3.1    | Basic and Advanced Models . . . . .                           | 96        |

| 7.3.2    | Using the Basic Model . . . . .                               | 97        |

| 7.3.3    | Thermal Effect on Physical Parameters . . . . .               | 100       |

| 7.3.4    | Thermal Effect on Parasitic Components . . . . .              | 100       |

| 7.4      | Channel Length Modulation . . . . .                           | 101       |

| 7.5      | External Source and Drain Series Resistance . . . . .         | 102       |

|                                                                 |            |

|-----------------------------------------------------------------|------------|

| References . . . . .                                            | 103        |

| <b>8 Charge Model</b>                                           | <b>105</b> |

| 8.1 Capacitance Modelling in SPICE . . . . .                    | 105        |

| 8.2 Intrinsic Capacitances . . . . .                            | 105        |

| 8.2.1 GCA Region Charge . . . . .                               | 106        |

| 8.2.2 Drain Region Charge . . . . .                             | 108        |

| 8.2.3 Drain Region Body Charge Model . . . . .                  | 109        |

| 8.3 Extrinsic Capacitances . . . . .                            | 122        |

| 8.3.1 Source and Drain Junction Depletion Capacitance . . . . . | 122        |

| 8.3.2 Overlap Capacitances . . . . .                            | 123        |

| References . . . . .                                            | 124        |

| <b>9 Model Evaluation Results</b>                               | <b>126</b> |

| 9.1 Introduction . . . . .                                      | 126        |

| 9.2 Transconductance Results . . . . .                          | 126        |

| 9.3 Subthreshold Results . . . . .                              | 132        |

| 9.4 Output Characteristics . . . . .                            | 134        |

| References . . . . .                                            | 138        |

| <b>10 Conclusions and Further Work</b>                          | <b>140</b> |

| 10.1 Conclusions . . . . .                                      | 140        |

| 10.2 Suggestions for Further Work . . . . .                     | 141        |

| 10.2.1 DC Model . . . . .                                       | 141        |

| 10.2.2 Charge and Noise Models . . . . .                        | 143        |

| 10.2.3 Other Device Models . . . . .                            | 144        |

| References . . . . .                                            | 145        |

| <b>A Technology Key</b>                                         | <b>147</b> |

| <b>B Publication List</b>                                       | <b>148</b> |

# List of Figures

|     |                                                                                                                                                                                                                                                                                               |    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

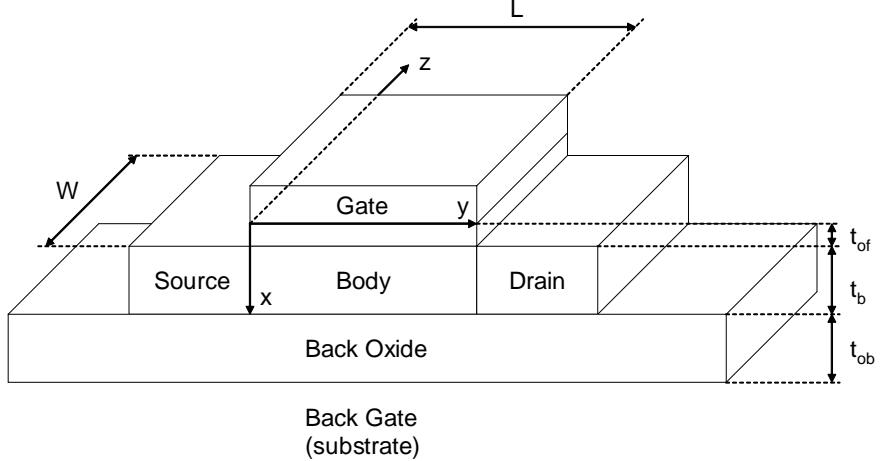

| 2.1 | Schematic of Silicon-on-Insulator (SOI) device, showing the co-ordinate orientation of x, y, and z . . . . .                                                                                                                                                                                  | 15 |

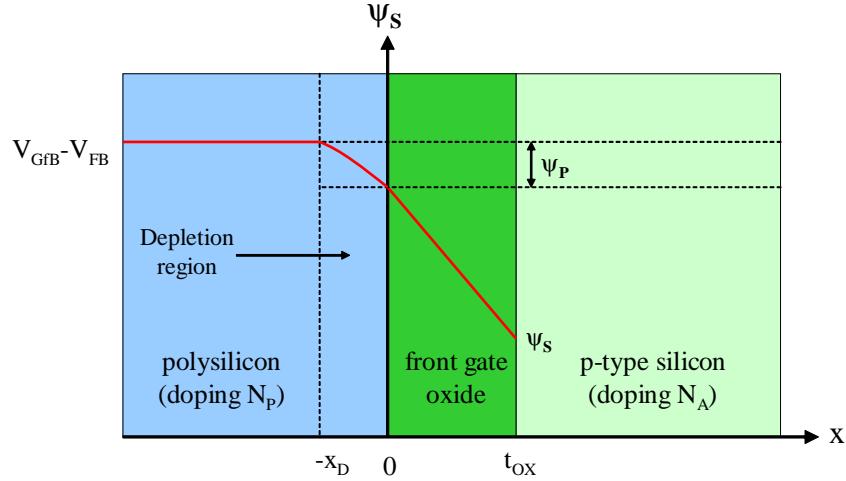

| 2.2 | Voltage profile across MOS capacitor structure. . . . .                                                                                                                                                                                                                                       | 17 |

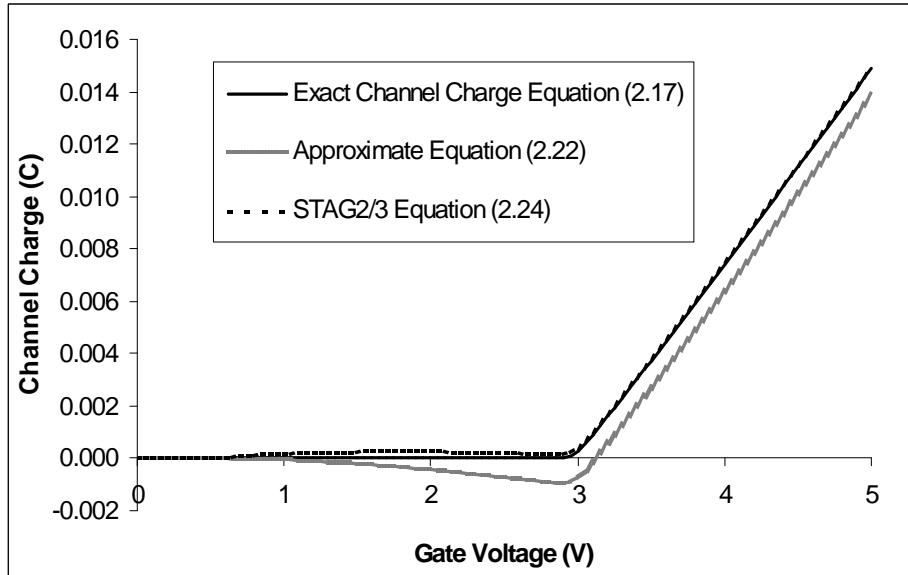

| 2.3 | Comparison of two channel charge approximation methods ( $V_{DS} = 1.8$ ) . .                                                                                                                                                                                                                 | 20 |

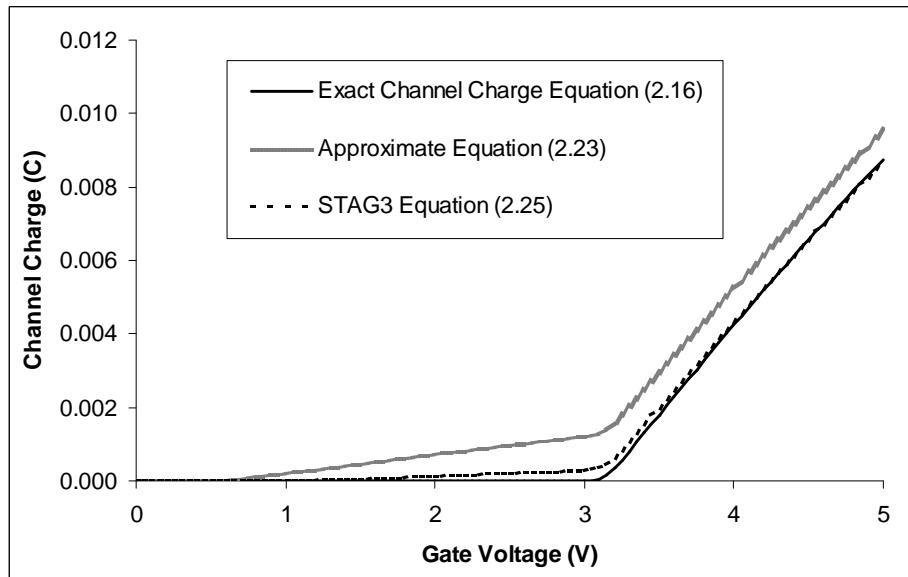

| 2.4 | Comparison of two channel charge approximation methods, with polysilicon depletion included ( $V_{DS} = 1.8$ ) . . . . .                                                                                                                                                                      | 20 |

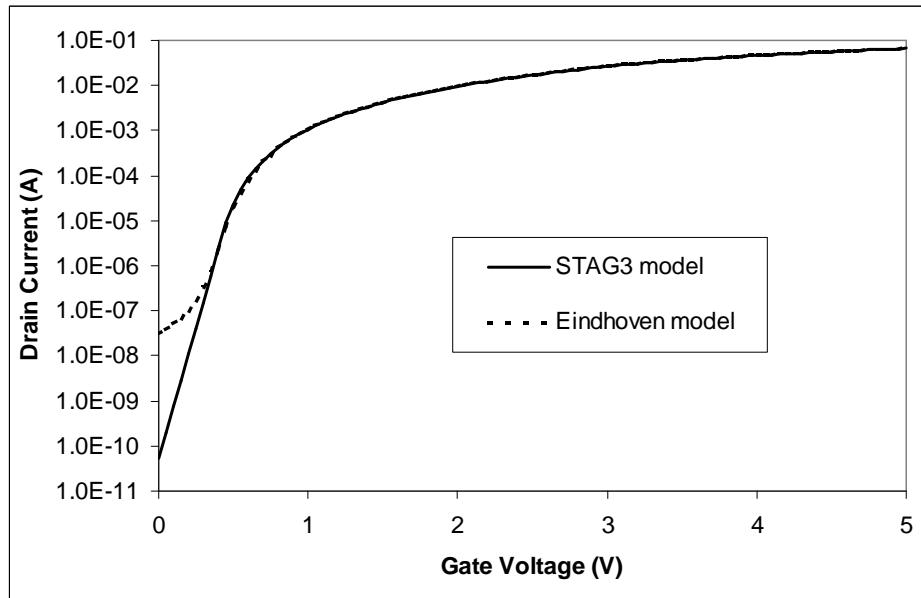

| 2.5 | Comparison of subthreshold characteristics using STAG3 and Eindhoven models. It can be seen that the Eindhoven model gives a non-physical subthreshold slope. . . . .                                                                                                                         | 27 |

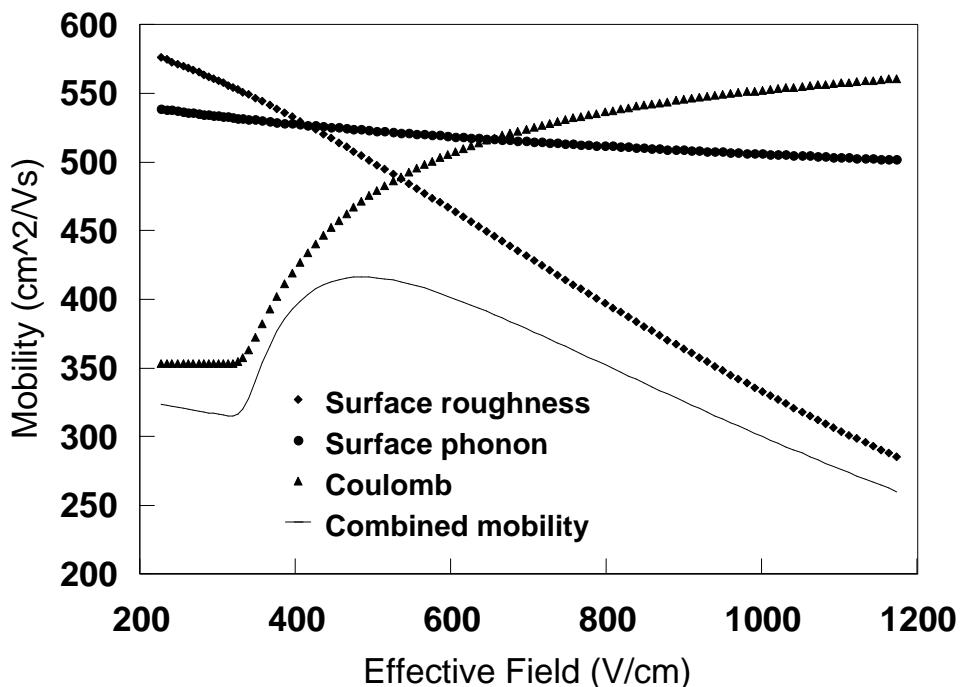

| 3.1 | Graph showing functional dependencies of different scattering mechanisms on effective vertical electric field . . . . .                                                                                                                                                                       | 31 |

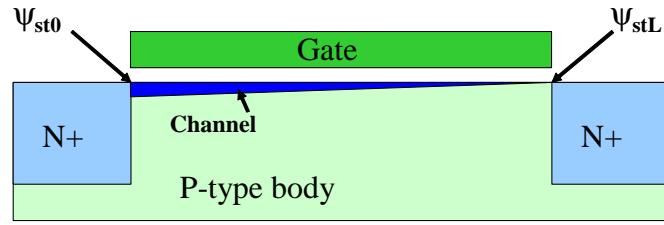

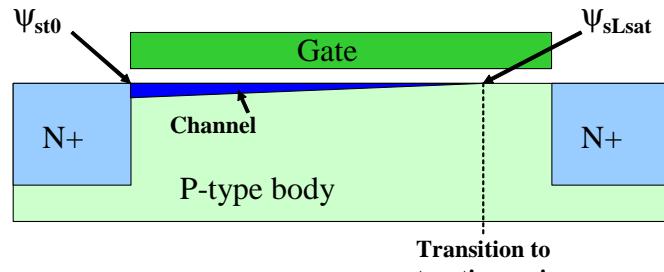

| 4.1 | Representation of a MOSFET a) in the linear regime, with the inversion channel extending all the way to the drain terminal, and b) in saturation, with the channel terminating at the transition to the saturation region. . .                                                                | 44 |

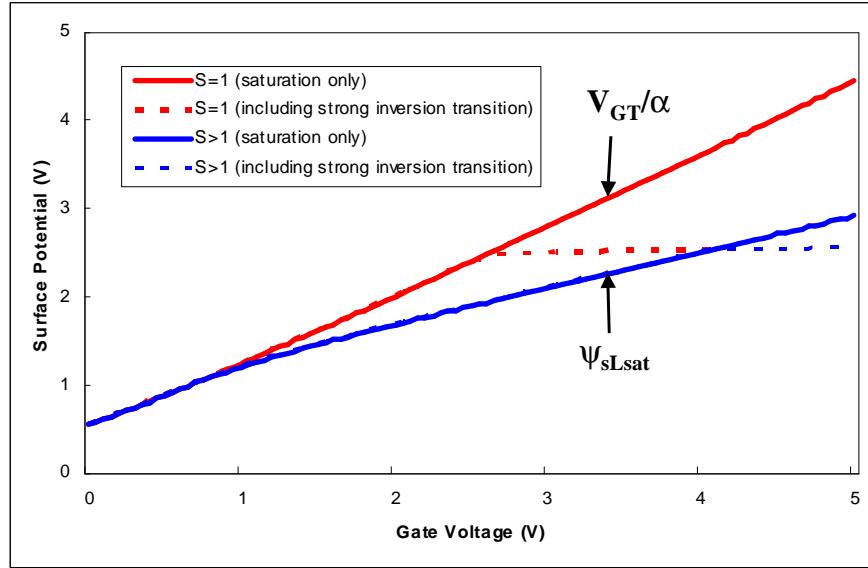

| 4.2 | Plots of surface potential against gate voltage, with (red line) and without (blue line) the effects of velocity saturation. Note that the difference is only seen outside strong inversion - at the appropriate value of gate voltage, both curves transition into the dotted lines. . . . . | 46 |

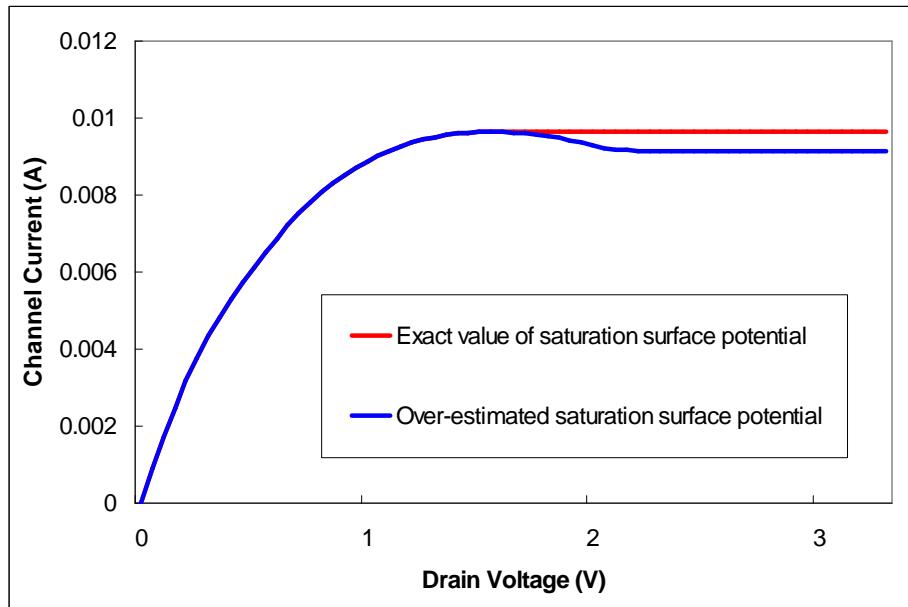

| 4.3 | Plot of channel current against gate voltage, showing the non-physical behaviour that occurs if the saturation surface potential is overestimated. .                                                                                                                                          | 50 |

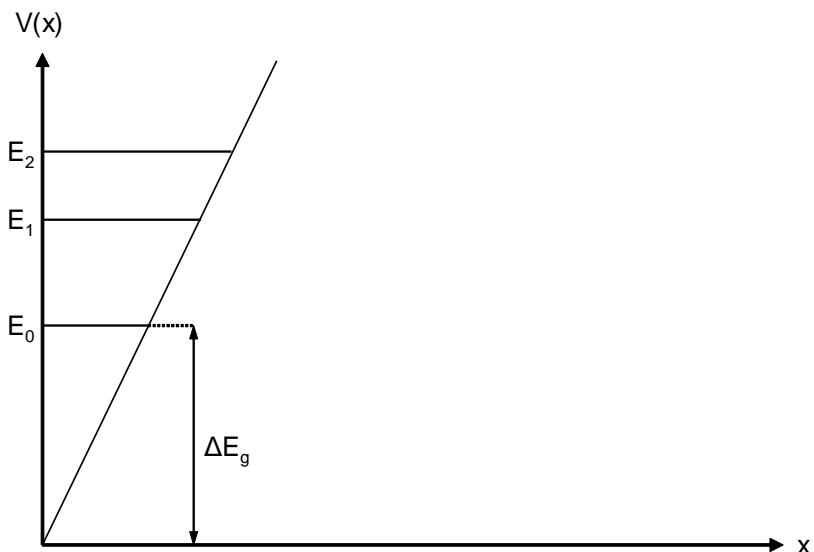

| 5.1 | Representation of a quantum well formed by strong conduction band-bending close to the silicon-oxide interface. The lowest three quantised energy levels are also shown. . . . .                                                                                                              | 56 |

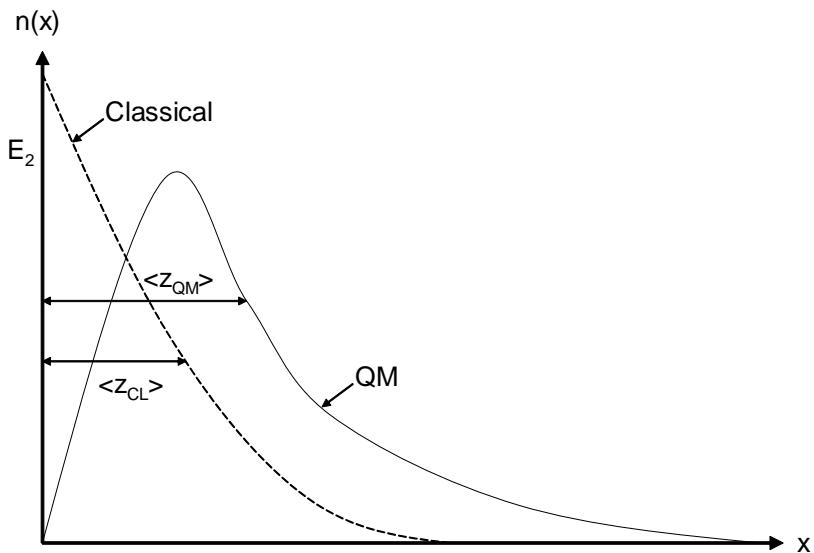

| 5.2 | Comparison of the classical and quantum mechanical distribution of inversion layer electrons as a function of depth into the silicon. $z_{CL}$ and $z_{QM}$ give the average distance of electrons from the silicon-oxide interface in each case. . . . .                                     | 57 |

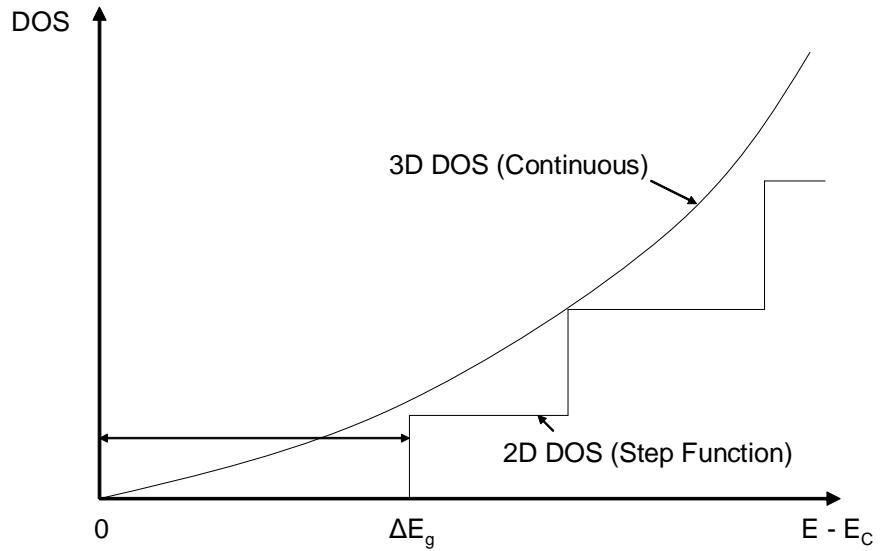

| 5.3 | Representation of the density of states (DOS) for 2D and 3D electron distributions . . . . .                                                                                                                                                                                                  | 59 |

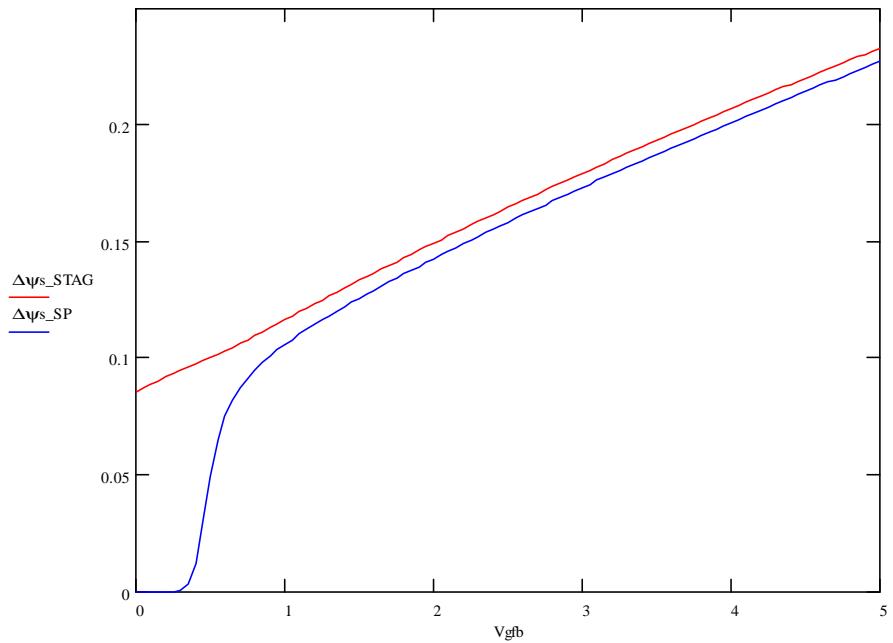

| 5.4 | Comparison of $\Delta V$ for the STAG3 and PSP models. Although there is close matching between the two expressions when equivalent parameter values are used, PSP displays more physical behaviour in that $\Delta V$ moves towards zero outside of the strong inversion regime. . . . .     | 64 |

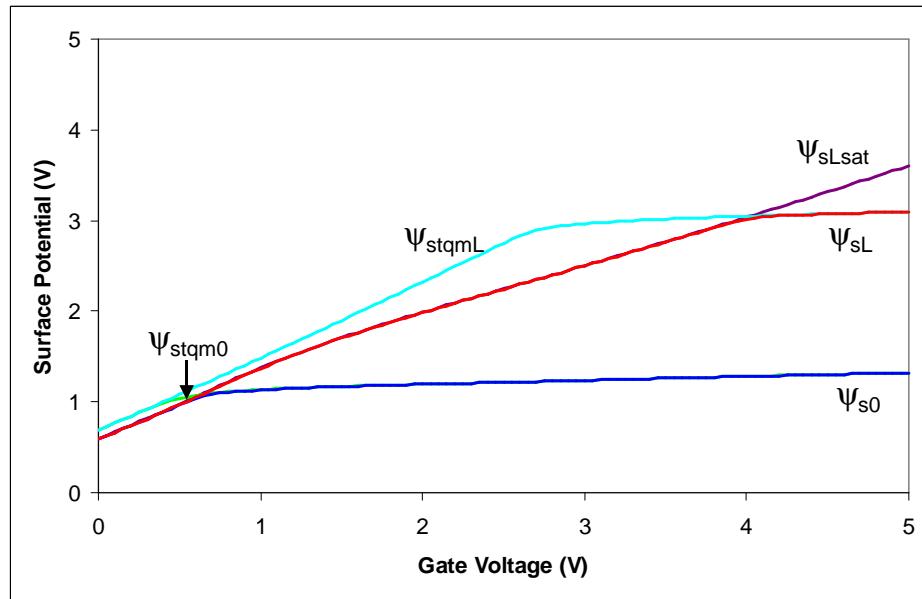

| 5.5 | Graphical plot of the mathematical transformations used to obtain $\psi_{s0}$ and $\psi_{sL}$ ( $V_{DS} = 1.8V$ ) . . . . .                                                                                                                                                                   | 64 |

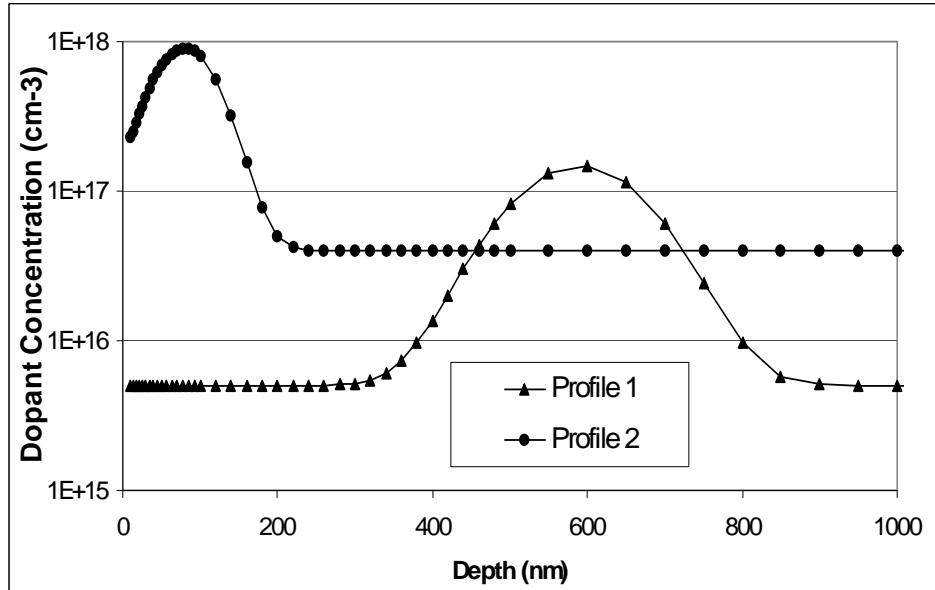

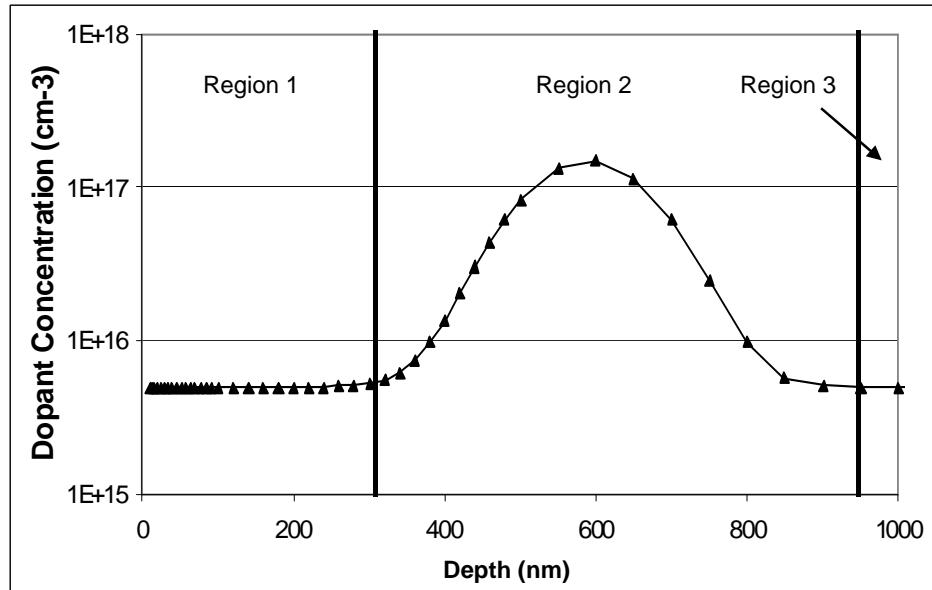

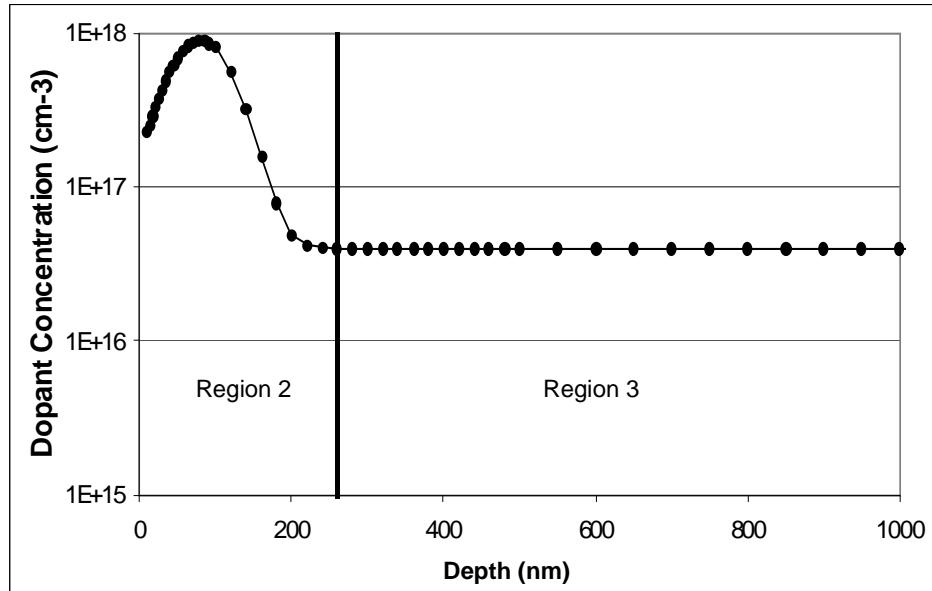

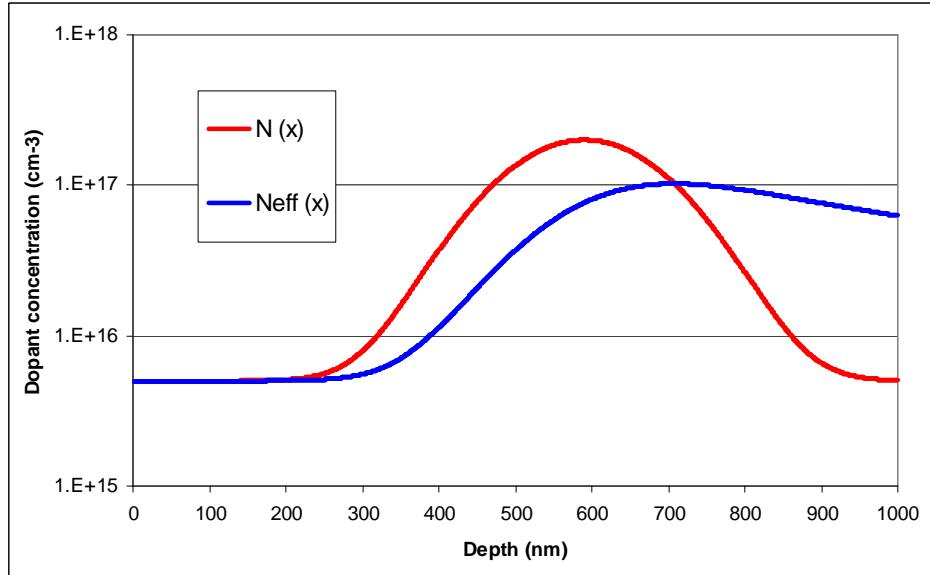

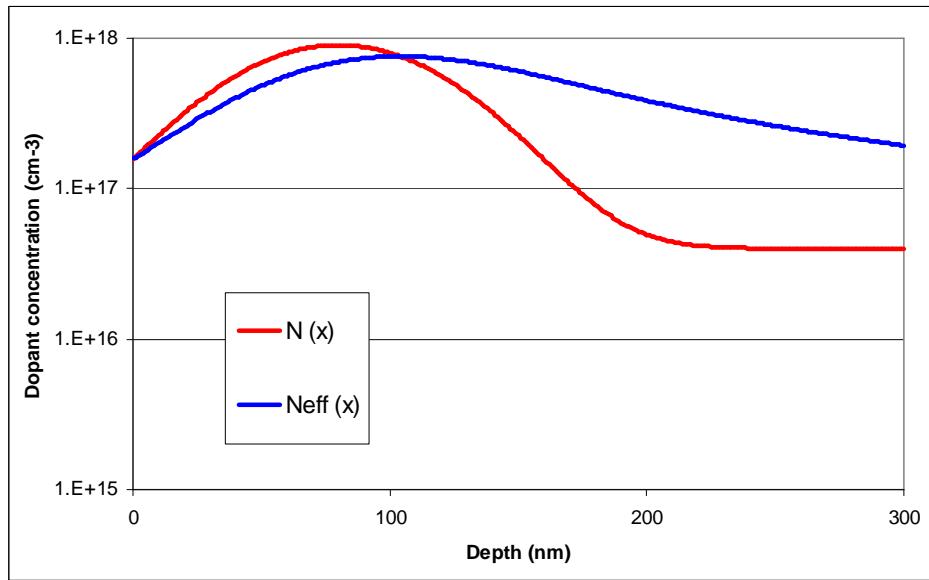

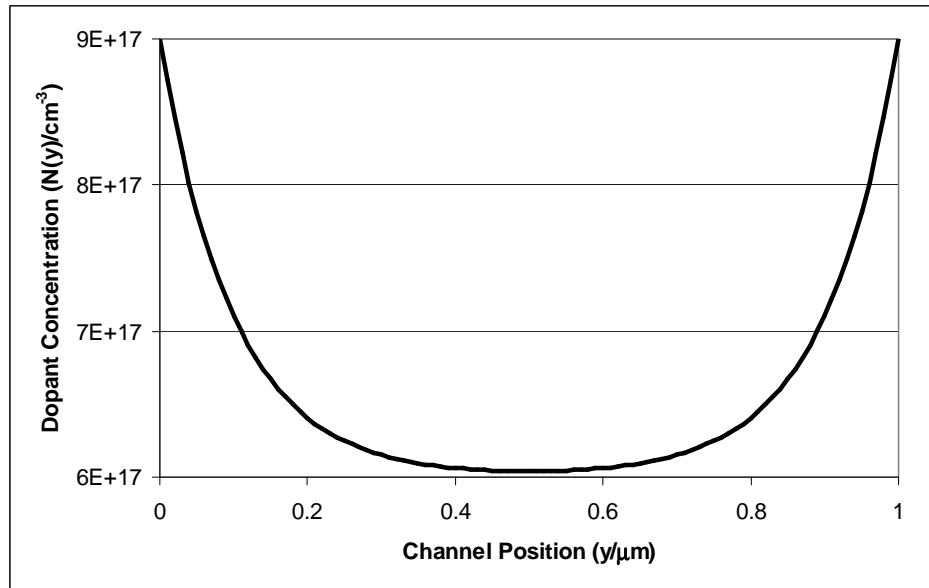

| 6.1 | Two example dopant profiles. Profile 1: $R_p = 100nm$ , $\Delta R_p = 590nm$ , $N_{max} = 2 \times 10^{17}cm^{-3}$ , $N_0 = 5 \times 10^{15}cm^{-3}$ . Profile 2: $R_p = 80nm$ , $\Delta R_p = 40nm$ , $N_{max} = 9 \times 10^{17}cm^{-3}$ , $N_0 = 4 \times 10^{16}cm^{-3}$ . . . . .        | 68 |

| 6.2 | Profile 1, showing 3 distinct modelling regions. . . . .                                                                                                                                                                                                                                      | 69 |

|      |                                                                                                                                                                                                                                               |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.3  | Profile 2, showing 2 distinct modelling regions (no Region 1). . . . .                                                                                                                                                                        | 70  |

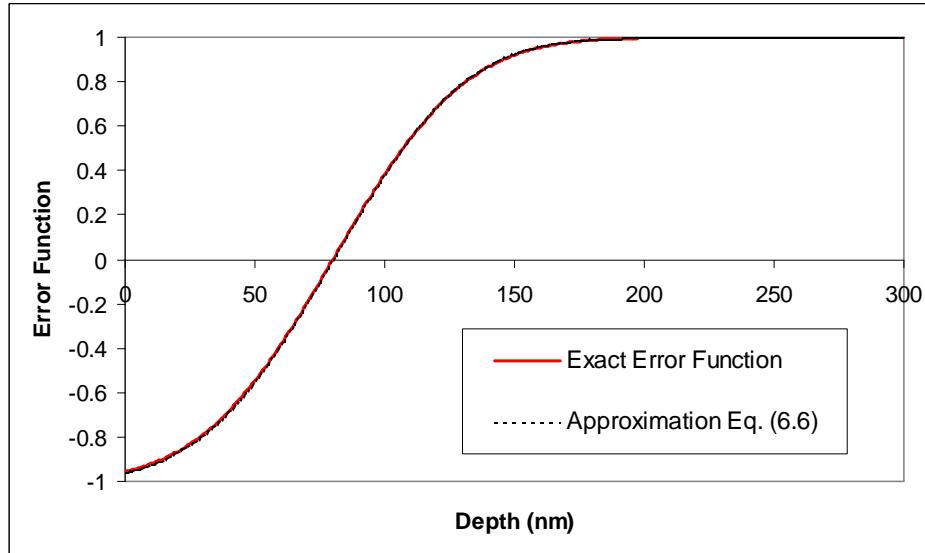

| 6.4  | Exact and approximate error functions expressions, plotted vs increasing depletion depth. $R_p = 80\text{nm}$ , $\Delta R_p = 40\text{nm}$ , $N_{max} = 9 \times 10^{17}\text{cm}^{-3}$ , $N_0 = 4 \times 10^{16}\text{cm}^{-3}$ . . . . .    | 72  |

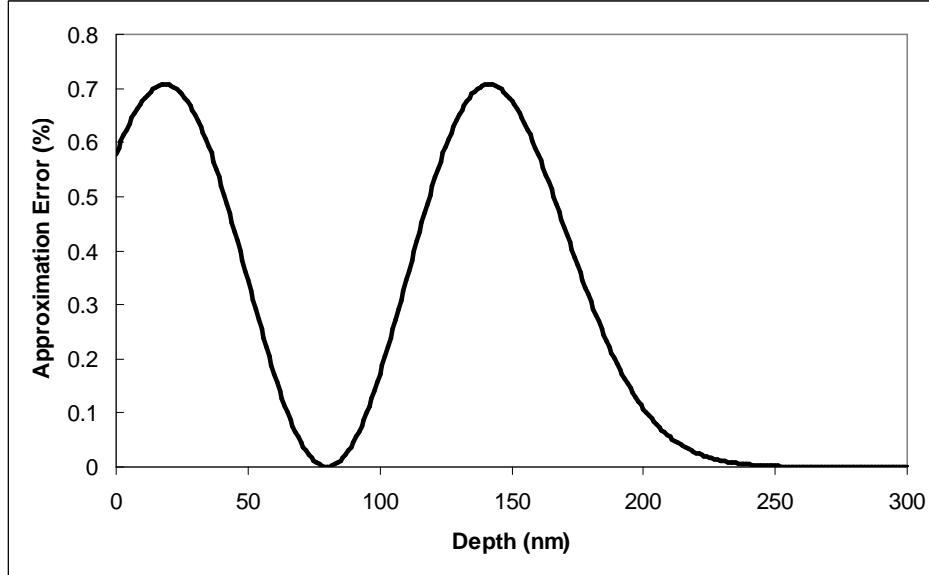

| 6.5  | Percentage error of the approximate solution shown in Fig. 6.4. . . . .                                                                                                                                                                       | 73  |

| 6.6  | True doping profile, and effective doping profile corresponding to Equation (6.9), for Profile 1. . . . .                                                                                                                                     | 74  |

| 6.7  | True doping profile, and effective doping profile corresponding to Equation (6.9), for Profile 2. . . . .                                                                                                                                     | 75  |

| 6.8  | Matching of polynomial expression to effective doping profile (Profile 1). . .                                                                                                                                                                | 75  |

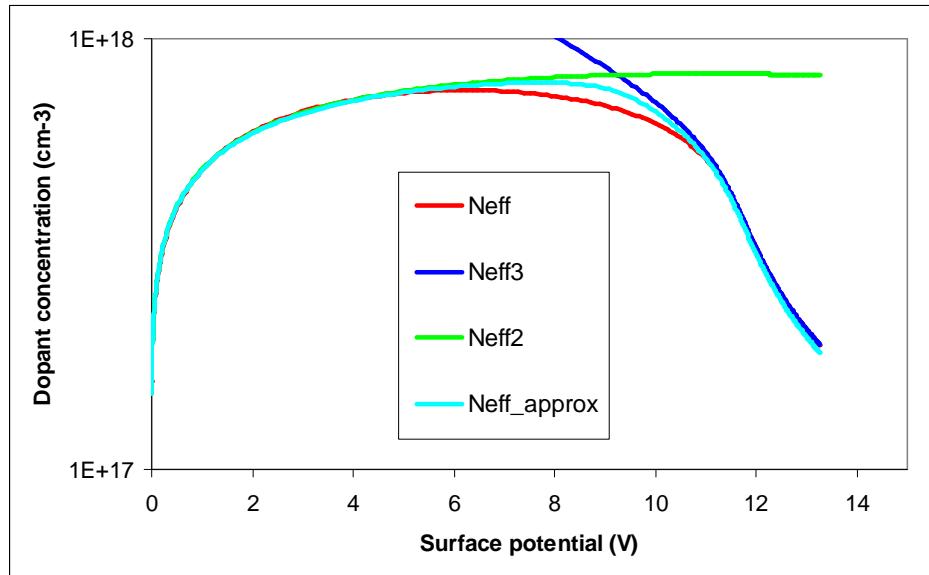

| 6.9  | Matching of polynomial expression to effective doping profile (Profile 2). .                                                                                                                                                                  | 76  |

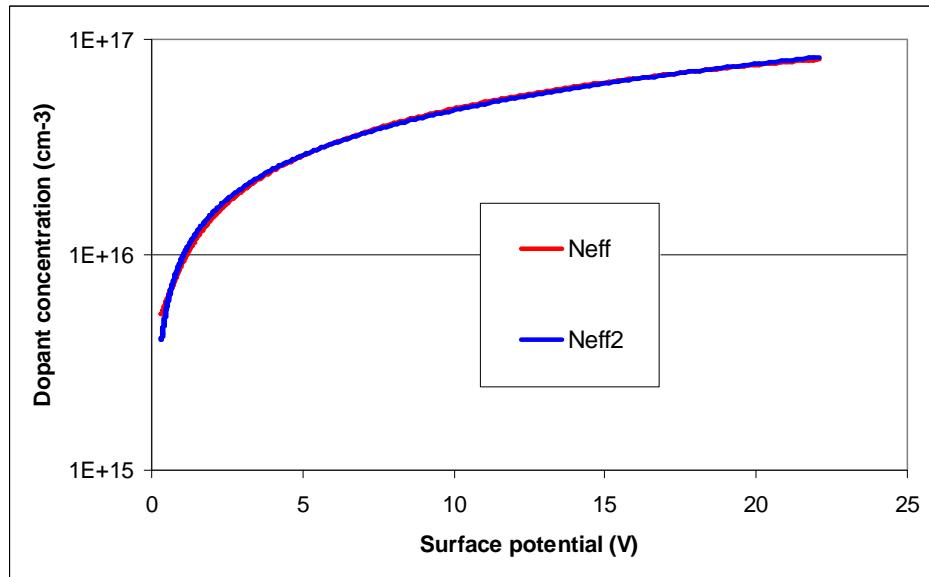

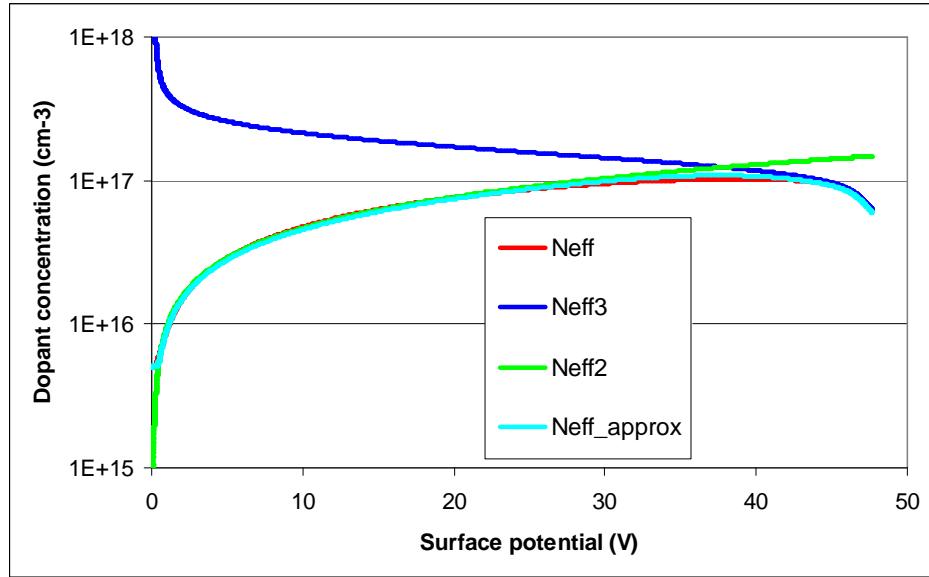

| 6.10 | Comparison of exact and approximate effective doping profiles for Profile 1.                                                                                                                                                                  | 77  |

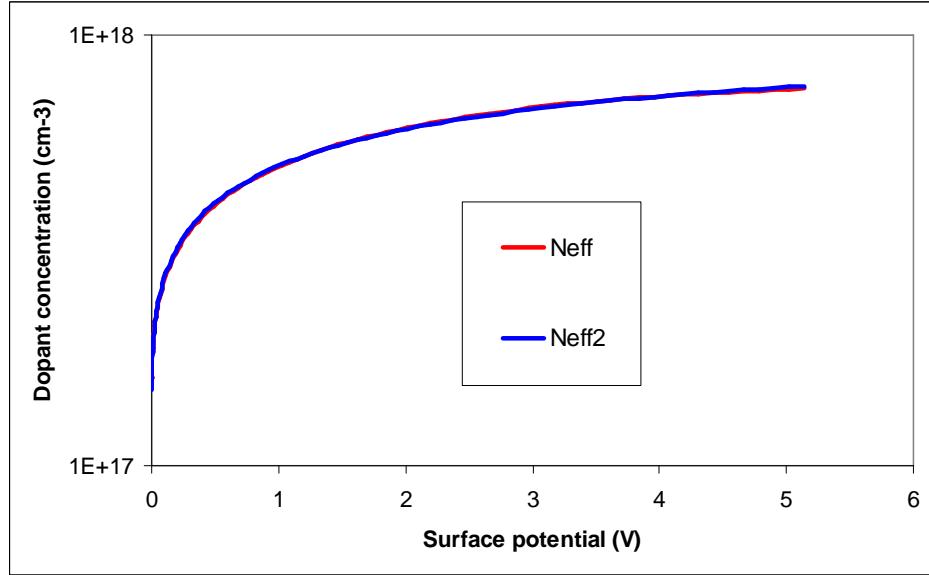

| 6.11 | Comparison of exact and approximate effective doping profiles for Profile 2.                                                                                                                                                                  | 77  |

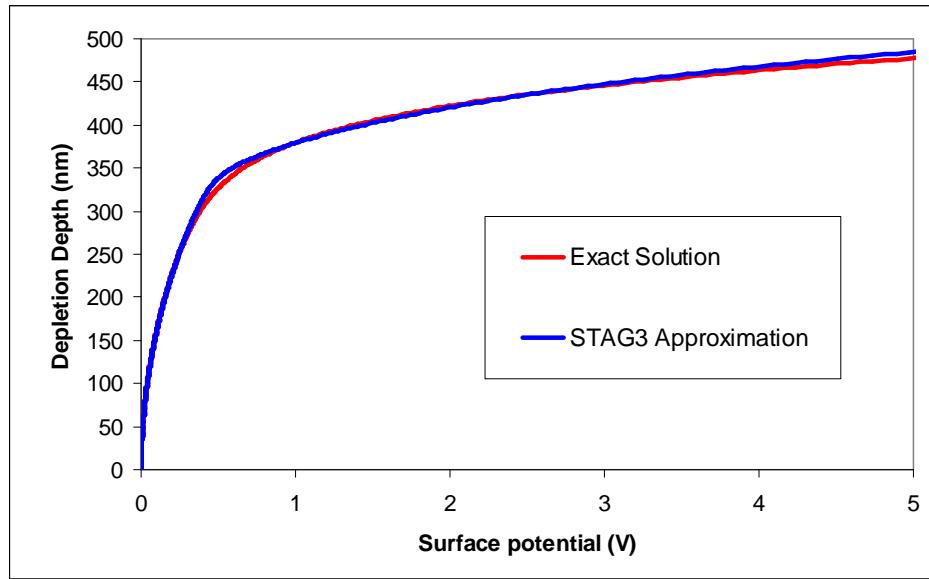

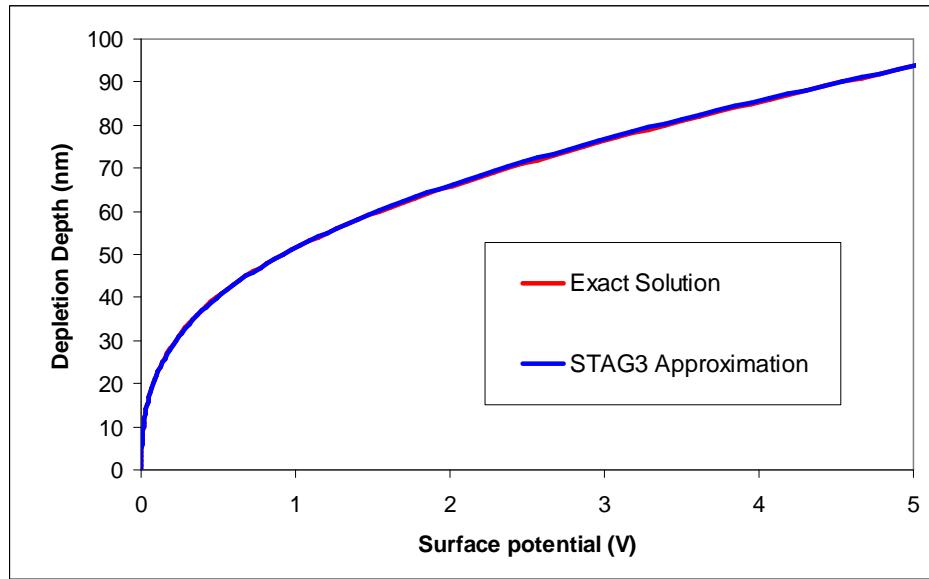

| 6.12 | Comparison of exact and approximate $x_d$ - $\psi_s$ relation for Profile 1. . . . .                                                                                                                                                          | 78  |

| 6.13 | Comparison of exact and approximate $x_d$ - $\psi_s$ relation for Profile 2. . . . .                                                                                                                                                          | 78  |

| 6.14 | Lateral doping profile from applying Equation (6.31), with dopant pile-up at the source and drain. . . . .                                                                                                                                    | 82  |

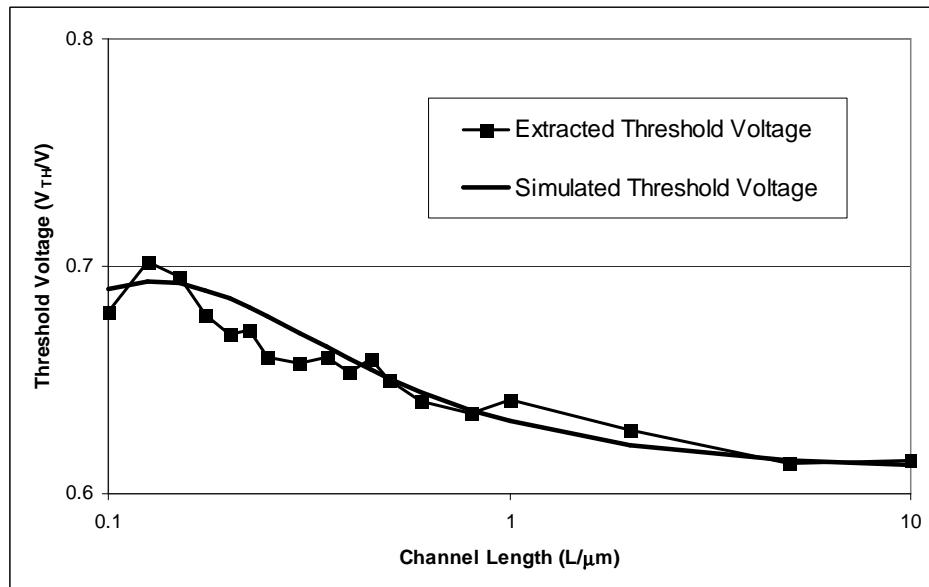

| 6.15 | Measured and simulated $V_{TH}$ vs L plots, showing the fitting capability of the new STAG3 RSCE model. . . . .                                                                                                                               | 82  |

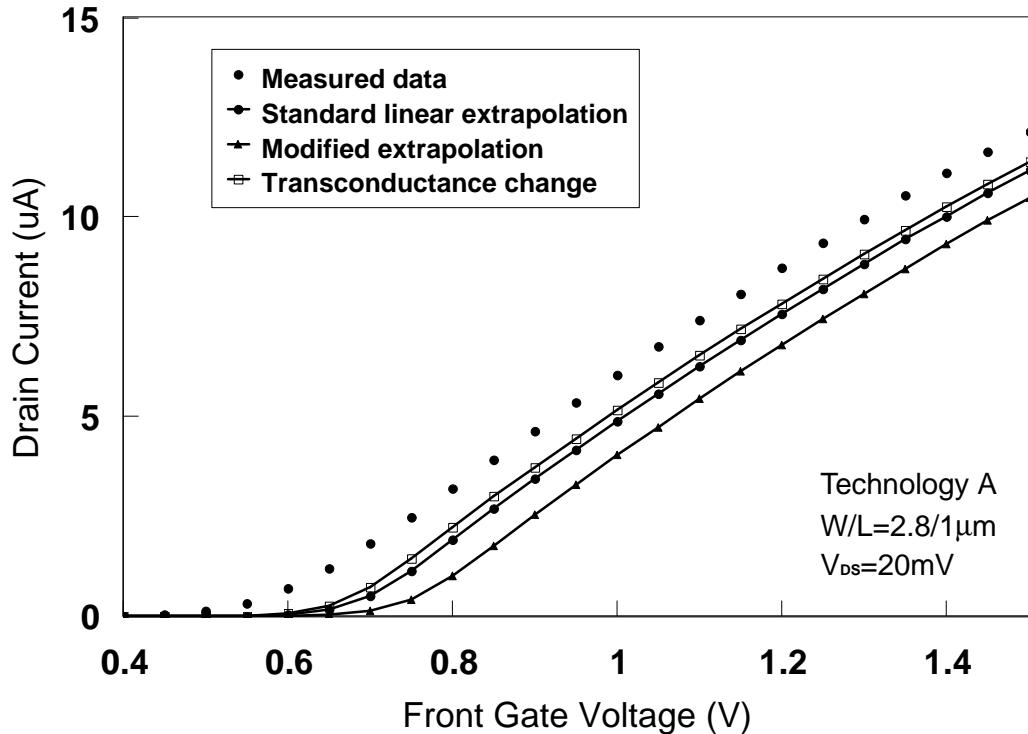

| 6.16 | Drain current versus front gate voltage, simulated using unmodified threshold voltages from three different extraction methods, and compared with measured data. . . . .                                                                      | 84  |

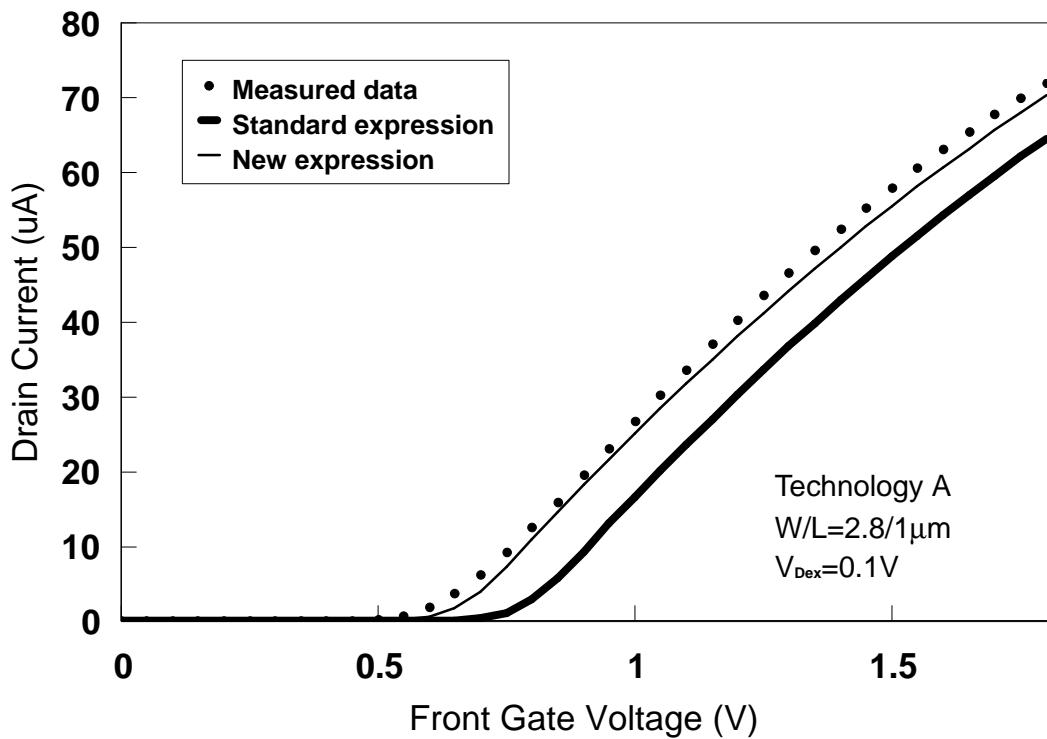

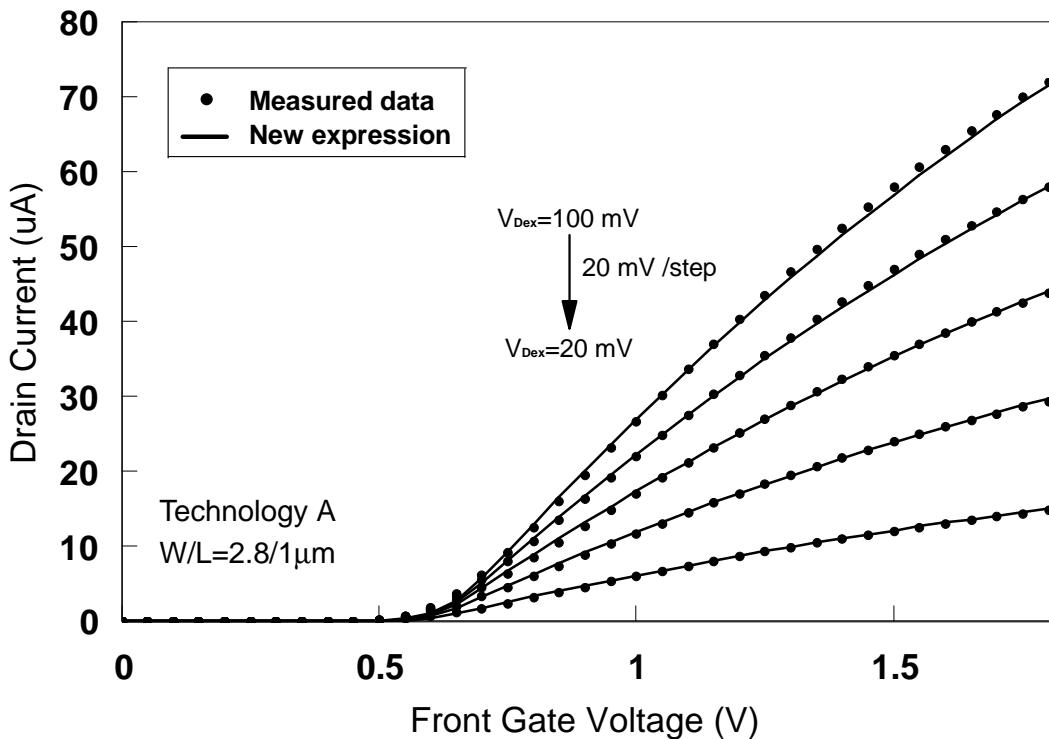

| 6.17 | Comparison of measured data with simulation results using new and standard threshold voltage expressions (Technology A). Default value for $\delta_0$ of 0.05 is used. . . . .                                                                | 88  |

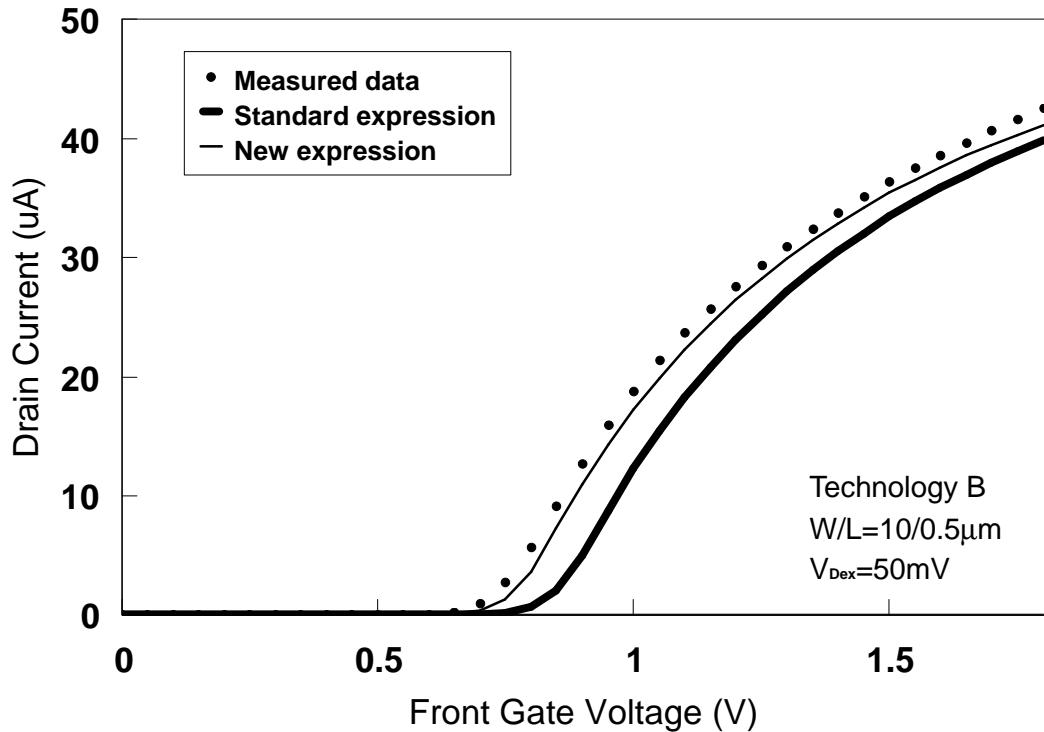

| 6.18 | Comparison of measured data with simulation results using new and standard threshold voltage expressions (Technology B). Default value for $\delta_0$ of 0.05 is used. . . . .                                                                | 89  |

| 6.19 | Comparison of measured data with simulation results using the new threshold relation, showing accurate relation between extracted threshold voltage and applied drain voltage. . . . .                                                        | 90  |

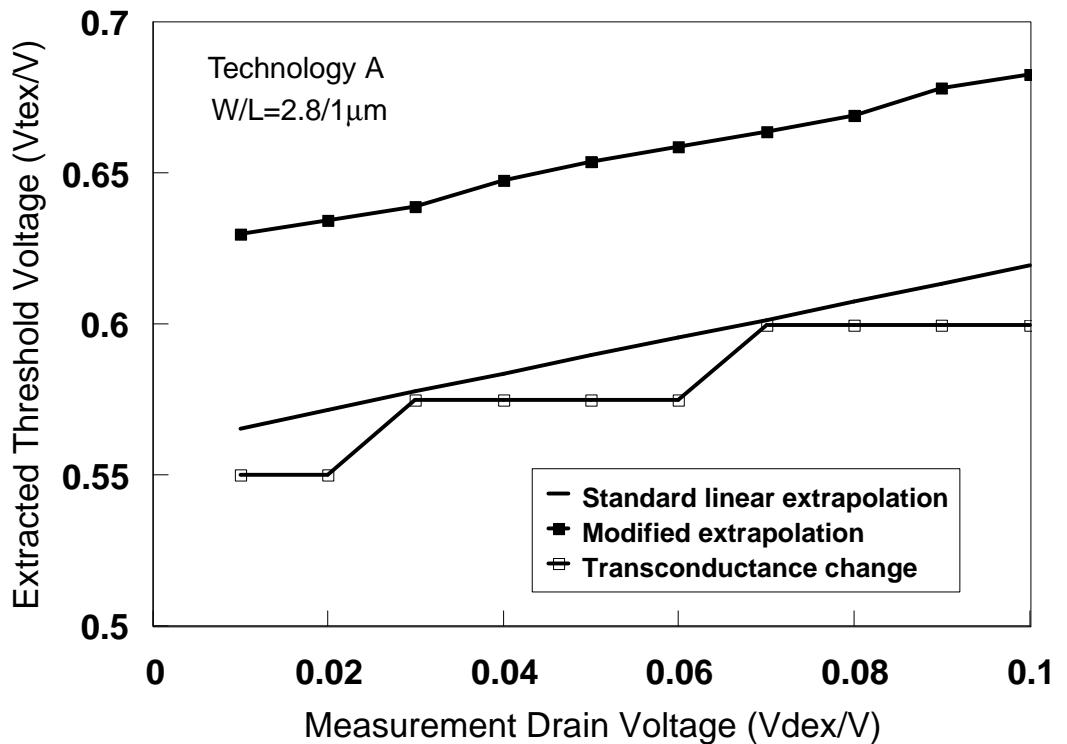

| 6.20 | Variation of measured extracted threshold voltage $V_{Tex}$ with drain voltage $V_{Dex}$ , up to $V_{Dex}=0.1\text{V}$ . Three different extraction methods were used. . .                                                                    | 91  |

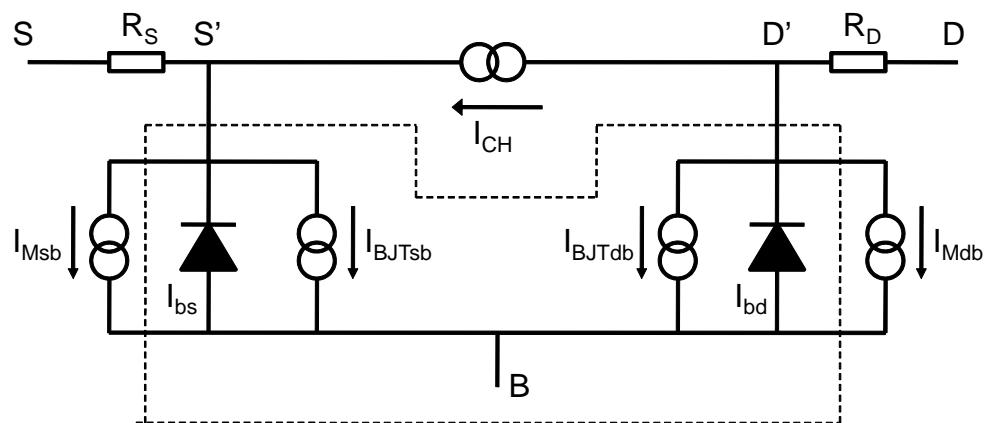

| 7.1  | Extrinsic parasitic components included in the STAG3 model. . . . .                                                                                                                                                                           | 94  |

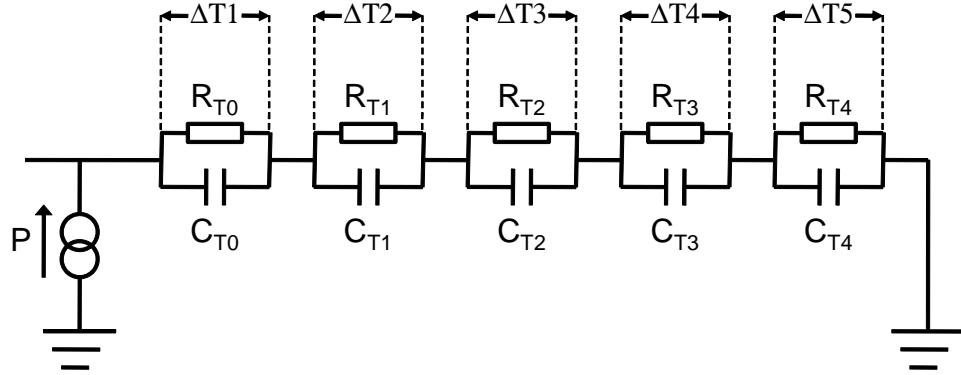

| 7.2  | Thermal sub-circuit for STAG3; up to 5 thermal time constants can be modelled. . . . .                                                                                                                                                        | 97  |

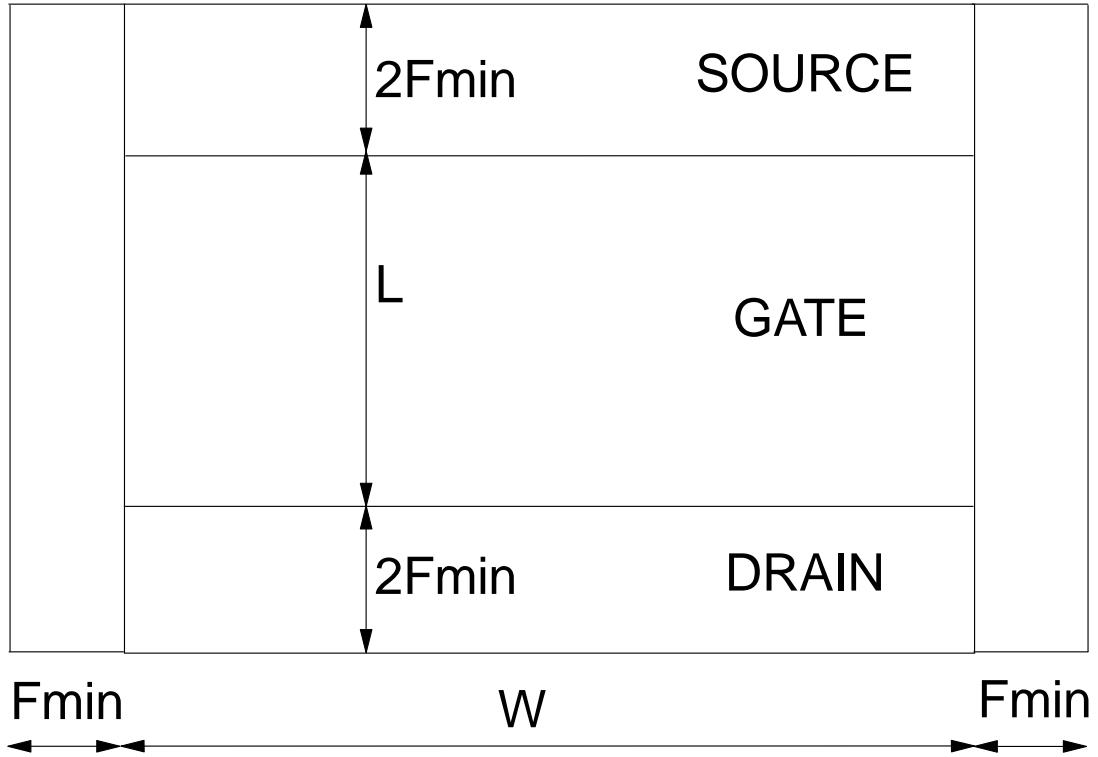

| 7.3  | Approximate scheme for calculating the effective thermal area of an SOI device. . . . .                                                                                                                                                       | 98  |

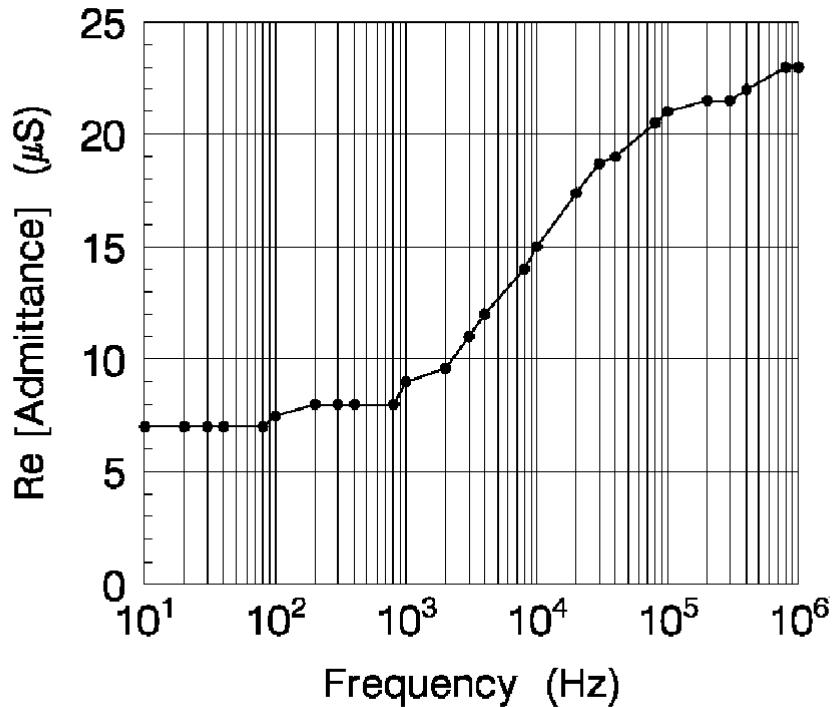

| 8.1  | Measured small-signal output conductance versus frequency for a floating body SOS device biased in saturation, below the onset of kink (W/L=20/3 $\mu\text{m}$ , $V_{GS}=2\text{V}$ , $V_{DS}=2\text{V}$ ). Taken from Reference [9]. . . . . | 110 |

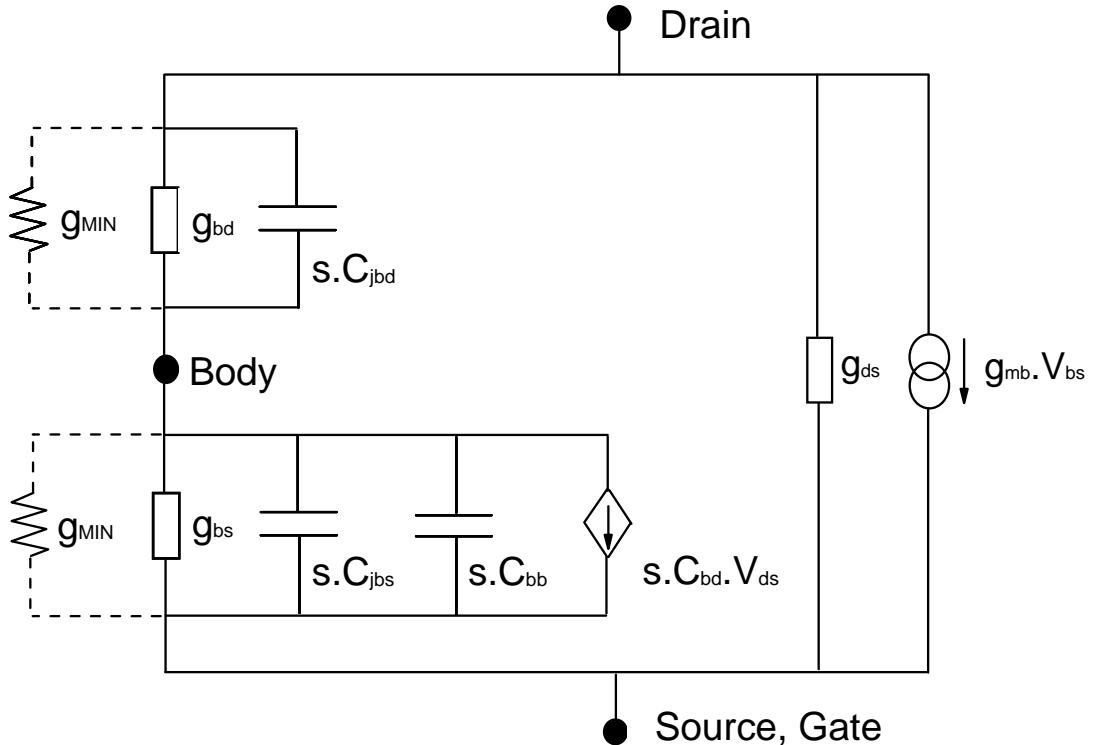

| 8.2  | Equivalent small-signal circuit for a floating body SOI MOSFET with the source and front gate tied to AC ground. . . . .                                                                                                                      | 111 |

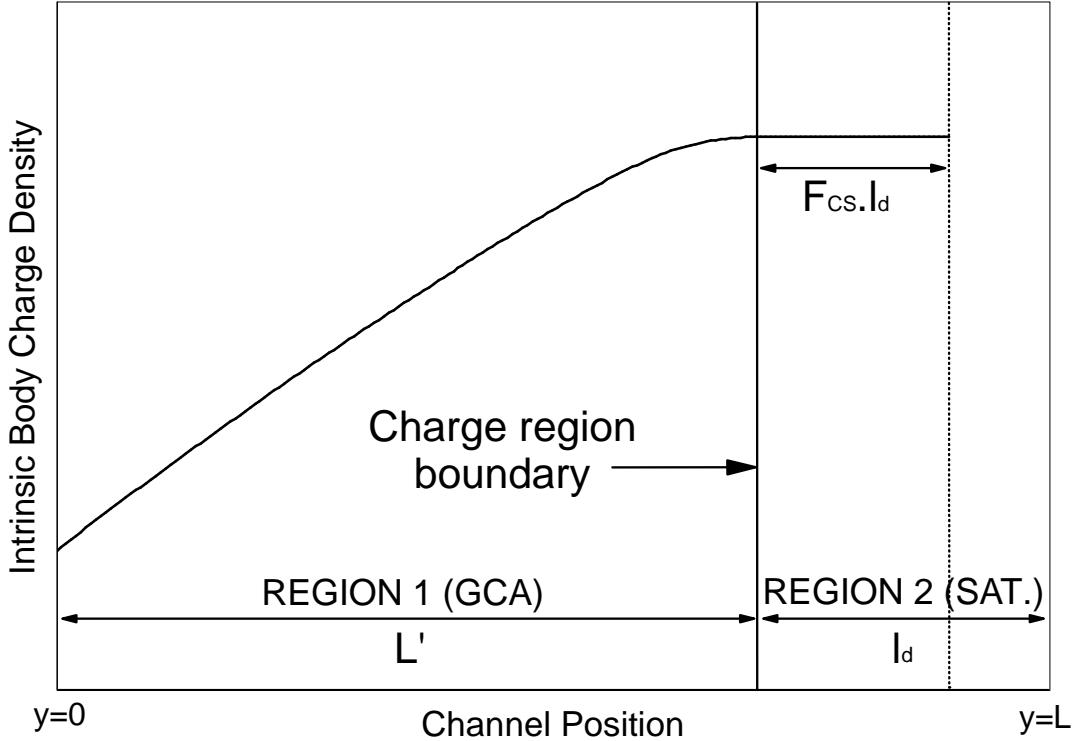

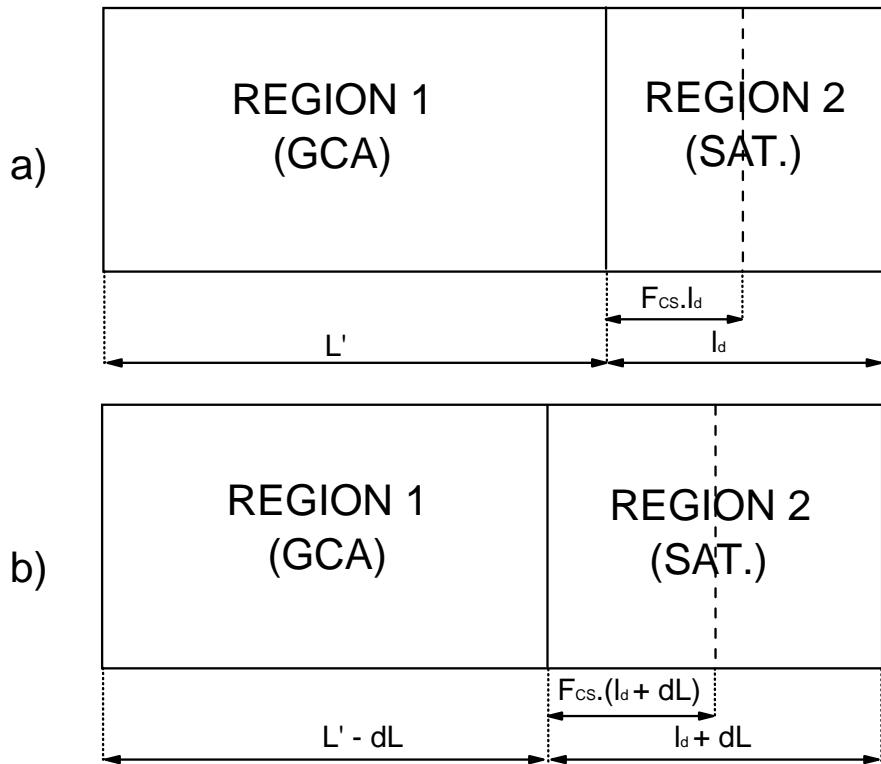

| 8.3  | Pictorial representation of new body charge model, showing the role of the new model parameter $F_{CS}$ . At the boundary between Regions 1 and 2, the intrinsic body charge density is continuous. . . . .                                   | 114 |

| 8.4  | GCA and saturation region length for a) drain voltage $V_{ds}$ and b) drain voltage $V_{ds}+dV_{ds}$ . . . . .                                                                                                                                | 115 |

|      |                                                                                                                                                                                                                                                                                                                                 |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

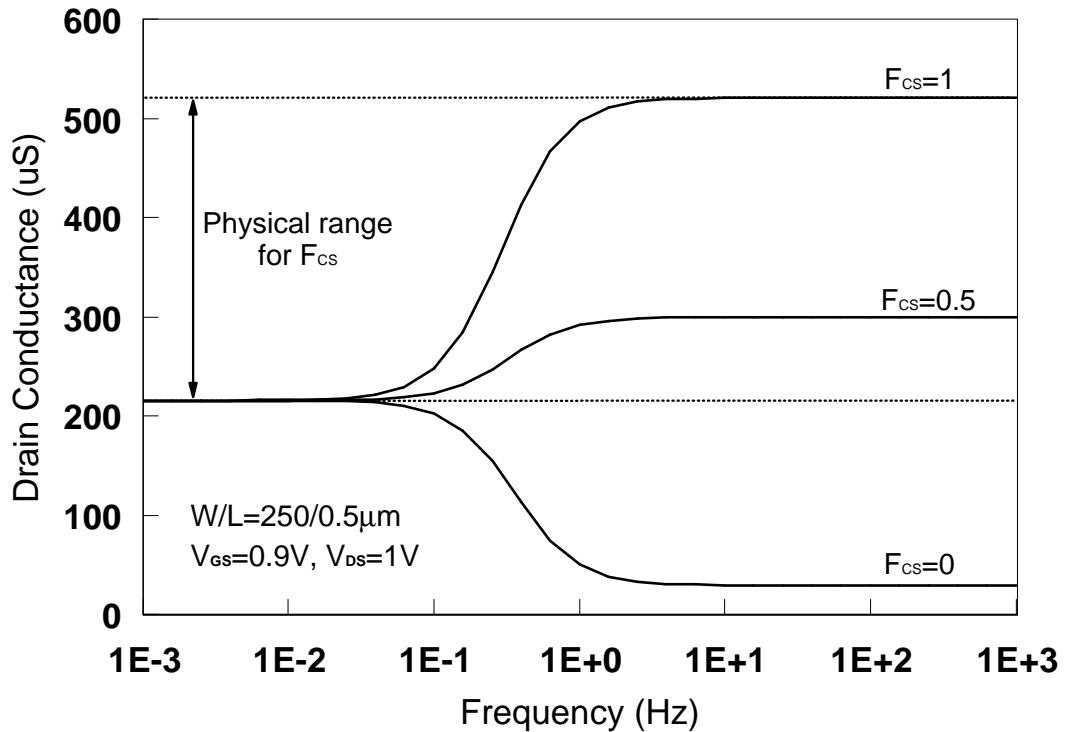

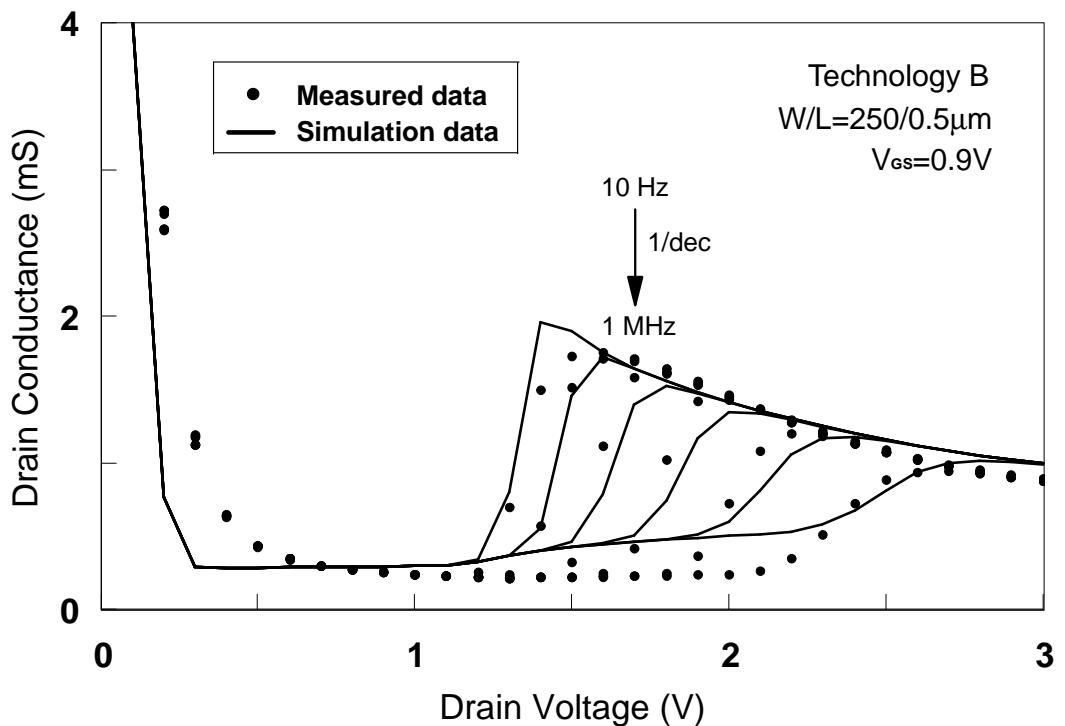

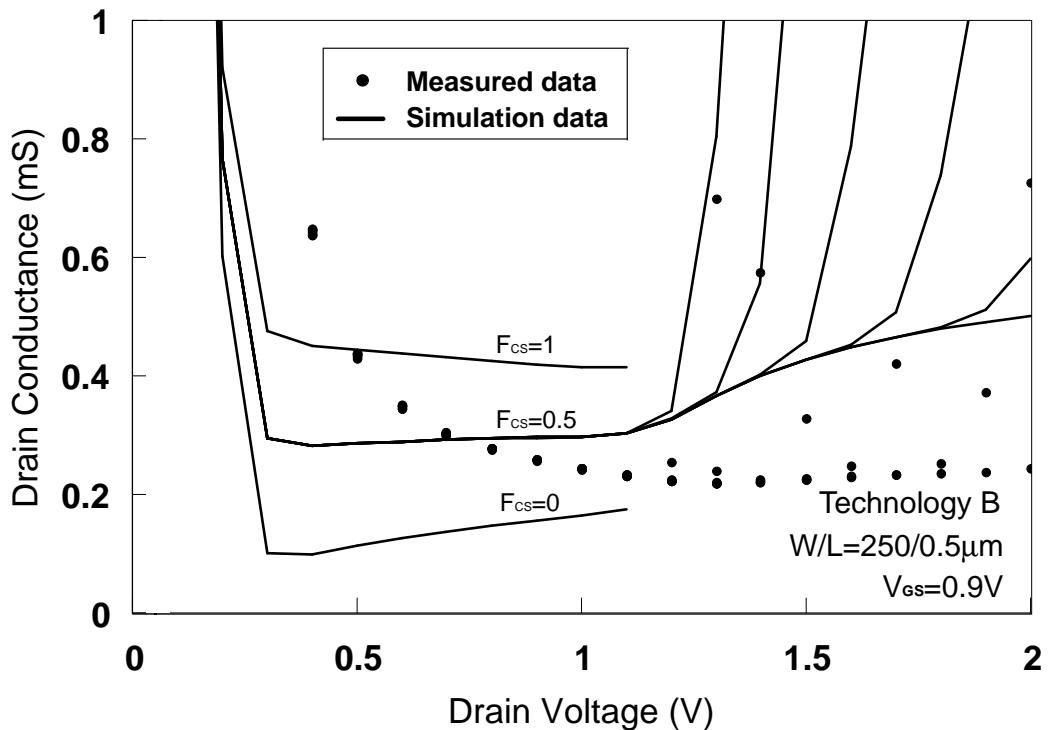

| 8.5  | Comparison of simulated drain conductance-frequency profiles for different values of charge sharing factor $F_{CS}$ . The dotted lines indicate the physical range of $F_{CS}$ , over which the correct drain conductance profile is observed.                                                                                  | 117 |

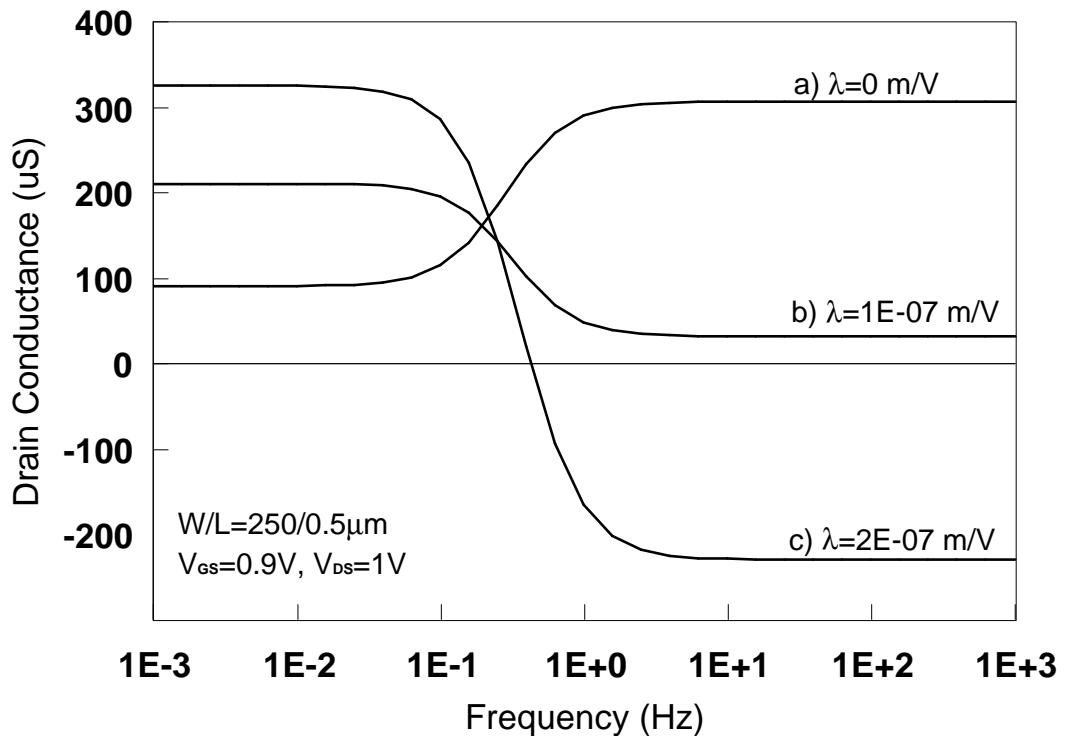

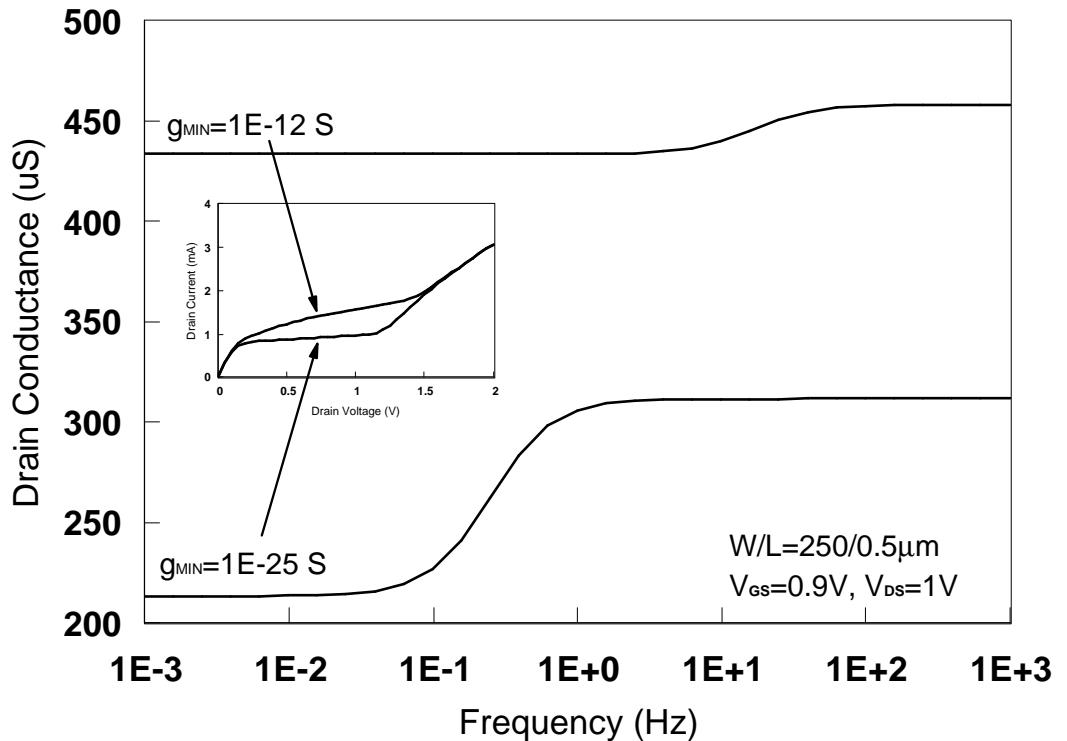

| 8.6  | Variation of simulated drain conductance with channel length modulation parameter $\lambda$ , for $F_{CS}=0$ . When $\lambda$ is set to zero, a physically correct drain conductance profile is observed. . . . .                                                                                                               | 118 |

| 8.7  | Simulated small-signal drain conductance versus drain bias, compared with measured data. New charge sharing factor is used to model saturation body charge, with $F_{CS}$ set to 0.5 for the simulation data. . . . .                                                                                                           | 119 |

| 8.8  | Plot of the small-signal drain conductance versus drain bias, focusing on the below-kink saturation region. Measured data is compared with simulation data for $F_{CS}=0$ , 0.5, and 1. . . . .                                                                                                                                 | 120 |

| 8.9  | Simulated drain conductance versus frequency, for $g_{MIN} = 10^{-25}$ and $10^{-12} S$ . The inset shows simulated drain current characteristics for the same device and conditions, showing anomalous effect on saturation characteristics of making $g_{MIN}$ comparable in magnitude to physical body conductances. . . . . | 121 |

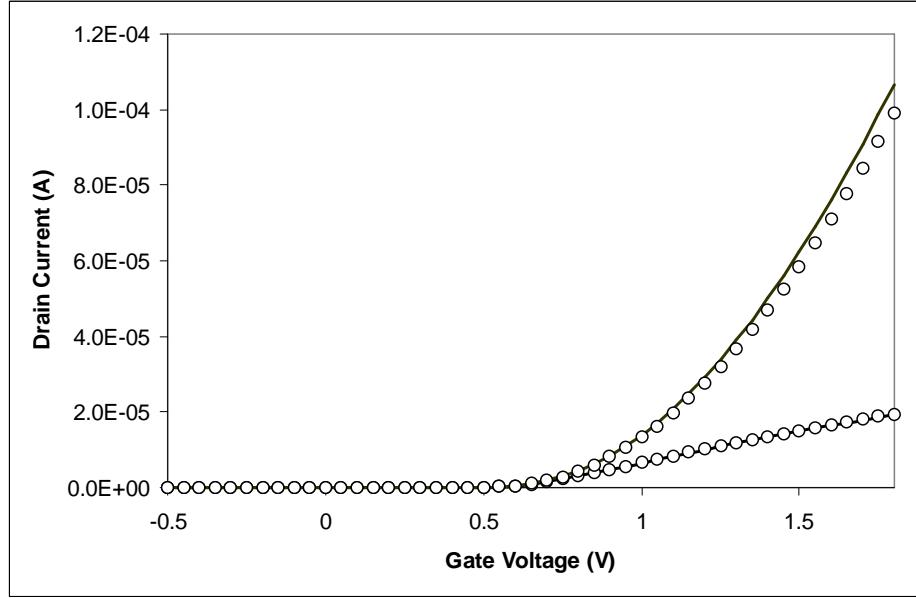

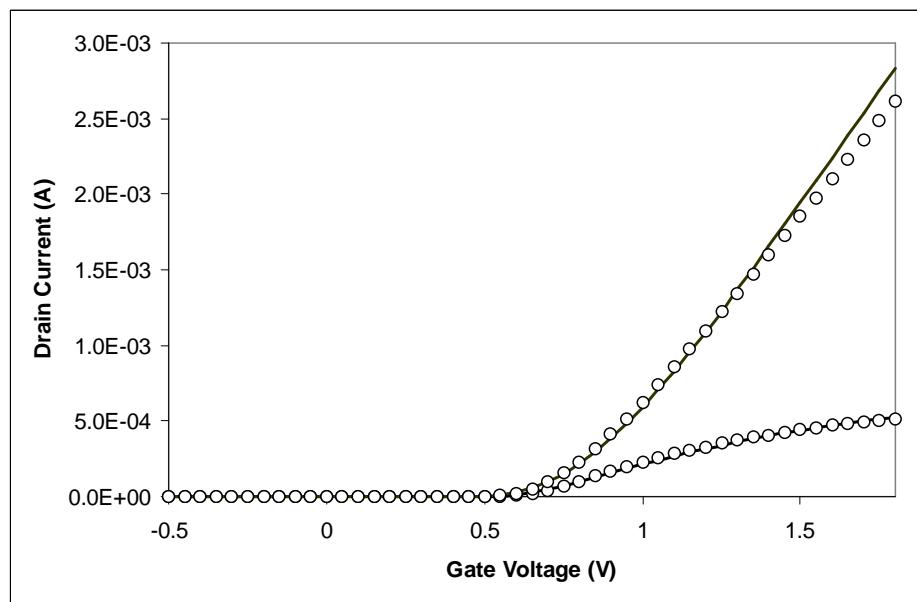

| 9.1  | Drain current versus gate voltage for $V_{DS} = 0.1V$ and $1.8V$ for a $W = 10\mu m$ , $L = 10\mu m$ body tied device. Circles indicate measured values, solid lines indicate simulated results. . . . .                                                                                                                        | 127 |

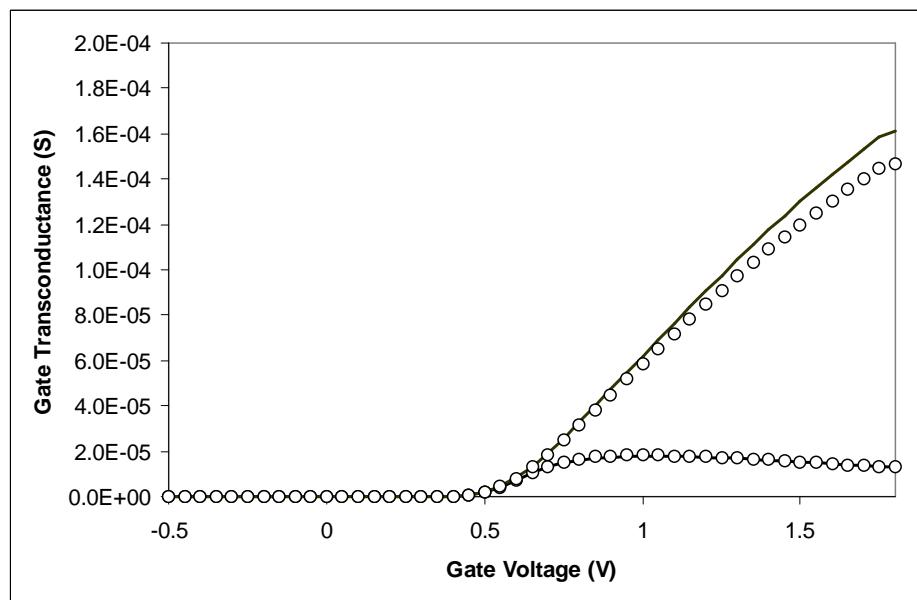

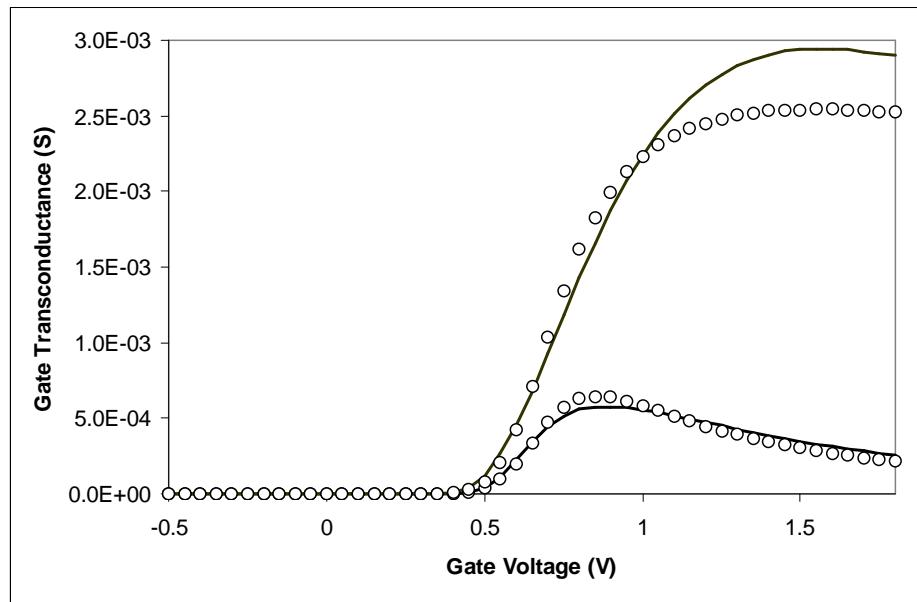

| 9.2  | Gate transconductance versus gate voltage for $V_{DS} = 0.1V$ and $1.8V$ for a $W = 10\mu m$ , $L = 10\mu m$ body tied device. Circles indicate measured values, solid lines indicate simulated results. . . . .                                                                                                                | 128 |

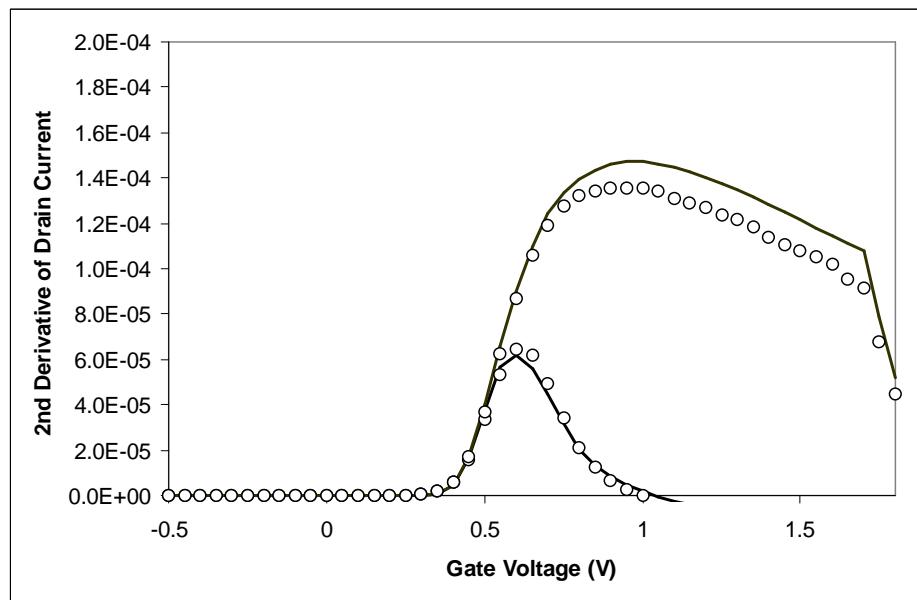

| 9.3  | 2nd derivative of drain current w.r.t. gate voltage versus gate voltage for $V_{DS} = 0.1V$ and $1.8V$ for a $W = 10\mu m$ , $L = 10\mu m$ body tied device. Circles indicate measured values, solid lines indicate simulated results. . . . .                                                                                  | 128 |

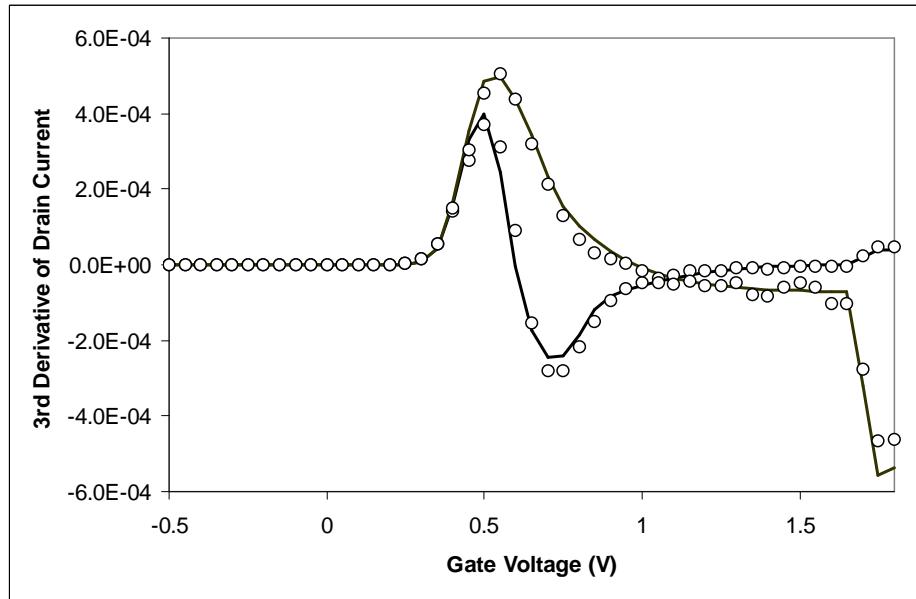

| 9.4  | 3rd derivative of drain current w.r.t. gate voltage versus gate voltage for $V_{DS} = 0.1V$ and $1.8V$ for a $W = 10\mu m$ , $L = 10\mu m$ body tied device. Circles indicate measured values, solid lines indicate simulated results. . . . .                                                                                  | 129 |

| 9.5  | Drain current versus gate voltage for $V_{DS} = 0.1V$ and $1.8V$ for a $W = 10\mu m$ , $L = 0.25\mu m$ body tied device. Circles indicate measured values, solid lines indicate simulated results. . . . .                                                                                                                      | 130 |

| 9.6  | Gate transconductance versus gate voltage for $V_{DS} = 0.1V$ and $1.8V$ for a $W = 10\mu m$ , $L = 0.25\mu m$ body tied device. Circles indicate measured values, solid lines indicate simulated results. . . . .                                                                                                              | 130 |

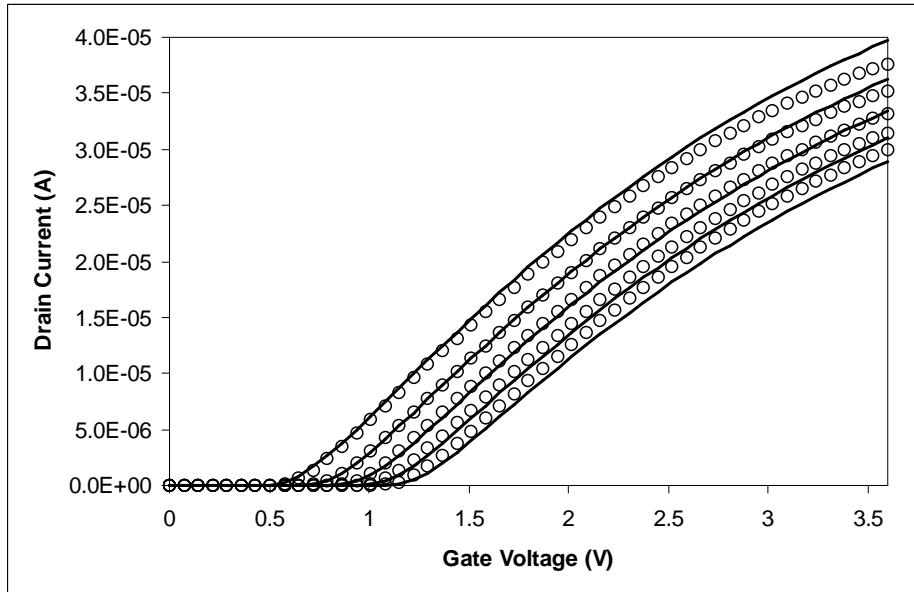

| 9.7  | Drain current versus gate voltage for $V_{DS} = 0.1V$ and $V_{BS} = 0, -0.5, -1.0, -1.5, -2.0$ , and $-2.5V$ for a $W = 50\mu m$ , $L = 50\mu m$ body tied device in Technology B. Circles indicate measured values, solid lines indicate simulated results. . . . .                                                            | 131 |

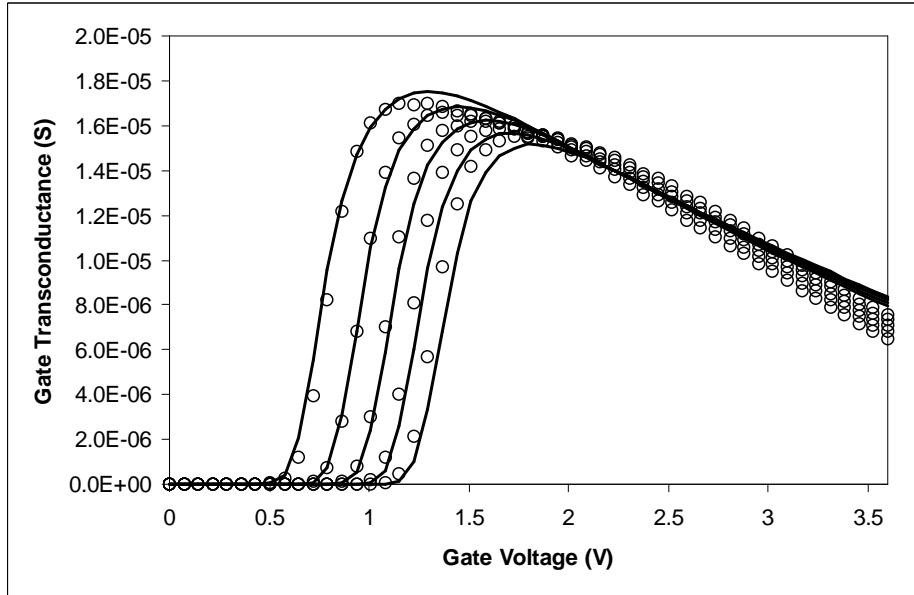

| 9.8  | Gate transconductance versus gate voltage for $V_{DS} = 0.1V$ and $V_{BS} = 0, -0.5, -1.0, -1.5, -2.0$ , and $-2.5V$ for a $W = 50\mu m$ , $L = 50\mu m$ body tied device in Technology B. Circles indicate measured values, solid lines indicate simulated results. . . . .                                                    | 132 |

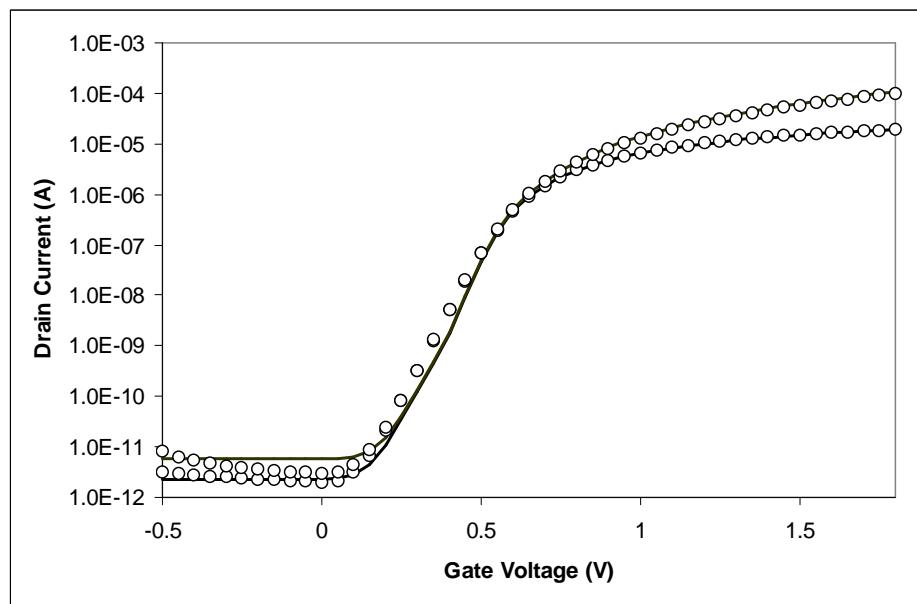

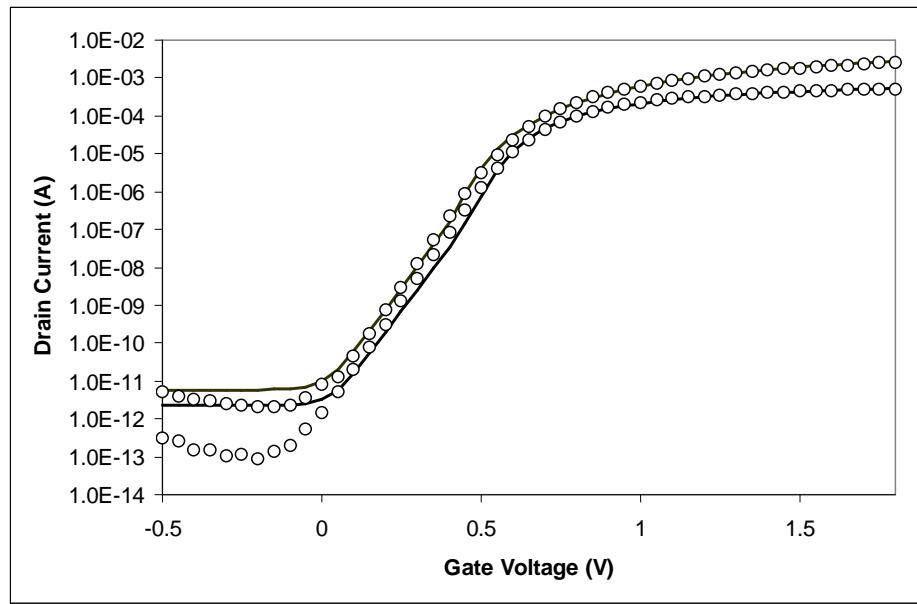

| 9.9  | Subthreshold characteristics for $V_{DS} = 0.1V$ and $1.8V$ for a $W = 10\mu m$ , $L = 10\mu m$ body tied device. Circles indicate measured values, solid lines indicate simulated results. . . . .                                                                                                                             | 133 |

| 9.10 | Subthreshold characteristics for $V_{DS} = 0.1V$ and $1.8V$ for a $W = 10\mu m$ , $L = 0.25\mu m$ body tied device. Circles indicate measured values, solid lines indicate simulated results. . . . .                                                                                                                           | 133 |

|                                                                                                                                                                                                                                                     |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

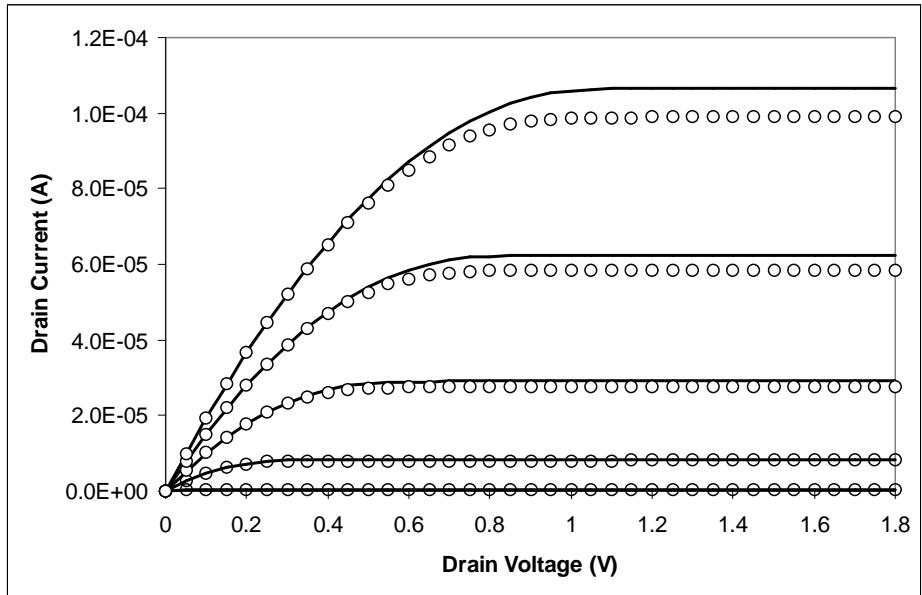

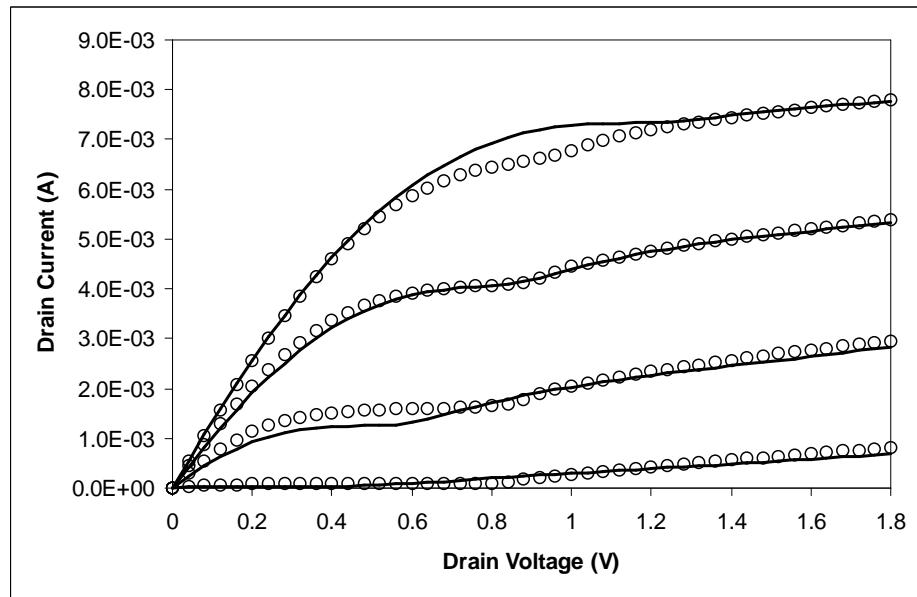

| 9.11 Drain current versus drain voltage for $V_{GFS} = 0, 0.3, 0.6, 0.9, 1.2, 1.5,$<br>and $1.8V$ for a $W = 10\mu m$ , $L = 10\mu m$ body tied device. Circles indicate<br>measured values, solid lines indicate simulated results. . . . .        | 134 |

| 9.12 Drain current versus drain voltage for $V_{GFS} = 0, 0.3, 0.6, 0.9, 1.2, 1.5,$ and<br>$1.8V$ for a $W = 10\mu m$ , $L = 0.25\mu m$ body tied device. Circles indicate<br>measured values, solid lines indicate simulated results. . . . .      | 135 |

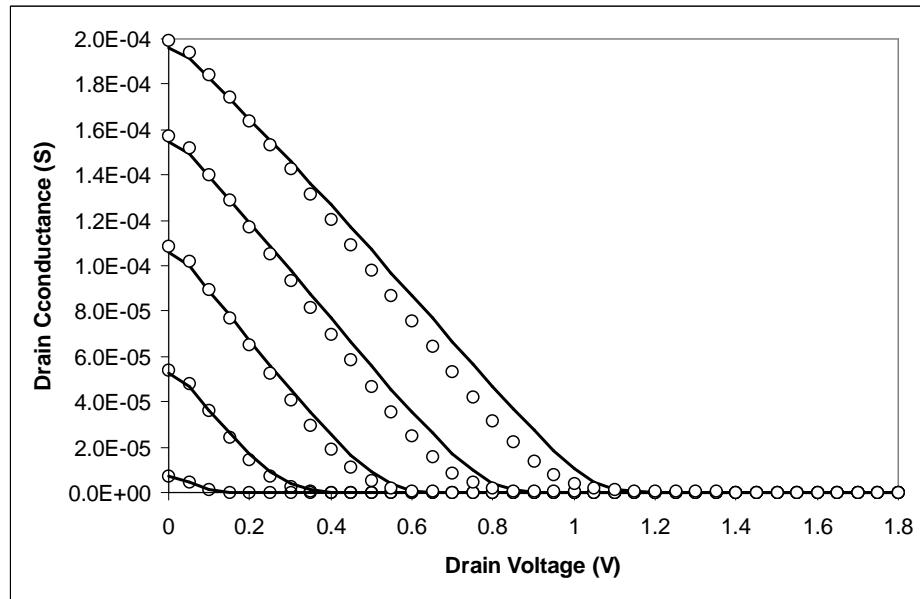

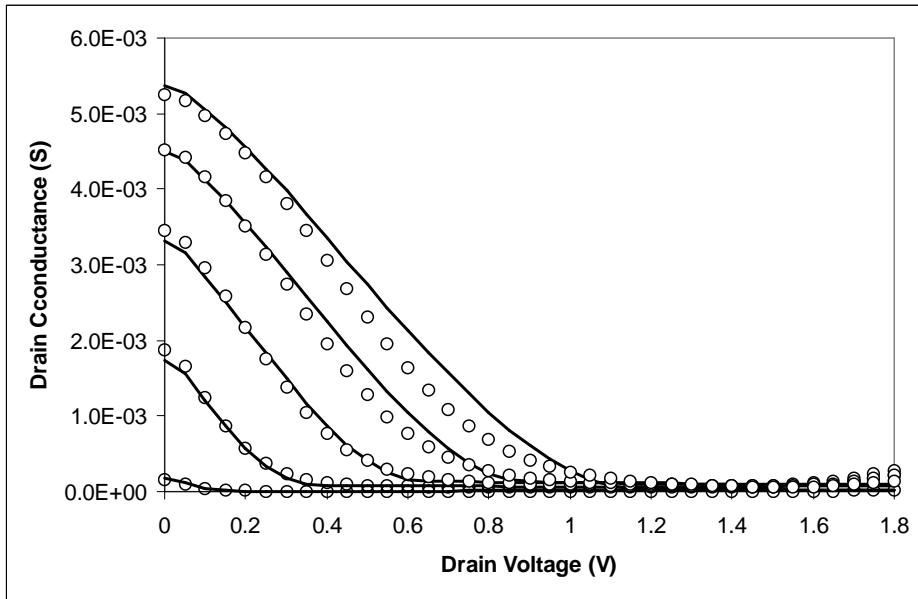

| 9.13 Output conductance versus drain voltage for $V_{GFS} = 0, 0.3, 0.6, 0.9, 1.2,$<br>1.5, and $1.8V$ for a $W = 10\mu m$ , $L = 10\mu m$ body tied device. Circles<br>indicate measured values, solid lines indicate simulated results. . . . .   | 135 |

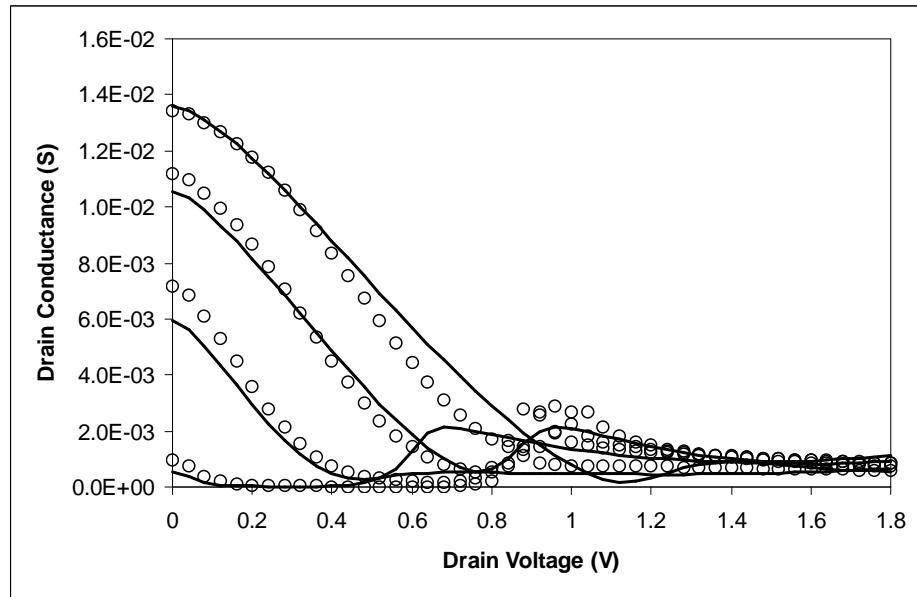

| 9.14 Output conductance versus drain voltage for $V_{GFS} = 0, 0.3, 0.6, 0.9, 1.2,$<br>1.5, and $1.8V$ for a $W = 10\mu m$ , $L = 0.25\mu m$ body tied device. Circles<br>indicate measured values, solid lines indicate simulated results. . . . . | 136 |

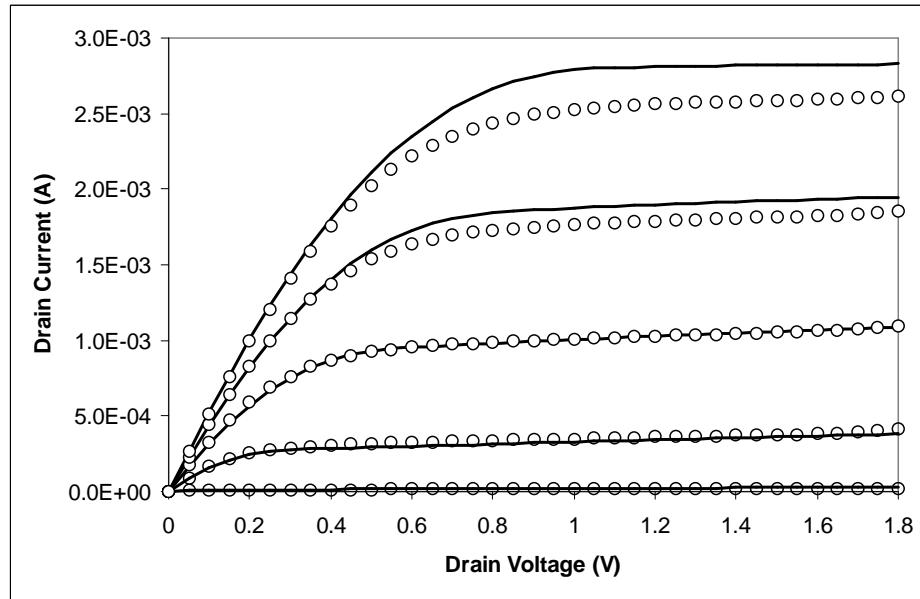

| 9.15 Drain current versus drain voltage for $V_{GFS} = 0.6, 1.0, 1.4,$ and $1.8V$ for a<br>$W = 25\mu m$ , $L = 0.25\mu m$ floating body device. Circles indicate measured<br>values, solid lines indicate simulated results. . . . .               | 137 |

| 9.16 Output conductance versus drain voltage for $V_{GFS} = 0.6, 1.0, 1.4,$ and<br>$1.8V$ for a $W = 25\mu m$ , $L = 0.25\mu m$ floating body device. Circles indicate<br>measured values, solid lines indicate simulated results. . . . .          | 137 |

# List of Symbols

|            |                                                                                   |

|------------|-----------------------------------------------------------------------------------|

| $a_1$      | Saturation surface potential cubic coefficient [-]                                |

| $a_2$      | Saturation surface potential cubic coefficient [-]                                |

| $a_3$      | Saturation surface potential cubic coefficient [-]                                |

| $a_{vo}$   | Velocity overshoot proportionality constant [-]                                   |

| $b$        | Variational parameter [ $\text{nm}^{-1}$ ]                                        |

| $CGFB0$    | Front gate-body overlap capacitance per unit length [F]                           |

| $CGFD0$    | Front gate-drain overlap capacitance per unit length [F]                          |

| $CGFS0$    | Front gate-source overlap capacitance per unit length [F]                         |

| $C_{J0}$   | Zero bias junction depletion capacitance per unit area [ $\text{F}/\text{cm}^2$ ] |

| $C_{jbd}$  | Body-drain junction depletion capacitance [F]                                     |

| $C_{jbs}$  | Body-source junction depletion capacitance [F]                                    |

| $C_{of}$   | Front gate capacitance per unit area [ $\text{F}/\text{cm}^2$ ]                   |

| $C_T$      | Device thermal capacitance [ $\text{pJ}/\text{K}$ ]                               |

| $C_{T0}$   | Thermal capacitance associated with first time constant [ $\text{pJ}/\text{K}$ ]  |

| $C_{T1}$   | Thermal capacitance associated with second time constant [ $\text{pJ}/\text{K}$ ] |

| $C_{T2}$   | Thermal capacitance associated with third time constant [ $\text{pJ}/\text{K}$ ]  |

| $C_{T3}$   | Thermal capacitance associated with fourth time constant [ $\text{pJ}/\text{K}$ ] |

| $C_{T4}$   | Thermal capacitance associated with fifth time constant [ $\text{pJ}/\text{K}$ ]  |

| $D_{itf}$  | Fast surface state density [ $1/\text{cm}^2 \cdot \text{eV}$ ]                    |

| $E_c$      | Critical lateral electric field for carrier velocity saturation [V/m]             |

| $E_{xeff}$ | Effective vertical electric field [V/m]                                           |

| $E_{yeff}$ | Effective lateral electric field [V/m]                                            |

| $f_b$      | Body charge electric field weighting coefficient [-]                              |

| $f_c$      | Channel charge electric field weighting coefficient [-]                           |

| $f_R$      | Total internal series resistance factor [-]                                       |

| $F$        | Quotient of drain to source charge densities ( $q_d/q_s$ ) [-]                    |

| $F$        | Channel degeneracy factor [-]                                                     |

| $F_{min}$  | Technology minimum feature size [ $\mu\text{m}$ ]                                 |

| $FC$       | Coefficient for forward-bias depletion capacitance model [-]                      |

| $g_{ds}$   | Drain-source output conductance [S]                                               |

| $g_m$      | Front gate transconductance [S]                                                   |

| $g_{mb}$   | Body-source transconductance [S]                                                  |

| $G_{cou}$  | Coulomb scattering mobility contribution [-]                                      |

| $G_{ph}$   | Phonon scattering mobility contribution [-]                                       |

| $G_{sr}$   | Surface roughness scattering mobility contribution [-]                            |

| $G_v$      | Total scattering mobility contribution [-]                                        |

| $G_{v0}$   | Total scattering mobility contribution at source end of channel [-]               |

| $\hbar$    | Planck's Constant divided by $2\pi$ [J.s]                                         |

| $I_{bd}$   | Body-drain diode current [A]                                                      |

| $I_{bs}$   | Body-source diode current [A]                                                     |

| $I_{CH}$   | Channel current [A]                                                               |

|             |                                                                                        |

|-------------|----------------------------------------------------------------------------------------|

| $I_{CHint}$ | Channel current excluding high field mobility effects [A]                              |

| $I_{Mdb}$   | Impact ionisation current in forward mode [A]                                          |

| $I_{Msb}$   | Impact ionisation current in reverse mode [A]                                          |

| $I_s$       | Diode diffusion component reverse saturation current [A]                               |

| $I_{s1}$    | Diode recombination component reverse saturation current [A]                           |

| $J_s$       | Diode diffusion component reverse saturation current density per metre width [A/m]     |

| $J_{s1}$    | Diode recombination component reverse saturation current density per metre width [A/m] |

| $J_n$       | Electron current density per unit area [A/cm <sup>2</sup> ]                            |

| $k$         | Mobility temperature exponent [-]                                                      |

| $k_B$       | Boltzmann constant [J/K]                                                               |

| $K_{SP}$    | Short-hand notation [-], see Equation (2.41)                                           |

| $L$         | Device channel length [m]                                                              |

| $L'$        | Length of GCA region [m]                                                               |

| $l_d$       | Length of drain region [m]                                                             |

| $l_m$       | Ionisation length [m]                                                                  |

| $l_x$       | Short channel channel length modulation parameter [m]                                  |

| $L_{eff}$   | Effective channel length [m]                                                           |

| $L_{m1}$    | Ionisation length bias coefficient [m/V]                                               |

| $L_{m2}$    | Ionisation length bias coefficient [m/V <sup>2</sup> ]                                 |

| $L_{meff}$  | Effective ionisation length [m]                                                        |

| $LD$        | Source/drain lateral diffusion [m]                                                     |

| $L_{DH}$    | Debye-Huckel length [ $\text{\AA}$ ]                                                   |

| $L_s$       | Effective fixed charge screening length [ $\text{\AA}$ ]                               |

| $L_{th}$    | Characteristic carrier thermal length [ $\text{\AA}$ ]                                 |

| $M$         | Avalanche multiplication factor due to impact ionisation [-]                           |

| $M$         | Junction grading coefficient [-]                                                       |

| $m_e$       | Electron effective mass                                                                |

| $M_{SP}$    | Charge linearisation empirical fitting parameter [-]                                   |

| $n$         | Free electron concentration [cm <sup>-3</sup> ]                                        |

| $N_B$       | Body doping concentration [cm <sup>-3</sup> ]                                          |

| $N_C$       | Channel carrier concentration [cm <sup>-3</sup> ]                                      |

| $N_P$       | Polysilicon gate doping concentration [cm <sup>-3</sup> ]                              |

| $P$         | Device power dissipation [W]                                                           |

| $PB$        | Junction built-in potential [V]                                                        |

| $q$         | Electron charge [C]                                                                    |

| $q_b$       | Body charge per unit area [C/cm <sup>2</sup> ]                                         |

| $q_{b0}$    | Body charge density at source end of channel [C/cm <sup>2</sup> ]                      |

| $Q_{B1}$    | Body charge in GCA region [C]                                                          |

| $Q_{B2}$    | Body charge in saturated drain region [C]                                              |

| $q_c$       | Channel charge per unit area [C/cm <sup>2</sup> ]                                      |

| $q_{c0}$    | Channel charge density at source end of channel [C/cm <sup>2</sup> ]                   |

| $Q_{CH1}$   | Channel charge in GCA region [C]                                                       |

| $Q_{CH2}$   | Channel charge in saturated drain region [C]                                           |

| $q_d$       | Channel charge density at drain end [C/cm <sup>2</sup> ]                               |

| $Q_{D1}$    | Drain charge in GCA region [C]                                                         |

| $Q_G$       | Front gate charge [C]                                                                  |

| $q_s$       | Channel charge density at source end [C/cm <sup>2</sup> ]                              |

| $q_{s0}$    | Channel screening charge density [C/cm <sup>2</sup> ]                                  |

| $Q_{S1}$    | Source charge in GCA region [C]                                                        |

| $q_{tot}$   | Total charge density in silicon film [C/cm <sup>2</sup> ]                              |

| $R_D$       | Drain series resistance [ $\Omega$ ]                                                   |

|                 |                                                                          |

|-----------------|--------------------------------------------------------------------------|

| $R_{DW}$        | Width scaling drain series resistance [ $\Omega \cdot \mu\text{m}$ ]     |

| $R_S$           | Source series resistance [ $\Omega$ ]                                    |

| $R_{SW}$        | Width scaling source series resistance [ $\Omega \cdot \mu\text{m}$ ]    |

| $R_P$           | Projected range of doping implant [nm]                                   |

| $R_T$           | Device thermal resistance [K/W]                                          |

| $R_{T0}$        | Thermal resistance associated with first time constant [K/W]             |

| $R_{T1}$        | Thermal resistance associated with second time constant [K/W]            |

| $R_{T2}$        | Thermal resistance associated with third time constant [K/W]             |

| $R_{T3}$        | Thermal resistance associated with fourth time constant [K/W]            |

| $R_{T4}$        | Thermal resistance associated with fifth time constant [K/W]             |

| $S$             | Saturation factor accounting for mobility effects [-]                    |

| $T$             | Device temperature (including self-heating effects) [K]                  |

| $T_{amb}$       | Ambient temperature [K]                                                  |

| $t_b$           | Silicon film thickness [m]                                               |

| $t_{box}$       | Back gate oxide thickness [m]                                            |

| $t_{ox}$        | Front gate oxide thickness [m]                                           |

| $t_{oxeff}$     | Effective front gate oxide thickness (accounting for quantum effect) [m] |

| $V_{BS}$        | Body-source voltage [V]                                                  |

| $V_{cb}$        | Channel-body potential [V]                                               |

| $V_{Dex}$       | Drain-source voltage used to extract $V_{Tex}$ [V]                       |

| $V_{DB}$        | Drain-body voltage [V]                                                   |

| $V_{DS}$        | Drain-source voltage [V]                                                 |

| $V_{Dsat}$      | Drain saturation voltage [V]                                             |

| $V_{FB}$        | Flat-band voltage [V]                                                    |

| $V_{FB}^f$      | Front flat-band voltage [V]                                              |

| $V_g$           | Short-hand notation [V], see Equation (2.35)                             |

| $V_{gy}$        | Numerically limited form of $V_g$ [V]                                    |

| $V_{GBT}$       | Short-hand notation [V], see Equation (2.31)                             |

| $V_{GfB}$       | Front gate-body voltage                                                  |

| $V_{GfS}$       | Front gate-source voltage                                                |

| $V_{GT}$        | Short-hand notation [V], see Equation (2.28)                             |

| $V_P$           | Short channel channel length modulation parameter [V]                    |

| $v_{sat}$       | Carrier saturation velocity [cm/s]                                       |

| $v_{sat\_vo}$   | Carrier saturation velocity (accounting for velocity overshoot) [cm/s]   |

| $V_{SB}$        | Source-body voltage [V]                                                  |

| $V_{Tex}$       | Extracted threshold voltage [V]                                          |

| $V_{TH}$        | Threshold voltage [V]                                                    |

| $W$             | Channel width [m]                                                        |

| $x_d$           | Depletion depth [nm]                                                     |

| $W_{eff}$       | Effective channel width [m]                                              |

| $y_{out}$       | Drain admittance [S]                                                     |

| $y_{sat}$       | Short-hand notation [-], see Equation (4.21)                             |

| $Z_{bd}$        | Body-drain network impedance [ $\Omega$ ]                                |

| $Z_{bs}$        | Body-source network impedance [ $\Omega$ ]                               |

| $\alpha$        | Short-hand notation [-], see Equation (2.28)                             |

| $\alpha_0$      | Impact ionisation coefficient [ $\text{cm}^{-1}$ ]                       |

| $\alpha_{cou}$  | Coulomb scattering coefficient [ $\text{m}^3$ ]                          |

| $\alpha_{ph}$   | Phonon scattering coefficient [ $(\text{m}/\text{V})^{1/3}$ ]            |

| $\alpha_{sr}$   | Surface roughness scattering coefficient [ $(\text{m}/\text{V})^2$ ]     |

| $\alpha_\theta$ | Mobility scattering coefficient [cm/V]                                   |

| $\beta_0$       | Impact ionisation coefficient [V/cm]                                     |

|                 |                                                                               |

|-----------------|-------------------------------------------------------------------------------|

| $\chi$          | Temperature coefficient of threshold voltage [V/K]                            |

| $\chi_\beta$    | Temperature coefficient of impact ionisation parameter [V/(cm.K)]             |

| $\chi_{FB}$     | Temperature coefficient of flat-band voltage [V/K]                            |

| $\delta_0$      | Empirical threshold extraction parameter [-]                                  |

| $\delta_s$      | Body charge linearisation coefficient $[V^{-1/2}]$                            |

| $\delta_p$      | Body charge linearisation coefficient $[V^{-1/2}]$                            |

| $\Delta E_g$    | Electron ground state offset from bottom of conduction band [eV]              |

| $\Delta L$      | Short channel effect parameter [m]                                            |

| $\Delta R_P$    | Standard deviation of $R_P$ [nm]                                              |

| $\Delta T$      | Device temperature rise [K]                                                   |

| $\Delta W$      | Narrow width effect parameter [m]                                             |

| $\Delta z_{CL}$ | Classical inversion charge centroid offset [m]                                |

| $\Delta z_I$    | Inversion charge centroid offset [m]                                          |

| $\Delta z_{QM}$ | Quantum mechanical inversion charge centroid offset [m]                       |

| $\eta$          | Impact ionisation empirical field adjustment parameter [-]                    |

| $\eta_d$        | Diode ideality factor for diffusion component [-]                             |

| $\eta_{d1}$     | Diode ideality factor for recombination component [-]                         |

| $\eta_s$        | Fast surface state coefficient [-]                                            |

| $\gamma_{eff}$  | Effective body factor $[V^{1/2}]$                                             |

| $\gamma_s$      | Silicon body factor $[V^{1/2}]$                                               |

| $\gamma_p$      | Polysilicon gate body factor $[V^{1/2}]$                                      |

| $\kappa$        | Thermal conductivity [W/m.K]                                                  |

| $\lambda$       | Channel length modulation parameter [m/V]                                     |

| $\lambda_{vo}$  | Velocity overshoot parameter [V/K]                                            |

| $\mu$           | Carrier mobility $[cm^2/V.s]$                                                 |

| $\mu_0$         | Low field carrier mobility $[cm^2/V.s]$                                       |

| $\mu_n$         | Electron mobility $[cm^2/V.s]$                                                |

| $\mu_s$         | Surface carrier mobility $[cm^2/V.s]$                                         |

| $\mu_{xeff}$    | Effective mobility accounting for vertical field degradation $[cm^2/V.s]$     |

| $\mu_{eff}$     | Effective mobility accounting for carrier velocity saturation $[cm^2/V.s]$    |

| $\mu_{cou}$     | Coulomb scattering limited mobility $[cm^2/V.s]$                              |

| $\mu_{ph}$      | Phonon scattering limited mobility $[cm^2/V.s]$                               |

| $\mu_{sr}$      | Surface roughness scattering limited mobility $[cm^2/V.s]$                    |

| $\mu^*$         | Unscreened mobility per scattering centre per unit area $[(V.s)^{-1}]$        |

| $\omega$        | Short-hand notation [V], see Equation (2.53)                                  |

| $\omega_{sinv}$ | Short-hand notation [V], see Equation (2.49)                                  |

| $\Phi_F$        | Fermi potential [V]                                                           |

| $\Phi_T$        | Thermal voltage (diode equations) [V]                                         |

| $\Phi_t$        | Thermal voltage [V]                                                           |

| $\Psi$          | Short-hand notation [V], see Equation (4.1)                                   |

| $\psi_s$        | Surface potential [V]                                                         |

| $\psi_{s0}$     | Surface potential at source end of channel [V]                                |

| $\psi_{sinv}$   | Strong inversion surface potential approximation [V]                          |

| $\psi_{sLsat}$  | Saturation surface potential [V]                                              |

| $\psi_{sL}$     | Surface potential at drain end of channel [V]                                 |

| $\psi_{ss}$     | Surface potential in sub-threshold [V]                                        |

| $\psi_{st}$     | Single piece surface potential approximation (no high field effects) [V]      |

| $\psi_{st0}$    | Surface potential at source end of channel (no high field effects) [V]        |

| $\psi_{stL}$    | Surface potential at drain end of channel (no high field effects) [V]         |

| $\psi_{stqmo}$  | Surface potential at source end of channel accounting for quantum effects [V] |

| $\psi_{stqmL}$  | Surface potential at drain end of channel accounting for quantum effects [V]  |

|                 |                                                                            |

|-----------------|----------------------------------------------------------------------------|

| $\sigma$        | DIBL parameter [m]                                                         |

| $\theta$        | Vertical field mobility degradation [ $V^{-1}$ ]                           |

| $\epsilon_{ox}$ | Permittivity of silicon dioxide [ $11.7 \times 8.854 \times 10^{-12}$ F/m] |

| $\epsilon_{si}$ | Permittivity of silicon [ $3.9 \times 8.854 \times 10^{-12}$ F/m]          |

# List of Acronyms

|        |                                                       |

|--------|-------------------------------------------------------|

| BJT    | Bipolar Junction Transistor                           |

| CMOS   | Complementary Metal–Oxide–Semiconductor (technology)  |

| DIBL   | Drain Induced Barrier Lowering                        |

| DOS    | Density of States                                     |

| FD     | Fully Depleted                                        |

| GIDL   | Gate Induced Drain Leakage                            |

| IC     | Integrated Circuit                                    |

| LDD    | Lightly Doped Drain                                   |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor     |

| PD     | Partially Depleted                                    |

| RSCE   | Reverse Short Channel Effect                          |

| SCE    | Short Channel Effect                                  |

| SOI    | Silicon-On-Insulator                                  |

| SOS    | Silicon-On-Sapphire                                   |

| STAG   | Southampton Thermal AnaloGue (SOI MOSFET SPICE model) |

| VLSI   | Very Large Scale Integration                          |

# Chapter 1

## Introduction

### 1.1 A Review of MOS Technology

#### 1.1.1 Bulk Technology

Despite the success of bulk CMOS in the microelectronics industry, devices manufactured in the conventional way do exhibit some non-ideal behaviour. There have traditionally been two problems in particular which have affected bulk CMOS devices, both of which result from a lack of electrical isolation between the active device and the substrate.

The first undesirable interaction involves a phenomenon known as latch-up [1]. This is unique to CMOS, and occurs through the activation of a PNPN thyristor structure, formed by three PN junctions in close proximity. When this happens, parasitic bipolar action creates a short circuit path between the power terminals, destroying the device. Various measures can be employed to avoid this, including using an oxide isolation wall to break the PNPN parasitic structure, or utilising the twin-tub configuration [1]. Of course, these measures introduce additional process steps, and so raise the cost of producing a wafer. Since it is the parasitic bipolar action which governs latch-up, it would follow that sub-micron processes are again more susceptible to this effect, featuring as they do larger parasitic BJT gains. Admittedly, latch-up is no longer the major concern it used to be, since modern rail voltages are often too low to turn on the parasitic PNPN device.

The second problem is the parasitic capacitance between the source/drain regions and the substrate. The effect of this is to slow down device operation, as these capacitors charge and discharge. Increasing the amount of substrate doping results in larger parasitic capacitances; unfortunately, this doping increase is necessary for scaling in modern deep sub-micron processes, in order to prevent punch-through and to help regulate the threshold voltage [2]. As a result, we expect the parasitic capacitance per unit area to increase with decreasing feature size.

Not only does this second parasitic effect become more problematic as MOS devices are scaled down, but new circuit applications now exist which tend to emphasise these prob-

lems. High frequency circuitry, critical to the wireless telecommunication market, requires fast device operation, and parasitic capacitances are extremely undesirable. Thus, any MOS technology which solves these problems, and which provides a viable alternative to bulk CMOS, is worthy of serious consideration. SOI is one such technology.

### 1.1.2 SOI Technology

SOI (Silicon-on-Insulator) technology has been in existence in some form for almost as long as bulk CMOS. The basic principle behind SOI is as follows: since it is the interaction between the active device and the substrate which causes many undesirable parasitic effects in bulk technology, simply replace the silicon substrate with an insulating substrate, thus electrically decoupling the active device. Initially, the substrate used was made of sapphire, and the technology was called SOS (Silicon-on-Sapphire). Later, it became possible to create good quality interfaces using silicon oxide, which remains the material of choice today. While it has proved very useful in certain niche markets, SOI has never come close to rivalling bulk CMOS in terms of volume of production or breadth of application.

SOI brings a number of benefits to circuit designers. The electrical isolation of the active device area eliminates any possibility of latch-up, whilst also greatly reducing parasitic drain and source capacitances. In addition, only a thin film of silicon is being used for the active device, so the source and drain diffusions will reach to the back oxide, and the p-n junction areas will be smaller. This in turn leads to smaller leakage currents, which makes it particularly useful for high temperature applications. Another benefit of SOI is that it uses a smaller active volume of silicon compared to bulk, making it less susceptible to single event upset caused by high levels of radiation. These two properties account for the usefulness of SOI technology in high temperature and rad hard applications, which for a long time were its main commercial uses.

With the advent of wireless communications, the demand for low power, high frequency systems has increased greatly. Such applications are also good candidates for development in SOI, since they can benefit from the reduced parasitic capacitances in order to achieve higher speed. Furthermore, the combination of reduced junction leakage current and parasitic capacitances mean that SOI CMOS circuits can achieve lower levels of power consumption, both when static and during switching, making SOI an attractive prospect for low power circuitry.

The presence of an electrically isolated active area can cause problems however. The well-documented kink effect [3,4] occurs when part of the body is left floating, due to the lack of a good electrical contact to the silicon film at the back oxide interface. The resulting unpredictability of the body node voltage can result in complex behaviour in DC, small signal and transient regimes [3,5,6]. Additional, less well known small signal phenomena can also be observed [6], which are caused by capacitive coupling of the floating body

node. These floating body effects make SOI behaviour less predictable than bulk, and conventional bulk models cannot predict these behaviours.

Devices in which the body region is not totally depleted when the MOS channel is inverted, and which are thus susceptible to the kink effect, are referred to as *Partially-Depleted SOI* (PD-SOI) devices. Another class of SOI MOS transistor exists, one in which the silicon film is sufficiently thin to give total depletion of the body even at low gate biases. These are called *Fully-Depleted SOI* (FD-SOI) devices. An ideal fully-depleted device is one in which there exists no undepleted quasi-neutral region in the body of the device, electrically isolated from the source and drain junctions. Any carriers injected into the body region below the channel, for instance as a result of impact ionisation, will not be able to remain in the depleted body region, and thus they cannot contribute to forward biasing of the source/body junction. Instead, they will be swept towards the source terminal by the built-in potential across the body-source junction [8]. Furthermore, lowering of the body-source junction barrier allows oppositely charged carriers to diffuse from the source into the body, with the result that recombination will occur before a substantial increase in body potential can occur.

Fully-depleted devices offer the benefits of SOI performance but without the kink effect, and with transconductance behaviour that is superior to both bulk and PD-SOI [7]. A decade ago, mature FD-SOI technologies had not yet been realised, due to limitations in processing techniques. In order to produce a device for which the gate-induced depletion region reaches all the way to the back gate, it is necessary to either reduce the doping level of the silicon film, or else reduce the thickness of the silicon film. The first option is prohibited in short-channel devices, since high doping levels are necessary to suppress short-channel effects. Therefore, it is necessary instead to use thinner silicon films. However, it is more difficult to ensure consistent film thicknesses in production [9]. Nowadays, FD-SOI is the more common technology, with PD-SOI finding use in certain high-performance niche applications.

Finally, SOI technology exhibits self-heating, due to the poor thermal conductivity of the buried oxide layer [10, 11]. Self-heating appears in both types of SOI device, and can degrade device performance. Because the heating is simply due to the power being dissipated from the channel current, the degradation becomes most noticeable at high gate and drain voltages. As with the electrical floating-body effects, this needs to be properly modelled, to avoid unexpected circuit behaviour.

### 1.1.3 SOI versus bulk

For several decades, SOI has occupied only certain niche markets in the microelectronics industry. While its properties have made it ideal for rad hard and high temperature applications, the difficulty of modelling and compensating for the various floating body effects,

combined with the additional cost compared with the more mature bulk technologies, have meant that SOI has been unable to compete in the core digital and mixed signal VLSI markets.

This situation began to change in the late 1990s, following IBM's announcement of its first commercial microprocessor designed in SOI technology, and a number of examples of commercial digital SOI designs can now be found, i.e. [12]. With the move to deep-submicron technologies, and the growing demand for low-power, high frequency circuit designs, the advantages of SOI over bulk have started to become sufficiently attractive for companies to invest time and money trying to overcome the process and design problems which have previously stifled the exploitation of this technology. The promise of improved performance, either through higher speeds or lower power consumption, has led companies such as Motorola, Texas Instruments and AMD to also start developing commercial SOI-based products.

At present, there is no clear consensus as to whether SOI can provide a long-term alternative to bulk. While it is generally agreed that SOI performance exceeds that of bulk by 10-20% [13], there is much debate as to whether this advantage can be maintained with further technology scaling. Much of the improvement afforded by SOI is a result of the reduction of the junction capacitance. However, as devices are scaled down, the issue of junction capacitance becomes secondary to parasitic capacitances in the gate and interconnects [13]. Furthermore, because floating-body devices are susceptible to the history effect [14], circuit designers must factor in a safety margin when designing circuits in SOI. This means that they cannot utilise the full performance gain of the technology, so that the theoretical improvement of around 15% is reduced to about 10% in practise. As a result, some companies, notably Intel, have been reluctant to commit resources to development of a SOI process.

Regardless of the performance issues, SOI circuit production is still somewhat limited by logistical issues arising from its lack of maturity relative to bulk. SOI wafers still cost more than bulk, and until recently, were not available in the quantities needed for volume production. However, the fact that so many semiconductor manufacturers are now taking SOI seriously means that this situation is likely to improve. It is difficult to see SOI totally replacing bulk over any timescale; the only scenario that could bring this about would be if bulk MOSFETs encountered some fundamental limit in scaling, one to which SOI was immune. Good progress is still being made in the scaling of transistors however, with commercial design work now being done with device gate lengths of 45nm for leading edge products. It is thought that ultimately, SOI might postpone the onset of any performance limit by about one generation, on account of the advantages that it provides over bulk. Of course, as already discussed, this assumes that advances in other areas such as interconnect technology allow it to retain its performance advantages. A plausible prediction would be that SOI will continue to mature and co-exist with bulk processes, with some

companies developing bulk and SOI processes in parallel, and using each for different types of application.

## 1.2 A Review of MOS Compact Models

We shall now look at the current state of MOS compact modelling. We shall be taking a broader look at available models, encompassing PD-SOI, FD-SOI, and bulk models. Having categorised the various basic model types, we shall then explain how the work described in this thesis fits into this wider picture.

### 1.2.1 Piece-Wise Models

Earlier generations of compact models are based on the Meyer model [15]. The Meyer model represented the first serious attempt to describe MOSFET characteristics in a relatively simple way, as a function of the applied terminal voltages. The model equations were derived by assuming that the channel current was composed of only a drift component, with the diffusion contribution being ignored. The original Meyer model failed to fulfill the important condition of charge conservation, a shortcoming that was later corrected by the capacitance model developed by Ward and Dutton [16].

Two main difficulties have emerged when using the Meyer formulation as the basis of a compact model. The first problem is that the model equations possess discontinuities. Since we are neglecting the diffusion current, we find a discontinuity when making the transition between strong inversion (where drift does indeed dominate over diffusion) and sub-threshold (where the reverse is true). The same is true for the transition between the strong inversion triode region and saturation. Separate equations need to be introduced to describe sub-threshold and saturation regions, and smoothed numerically. Models which describe different operating regions with different equations are called 'piece-wise' or 'regional' models. It is in fact perfectly possible to eliminate such discontinuities through the application of appropriate smoothing functions, but the need for such measures was less apparent at the time these models were being developed, and so the problem of discontinuities is one that has become associated with piece-wise models.

The second problem is that it is difficult to incorporate new physical effects that result from device scaling. This stems from the empirical nature of these models, and is usually reflected in the model possessing large numbers of empirical fitting parameters. It is not unusual for such models to employ 'binning', whereby each key parameter is given additional dependencies for device length, width and area, thus making model parameter sets large and unwieldy. Fitting for such models is often very good under ideal circumstances, since the extra fitting parameters offer so many degrees of freedom. However, actually optimising such a large number of parameters is difficult and time-consuming, and can

lead to non-physical parameter values being assigned. This in turn greatly reduces the model's predictive power, since there is less likelihood of accuracy outside the optimisation range.

Although it is now standard practise for models to be based on the newer surface potential based approach, there exist some well-known older piece-wise models. Among them is the BSIM3 model, which for a long time was the industry standard. There are versions of BSIM3 for both bulk MOS [17] and SOI [18, 19]. Another well known piece-wise model is the Philips MOS9 model [20]; like BSIM3, these is well established, and can be fitted to give good matching to experimental data.

### 1.2.2 Surface Potential Models

This newer class of model is effectively considered the de facto standard in compact circuit model development, even if the microelectronics industry has been somewhat slow in the past to actually adopt these models into their design flow [21]. At the core of the surface potential approach is the drift-diffusion approximation, originally developed by Pao and Sah [22]. As with the piece-wise models, the intention is to describe the characteristics of a MOSFET as a function of its applied terminal voltages. However, the inclusion of both drift and diffusion current components leads to a more unified physical description which includes all bias conditions within a single expression. To obtain this expression requires the combined solution of three key equations: the Poisson equation, which relates the electric field to the distribution of charges, the current density equation, which describes the current as being composed of a drift and a diffusion component, and the continuity equation, which maintains the overall carrier flux at zero.